Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | M8C                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 24MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 44                                                                          |

| Program Memory Size        | 16KB (16K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                |                                                                             |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.25V                                                                  |

| Data Converters            | A/D 4x14b; D/A 4x9b                                                         |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

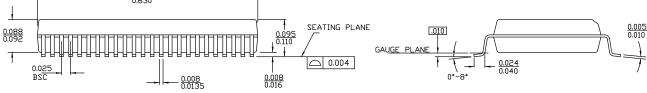

| Package / Case             | 48-BSSOP (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 48-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c27643-24pvxi |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

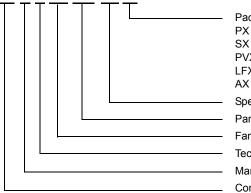

# 56-pin Part Pinout

The 56-pin SSOP part is for the CY8C27002 On-Chip Debug (OCD) PSoC device.

Note This part is only used for in-circuit debugging. It is NOT available for production.

## Table 8. Pin Definitions – 56-pin Part Pinout (SSOP)

| Pin | Ту      | /pe    | Pin             | Description                                                                   |  |  |  |  |  |

|-----|---------|--------|-----------------|-------------------------------------------------------------------------------|--|--|--|--|--|

| No. | Digital | Analog | Name            | Description                                                                   |  |  |  |  |  |

| 1   |         |        | NC              | No connection. Pin must be left floating                                      |  |  |  |  |  |

| 2   | I/O     | I      | P0[7]           | Analog column mux input                                                       |  |  |  |  |  |

| 3   | I/O     | I      | P0[5]           | Analog column mux input and column output                                     |  |  |  |  |  |

| 4   | I/O     | I      | P0[3]           | Analog column mux input and column output                                     |  |  |  |  |  |

| 5   | I/O     | I      | P0[1]           | Analog column mux input                                                       |  |  |  |  |  |

| 6   | I/O     |        | P2[7]           |                                                                               |  |  |  |  |  |

| 7   | I/O     |        | P2[5]           |                                                                               |  |  |  |  |  |

| 8   | I/O     | I      | P2[3]           | Direct switched capacitor block input                                         |  |  |  |  |  |

| 9   | I/O     | I      | P2[1]           | Direct switched capacitor block input                                         |  |  |  |  |  |

| 10  | I/O     |        | P4[7]           |                                                                               |  |  |  |  |  |

| 11  | I/O     |        | P4[5]           |                                                                               |  |  |  |  |  |

| 12  | I/O     | I      | P4[3]           |                                                                               |  |  |  |  |  |

| 13  | I/O     | I      | P4[1]           |                                                                               |  |  |  |  |  |

| 14  | OCD     |        | OCDE            | OCD even data I/O                                                             |  |  |  |  |  |

| 15  | OCD     |        | OCDO            | OCD odd data output                                                           |  |  |  |  |  |

| 16  | Po      | ower   | SMP             | SMP connection to required external components                                |  |  |  |  |  |

| 17  | I/O     |        | P3[7]           |                                                                               |  |  |  |  |  |

| 18  | I/O     |        | P3[5]           |                                                                               |  |  |  |  |  |

| 19  | I/O     |        | P3[3]           |                                                                               |  |  |  |  |  |

| 20  | I/O     |        | P3[1]           |                                                                               |  |  |  |  |  |

| 21  | I/O     |        | P5[3]           |                                                                               |  |  |  |  |  |

| 22  | I/O     |        | P5[1]           |                                                                               |  |  |  |  |  |

| 23  | I/O     |        | P1[7]           | I <sup>2</sup> C SCL                                                          |  |  |  |  |  |

| 24  | I/O     |        | P1[5]           | I <sup>2</sup> C SDA                                                          |  |  |  |  |  |

| 25  |         | I      | NC              | No connection. Pin must be left floating                                      |  |  |  |  |  |

| 26  | I/O     |        | P1[3]           |                                                                               |  |  |  |  |  |

| 27  | I/O     |        | P1[1]           | Crystal Input (XTALin), I <sup>2</sup> C SCL,<br>ISSP-SCLK <sup>[12]</sup>    |  |  |  |  |  |

| 28  | Po      | wer    | V <sub>DD</sub> | Supply voltage                                                                |  |  |  |  |  |

| 29  |         |        | NC              | No connection. Pin must be left floating                                      |  |  |  |  |  |

| 30  |         |        | NC              | No connection. Pin must be left floating                                      |  |  |  |  |  |

| 31  | I/O     |        | P1[0]           | Crystal output (XTALout), I <sup>2</sup> C SDA,<br>ISSP-SDATA <sup>[12]</sup> |  |  |  |  |  |

| 32  | I/O     |        | P1[2]           |                                                                               |  |  |  |  |  |

| 33  | I/O     | 1      | P1[4]           | Optional external clock input (EXTCLK)                                        |  |  |  |  |  |

| 34  | I/O     |        | P1[6]           |                                                                               |  |  |  |  |  |

| 35  | I/O     |        | P5[0]           |                                                                               |  |  |  |  |  |

| 36  | I/O     | 1      | P5[2]           |                                                                               |  |  |  |  |  |

| 37  | I/O     |        | P3[0]           |                                                                               |  |  |  |  |  |

| 38  | I/O     |        | P3[2]           |                                                                               |  |  |  |  |  |

| 39  | I/O     |        | P3[4]           |                                                                               |  |  |  |  |  |

| 40  | I/O     | 1      | P3[6]           |                                                                               |  |  |  |  |  |

| L   |         | 1      |                 | ۱ <u> </u>                                                                    |  |  |  |  |  |

| <b>J</b>                | -  |      |    |   |                      |

|-------------------------|----|------|----|---|----------------------|

| ſ                       | 0  | —, — |    |   |                      |

| NC 🗖                    | 1  |      | 56 |   | V <sub>DD</sub>      |

| AI, P0[7] <b>=</b>      | 2  |      | 55 | - | P0[6], AI            |

| AIO, P0[5] <b>=</b>     | 3  |      | 54 | - | P0[4], AIO           |

| AIO, P0[3]              | 4  |      | 53 |   | P0[2], AIO           |

| AI, P0[1]               | 5  |      | 52 |   | P0[0], AI            |

| P2[7] 🗖                 | 6  |      | 51 |   | P2[6], External VRef |

| P2[5] 🗖                 | 7  |      | 50 | - | P2[4], External AGND |

| AI, P2[3] <b>=</b>      | 8  |      | 49 | - | P2[2], AI            |

| AI, P2[1]               | 9  |      | 48 |   | P2[0], AI            |

| P4[7] 🖬                 | 10 |      | 47 |   | P4[6]                |

| P4[5] 🗖                 | 11 |      | 46 | - | P4[4]                |

| P4[3] 🗖                 | 12 |      | 45 |   | P4[2]                |

| P4[1] <b>=</b>          | 13 |      | 44 | - | P4[0]                |

| OCDE                    | 14 | SSOP | 43 | - | CCLK                 |

| OCDO 🗖                  | 15 |      | 42 |   | HCLK                 |

| SMP 🗖                   | 16 |      | 41 | - | XRES                 |

| P3[7] 🗖                 | 17 |      | 40 |   | P3[6]                |

| P3[5] 🗖                 | 18 |      | 39 | - | P3[4]                |

| P3[3] 🗖                 | 19 |      | 38 | - | P3[2]                |

| P3[1] 🗖                 | 20 |      | 37 |   | P3[0]                |

| P5[3] <b>=</b>          | 21 |      | 36 | - | P5[2]                |

| P5[1] <b>=</b>          | 22 |      | 35 | - | P5[0]                |

| I2C SCL, P1[7]=         | 23 |      | 34 |   | P1[6]                |

| I2C SDA, P1[5] <b>■</b> | 24 |      | 33 |   | P1[4], EXTCLK        |

| NC 🗖                    | 25 |      | 32 |   | P1[2]                |

Figure 10. CY8C27002 56-pin PSoC Device

#### **Not for Production**

31

30 È. NC

29

NC

P1[3] = 26

27

28

SCLK, I2C SCL, XTALIn, P1[

P1[0], XTALOut, I2C SDA, S

#### Note

12. These are the ISSP pins, which are not High Z at POR (Power On Reset). See the PSoC Programmable System-on-Chip Technical Reference Manual for details.

# **Electrical Specifications**

This section presents the DC and AC electrical specifications of the CY8C27x43 PSoC device. For the most up to date electrical specifications, confirm that you have the most recent datasheet by going to the web at http://www.cypress.com.

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications for devices running at greater than 12 MHz are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  70 °C and T<sub>J</sub>  $\leq$  82 °C.

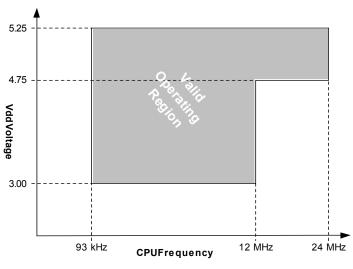

# Figure 11. Voltage versus CPU Frequency

#### **Absolute Maximum Ratings**

Exceeding maximum ratings may shorten the useful life of the device. User guidelines are not tested.

#### Table 12. Absolute Maximum Ratings

| Symbol                | Description                                                   | Min                     | Тур | Max                     | Unit  | Notes                                                                                                                                                                                                |

|-----------------------|---------------------------------------------------------------|-------------------------|-----|-------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>STG</sub>      | Storage temperature                                           | -55                     | 25  | +100                    | °C    | Higher storage temperatures<br>reduce data retention time.<br>Recommended storage<br>temperature is +25 °C ± 25 °C.<br>Extended duration storage<br>temperatures above 65 °C<br>degrade reliability. |

| T <sub>BAKETEMP</sub> | Bake temperature                                              | -                       | 125 | See<br>package<br>label | °C    |                                                                                                                                                                                                      |

| <sup>t</sup> вакетіме | Bake time                                                     | See<br>package<br>label | -   | 72                      | Hours |                                                                                                                                                                                                      |

| T <sub>A</sub>        | Ambient temperature with power applied                        | -40                     | -   | +85                     | °C    |                                                                                                                                                                                                      |

| V <sub>DD</sub>       | Supply voltage on V <sub>DD</sub> relative to Vss             | -0.5                    | -   | +6.0                    | V     |                                                                                                                                                                                                      |

| V <sub>IO</sub>       | DC input voltage                                              | Vss - 0.5               | -   | V <sub>DD</sub> + 0.5   | V     |                                                                                                                                                                                                      |

| V <sub>IOZ</sub>      | DC voltage applied to tristate                                | Vss – 0.5               | -   | V <sub>DD</sub> + 0.5   | V     |                                                                                                                                                                                                      |

| I <sub>MIO</sub>      | Maximum current into any port pin                             | -25                     | _   | +50                     | mA    |                                                                                                                                                                                                      |

| I <sub>MAIO</sub>     | Maximum current into any port pin configured as analog driver | -50                     | _   | +50                     | mA    |                                                                                                                                                                                                      |

| ESD                   | Electrostatic discharge voltage                               | 2000                    | -   | -                       | V     | Human body model ESD.                                                                                                                                                                                |

| LU                    | Latch-up current                                              | -                       | -   | 200                     | mA    |                                                                                                                                                                                                      |

# Table 19. 5-V DC Analog Output Buffer Specifications (continued)

| Symbol             | Description                                                                          | Min | Тур        | Max        | Unit     | Notes                                                                                  |

|--------------------|--------------------------------------------------------------------------------------|-----|------------|------------|----------|----------------------------------------------------------------------------------------|

| I <sub>SOB</sub>   | Supply current including opamp<br>bias cell (no load)<br>Power = low<br>Power = high |     | 1.1<br>2.6 | 5.1<br>8.8 | mA<br>mA |                                                                                        |

| PSRR <sub>OB</sub> | Supply voltage rejection ratio                                                       | 60  | 64         | _          | dB       |                                                                                        |

| I <sub>OMAX</sub>  | Maximum output current                                                               | _   | 40         | _          | mA       |                                                                                        |

| CL                 | Load capacitance                                                                     | -   | -          | 200        | pF       | This specification applies to the external circuit driven by the analog output buffer. |

# Table 20. 3.3-V DC Analog Output Buffer Specifications

| Symbol               | Description                                                                                                                                                                   | Min                                                        | Тур                  | Max                                                        | Unit                             | Notes                                                                                  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------|------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------|

| V <sub>OSOB</sub>    | Input offset voltage (absolute value)<br>Power = Iow, Opamp bias = Iow<br>Power = Iow, Opamp bias = high<br>Power = high, Opamp bias = Iow<br>Power = high, Opamp bias = high |                                                            | 3.2<br>3.2<br>6<br>6 | 20<br>20<br>25<br>25                                       | mV<br>mV<br>mV<br>mV             | High power setting is not recommended.                                                 |

| TCV <sub>OSOB</sub>  | Average input offset voltage drift<br>Power = Iow, Opamp bias = Iow<br>Power = Iow, Opamp bias = high<br>Power = high, Opamp bias = Iow<br>Power = high, Opamp bias = high    |                                                            | 9<br>9<br>12<br>12   | 55<br>55<br>70<br>70                                       | μV/°C<br>μV/°C<br>μV/°C<br>μV/°C | High power setting is not recommended.                                                 |

| V <sub>CMOB</sub>    | Common-mode input voltage range                                                                                                                                               | 0.5                                                        | -                    | V <sub>DD</sub> – 1.0                                      | V                                |                                                                                        |

| R <sub>OUTOB</sub>   | Output resistance<br>Power = low<br>Power = high                                                                                                                              |                                                            | 1<br>1               |                                                            | $\Omega \Omega$                  |                                                                                        |

| V <sub>OHIGHOB</sub> | High output voltage swing<br>(load = 32 ohms to V <sub>DD</sub> /2)<br>Power = low<br>Power = high                                                                            | 0.5 × V <sub>DD</sub> + 1.0<br>0.5 × V <sub>DD</sub> + 1.0 |                      |                                                            | V<br>V                           |                                                                                        |

| V <sub>OLOWOB</sub>  | Low output voltage swing<br>(load = 32 ohms to V <sub>DD</sub> /2)<br>Power = low<br>Power = high                                                                             | -                                                          | -                    | 0.5 × V <sub>DD</sub> – 1.0<br>0.5 × V <sub>DD</sub> – 1.0 | V<br>V                           |                                                                                        |

| I <sub>SOB</sub>     | Supply current including opamp<br>bias cell (no load)<br>Power = low<br>Power = high                                                                                          | -                                                          | 0.8<br>2.0           | 2<br>4.3                                                   | mA<br>mA                         |                                                                                        |

| PSRR <sub>OB</sub>   | Supply voltage rejection ratio                                                                                                                                                | 60                                                         | 64                   | -                                                          | dB                               |                                                                                        |

| CL                   | Load capacitance                                                                                                                                                              | -                                                          | -                    | 200                                                        | pF                               | This specification applies to the external circuit driven by the analog output buffer. |

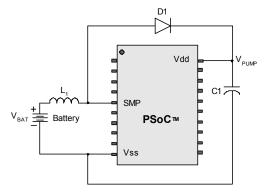

#### DC Switch Mode Pump Specifications

Table 21 lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.0 V to 3.6 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

Table 21. DC Switch Mode Pump (SMP) Specifications

| Symbol                   | Description                                                                                             | Min    | Тур  | Max  | Unit            | Notes                                                                                                                                                                           |

|--------------------------|---------------------------------------------------------------------------------------------------------|--------|------|------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>PUMP</sub> 5 V    | 5 V output voltage                                                                                      | 4.75   | 5.0  | 5.25 | V               | Configured as in Note 15. Average,<br>neglecting ripple. SMP trip voltage is<br>set to 5.0 V.                                                                                   |

| V <sub>PUMP</sub> 3 V    | 3 V output voltage                                                                                      | 3.00   | 3.25 | 3.60 | V               | Configured as in Note 15. Average,<br>neglecting ripple. SMP trip voltage is<br>set to 3.25 V.                                                                                  |

| I <sub>PUMP</sub>        | Available output current<br>$V_{BAT} = 1.5 V, V_{PUMP} = 3.25 V$<br>$V_{BAT} = 1.8 V, V_{PUMP} = 5.0 V$ | 8<br>5 |      |      | mA<br>mA        | Configured as in Note 15. SMP trip<br>voltage is set to 3.25 V.<br>SMP trip voltage is set to 5.0 V.                                                                            |

| V <sub>BAT</sub> 5 V     | Input voltage range from battery                                                                        | 1.8    | -    | 5.0  | V               | Configured as in Note 15. SMP trip voltage is set to 5.0 V.                                                                                                                     |

| V <sub>BAT</sub> 3 V     | Input voltage range from battery                                                                        | 1.0    | -    | 3.3  | V               | Configured as in Note 15. SMP trip voltage is set to 3.25 V.                                                                                                                    |

| VBATSTART                | Minimum input voltage from battery to start pump                                                        | 1.1    | -    | -    | V               | Configured as in Note 15.                                                                                                                                                       |

| $\Delta V_{PUMP}_{Line}$ | Line regulation (over V <sub>BAT</sub> range)                                                           | -      | 5    | _    | %V <sub>O</sub> | Configured as in Note 15. $V_{O}$ is the " $V_{DD}$ Value for PUMP Trip" specified by the VM[2:0] setting in the DC POR and LVD Specification, Table 25 on page 33.             |

| $\Delta V_{PUMP\_Load}$  | Load regulation                                                                                         | _      | 5    | _    | %V <sub>O</sub> | Configured as in Note 15. $V_{O}$ is the<br>" $V_{DD}$ Value for PUMP Trip" specified<br>by the VM[2:0] setting in the DC POR<br>and LVD Specification, Table 25 on<br>page 33. |

| $\Delta V_{PUMP}$ Ripple | Output voltage ripple (depends on capacitor/load)                                                       | -      | 100  | -    | mVpp            | Configured as in Note 15. Load is 5 mA.                                                                                                                                         |

| E <sub>3</sub>           | Efficiency                                                                                              | 35     | 50   | -    | %               | Configured as in Note 15. Load is 5 mA. SMP trip voltage is set to 3.25 V.                                                                                                      |

| F <sub>PUMP</sub>        | Switching frequency                                                                                     | -      | 1.3  | -    | MHz             |                                                                                                                                                                                 |

| DC <sub>PUMP</sub>       | Switching duty cycle                                                                                    | _      | 50   | -    | %               |                                                                                                                                                                                 |

#### Figure 12. Basic Switch Mode Pump Circuit

# Table 22. 5-V DC Analog Reference Specifications (continued)

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings            | Symbol             | Reference | Description                                     | Min             | Тур                     | Max                     | Unit |

|------------------------------|----------------------------------------|--------------------|-----------|-------------------------------------------------|-----------------|-------------------------|-------------------------|------|

|                              | RefPower = high<br>Opamp bias = high   | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.222   | P2[4] + 1.290           | P2[4] + 1.343           | V    |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -    |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.331   | P2[4] – 1.295           | P2[4] – 1.254           | V    |

|                              | RefPower = high<br>Opamp bias = low    | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.226   | P2[4] + 1.293           | P2[4] + 1.347           | V    |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -    |

| 0b101                        |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.331   | P2[4] – 1.298           | P2[4] – 1.259           | V    |

| 00101                        | RefPower = medium<br>Opamp bias = high | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.227   | P2[4] + 1.294           | P2[4] + 1.347           | V    |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -    |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.331   | P2[4] – 1.298           | P2[4] – 1.259           | V    |

|                              | RefPower = medium<br>Opamp bias = low  | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.228   | P2[4] + 1.295           | P2[4] + 1.349           | V    |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -    |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.332   | P2[4] – 1.299           | P2[4] – 1.260           | V    |

|                              | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.535           | 2.598                   | 2.644                   | V    |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.227           | 1.305                   | 1.398                   | V    |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.009 | V <sub>SS</sub> + 0.038 | V    |

|                              | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.530           | 2.598                   | 2.643                   | V    |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.244           | 1.303                   | 1.370                   | V    |

| 0b110                        |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.005 | V <sub>SS</sub> + 0.024 | V    |

| 00110                        | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.532           | 2.598                   | 2.644                   | V    |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.239           | 1.304                   | 1.380                   | V    |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.006 | V <sub>SS</sub> + 0.026 | V    |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.528           | 2.598                   | 2.645                   | V    |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.249           | 1.302                   | 1.362                   | V    |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.004 | V <sub>SS</sub> + 0.018 | V    |

|                              | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap                                   | 4.041           | 4.155                   | 4.234                   | V    |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap                                   | 1.998           | 2.083                   | 2.183                   | V    |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.010 | V <sub>SS</sub> + 0.038 | V    |

|                              | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap                                   | 4.047           | 4.153                   | 4.236                   | V    |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap                                   | 2.012           | 2.082                   | 2.157                   | V    |

| 0b111                        |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.006 | V <sub>SS</sub> + 0.024 | V    |

| 00111                        | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap                                   | 4.049           | 4.154                   | 4.238                   | V    |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap                                   | 2.008           | 2.083                   | 2.165                   | V    |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.006 | V <sub>SS</sub> + 0.026 | V    |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap                                   | 4.047           | 4.154                   | 4.238                   | V    |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap                                   | 2.016           | 2.081                   | 2.150                   | V    |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.004 | V <sub>SS</sub> + 0.018 | V    |

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings                  | Symbol             | Reference | Description | Min   | Тур         | Max         | Unit |

|------------------------------|----------------------------------------------|--------------------|-----------|-------------|-------|-------------|-------------|------|

|                              |                                              | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap | 2.507 | 2.598       | 2.698       | V    |

|                              | RefPower = high<br>Opamp bias = high         | V <sub>AGND</sub>  | AGND      | Bandgap     | 1.203 | 1.307       | 1.424       | V    |

|                              |                                              | $V_{REFLO}$        | Ref Low   | Vss         | Vss   | Vss + 0.012 | Vss + 0.067 | V    |

|                              |                                              | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap | 2.516 | 2.598       | 2.683       | V    |

|                              | RefPower = high<br>Opamp bias = low          | V <sub>AGND</sub>  | AGND      | Bandgap     | 1.241 | 1.303       | 1.376       | V    |

| 0b110                        |                                              | $V_{REFLO}$        | Ref Low   | Vss         | Vss   | Vss + 0.007 | Vss + 0.040 | V    |

| 00110                        |                                              | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap | 2.510 | 2.599       | 2.693       | V    |

|                              | RefPower = medium<br>Opamp bias = high       | V <sub>AGND</sub>  | AGND      | Bandgap     | 1.240 | 1.305       | 1.374       | V    |

|                              |                                              | $V_{REFLO}$        | Ref Low   | Vss         | Vss   | Vss + 0.008 | Vss + 0.048 | V    |

|                              |                                              | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap | 2.515 | 2.598       | 2.683       | V    |

|                              | RefPower = medium<br>Opamp bias = low        | V <sub>AGND</sub>  | AGND      | Bandgap     | 1.258 | 1.302       | 1.355       | V    |

|                              | • •                                          | $V_{REFLO}$        | Ref Low   | Vss         | Vss   | Vss + 0.005 | Vss + 0.03  | V    |

| 0b111                        | All power settings.<br>Not allowed for 3.3 V | -                  | -         | _           | -     | -           | _           | -    |

#### Table 23. 3.3-V DC Analog Reference Specifications

#### DC Analog PSoC Block Specifications

Table 24 lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.0 V to 3.6 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

#### Table 24. DC Analog PSoC Block Specifications

| Symbol          | Description                           | Min | Тур  | Max | Unit |

|-----------------|---------------------------------------|-----|------|-----|------|

| R <sub>CT</sub> | Resistor unit value (continuous time) | _   | 12.2 | -   | kΩ   |

| C <sub>SC</sub> | Capacitor unit value (switch cap)     | _   | 80   |     | fF   |

#### DC POR and LVD Specifications

Table 25 lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40 \degree C \le T_A \le 85 \degree C$ , or 3.0 V to 3.6 V and  $-40 \degree C \le T_A \le 85 \degree C$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

**Note** The bits PORLEV and VM in the following table refer to bits in the VLT\_CR register. See the *PSoC Programmable System-on-Chip Technical Reference Manual* for more information on the VLT\_CR register.

#### Table 25. DC POR and LVD Specifications

| Symbol                                                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Min                                                          | Тур                                                          | Max                                                                                          | Unit                                      | Notes                                                                                                            |

|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| V <sub>PPOR0R</sub><br>V <sub>PPOR1R</sub><br>V <sub>PPOR2R</sub>             | V <sub>DD</sub> value for PPOR trip (positive ramp)<br>PORLEV[1:0] = 00b<br>PORLEV[1:0] = 01b<br>PORLEV[1:0] = 10b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -<br>-<br>-                                                  | 2.91<br>4.39<br>4.55                                         |                                                                                              | >>>                                       | $V_{DD}$ must be greater than or equal to 2.5 V during startup, reset from the XRES pin, or reset from watchdog. |

| V <sub>PPOR0</sub><br>V <sub>PPOR1</sub><br>V <sub>PPOR2</sub>                | V <sub>DD</sub> value for PPOR trip (negative ramp)<br>PORLEV[1:0] = 00b<br>PORLEV[1:0] = 01b<br>PORLEV[1:0] = 10b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                              | 2.82<br>4.39<br>4.55                                         |                                                                                              | V<br>V<br>V                               |                                                                                                                  |

| V <sub>PH0</sub><br>V <sub>PH1</sub><br>V <sub>PH2</sub>                      | PPOR hysteresis<br>PORLEV[1:0] = 00b<br>PORLEV[1:0] = 01b<br>PORLEV[1:0] = 10b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                              | 92<br>0<br>0                                                 |                                                                                              | mV<br>mV<br>mV                            |                                                                                                                  |

| VLVD0<br>VLVD1<br>VLVD2<br>VLVD3<br>VLVD4<br>VLVD5<br>VLVD5<br>VLVD6<br>VLVD7 | $V_{DD} \text{ value for LVD trip} \\ VM[2:0] = 000b \\ VM[2:0] = 001b \\ VM[2:0] = 010b \\ VM[2:0] = 011b \\ VM[2:0] = 100b \\ VM[2:0] = 101b \\ VM[2:0] = 110b \\ VM[2:0] = 111b \\ VM[2:0] = 111b \\ VM[2:0] = 111b \\ VM[2:0] = 000 \\ VM$ | 2.86<br>2.96<br>3.07<br>3.92<br>4.39<br>4.55<br>4.63<br>4.72 | 2.92<br>3.02<br>3.13<br>4.00<br>4.48<br>4.64<br>4.73<br>4.81 | 2.98 <sup>[17]</sup><br>3.08<br>3.20<br>4.08<br>4.57<br>4.74 <sup>[18]</sup><br>4.82<br>4.91 | >>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>   |                                                                                                                  |

| Vpumpo<br>Vpump1<br>Vpump2<br>Vpump3<br>Vpump4<br>Vpump5<br>Vpump6<br>Vpump7  | V <sub>DD</sub> value for PUMP trip<br>VM[2:0] = 000b<br>VM[2:0] = 001b<br>VM[2:0] = 010b<br>VM[2:0] = 010b<br>VM[2:0] = 100b<br>VM[2:0] = 100b<br>VM[2:0] = 101b<br>VM[2:0] = 110b<br>VM[2:0] = 111b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.96<br>3.03<br>3.18<br>4.11<br>4.55<br>4.63<br>4.72<br>4.90 | 3.02<br>3.10<br>3.25<br>4.19<br>4.64<br>4.73<br>4.82<br>5.00 | 3.08<br>3.16<br>3.32<br>4.28<br>4.74<br>4.82<br>4.91<br>5.10                                 | V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V |                                                                                                                  |

Notes

17. Always greater than 50 mV above PPOR (PORLEV = 00) for falling supply. 18. Always greater than 50 mV above PPOR (PORLEV = 10) for falling supply.

# **AC Electrical Characteristics**

#### AC Chip-Level Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.0 V to 3.6 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

#### Table 28. AC Chip-Level Specifications

| Symbol                   | Description                                             | Min    | Тур    | Мах                      | Unit | Notes                                                                                                                                                                                                                                                                                                  |

|--------------------------|---------------------------------------------------------|--------|--------|--------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F <sub>IMO</sub>         | Internal main oscillator (IMO) frequency                | 23.4   | 24     | 24.6 <sup>[22]</sup>     | MHz  | Trimmed. Utilizing factory trim values.                                                                                                                                                                                                                                                                |

| F <sub>CPU1</sub>        | CPU frequency (5 V nominal)                             | 0.0914 | 24     | 24.6 <sup>[22]</sup>     | MHz  | Trimmed. Utilizing factory trim values. SLIMO mode = 0.                                                                                                                                                                                                                                                |

| F <sub>CPU2</sub>        | CPU frequency (3.3 V nominal)                           | 0.0914 | 12     | 12.3 <sup>[23]</sup>     | MHz  | Trimmed. Utilizing factory trim values. SLIMO mode = 0.                                                                                                                                                                                                                                                |

| F <sub>48M</sub>         | Digital PSoC block frequency                            | 0      | 48     | 49.2 <sup>[22, 24]</sup> | MHz  | Refer to AC Digital Block<br>Specifications on page 40.                                                                                                                                                                                                                                                |

| F <sub>24M</sub>         | Digital PSoC block frequency                            | 0      | 24     | 24.6 <sup>[24]</sup>     | MHz  |                                                                                                                                                                                                                                                                                                        |

| F <sub>32K1</sub>        | Internal low speed oscillator (ILO) frequency           | 15     | 32     | 64                       | kHz  |                                                                                                                                                                                                                                                                                                        |

| F <sub>32K2</sub>        | External crystal oscillator                             | -      | 32.768 | _                        | kHz  | Accuracy is capacitor and crystal dependent. 50% duty cycle.                                                                                                                                                                                                                                           |

| F <sub>32K_U</sub>       | ILO untrimmed frequency                                 | 5      | -      | 100                      | kHz  | After a reset and before the m8c<br>starts to run, the ILO is not<br>trimmed. See the System Resets<br>section of the PSoC Technical<br>Reference Manual for details on<br>timing this                                                                                                                 |

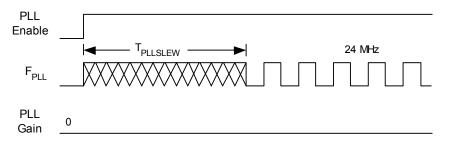

| F <sub>PLL</sub>         | PLL frequency                                           | -      | 23.986 | _                        | MHz  | Multiple (x732) of crystal frequency.                                                                                                                                                                                                                                                                  |

| t <sub>PLLSLEW</sub>     | PLL lock time                                           | 0.5    | -      | 10                       | ms   |                                                                                                                                                                                                                                                                                                        |

| t <sub>PLLSLEWSLOW</sub> | PLL lock time for low gain setting                      | 0.5    | -      | 50                       | ms   |                                                                                                                                                                                                                                                                                                        |

| t <sub>OS</sub>          | External crystal oscillator startup to 1%               | -      | 1700   | 2620                     | ms   |                                                                                                                                                                                                                                                                                                        |

| tosacc                   | External crystal oscillator startup to 100 ppm          | _      | 2800   | 3800                     | ms   | The crystal oscillator frequency is within 100 ppm of its final value by the end of the T <sub>osacc</sub> period. Correct operation assumes a properly loaded 1 $\mu$ W maximum drive level 32.768 kHz crystal. 3.0 V $\leq$ V <sub>DD</sub> $\leq$ 5.5 V, -40 °C $\leq$ T <sub>A</sub> $\leq$ 85 °C. |

| t <sub>XRST</sub>        | External reset pulse width                              | 10     | -      | _                        | μs   |                                                                                                                                                                                                                                                                                                        |

| DC <sub>24M</sub>        | 24 MHz duty cycle                                       | 40     | 50     | 60                       | %    |                                                                                                                                                                                                                                                                                                        |

| DC <sub>ILO</sub>        | ILO duty cycle                                          | 20     | 50     | 80                       | %    |                                                                                                                                                                                                                                                                                                        |

| Step <sub>24M</sub>      | 24 MHz trim step size                                   | -      | 50     | -                        | kHz  |                                                                                                                                                                                                                                                                                                        |

| t <sub>POWERUP</sub>     | Time from end of POR to CPU executing code              | -      | 16     | 100                      | ms   | wer-up from 0 V. See the System<br>Resets section of the PSoC<br>Technical Reference Manual.                                                                                                                                                                                                           |

| Fout <sub>48M</sub>      | 48 MHz output frequency                                 | 46.8   | 48.0   | 49.2 <sup>[22, 23]</sup> | MHz  | Trimmed. Utilizing factory trim values.                                                                                                                                                                                                                                                                |

| F <sub>MAX</sub>         | Maximum frequency of signal on row input or row output. | -      | -      | 12.3                     | MHz  |                                                                                                                                                                                                                                                                                                        |

| SR <sub>POWER_UP</sub>   | Power supply slew rate                                  | _      | -      | 250                      | V/ms | V <sub>DD</sub> slew rate during power-up.                                                                                                                                                                                                                                                             |

Notes

22.4.75 V <  $V_{DD}$  < 5.25 V. 23.3.0 V <  $V_{DD}$  < 3.6 V. See application note Adjusting PSoC<sup>®</sup> Trims for 3.3 V and 2.7 V Operation – AN2012 for information on trimming for operation at 3.3 V. 24. See the individual user module datasheets for information on maximum frequencies for user modules.

#### Table 28. AC Chip-Level Specifications (continued)

| Symbol                   | Description                                        | Min | Тур | Max  | Unit | Notes  |

|--------------------------|----------------------------------------------------|-----|-----|------|------|--------|

| tjit_IMO <sup>[25]</sup> | 24 MHz IMO cycle-to-cycle jitter (RMS)             | -   | 200 | 700  | ps   | N = 32 |

|                          | 24 MHz IMO long term N cycle-to-cycle jitter (RMS) | -   | 300 | 900  |      |        |

|                          | 24 MHz IMO period jitter (RMS)                     | -   | 100 | 400  |      |        |

| tjit_PLL <sup>[25]</sup> | 24 MHz IMO cycle-to-cycle jitter (RMS)             | -   | 200 | 800  | ps   | N = 32 |

|                          | 24 MHz IMO long term N cycle-to-cycle jitter (RMS) | -   | 300 | 1200 |      |        |

|                          | 24 MHz IMO period jitter (RMS)                     | -   | 100 | 700  | 1    |        |

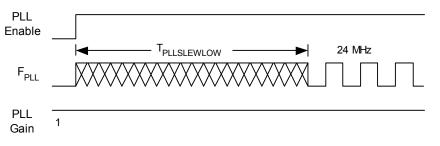

Figure 14. PLL Lock for Low Gain Setting Timing Diagram

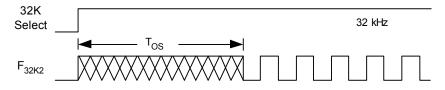

Figure 15. External Crystal Oscillator Startup Timing Diagram

Note

25. Refer to Cypress Jitter Specifications application note, Understanding Datasheet Jitter Specifications for Cypress Timing Products – AN5054 for more information.

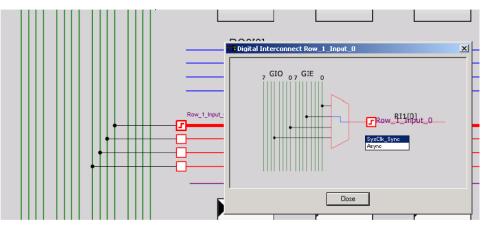

#### AC Digital Block Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.0 V to 3.6 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

Table 33. AC Digital Block Specifications

| Function                  | Description                                     | Min                | Тур                                                               | Max  | Unit | Notes                                                                                     |

|---------------------------|-------------------------------------------------|--------------------|-------------------------------------------------------------------|------|------|-------------------------------------------------------------------------------------------|

| All functions             | Block input clock frequency                     |                    |                                                                   |      |      |                                                                                           |

|                           | $V_{DD} \ge 4.75 \text{ V}$                     | -                  | -                                                                 | 49.2 | MHz  |                                                                                           |

|                           | V <sub>DD</sub> < 4.75 V                        | _                  | -                                                                 | 24.6 | MHz  |                                                                                           |

| Timer <sup>[26, 27]</sup> | Input clock frequency                           |                    |                                                                   |      |      |                                                                                           |

|                           | No capture, $V_{DD} \ge 4.75 \text{ V}$         | -                  | -                                                                 | 49.2 | MHz  |                                                                                           |

|                           | No capture, V <sub>DD</sub> < 4.75 V            | -                  | -                                                                 | 24.6 | MHz  |                                                                                           |

|                           | With capture                                    | -                  | -                                                                 | 24.6 | MHz  |                                                                                           |

|                           | Capture pulse width                             | 50 <sup>[28]</sup> | -                                                                 | -    | ns   |                                                                                           |

| Counter                   | Input clock frequency                           | •                  |                                                                   | •    | •    |                                                                                           |

|                           | No enable input, $V_{DD} \ge 4.75 \text{ V}$    | -                  | -                                                                 | 49.2 | MHz  |                                                                                           |

|                           | No enable input, V <sub>DD</sub> < 4.75 V       | -                  | -                                                                 | 24.6 | MHz  |                                                                                           |

|                           | With enable input                               | -                  | -                                                                 | 24.6 | MHz  |                                                                                           |

|                           | Enable input pulse width                        | 50 <sup>[28]</sup> | -                                                                 | -    | ns   |                                                                                           |

| Dead Band                 | Kill pulse width                                |                    |                                                                   |      |      |                                                                                           |

|                           | Asynchronous restart mode                       | 20                 | -                                                                 | -    | ns   |                                                                                           |

|                           | Synchronous restart mode                        | 50 <sup>[28]</sup> | -                                                                 | -    | ns   |                                                                                           |

|                           | Disable mode                                    | 50 <sup>[28]</sup> | -                                                                 | -    | ns   |                                                                                           |

|                           | Input clock frequency                           |                    |                                                                   |      |      |                                                                                           |

|                           | $V_{DD} \ge 4.75 \text{ V}$                     | -                  | -                                                                 | 49.2 | MHz  |                                                                                           |

|                           | V <sub>DD</sub> < 4.75 V                        | -                  | -                                                                 | 24.6 | MHz  |                                                                                           |

| CRCPRS                    | Input clock frequency                           |                    |                                                                   |      |      |                                                                                           |

| (PRS Mode)                | $V_{DD} \ge 4.75 \text{ V}$                     | -                  | -                                                                 | 49.2 | MHz  |                                                                                           |