Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | AVR                                                                        |

| Core Size                  | 8/16-Bit                                                                   |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                                |

| Data Converters            | A/D 12x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega128d4-anr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table 7-3. Number of Bytes and Pages in the EEPROM

| Devices      | Devices EEPROM |       | EEPROM Page Size E2BYTE |            | E2BYTE | E2PAGE | No of Pages |

|--------------|----------------|-------|-------------------------|------------|--------|--------|-------------|

|              | Size           | bytes |                         |            |        |        |             |

| ATxmega16D4  | 1K             | 32    | ADDR[4:0]               | ADDR[10:5] | 32     |        |             |

| ATxmega32D4  | 1K             | 32    | ADDR[4:0]               | ADDR[10:5] | 32     |        |             |

| ATxmega64D4  | 2K             | 32    | ADDR[4:0]               | ADDR[10:5] | 64     |        |             |

| ATxmega128D4 | 2К             | 32    | ADDR[4:0]               | ADDR[10:5] | 64     |        |             |

# 14. I/O Ports

# 14.1 Features

- 34 general purpose input and output pins with individual configuration

- Output driver with configurable driver and pull settings:

- Totem-pole

- Wired-AND

- Wired-OR

- Bus-keeper

- Inverted I/O

- Input with synchronous and/or asynchronous sensing with interrupts and events

- Sense both edges

- Sense rising edges

- Sense falling edges

- Sense low level

- Optional pull-up and pull-down resistor on input and Wired-OR/AND configurations

- Asynchronous pin change sensing that can wake the device from all sleep modes

- Two port interrupts with pin masking per I/O port

- Efficient and safe access to port pins

- Hardware read-modify-write through dedicated toggle/clear/set registers

- Configuration of multiple pins in a single operation

- Mapping of port registers into bit-accessible I/O memory space

- Peripheral clocks output on port pin

- Real-time counter clock output to port pin

- Event channels can be output on port pin

- Remapping of digital peripheral pin functions

- Selectable USART, SPI, and timer/counter input/output pin locations

# 14.2 Overview

One port consists of up to eight port pins: pin 0 to 7. Each port pin can be configured as input or output with configurable driver and pull settings. They also implement synchronous and asynchronous input sensing with interrupts and events for selectable pin change conditions. Asynchronous pin-change sensing means that a pin change can wake the device from all sleep modes, included the modes where no clocks are running.

All functions are individual and configurable per pin, but several pins can be configured in a single operation. The pins have hardware read-modify-write (RMW) functionality for safe and correct change of drive value and/or pull resistor configuration. The direction of one port pin can be changed without unintentionally changing the direction of any other pin.

The port pin configuration also controls input and output selection of other device functions. It is possible to have both the peripheral clock and the real-time clock output to a port pin, and available for external use. The same applies to events from the event system that can be used to synchronize and control external functions. Other digital peripherals, such as USART, SPI, and timer/counters, can be remapped to selectable pin locations in order to optimize pin-out versus application needs.

The notation of the ports are PORTA, PORTB, PORTC, PORTD, PORTE, and PORTR.

# 20. TWI – Two-Wire Interface

## 20.1 Features

- Two identical two-wire interface peripherals

- Bidirectional, two-wire communication interface

- Phillips I<sup>2</sup>C compatible

- System Management Bus (SMBus) compatible

- Bus master and slave operation supported

- Slave operation

- Single bus master operation

- Bus master in multi-master bus environment

- Multi-master arbitration

- Flexible slave address match functions

- 7-bit and general call address recognition in hardware

- 10-bit addressing supported

- Address mask register for dual address match or address range masking

- Optional software address recognition for unlimited number of addresses

- Slave can operate in all sleep modes, including power-down

- Slave address match can wake device from all sleep modes

- 100kHz and 400kHz bus frequency support

- Slew-rate limited output drivers

- Input filter for bus noise and spike suppression

- Support arbitration between start/repeated start and data bit (SMBus)

- Slave arbitration allows support for address resolve protocol (ARP) (SMBus)

# 20.2 Overview

The two-wire interface (TWI) is a bidirectional, two-wire communication interface. It is  $I^2C$  and System Management Bus (SMBus) compatible. The only external hardware needed to implement the bus is one pull-up resistor on each bus line.

A device connected to the bus must act as a master or a slave. The master initiates a data transaction by addressing a slave on the bus and telling whether it wants to transmit or receive data. One bus can have many slaves and one or several masters that can take control of the bus. An arbitration process handles priority if more than one master tries to transmit data at the same time. Mechanisms for resolving bus contention are inherent in the protocol.

The TWI module supports master and slave functionality. The master and slave functionality are separated from each other, and can be enabled and configured separately. The master module supports multi-master bus operation and arbitration. It contains the baud rate generator. Both 100kHz and 400kHz bus frequency is supported. Quick command and smart mode can be enabled to auto-trigger operations and reduce software complexity.

The slave module implements 7-bit address match and general address call recognition in hardware. 10-bit addressing is also supported. A dedicated address mask register can act as a second address match register or as a register for address range masking. The slave continues to operate in all sleep modes, including power-down mode. This enables the slave to wake up the device from all sleep modes on TWI address match. It is possible to disable the address matching to let this be handled in software instead.

The TWI module will detect START and STOP conditions, bus collisions, and bus errors. Arbitration lost, errors, collision, and clock hold on the bus are also detected and indicated in separate status flags available in both master and slave modes.

It is possible to disable the TWI drivers in the device, and enable a four-wire digital interface for connecting to an external TWI bus driver. This can be used for applications where the device operates from a different  $V_{CC}$  voltage than used by the TWI bus.

PORTC and PORTE each has one TWI. Notation of these peripherals are TWIC and TWIE.

# 28. Pinout and Pin Functions

The device pinout is shown in "Pinout/Block Diagram" on page 3. In addition to general purpose I/O functionality, each pin can have several alternate functions. This will depend on which peripheral is enabled and connected to the actual pin. Only one of the pin functions can be used at time.

# 28.1 Alternate Pin Function Description

The tables below show the notation for all pin functions available and describe its function.

### 28.1.1 Operation/Power Supply

| V <sub>CC</sub>  | Digital supply voltage |

|------------------|------------------------|

| AV <sub>CC</sub> | Analog supply voltage  |

| GND              | Ground                 |

### 28.1.2 Port Interrupt functions

| SYNC  | Port pin with full synchronous and limited asynchronous interrupt function |

|-------|----------------------------------------------------------------------------|

| ASYNC | Port pin with full synchronous and full asynchronous interrupt function    |

### 28.1.3 Analog Functions

| ACn              | Analog Comparator input pin n           |

|------------------|-----------------------------------------|

| ACnOUT           | Analog Comparator n Output              |

| ADCn             | Analog to Digital Converter input pin n |

| A <sub>REF</sub> | Analog reference input pin              |

### 28.1.4 Timer/Counter and AWEX Functions

| OCnxLS | Output Compare Channel x Low Side for Timer/Counter n  |

|--------|--------------------------------------------------------|

| OCnxHS | Output Compare Channel x High Side for Timer/Counter n |

### 28.1.5 Communication Functions

| SCL  | Serial Clock for TWI         |

|------|------------------------------|

| SDA  | Serial Data for TWI          |

| XCKn | Transfer Clock for USART n   |

| RXDn | Receiver Data for USART n    |

| TXDn | Transmitter Data for USART n |

| SS   | Slave Select for SPI         |

| MOSI | Master Out Slave In for SPI  |

| MISO | Master In Slave Out for SPI  |

| SCK  | Serial Clock for SPI         |

# **Atmel**

| PORT E | PIN # | INTERRUPT  | TCE0 | TWIE |

|--------|-------|------------|------|------|

| vcc    | 31    |            |      |      |

| PE2    | 32    | SYNC/ASYNC | OC0C |      |

| PE3    | 33    | SYNC       | OC0D |      |

### Table 28-6. Port F - Alternate Functions

| PORT R | PIN # | INTERRUPT | PDI       | XTAL  | TOSC <sup>(1)</sup> |

|--------|-------|-----------|-----------|-------|---------------------|

| PDI    | 34    |           | PDI_DATA  |       |                     |

| RESET  | 35    |           | PDI_CLOCK |       |                     |

| PRO    | 36    | SYNC      |           | XTAL2 | TOSC2               |

| PR1    | 37    | SYNC      |           | XTAL1 | TOSC1               |

Note: 1. TOSC pins can optionally be moved to PE2/PE3

| Mnemonics | Operands | Description                         | Oper                         | ation  |             | Flags       | #Clocks              |

|-----------|----------|-------------------------------------|------------------------------|--------|-------------|-------------|----------------------|

| ICALL     |          | Indirect Call to (Z)                | PC(15:0)<br>PC(21:16)        | ←<br>← | Z,<br>0     | None        | 2 / 3 <sup>(1)</sup> |

| EICALL    |          | Extended Indirect Call to (Z)       | PC(15:0)<br>PC(21:16)        | ←<br>← | Z,<br>EIND  | None        | 3 <sup>(1)</sup>     |

| CALL      | k        | call Subroutine                     | PC                           | ←      | k           | None        | 3 / 4 <sup>(1)</sup> |

| RET       |          | Subroutine Return                   | PC                           | ←      | STACK       | None        | 4 / 5 <sup>(1)</sup> |

| RETI      |          | Interrupt Return                    | PC                           | ←      | STACK       | I           | 4 / 5 <sup>(1)</sup> |

| CPSE      | Rd,Rr    | Compare, Skip if Equal              | if (Rd = Rr) PC              | ←      | PC + 2 or 3 | None        | 1/2/3                |

| CP        | Rd,Rr    | Compare                             | Rd - Rr                      |        |             | Z,C,N,V,S,H | 1                    |

| CPC       | Rd,Rr    | Compare with Carry                  | Rd - Rr - C                  |        |             | Z,C,N,V,S,H | 1                    |

| CPI       | Rd,K     | Compare with Immediate              | Rd - K                       |        |             | Z,C,N,V,S,H | 1                    |

| SBRC      | Rr, b    | Skip if Bit in Register Cleared     | if (Rr(b) = 0) PC            | ←      | PC + 2 or 3 | None        | 1/2/3                |

| SBRS      | Rr, b    | Skip if Bit in Register Set         | if (Rr(b) = 1) PC            | ←      | PC + 2 or 3 | None        | 1/2/3                |

| SBIC      | A, b     | Skip if Bit in I/O Register Cleared | if (I/O(A,b) = 0) PC         | ←      | PC + 2 or 3 | None        | 2/3/4                |

| SBIS      | A, b     | Skip if Bit in I/O Register Set     | If (I/O(A,b) =1) PC          | ~      | PC + 2 or 3 | None        | 2/3/4                |

| BRBS      | s, k     | Branch if Status Flag Set           | if (SREG(s) = 1) then PC     | ~      | PC + k + 1  | None        | 1/2                  |

| BRBC      | s, k     | Branch if Status Flag Cleared       | if (SREG(s) = 0) then PC     | ~      | PC + k + 1  | None        | 1/2                  |

| BREQ      | k        | Branch if Equal                     | if (Z = 1) then PC           | ~      | PC + k + 1  | None        | 1/2                  |

| BRNE      | k        | Branch if Not Equal                 | if (Z = 0) then PC           | ~      | PC + k + 1  | None        | 1/2                  |

| BRCS      | k        | Branch if Carry Set                 | if (C = 1) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRCC      | k        | Branch if Carry Cleared             | if (C = 0) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRSH      | k        | Branch if Same or Higher            | if (C = 0) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRLO      | k        | Branch if Lower                     | if (C = 1) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRMI      | k        | Branch if Minus                     | if (N = 1) then PC           | ~      | PC + k + 1  | None        | 1/2                  |

| BRPL      | k        | Branch if Plus                      | if (N = 0) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRGE      | k        | Branch if Greater or Equal, Signed  | if (N $\oplus$ V= 0) then PC | ←      | PC + k + 1  | None        | 1/2                  |

| BRLT      | k        | Branch if Less Than, Signed         | if (N $\oplus$ V= 1) then PC | ←      | PC + k + 1  | None        | 1/2                  |

| BRHS      | k        | Branch if Half Carry Flag Set       | if (H = 1) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRHC      | k        | Branch if Half Carry Flag Cleared   | if (H = 0) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRTS      | k        | Branch if T Flag Set                | if (T = 1) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRTC      | k        | Branch if T Flag Cleared            | if (T = 0) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRVS      | k        | Branch if Overflow Flag is Set      | if (V = 1) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRVC      | k        | Branch if Overflow Flag is Cleared  | if (V = 0) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRIE      | k        | Branch if Interrupt Enabled         | if (I = 1) then PC           | ←      | PC + k + 1  | None        | 1 / 2                |

| BRID      | k        | Branch if Interrupt Disabled        | if (I = 0) then PC           | ←      | PC + k + 1  | None        | 1 / 2                |

|           |          | Data tra                            | ansfer instructions          |        |             |             |                      |

| MOV       | Rd, Rr   | Copy Register                       | Rd                           | ←      | Rr          | None        | 1                    |

| MOVW      | Rd, Rr   | Copy Register Pair                  | Rd+1:Rd                      | ~      | Rr+1:Rr     | None        | 1                    |

| LDI       | Rd, K    | Load Immediate                      | Rd                           | ←      | К           | None        | 1                    |

| Mnemonics | Operands | Description                                         | Oper                                                                                    | ation  |                     | Flags | #Clocks             |

|-----------|----------|-----------------------------------------------------|-----------------------------------------------------------------------------------------|--------|---------------------|-------|---------------------|

| LDS       | Rd, k    | Load Direct from data space                         | Rd                                                                                      | ~      | (k)                 | None  | 2 <sup>(1)(2)</sup> |

| LD        | Rd, X    | Load Indirect                                       | Rd                                                                                      | ~      | (X)                 | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, X+   | Load Indirect and Post-Increment                    | Rd<br>X                                                                                 | ←<br>← | (X)<br>X + 1        | None  | 1(1)(2)             |

| LD        | Rd, -X   | Load Indirect and Pre-Decrement                     | $\begin{array}{l} X \leftarrow X \text{ - } 1, \\ \text{Rd} \leftarrow (X) \end{array}$ | ←<br>← | X - 1<br>(X)        | None  | 2 <sup>(1)(2)</sup> |

| LD        | Rd, Y    | Load Indirect                                       | $Rd \gets (Y)$                                                                          | ~      | (Y)                 | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, Y+   | Load Indirect and Post-Increment                    | Rd<br>Y                                                                                 | ←<br>← | (Y)<br>Y + 1        | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, -Y   | Load Indirect and Pre-Decrement                     | Y<br>Rd                                                                                 | ←<br>← | Y - 1<br>(Y)        | None  | 2 <sup>(1)(2)</sup> |

| LDD       | Rd, Y+q  | Load Indirect with Displacement                     | Rd                                                                                      | ←      | (Y + q)             | None  | 2 <sup>(1)(2)</sup> |

| LD        | Rd, Z    | Load Indirect                                       | Rd                                                                                      | ~      | (Z)                 | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, Z+   | Load Indirect and Post-Increment                    | Rd<br>Z                                                                                 | ←<br>← | (Z),<br>Z+1         | None  | 1(1)(2)             |

| LD        | Rd, -Z   | Load Indirect and Pre-Decrement                     | Z<br>Rd                                                                                 | ←<br>← | Z - 1,<br>(Z)       | None  | 2 <sup>(1)(2)</sup> |

| LDD       | Rd, Z+q  | Load Indirect with Displacement                     | Rd                                                                                      | ~      | (Z + q)             | None  | 2 <sup>(1)(2)</sup> |

| STS       | k, Rr    | Store Direct to Data Space                          | (k)                                                                                     | ←      | Rd                  | None  | 2 <sup>(1)</sup>    |

| ST        | X, Rr    | Store Indirect                                      | (X)                                                                                     | ←      | Rr                  | None  | 1 <sup>(1)</sup>    |

| ST        | X+, Rr   | Store Indirect and Post-Increment                   | (X)<br>X                                                                                | ←<br>← | Rr,<br>X + 1        | None  | 1 <sup>(1)</sup>    |

| ST        | -X, Rr   | Store Indirect and Pre-Decrement                    | X<br>(X)                                                                                | ←<br>← | X - 1,<br>Rr        | None  | 2 <sup>(1)</sup>    |

| ST        | Y, Rr    | Store Indirect                                      | (Y)                                                                                     | ~      | Rr                  | None  | 1 <sup>(1)</sup>    |

| ST        | Y+, Rr   | Store Indirect and Post-Increment                   | (Y)<br>Y                                                                                | ←<br>← | Rr,<br>Y + 1        | None  | 1 <sup>(1)</sup>    |

| ST        | -Y, Rr   | Store Indirect and Pre-Decrement                    | Y<br>(Y)                                                                                | ←<br>← | Y - 1,<br>Rr        | None  | 2 <sup>(1)</sup>    |

| STD       | Y+q, Rr  | Store Indirect with Displacement                    | (Y + q)                                                                                 | ←      | Rr                  | None  | 2 <sup>(1)</sup>    |

| ST        | Z, Rr    | Store Indirect                                      | (Z)                                                                                     | ←      | Rr                  | None  | 1 <sup>(1)</sup>    |

| ST        | Z+, Rr   | Store Indirect and Post-Increment                   | (Z)<br>Z                                                                                | ←<br>← | Rr<br>Z + 1         | None  | 1 <sup>(1)</sup>    |

| ST        | -Z, Rr   | Store Indirect and Pre-Decrement                    | Z                                                                                       | ~      | Z - 1               | None  | 2 <sup>(1)</sup>    |

| STD       | Z+q,Rr   | Store Indirect with Displacement                    | (Z + q)                                                                                 | ←      | Rr                  | None  | 2 <sup>(1)</sup>    |

| LPM       |          | Load Program Memory                                 | R0                                                                                      | ~      | (Z)                 | None  | 3                   |

| LPM       | Rd, Z    | Load Program Memory                                 | Rd                                                                                      | ~      | (Z)                 | None  | 3                   |

| LPM       | Rd, Z+   | Load Program Memory and Post-Increment              | Rd<br>Z                                                                                 | ←<br>← | (Z),<br>Z + 1       | None  | 3                   |

| ELPM      |          | Extended Load Program Memory                        | R0                                                                                      | ←      | (RAMPZ:Z)           | None  | 3                   |

| ELPM      | Rd, Z    | Extended Load Program Memory                        | Rd                                                                                      | ←      | (RAMPZ:Z)           | None  | 3                   |

| ELPM      | Rd, Z+   | Extended Load Program Memory and Post-<br>Increment | Rd<br>Z                                                                                 | ←<br>← | (RAMPZ:Z),<br>Z + 1 | None  | 3                   |

| SPM       |          | Store Program Memory                                | (RAMPZ:Z)                                                                               | ←      | R1:R0               | None  | -                   |

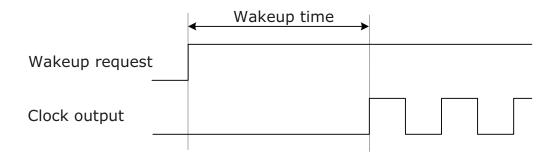

### 32.1.4 Wake-up Time from Sleep Modes

|                    |         | - 32-0. Device wake-up time from Sleep modes with various system clock sources                                          |                               |      |                     |      |  |  |  |

|--------------------|---------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------|------|---------------------|------|--|--|--|

|                    | Symbol  | Parameter                                                                                                               | Condition                     | Min. | Typ. <sup>(1)</sup> | Max. |  |  |  |

|                    |         |                                                                                                                         | External 2MHz clock           |      | 2.0                 |      |  |  |  |

|                    |         | Wake-up time from idle,<br>standby, and extended standby<br>mode<br>Wake-up time from power-save<br>and power-down mode | 32.768kHz internal oscillator |      | 120                 |      |  |  |  |

|                    |         |                                                                                                                         | 2MHz internal oscillator      |      | 2.0                 |      |  |  |  |

|                    | +       |                                                                                                                         | 32MHz internal oscillator     |      | 0.2                 |      |  |  |  |

| <sup>L</sup> wakeu | Lwakeup |                                                                                                                         | External 2MHz clock           |      | 5.0                 |      |  |  |  |

|                    |         |                                                                                                                         | 32.768kHz internal oscillator |      | 320                 |      |  |  |  |

|                    |         |                                                                                                                         | 2MHz internal oscillator      |      | 9.0                 |      |  |  |  |

32MHz internal oscillator

| Table 32-6. | Device Wake-up | Time from Sleep | Modes with | Various Sys | stem Clock Sources |

|-------------|----------------|-----------------|------------|-------------|--------------------|

|-------------|----------------|-----------------|------------|-------------|--------------------|

#### Note: 1. The wake-up time is the time from the wake-up request is given until the peripheral clock is available on pin, see Figure 32-2. All peripherals and modules start execution from the first clock cycle, expect the CPU that is halted for four clock cycles before program execution starts.

### Figure 32-2. Wake-up Time Definition

Units

μs

5.0

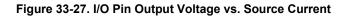

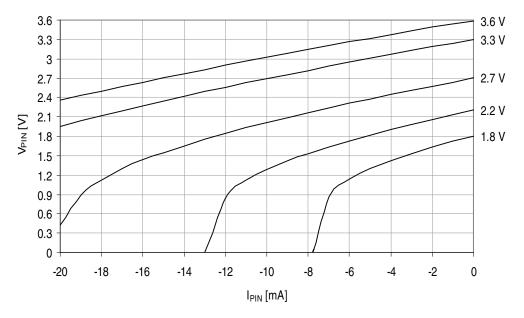

### 32.3.5 I/O Pin Characteristics

The I/O pins complies with the JEDEC LVTTL and LVCMOS specification and the high- and low level input and output voltage limits reflect or exceed this specification.

### Table 32-63. I/O Pin Characteristics

| Symbol                                                             | Parameter                   | Con                          | dition                 | Min.                | Тур.                 | Max.                 | Units |

|--------------------------------------------------------------------|-----------------------------|------------------------------|------------------------|---------------------|----------------------|----------------------|-------|

| I <sub>OH</sub> <sup>(1)</sup> /<br>I <sub>OL</sub> <sup>(2)</sup> | I/O pin source/sink current |                              |                        | -15                 |                      | 15                   | mA    |

|                                                                    |                             | V <sub>CC</sub> = 2.7 - 3.6V |                        | 2                   |                      | V <sub>CC</sub> +0.3 | V     |

| V <sub>IH</sub>                                                    | High level input voltage    | V <sub>CC</sub> = 2.0 - 2.7V |                        | 0.7*V <sub>CC</sub> |                      | V <sub>CC</sub> +0.3 |       |

|                                                                    |                             | V <sub>CC</sub> = 1.6 - 2.0V |                        | 0.7*V <sub>CC</sub> |                      | V <sub>CC</sub> +0.3 |       |

|                                                                    | Low level input voltage     | V <sub>CC</sub> = 2.7- 3.6V  |                        | -0.3                |                      | 0.3*V <sub>CC</sub>  |       |

| V <sub>IL</sub>                                                    |                             | V <sub>CC</sub> = 2.0 - 2.7V |                        | -0.3                |                      | 0.3*V <sub>CC</sub>  |       |

|                                                                    |                             | V <sub>CC</sub> = 1.6 - 2.0V |                        | -0.3                |                      | 0.3*V <sub>CC</sub>  |       |

|                                                                    | High level output voltage   | V <sub>CC</sub> = 3.0 - 3.6V | I <sub>OH</sub> = -2mA | 2.4                 | 0.94*V <sub>CC</sub> |                      |       |

| V <sub>OH</sub>                                                    |                             | V <sub>CC</sub> = 3.3V       | I <sub>OH</sub> = -4mA | 2.6                 | 2.9                  |                      |       |

| ¥ OH                                                               |                             | V <sub>CC</sub> = 3.0V       | I <sub>OH</sub> = -3mA | 2.1                 | 2.6                  |                      |       |

|                                                                    |                             | V <sub>CC</sub> = 1.8V       | I <sub>OH</sub> = -1mA | 1.4                 | 1.6                  |                      |       |

|                                                                    | Low level output voltage    | V <sub>CC</sub> = 3.0 - 3.6V | I <sub>OL</sub> = 2mA  |                     | 0.05*V <sub>CC</sub> | 0.4                  |       |

| V <sub>OL</sub>                                                    |                             | V <sub>CC</sub> = 3.3V       | I <sub>OL</sub> = 8mA  |                     | 0.4                  | 0.76                 |       |

| ♥ OL                                                               |                             | V <sub>CC</sub> = 3.0V       | I <sub>OL</sub> = 5mA  |                     | 0.3                  | 0.64                 |       |

|                                                                    |                             | V <sub>CC</sub> = 1.8V       | I <sub>OL</sub> = 3mA  |                     | 0.2                  | 0.46                 |       |

| I <sub>IN</sub>                                                    | Input leakage current       | T = 25°C                     |                        |                     | <0.001               | 0.1                  | μA    |

| R <sub>P</sub>                                                     | Pull/Buss keeper resistor   |                              |                        |                     | 24                   |                      | kΩ    |

| t <sub>r</sub>                                                     | Rise time                   | No load                      |                        |                     | 4                    |                      | ns    |

Notes:

1. The sum of all I<sub>OH</sub> for PORTA and PORTB must not exceed 100mA. The sum of all I<sub>OH</sub> for PORTC must not exceed 200mA. The sum of all I<sub>OH</sub> for PORTD and pins PE[0-1] on PORTE must not exceed 200mA. The sum of all I<sub>OH</sub> for PE[2-3] on PORTE, PORTR and PDI must not exceed 100mA.

2.

The sum of all  $I_{OL}$  for PORTC must not exceed 200mA. The sum of all  $I_{OL}$  for PORTC must not exceed 200mA. The sum of all  $I_{OL}$  for PORTC must not exceed 200mA. The sum of all  $I_{OL}$  for PORTD and pins PE[0-1] on PORTE must not exceed 200mA. The sum of all  $I_{OL}$  for PE[2-3] on PORTE, PORTR and PDI must not exceed 100mA.

### Table 32-74. Programming Time

| Symbol | Parameter                   | Condition                                        | Min. | <b>Typ.</b> <sup>(1)</sup> | Max. | Units |

|--------|-----------------------------|--------------------------------------------------|------|----------------------------|------|-------|

|        | Chip erase                  | 64KB Flash, EEPROM <sup>(2)</sup> and SRAM erase |      | 55                         |      | ms    |

| Flash  | Page erase                  |                                                  | 4    |                            |      |       |

|        | Flash                       | Page write                                       |      | 4                          |      |       |

|        | Atomic Page Erase and write |                                                  | 8    |                            |      |       |

| EEPROM |                             | Page erase                                       |      | 4                          |      |       |

|        | EEPROM                      | Page write                                       |      | 4                          |      |       |

|        |                             | Atomic Page erase and write                      |      | 8                          |      |       |

Notes: 1. Programming is timed from the 2MHz internal oscillator.

2. EEPROM is not erased if the EESAVE fuse is programmed.

### 32.3.13 Clock and Oscillator Characteristics

### 32.3.13.1 Calibrated 32.768kHz Internal Oscillator Characteristics

### Table 32-75. 32.768kHz Internal Oscillator Characteristics

| Symbol | Parameter                    | Condition                        | Min. | Тур.   | Max. | Units |

|--------|------------------------------|----------------------------------|------|--------|------|-------|

|        | Frequency                    |                                  |      | 32.768 |      | kHz   |

|        | Factory calibration accuracy | T = 85°C, V <sub>CC</sub> = 3.0V | -0.5 |        | 0.5  | %     |

|        | User calibration accuracy    |                                  | -0.5 |        | 0.5  | /0    |

### 32.3.13.2 Calibrated 2MHz RC Internal Oscillator Characteristics

### Table 32-76. 2MHz Internal Oscillator Characteristics

| Symbol | Parameter                    | Condition                                                    | Min. | Тур. | Max. | Units |

|--------|------------------------------|--------------------------------------------------------------|------|------|------|-------|

|        | Frequency range              | DFLL can tune to this frequency over voltage and temperature | 1.8  |      | 2.2  | MHz   |

|        | Factory calibrated frequency |                                                              |      | 2.0  |      |       |

|        | Factory calibration accuracy | T = 85°C, V <sub>CC</sub> = 3.0V                             | -1.5 |      | 1.5  |       |

|        | User calibration accuracy    |                                                              | -0.2 |      | 0.2  | %     |

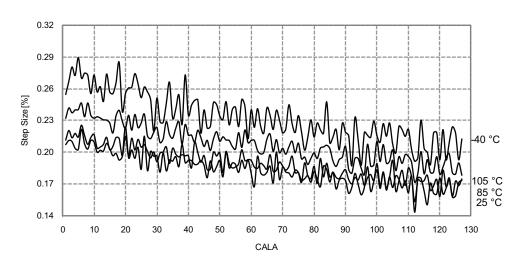

|        | DFLL calibration stepsize    |                                                              |      | 0.21 |      |       |

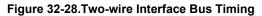

### 32.4.15 Two-Wire Interface Characteristics

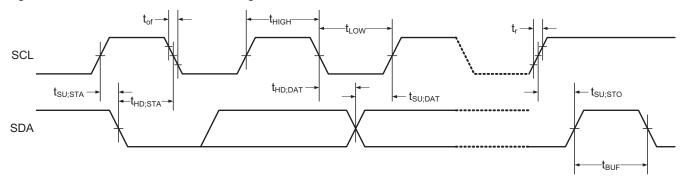

Table 32-114 describes the requirements for devices connected to the Two-Wire Interface Bus. The Atmel AVR XMEGA Two-Wire Interface meets or exceeds these requirements under the noted conditions. Timing symbols refer to Figure 32-28.

### Table 32-114. Two-wire Interface Characteristics

| Symbol           | Parameter                                                      | Condition                                                         | Min.                                   | Тур. | Max.                 | Units |

|------------------|----------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------|------|----------------------|-------|

| V <sub>IH</sub>  | Input high voltage                                             |                                                                   | 0.7*V <sub>CC</sub>                    |      | V <sub>CC</sub> +0.5 |       |

| V <sub>IL</sub>  | Input low voltage                                              |                                                                   | -0.5                                   |      | 0.3*V <sub>CC</sub>  | V     |

| V <sub>hys</sub> | Hysteresis of Schmitt Trigger Inputs                           |                                                                   | 0.05*V <sub>CC</sub> <sup>(1)</sup>    |      |                      | v     |

| V <sub>OL</sub>  | Output low voltage                                             | 3mA, sink current                                                 | 0                                      |      | 0.4                  |       |

| t <sub>r</sub>   | Rise time for both SDA and SCL                                 |                                                                   | 20+0.1C <sub>b</sub> <sup>(1)(2)</sup> |      | 300                  |       |

| t <sub>of</sub>  | Output fall time from $V_{\text{IHmin}}$ to $V_{\text{ILmax}}$ | $10pF < C_b < 400pF^{(2)}$                                        | 20+0.1C <sub>b</sub> <sup>(1)(2)</sup> |      | 250                  | ns    |

| t <sub>SP</sub>  | Spikes suppressed by input filter                              |                                                                   | 0                                      |      | 50                   |       |

| I <sub>I</sub>   | Input current for each I/O pin                                 | $0.1V_{CC} < V_{I} < 0.9V_{CC}$                                   | -10                                    |      | 10                   | μA    |

| CI               | Capacitance for each I/O pin                                   |                                                                   |                                        |      | 10                   | pF    |

| f <sub>SCL</sub> | SCL clock frequency                                            | f <sub>PER</sub> <sup>(3)</sup> >max(10f <sub>SCL</sub> , 250kHz) | 0                                      |      | 400                  | kHz   |

| R <sub>₽</sub>   | Value of pull-up resistor                                      | $f_{SCL} \leq 100 kHz$                                            | $V_{CC} - 0.4V$                        |      | $\frac{100ns}{C_b}$  | Ω     |

| ГЪр              |                                                                | f <sub>SCL</sub> > 100kHz                                         | 3 <i>mA</i>                            |      | $\frac{300ns}{C_b}$  | 32    |

Figure 33-28. I/O Pin Output Voltage vs. Sink Current  $V_{CC} = 1.8V$

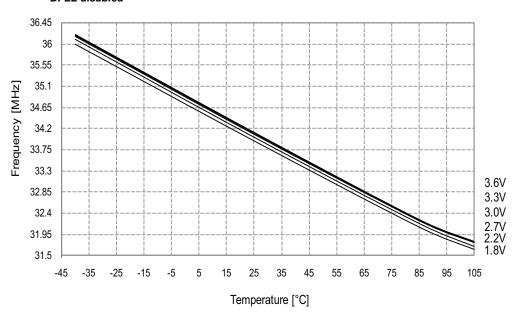

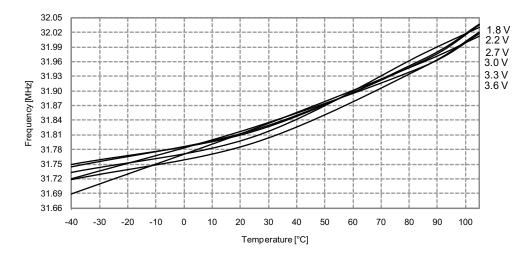

Figure 33-71. 32MHz Internal Oscillator Frequency vs. Temperature DFLL disabled

# **Atmel**

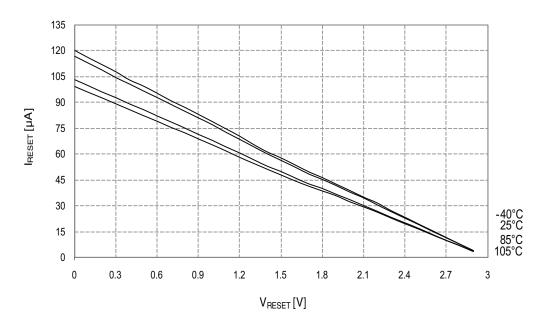

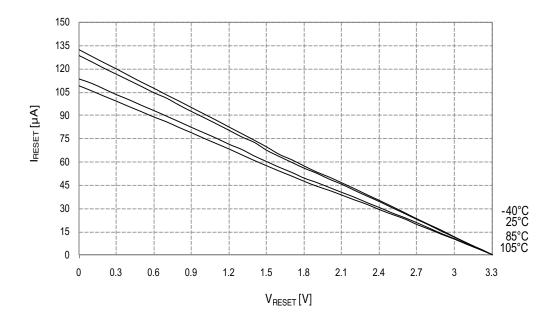

Figure 33-138. Reset Pin Pull-up Resistor Current vs. Reset Pin Voltage  $V_{CC} = 3.0V$

Figure 33-139. Reset Pin Pull-up Resistor Current vs. Reset Pin Voltage  $V_{CC} = 3.3V$

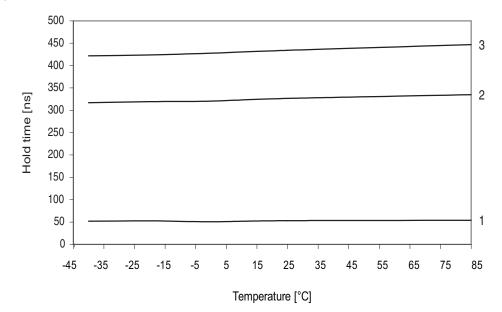

### 33.2.10 Two-Wire Interface Characteristics

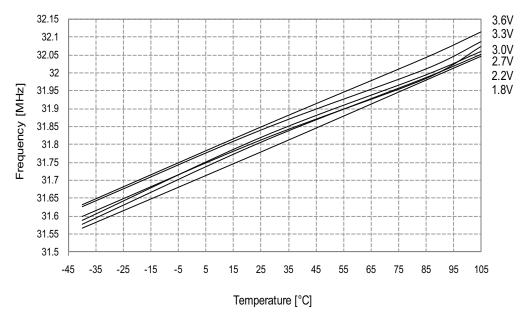

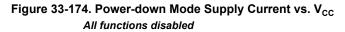

### 33.3.1.3 Power-down Mode Supply Current

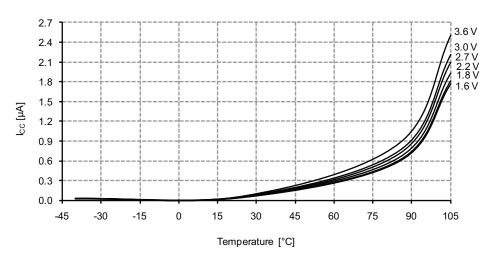

### Figure 33-173. Power-down Mode Supply Current vs. Temperature All functions disabled

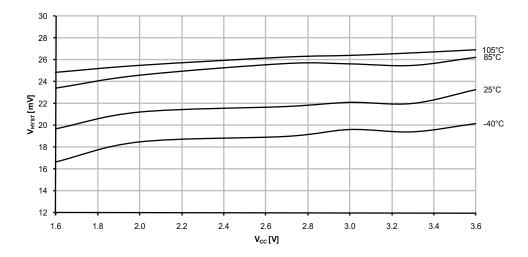

Figure 33-295. Analog Comparator Hysteresis vs. V<sub>CC</sub> Low power, small hysteresis

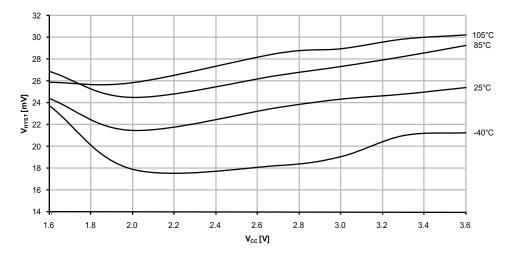

Figure 33-296. Analog Comparator Hysteresis vs. V<sub>CC</sub> High-speed mode, large hysteresis

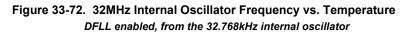

Figure 33-319. 32MHz Internal Oscillator Frequency vs. Temperature DFLL enabled, from the 32.768kHz internal oscillator

Figure 33-320. 32MHz Internal Oscillator CALA Calibration Step Size  $V_{cc} = 3.0V$