Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2000.00                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | AVR                                                                       |

| Core Size                  | 8/16-Bit                                                                  |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 34                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 4K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                               |

| Data Converters            | A/D 12x12b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 44-VQFN (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega32d4-mnr |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

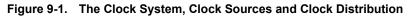

### 9.3 Clock Sources

The clock sources are divided in two main groups: internal oscillators and external clock sources. Most of the clock sources can be directly enabled and disabled from software, while others are automatically enabled or disabled, depending on peripheral settings. After reset, the device starts up running from the 2MHz internal oscillator. The other clock sources, DFLLs and PLL, are turned off by default.

The internal oscillators do not require any external components to run. For details on characteristics and accuracy of the internal oscillators, refer to the device datasheet.

#### 9.3.1 32kHz Ultra Low Power Internal Oscillator

This oscillator provides an approximate 32kHz clock. The 32kHz ultra low power (ULP) internal oscillator is a very low power clock source, and it is not designed for high accuracy. The oscillator employs a built-in prescaler that provides a

#### 10.3.3 Power-save Mode

Power-save mode is identical to power down, with one exception. If the real-time counter (RTC) is enabled, it will keep running during sleep, and the device can also wake up from either an RTC overflow or compare match interrupt.

#### 10.3.4 Standby Mode

Standby mode is identical to power down, with the exception that the enabled system clock sources are kept running while the CPU, peripheral, and RTC clocks are stopped. This reduces the wake-up time.

#### 10.3.5 Extended Standby Mode

Extended standby mode is identical to power-save mode, with the exception that the enabled system clock sources are kept running while the CPU and peripheral clocks are stopped. This reduces the wake-up time.

## 11. System Control and Reset

## 11.1 Features

- Reset the microcontroller and set it to initial state when a reset source goes active

- Multiple reset sources that cover different situations

- Power-on reset

- External reset

- Watchdog reset

- Brownout reset

- PDI reset

- Software reset

- Asynchronous operation

- No running system clock in the device is required for reset

- Reset status register for reading the reset source from the application code

## 11.2 Overview

The reset system issues a microcontroller reset and sets the device to its initial state. This is for situations where operation should not start or continue, such as when the microcontroller operates below its power supply rating. If a reset source goes active, the device enters and is kept in reset until all reset sources have released their reset. The I/O pins are immediately tri-stated. The program counter is set to the reset vector location, and all I/O registers are set to their initial values. The SRAM content is kept. However, if the device accesses the SRAM when a reset occurs, the content of the accessed location can not be guaranteed.

After reset is released from all reset sources, the default oscillator is started and calibrated before the device starts running from the reset vector address. By default, this is the lowest program memory address, 0, but it is possible to move the reset vector to the lowest address in the boot section.

The reset functionality is asynchronous, and so no running system clock is required to reset the device. The software reset feature makes it possible to issue a controlled system reset from the user software.

The reset status register has individual status flags for each reset source. It is cleared at power-on reset, and shows which sources have issued a reset since the last power-on.

## 11.3 Reset Sequence

A reset request from any reset source will immediately reset the device and keep it in reset as long as the request is active. When all reset requests are released, the device will go through three stages before the device starts running again:

- Reset counter delay

- Oscillator startup

- Oscillator calibration

If another reset requests occurs during this process, the reset sequence will start over again.

## 14. I/O Ports

## 14.1 Features

- 34 general purpose input and output pins with individual configuration

- Output driver with configurable driver and pull settings:

- Totem-pole

- Wired-AND

- Wired-OR

- Bus-keeper

- Inverted I/O

- Input with synchronous and/or asynchronous sensing with interrupts and events

- Sense both edges

- Sense rising edges

- Sense falling edges

- Sense low level

- Optional pull-up and pull-down resistor on input and Wired-OR/AND configurations

- Asynchronous pin change sensing that can wake the device from all sleep modes

- Two port interrupts with pin masking per I/O port

- Efficient and safe access to port pins

- Hardware read-modify-write through dedicated toggle/clear/set registers

- Configuration of multiple pins in a single operation

- Mapping of port registers into bit-accessible I/O memory space

- Peripheral clocks output on port pin

- Real-time counter clock output to port pin

- Event channels can be output on port pin

- Remapping of digital peripheral pin functions

- Selectable USART, SPI, and timer/counter input/output pin locations

## 14.2 Overview

One port consists of up to eight port pins: pin 0 to 7. Each port pin can be configured as input or output with configurable driver and pull settings. They also implement synchronous and asynchronous input sensing with interrupts and events for selectable pin change conditions. Asynchronous pin-change sensing means that a pin change can wake the device from all sleep modes, included the modes where no clocks are running.

All functions are individual and configurable per pin, but several pins can be configured in a single operation. The pins have hardware read-modify-write (RMW) functionality for safe and correct change of drive value and/or pull resistor configuration. The direction of one port pin can be changed without unintentionally changing the direction of any other pin.

The port pin configuration also controls input and output selection of other device functions. It is possible to have both the peripheral clock and the real-time clock output to a port pin, and available for external use. The same applies to events from the event system that can be used to synchronize and control external functions. Other digital peripherals, such as USART, SPI, and timer/counters, can be remapped to selectable pin locations in order to optimize pin-out versus application needs.

The notation of the ports are PORTA, PORTB, PORTC, PORTD, PORTE, and PORTR.

## 28.2 Alternate Pin Functions

The tables below show the primary/default function for each pin on a port in the first column, the pin number in the second column, and then all alternate pin functions in the remaining columns. The head row shows what peripheral that enable and use the alternate pin functions.

For better flexibility, some alternate functions also have selectable pin locations for their functions, this is noted under the first table where this apply.

| PORT A | PIN# | INTERRUPT  | ADCA<br>POS/GAINPOS | ADCA<br>NEG | ADCA<br>GAINNEG | ACAPOS | ACANEG | ACAOUT | REFA |

|--------|------|------------|---------------------|-------------|-----------------|--------|--------|--------|------|

| GND    | 38   |            |                     |             |                 |        |        |        |      |

| AVCC   | 39   |            |                     |             |                 |        |        |        |      |

| PA0    | 40   | SYNC       | ADC0                | ADC0        |                 | AC0    | AC0    |        | AREF |

| PA1    | 41   | SYNC       | ADC1                | ADC1        |                 | AC1    | AC1    |        |      |

| PA2    | 42   | SYNC/ASYNC | ADC2                | ADC2        |                 | AC2    |        |        |      |

| PA3    | 43   | SYNC       | ADC3                | ADC3        |                 | AC3    | AC3    |        |      |

| PA4    | 44   | SYNC       | ADC4                |             | ADC4            | AC4    |        |        |      |

| PA5    | 1    | SYNC       | ADC5                |             | ADC5            | AC5    | AC5    |        |      |

| PA6    | 2    | SYNC       | ADC6                |             | ADC6            | AC6    |        |        |      |

| PA7    | 3    | SYNC       | ADC7                |             | ADC7            |        | AC7    | AC0OUT |      |

#### Table 28-1. Port A - Alternate Functions

#### Table 28-2. Port B - Alternate Functions

| PORT B | PIN# | INTERRUPT  | ADCAPOS/GAINPOS | REFB |

|--------|------|------------|-----------------|------|

| PB0    | 4    | SYNC       | ADC8            | AREF |

| PB1    | 5    | SYNC       | ADC9            |      |

| PB2    | 6    | SYNC/ASYNC | ADC10           |      |

| PB3    | 7    | SYNC       | ADC11           |      |

# 30. Instruction Set Summary

| Mnemonics | Operands | Description                              | Oper                   | ation  |                  | Flags       | #Clock               |

|-----------|----------|------------------------------------------|------------------------|--------|------------------|-------------|----------------------|

|           |          | Arithmetic a                             | and Logic Instructions |        |                  |             |                      |

| ADD       | Rd, Rr   | Add without Carry                        | Rd                     | ←      | Rd + Rr          | Z,C,N,V,S,H | 1                    |

| ADC       | Rd, Rr   | Add with Carry                           | Rd                     | ←      | Rd + Rr + C      | Z,C,N,V,S,H | 1                    |

| ADIW      | Rd, K    | Add Immediate to Word                    | Rd                     | ←      | Rd + 1:Rd + K    | Z,C,N,V,S   | 2                    |

| SUB       | Rd, Rr   | Subtract without Carry                   | Rd                     | ←      | Rd - Rr          | Z,C,N,V,S,H | 1                    |

| SUBI      | Rd, K    | Subtract Immediate                       | Rd                     | ←      | Rd - K           | Z,C,N,V,S,H | 1                    |

| SBC       | Rd, Rr   | Subtract with Carry                      | Rd                     | ←      | Rd - Rr - C      | Z,C,N,V,S,H | 1                    |

| SBCI      | Rd, K    | Subtract Immediate with Carry            | Rd                     | ←      | Rd - K - C       | Z,C,N,V,S,H | 1                    |

| SBIW      | Rd, K    | Subtract Immediate from Word             | Rd + 1:Rd              | ←      | Rd + 1:Rd - K    | Z,C,N,V,S   | 2                    |

| AND       | Rd, Rr   | Logical AND                              | Rd                     | ←      | Rd • Rr          | Z,N,V,S     | 1                    |

| ANDI      | Rd, K    | Logical AND with Immediate               | Rd                     | ←      | Rd • K           | Z,N,V,S     | 1                    |

| OR        | Rd, Rr   | Logical OR                               | Rd                     | ~      | Rd v Rr          | Z,N,V,S     | 1                    |

| ORI       | Rd, K    | Logical OR with Immediate                | Rd                     | ←      | Rd v K           | Z,N,V,S     | 1                    |

| EOR       | Rd, Rr   | Exclusive OR                             | Rd                     | ←      | Rd ⊕ Rr          | Z,N,V,S     | 1                    |

| СОМ       | Rd       | One's Complement                         | Rd                     | ←      | \$FF - Rd        | Z,C,N,V,S   | 1                    |

| NEG       | Rd       | Two's Complement                         | Rd                     | ←      | \$00 - Rd        | Z,C,N,V,S,H | 1                    |

| SBR       | Rd,K     | Set Bit(s) in Register                   | Rd                     | ←      | Rd v K           | Z,N,V,S     | 1                    |

| CBR       | Rd,K     | Clear Bit(s) in Register                 | Rd                     | ←      | Rd • (\$FFh - K) | Z,N,V,S     | 1                    |

| INC       | Rd       | Increment                                | Rd                     | ←      | Rd + 1           | Z,N,V,S     | 1                    |

| DEC       | Rd       | Decrement                                | Rd                     | ←      | Rd - 1           | Z,N,V,S     | 1                    |

| тэт       | Rd       | Test for Zero or Minus                   | Rd                     | ←      | Rd • Rd          | Z,N,V,S     | 1                    |

| CLR       | Rd       | Clear Register                           | Rd                     | ←      | $Rd \oplus Rd$   | Z,N,V,S     | 1                    |

| SER       | Rd       | Set Register                             | Rd                     | ←      | \$FF             | None        | 1                    |

| MUL       | Rd,Rr    | Multiply Unsigned                        | R1:R0                  | ←      | Rd x Rr (UU)     | Z,C         | 2                    |

| MULS      | Rd,Rr    | Multiply Signed                          | R1:R0                  | ←      | Rd x Rr (SS)     | Z,C         | 2                    |

| MULSU     | Rd,Rr    | Multiply Signed with Unsigned            | R1:R0                  | ←      | Rd x Rr (SU)     | Z,C         | 2                    |

| FMUL      | Rd,Rr    | Fractional Multiply Unsigned             | R1:R0                  | ←      | Rd x Rr<<1 (UU)  | Z,C         | 2                    |

| FMULS     | Rd,Rr    | Fractional Multiply Signed               | R1:R0                  | ←      | Rd x Rr<<1 (SS)  | Z,C         | 2                    |

| FMULSU    | Rd,Rr    | Fractional Multiply Signed with Unsigned | R1:R0                  | ←      | Rd x Rr<<1 (SU)  | Z,C         | 2                    |

|           |          | Bran                                     | ch instructions        |        |                  |             |                      |

| RJMP      | k        | Relative Jump                            | PC                     | ←      | PC + k + 1       | None        | 2                    |

| JMP       |          | Indirect Jump to (Z)                     | PC(15:0)<br>PC(21:16)  | ←<br>← | Z,<br>0          | None        | 2                    |

| EIJMP     |          | Extended Indirect Jump to (Z)            | PC(15:0)<br>PC(21:16)  | ←<br>← | Z,<br>EIND       | None        | 2                    |

| JMP       | k        | Jump                                     | PC                     | ←      | k                | None        | 3                    |

| RCALL     | k        | Relative Call Subroutine                 | PC                     | ←      | PC + k + 1       | None        | 2 / 3 <sup>(1)</sup> |

#### 32.2.13.5 Internal Phase Locked Loop (PLL) Characteristics

### Table 32-51. Internal PLL Characteristics

| Symbol           | Parameter                       | Condition                                                 | Min. | Тур. | Max. | Units |

|------------------|---------------------------------|-----------------------------------------------------------|------|------|------|-------|

| f <sub>IN</sub>  | Input frequency                 | Output frequency must be within $\mathbf{f}_{\text{OUT}}$ | 0.4  |      | 64   |       |

| f <sub>OUT</sub> | Output frequency <sup>(1)</sup> | V <sub>CC</sub> = 1.6 - 1.8V                              | 20   |      | 48   | MHz   |

|                  |                                 | V <sub>CC</sub> = 2.7 - 3.6V                              | 20   |      | 128  |       |

|                  | Start-up time                   |                                                           |      | 25   |      |       |

|                  | Re-lock time                    |                                                           |      | 25   |      | μs    |

Note: 1. The maximum output frequency vs. supply voltage is linear between 1.8V and 2.7V, and can never be higher than four times the maximum CPU frequency.

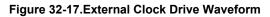

#### 32.2.13.6External Clock Characteristics

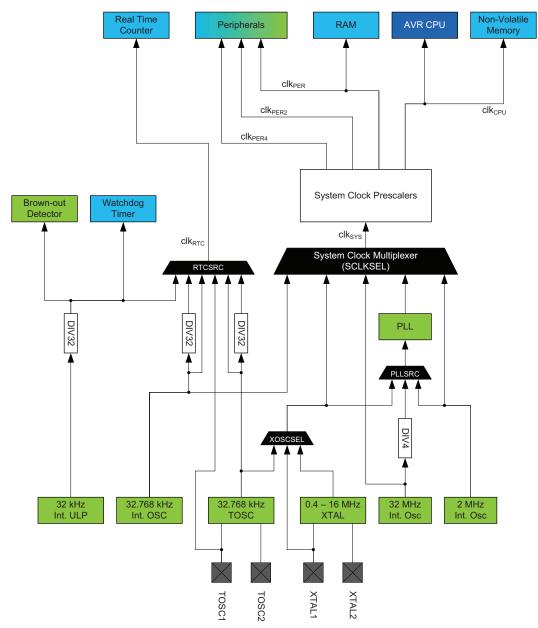

#### Figure 32-10. External Clock Drive Waveform

#### Table 32-52. External Clock<sup>(1)</sup>

| Symbol             | Parameter                                                 | Condition                    | Min.   | Тур.          | Max.   | Units |

|--------------------|-----------------------------------------------------------|------------------------------|--------|---------------|--------|-------|

| 1 /4               | Clock frequency <sup>(2)</sup>                            | V <sub>CC</sub> = 1.6 - 1.8V | 0      |               | 90     | MHz   |

| 1/t <sub>CK</sub>  |                                                           | V <sub>CC</sub> = 2.7 - 3.6V | 0      |               | 142    |       |

| +                  | Clock period                                              | V <sub>CC</sub> = 1.6 - 1.8V | 11     |               |        |       |

| t <sub>ск</sub>    |                                                           | V <sub>CC</sub> = 2.7 - 3.6V | 7.0    |               |        |       |

| +                  | Clock high/low time                                       | V <sub>CC</sub> = 1.6 - 1.8V | 4.5    |               |        | ns    |

| t <sub>CH/CL</sub> |                                                           | V <sub>CC</sub> = 2.7 - 3.6V | 2.4    |               |        |       |

| V <sub>IL/IH</sub> | Low/high level input voltage                              |                              | See Ta | ble 32-7 on p | age 69 | V     |

| $\Delta t_{CK}$    | Reduction in period time from one clock cycle to the next |                              |        |               | 10     | %     |

Notes: 1. System Clock Prescalers must be set so that maximum CPU clock frequency for device is not exceeded.

2. The maximum frequency vs. supply voltage is linear between 1.8V and 2.7V, and the same applies for all other parameters with supply voltage conditions.

#### Table 32-66. Accuracy Characteristics

| Symbol             | Parameter                  |                      | Condition <sup>(2)</sup>                                              | Min. | Тур.  | Max. | Units     |

|--------------------|----------------------------|----------------------|-----------------------------------------------------------------------|------|-------|------|-----------|

| RES                | Resolution                 | Programmab           | le to 8 or 12 bit                                                     | 8    | 12    | 12   | Bits      |

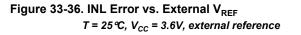

|                    |                            | Foliana              | $V_{\rm CC}$ -1.0V < $V_{\rm REF}$ < $V_{\rm CC}$ -0.6V               |      | ±1.2  | ±3   |           |

| INL <sup>(1)</sup> | Integral non-linearity     | 50ksps               | All V <sub>REF</sub>                                                  |      | ±1.5  | ±4   |           |

|                    | Integral non-inteanty      | 200ksps              | $V_{\rm CC}$ -1.0V < $V_{\rm REF}$ < $V_{\rm CC}$ -0.6V               |      | ±1.0  | ±3   | lsb       |

|                    |                            | 2006505              | All V <sub>REF</sub>                                                  |      | ±1.5  | ±4   |           |

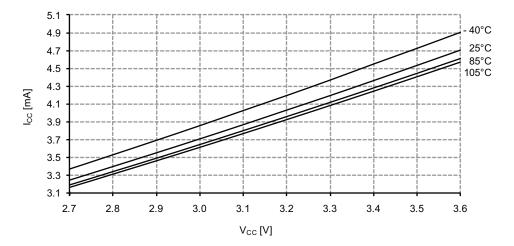

| DNL <sup>(1)</sup> | Differential non-linearity | gu                   | aranteed monotonic                                                    |      | <±0.8 | <±1  |           |

|                    |                            |                      |                                                                       |      | -1    |      | mV        |

|                    | Offset error               | Temperature drift    |                                                                       |      | <0.01 |      | mV/K      |

|                    |                            | Operating vo         | Itage drift                                                           |      | <0.6  |      | mV/V      |

|                    |                            | Differential<br>mode | External reference                                                    |      | -1    |      |           |

|                    |                            |                      | AV <sub>CC</sub> /1.6                                                 |      | 10    |      |           |

|                    | Gain error                 |                      | AV <sub>CC</sub> /2.0                                                 |      | 8     |      | mV        |

|                    | Gainenoi                   |                      | Bandgap                                                               |      | ±5    |      |           |

|                    |                            | Temperature drift    |                                                                       |      | <0.02 |      | mV/K      |

|                    |                            | Operating vo         | Itage drift                                                           |      | <0.5  |      | mV/V      |

|                    | Noise                      |                      | ode, shorted input<br><sub>C</sub> = 3.6V, Clk <sub>PER</sub> = 16MHz |      | 0.4   |      | mV<br>rms |

Notes: 1. Maximum numbers are based on characterisation and not tested in production, and valid for 5% to 95% input voltage range.

2. Unless otherwise noted all linearity, offset and gain error numbers are valid under the condition that external V<sub>REF</sub> is used.

#### 32.3.13.6 External Clock Characteristics

#### Table 32-80. External Clock Used as System Clock without Prescaling

| Symbol            | Parameter                                         | Condition                    | Min. | Тур. | Max. | Units      |

|-------------------|---------------------------------------------------|------------------------------|------|------|------|------------|

| 1 /+              | Clock frequency <sup>(1)</sup>                    | V <sub>CC</sub> = 1.6 - 1.8V | 0    |      | 12   | MHz        |

| 1/t <sub>CK</sub> |                                                   | V <sub>CC</sub> = 2.7 - 3.6V | 0    |      | 32   |            |

| +                 | Clock period                                      | V <sub>CC</sub> = 1.6 - 1.8V | 83.3 |      |      |            |

| t <sub>CK</sub>   | Clock period                                      | V <sub>CC</sub> = 2.7 - 3.6V | 31.5 |      |      |            |

| +                 | Clock high time                                   | V <sub>CC</sub> = 1.6 - 1.8V | 30.0 |      |      |            |

| t <sub>CH</sub>   |                                                   | V <sub>CC</sub> = 2.7 - 3.6V | 12.5 |      |      |            |

| +                 | Clock low time                                    | V <sub>CC</sub> = 1.6 - 1.8V | 30.0 |      |      | <b>n</b> 0 |

| t <sub>CL</sub>   |                                                   | V <sub>CC</sub> = 2.7 - 3.6V | 12.5 |      |      | ns         |

|                   |                                                   | V <sub>CC</sub> = 1.6 - 1.8V |      |      | 10   |            |

| t <sub>CR</sub>   | Rise time (for maximum frequency)                 | V <sub>CC</sub> = 2.7 - 3.6V |      |      | 3    |            |

| 4                 | Fall time (for maximum frequency)                 | V <sub>CC</sub> = 1.6 - 1.8V |      |      | 10   |            |

| t <sub>CF</sub>   |                                                   | V <sub>CC</sub> = 2.7 - 3.6V |      |      | 3    |            |

| $\Delta t_{CK}$   | Change in period from one clock cycle to the next |                              |      |      | 10   | %          |

Note: 1. System Clock Prescalers must be set so that maximum CPU clock frequency for device is not exceeded.

#### 33.1.3 ADC Characteristics

## Atmel

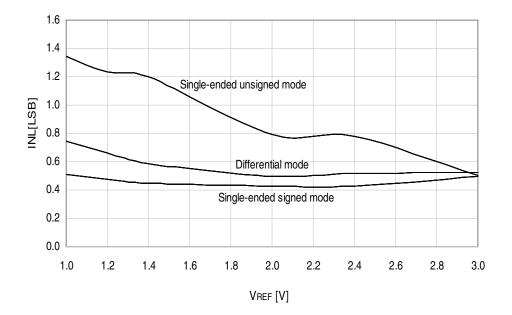

Figure 33-138. Reset Pin Pull-up Resistor Current vs. Reset Pin Voltage  $V_{CC} = 3.0V$

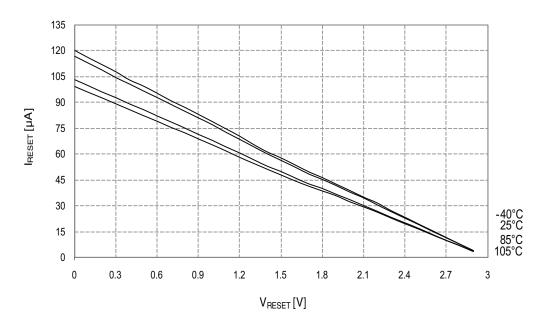

Figure 33-139. Reset Pin Pull-up Resistor Current vs. Reset Pin Voltage  $V_{CC} = 3.3V$

## Atmel

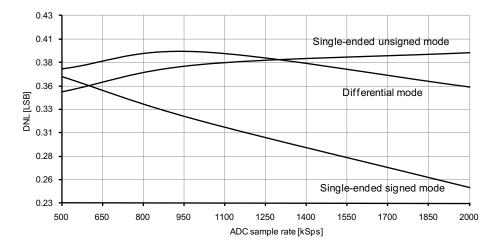

Figure 33-197. DNL Error vs. External  $V_{REF}$ T = 25 °C,  $V_{CC}$  = 3.6V, external reference

Figure 33-198. DNL Error vs. Sample rate  $T = 25 \, ^{\circ}C$ ,  $V_{cc} = 2.7V$ ,  $V_{REF} = 1.0V$  external

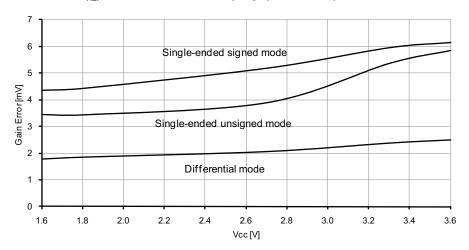

## Figure 33-201. Gain Error vs. $V_{cc}$

$T = 25 \,^{\circ}C$ ,  $V_{REF} = external 1.0V$ , ADC sampling speed = 500ksps

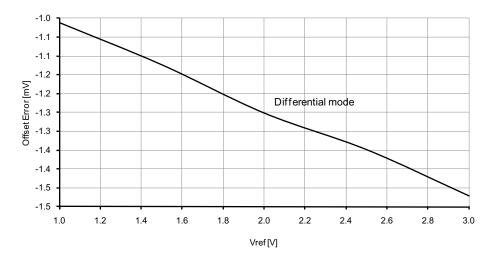

Figure 33-202. Offset Error vs.  $V_{REF}$ T = 25 °C,  $V_{CC}$  = 3.6V, ADC sampling speed = 500ksps

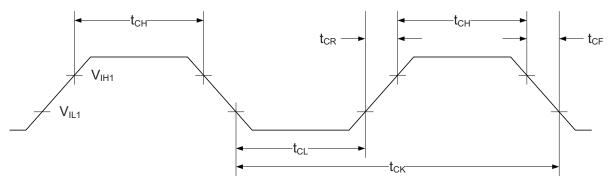

#### 33.4.2.3 Thresholds and Hysteresis

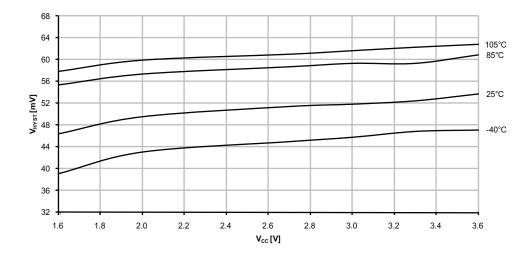

Figure 33-297. Analog Comparator Hysteresis vs. V<sub>CC</sub> Low power, large hysteresis

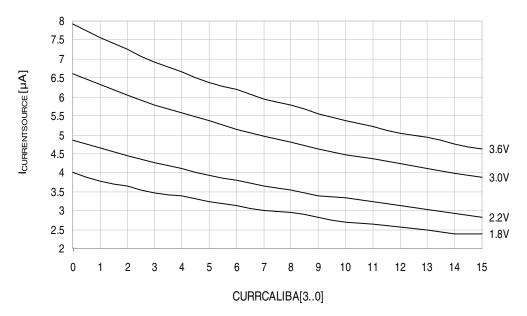

Figure 33-298. Analog Comparator Current Source vs. Calibration Value Temperature = 25°C

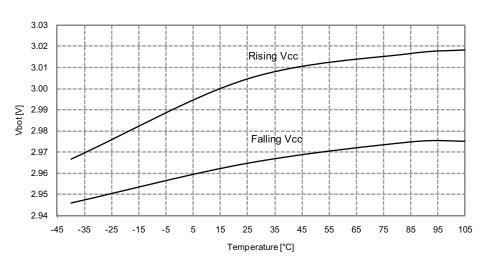

#### Figure 33-303. BOD Thresholds vs. Temperature BOD level = 3.0V

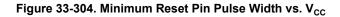

#### 33.4.8 External Reset Characteristics

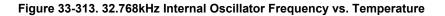

#### 33.4.10.2 32.768kHz Internal Oscillator

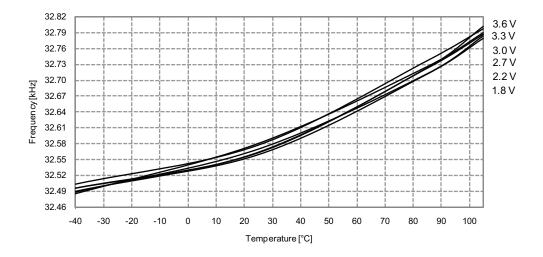

Figure 33-314. 32.768kHz Internal Oscillator Frequency vs. Calibration Value  $V_{cc} = 3.0V$ ,  $T = 25^{\circ}C$

#### 35.9 8135K - 06/2012

1. ATxmega64D4-CU is added in "Ordering Information" on page 2

### 35.10 8135J - 12/10

- 1. Datasheet status changed to complete: Preliminary removed from the front page.

- 2. Updated all tables in the "Electrical Characteristics" on page 64.

- 3. Replaced Table 31-11 on page 64.

- 4. Replaced Table 31-17 on page 65 and added the figure "TOSC input capacitance" on page 66.

- 5. Updated ERRATA ADC (ADC has increased INL for some operating conditions).

- 6. Updated ERRATA "rev. A/B" on page 90 with TWIE (TWIE is not available).

- 7. Updated the last page with Atmel new Brand Style Guide.

## 35.11 81351 - 10/10

1. Updated Table 31-1 on page 58.

#### 35.12 8135H - 09/10

1. Updated "Errata" on page 90.

## 35.13 8135G - 08/10

- 1. Updated the Footnote 3 of "Ordering Information" on page 2.

- 2. All references to CRC removed. Updated Figure 3-1 on page 7.

- 3. Updated "Features" on page 26. Event Channel 0 output on port pin 7.

- 4. Updated "DC Characteristics" on page 58 by adding Icc for Flash/EEPROM Programming.

- 5. Added AVCC in "ADC Characteristics" on page 62.

- 6. Updated Start up time in "ADC Characteristics" on page 62.

- 7. Updated and fixed typo in "Errata" section.

### 35.14 8135F - 02/10

1. Added "PDI Speed" on page 89.

# Atmel Enabling Unlimited Possibilities

www.atmel.com

Atmel Corporation 1600 Technology Drive, San Jose, CA 95110 USA T: (+1)(408) 441.0311 F: (+1)(408) 436.4200

© 2015 Atmel Corporation. / Rev.: Atmel-8135R-AVR-ATxmega16D4-32D4-64D4-128D4-Datasheet\_09/2016.

Atmel<sup>®</sup>, Atmel logo and combinations thereof, Enabling Unlimited Possibilities<sup>®</sup>, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. Other terms and product names may be trademarks of others.

DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make to specifications and products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death ("Safety-Critical Applications") without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems. Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.