Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18855t-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                                                                              | Function              | Input Type             | Output Type | Description                                                                                 |

|-------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------|-------------|---------------------------------------------------------------------------------------------|

| RA5/ANA5/SS1 <sup>(1)</sup> /MDSRC <sup>(1)</sup> /IOCA5                                                          | RA5                   | TTL/ST                 | CMOS/OD     | General purpose I/O.                                                                        |

|                                                                                                                   | ANA5                  | AN                     | _           | ADC Channel A5 input.                                                                       |

|                                                                                                                   | SS1 <sup>(1)</sup>    | TTL/ST                 | _           | MSSP1 SPI slave select input.                                                               |

|                                                                                                                   | MDSRC <sup>(1)</sup>  | TTL/ST                 | _           | Modulator Source input.                                                                     |

|                                                                                                                   | IOCA5                 | TTL/ST                 | -           | Interrupt-on-change input.                                                                  |

| RA6/ANA6/OSC2/CLKOUT/IOCA6                                                                                        | RA6                   | TTL/ST                 | CMOS/OD     | General purpose I/O.                                                                        |

|                                                                                                                   | ANA6                  | AN                     | -           | ADC Channel A6 input.                                                                       |

|                                                                                                                   | OSC2                  | _                      | XTAL        | External Crystal/Resonator (LP, XT, HS modes) driver out-<br>put.                           |

|                                                                                                                   | CLKOUT                | —                      | CMOS/OD     | Fosc/4 digital output (in non-crystal/resonator modes).                                     |

|                                                                                                                   | IOCA6                 | TTL/ST                 | -           | Interrupt-on-change input.                                                                  |

| RA7/ANA7/OSC1/CLKIN/IOCA7                                                                                         | RA7                   | TTL/ST                 | CMOS/OD     | General purpose I/O.                                                                        |

|                                                                                                                   | ANA7                  | AN                     | _           | ADC Channel A7 input.                                                                       |

|                                                                                                                   | OSC1                  | XTAL                   | _           | External Crystal/Resonator (LP, XT, HS modes) driver input.                                 |

|                                                                                                                   | CLKIN                 | TTL/ST                 | _           | External digital clock input.                                                               |

|                                                                                                                   | IOCA7                 | TTL/ST                 | _           | Interrupt-on-change input.                                                                  |

| RB0/ANB0/C2IN1+/ZCD/SS2 <sup>(1)</sup> /<br>CCP4 <sup>(1)</sup> /CWG1IN <sup>(1)</sup> /INT <sup>(1)</sup> /IOCB0 | RB0                   | TTL/ST                 | CMOS/OD     | General purpose I/O.                                                                        |

| CCP4 <sup>(1)</sup> /CWG1IN <sup>(1)</sup> /INT <sup>(1)</sup> /IOCB0                                             | ANB0                  | AN                     | _           | ADC Channel B0 input.                                                                       |

|                                                                                                                   | C2IN1+                | AN                     | _           | Comparator positive input.                                                                  |

|                                                                                                                   | ZCD                   | AN                     | AN          | Zero-cross detect input pin (with constant current sink/<br>source).                        |

|                                                                                                                   | SS2 <sup>(1)</sup>    | TTL/ST                 | -           | MSSP2 SPI slave select input.                                                               |

|                                                                                                                   | CCP4 <sup>(1)</sup>   | TTL/ST                 | CMOS/OD     | Capture/compare/PWM4 (default input location for capture function).                         |

|                                                                                                                   | CWG1IN <sup>(1)</sup> | TTL/ST                 | -           | Complementary Waveform Generator 1 input.                                                   |

|                                                                                                                   | INT <sup>(1)</sup>    | TTL/ST                 | -           | External interrupt request input.                                                           |

|                                                                                                                   | IOCB0                 | TTL/ST                 | -           | Interrupt-on-change input.                                                                  |

| RB1/ANB1/C1IN3-/C2IN3-/SCL2 <sup>(3,4)</sup> /<br>SCK2 <sup>(1)</sup> /CWG2IN <sup>(1)</sup> /IOCB1               | RB1                   | TTL/ST                 | CMOS/OD     | General purpose I/O.                                                                        |

| SCK2 <sup>(1)</sup> /CWG2IN <sup>(1)</sup> /IOCB1                                                                 | ANB1                  | AN                     | _           | ADC Channel B1 input.                                                                       |

|                                                                                                                   | C1IN3-                | AN                     | _           | Comparator negative input.                                                                  |

|                                                                                                                   | C2IN3-                | AN                     | _           | Comparator negative input.                                                                  |

|                                                                                                                   | SCL2 <sup>(3,4)</sup> | I <sup>2</sup> C/SMBus | OD          | MSSP2 I <sup>2</sup> C clock input/output.                                                  |

|                                                                                                                   | SCK2 <sup>(1)</sup>   | TTL/ST                 | CMOS/OD     | MSSP2 SPI serial clock (default input location, SCK2 is a PPS remappable input and output). |

|                                                                                                                   | CWG2IN <sup>(1)</sup> | TTL/ST                 | _           | Complementary Waveform Generator 2 input.                                                   |

|                                                                                                                   | IOCB1                 | TTL/ST                 | -           | Interrupt-on-change input.                                                                  |

### TABLE 1-3: PIC16F18875 PINOUT DESCRIPTION (CONTINUED)

Legend:

AN

= Analog input or output TTL

CMOS

= CMOS compatible input or output ST

OD

= Open-Drain

TTL

TTL compatible input High Voltage XTAL= Crystal levels

ST

= Schmitt Trigger input with CMOS levels

I<sup>2</sup>C

= Schmitt Trigger input with I<sup>2</sup>CHV=

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 13-1 for details on which PORT pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 13-3.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

| TABLE                                               | 3-13: SPE                                       | 1 1                              |       | REGISTE | R SUMMA |             | 0-31 (CONTI | NUED)     | T     |       | 1                     |                              |

|-----------------------------------------------------|-------------------------------------------------|----------------------------------|-------|---------|---------|-------------|-------------|-----------|-------|-------|-----------------------|------------------------------|

| Address                                             | Name                                            | PIC16(L)F18855<br>PIC16(L)F18875 | Bit 7 | Bit 6   | Bit 5   | Bit 4       | Bit 3       | Bit 2     | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on all<br>other Resets |

| Bank 30                                             | Bank 30                                         |                                  |       |         |         |             |             |           |       |       |                       |                              |

|                                                     | CPU CORE REGISTERS; see Table 3-2 for specifics |                                  |       |         |         |             |             |           |       |       |                       |                              |

| F0Ch     —     —     —     —     —     —       F0Fh |                                                 |                                  |       |         |         |             |             |           | _     |       |                       |                              |

| F10h                                                | RA0PPS                                          |                                  | —     | _       |         |             | RAC         | PPS<5:0>  |       |       | 00 0000               | uu uuuu                      |

| F11h                                                | RA1PPS                                          |                                  | —     | —       |         |             | RA1         | PPS<5:0>  |       |       | 00 0000               | uu uuuu                      |

| F12h                                                | RA2PPS                                          |                                  | —     | —       |         |             | RA2         | PPS<5:0>  |       |       | 00 0000               | uu uuuu                      |

| F13h                                                | RA3PPS                                          |                                  | —     | —       |         | RA3PPS<5:0> |             |           |       |       |                       | uu uuuu                      |

| F14h                                                | RA4PPS                                          |                                  | —     | —       |         | RA4PPS<5:0> |             |           |       |       |                       | uu uuuu                      |

| F15h                                                | RA5PPS                                          |                                  | —     | —       |         |             | RAS         | iPPS<5:0> |       |       | 00 0000               | uu uuuu                      |

| F16h                                                | RA6PPS                                          |                                  | —     | —       |         |             | RAG         | PPS<5:0>  |       |       | 00 0000               | uu uuuu                      |

| F17h                                                | RA7PPS                                          |                                  | —     | —       |         |             | RA7         | 'PPS<5:0> |       |       | 00 0000               | uu uuuu                      |

| F18h                                                | RB0PPS                                          |                                  | —     | —       |         |             | RBC         | PPS<5:0>  |       |       | 00 0000               | uu uuuu                      |

| F19h                                                | RB1PPS                                          |                                  | —     | —       |         | RB1PPS<5:0> |             |           |       |       |                       | uu uuuu                      |

| F1Ah                                                | RB2PPS                                          |                                  | —     | —       |         |             | RB2         | PPS<5:0>  |       |       | 00 0000               | uu uuuu                      |

| F1Bh                                                | RB3PPS                                          |                                  | —     | _       |         |             | RB3         | PPS<5:0>  |       |       | 00 0000               | uu uuuu                      |

| F1Ch                                                | RB4PPS                                          |                                  | —     | —       |         |             | RB4         | PPS<5:0>  |       |       | 00 0000               | uu uuuu                      |

| F1Dh                                                | RB5PPS                                          |                                  | —     | _       |         |             | RBS         | iPPS<5:0> |       |       | 00 0000               | uu uuuu                      |

| F1Eh                                                | RB6PPS                                          |                                  | —     | —       |         | RB6PPS<5:0> |             |           |       |       | 00 0000               | uu uuuu                      |

| F1Fh                                                | RB7PPS                                          |                                  | —     | —       |         | RB7PPS<5:0> |             |           |       |       | 00 0000               | uu uuuu                      |

| F20h                                                | RC0PPS                                          |                                  | —     | —       |         |             | RCC         | )PPS<5:0> |       |       | 00 0000               | uu uuuu                      |

| F21h                                                | RC1PPS                                          |                                  | —     | —       |         |             | RC1         | PPS<5:0>  |       |       | 00 0000               | uu uuuu                      |

| F22h                                                | RC2PPS                                          |                                  | _     | _       |         |             | RC2         | 2PPS<5:0> |       |       | 00 0000               | uu uuuu                      |

| F23h                                                | RC3PPS                                          |                                  | —     | —       |         |             | RC3         | 8PPS<5:0> |       |       | 00 0000               | uu uuuu                      |

# © 2015-2017 Microchip Technology Inc.

DS40001802D-page 77

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Register present on PIC16F18855/75 devices only.

2: Unimplemented, read as '1'.

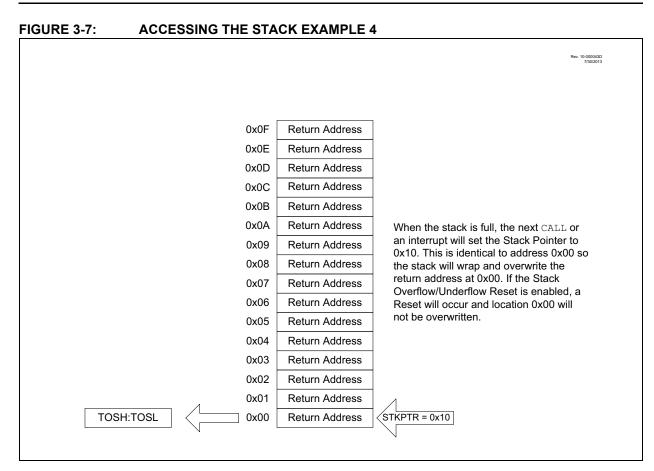

### 3.4 Stack

All devices have a 16-level x 15-bit wide hardware stack (refer to Figure 3-4 through Figure 3-7). The stack space is not part of either program or data space. The PC is PUSHed onto the stack when CALL or CALLW instructions are executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer if the STVREN bit is programmed to '0' (Configuration Words). This means that after the stack has been PUSHed sixteen times, the seventeenth PUSH overwrites the value that was stored from the first PUSH. The eighteenth PUSH overwrites the second PUSH (and so on). The STKOVF and STKUNF flag bits will be set on an Overflow/Underflow, regardless of whether the Reset is enabled.

Note 1: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, CALLW, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

### 3.4.1 ACCESSING THE STACK

The stack is available through the TOSH, TOSL and STKPTR registers. STKPTR is the current value of the Stack Pointer. TOSH:TOSL register pair points to the TOP of the stack. Both registers are read/writable. TOS is split into TOSH and TOSL due to the 15-bit size of the PC. To access the stack, adjust the value of STKPTR, which will position TOSH:TOSL, then read/write to TOSH:TOSL. STKPTR is five bits to allow detection of overflow and underflow.

| Note: | Care should be taken when modifying the |

|-------|-----------------------------------------|

|       | STKPTR while interrupts are enabled.    |

During normal program operation, CALL, CALLW and interrupts will increment STKPTR while RETLW, RETURN, and RETFIE will decrement STKPTR. At any time, STKPTR can be inspected to see how much stack is left. The STKPTR always points at the currently used place on the stack. Therefore, a CALL or CALLW will increment the STKPTR and then write the PC, and a return will unload the PC and then decrement the STKPTR.

Reference Figure 3-4 through Figure 3-7 for examples of accessing the stack.

|                | Rev: 10/000434<br>700/013                                                              |

|----------------|----------------------------------------------------------------------------------------|

| TOSH:TOSL 0x0F | STKPTR = 0x1F Stack Reset Disabled (STVREN = 0)                                        |

| 0x0E           |                                                                                        |

| 0x0D           |                                                                                        |

| 0x0C           |                                                                                        |

| 0x0B           | Initial Stack Configuration:                                                           |

| 0x0A           | , i i i i i i i i i i i i i i i i i i i                                                |

| 0x09           | After Reset, the stack is empty. The<br>empty stack is initialized so the Stack        |

| 0x08           | Pointer is pointing at 0x1F. If the Stack                                              |

| 0x07           | Overflow/Underflow Reset is enabled, the<br>TOSH/TOSL register will return '0'. If the |

| 0x06           | Stack Overflow/Underflow Reset is                                                      |

| 0x05           | disabled, the TOSH/TOSL register will<br>return the contents of stack address          |

| 0x04           | 0x0F.                                                                                  |

| 0x03           |                                                                                        |

| 0x02           |                                                                                        |

| 0x01           |                                                                                        |

| 0x00           |                                                                                        |

| TOSH:TOSL 0x1F | 0x0000 STKPTR = 0x1F Stack Reset Enabled<br>(STVREN = 1)                               |

| N              | N , , , , ,                                                                            |

|                |                                                                                        |

|                |                                                                                        |

FIGURE 3-4: ACCESSING THE STACK EXAMPLE 1

### 3.4.2 OVERFLOW/UNDERFLOW RESET

If the STVREN bit in Configuration Words is programmed to '1', the device will be Reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

### 3.5 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- Traditional Data Memory

- · Linear Data Memory

- Data EEPROM Memory

- Program Flash Memory

|                                                         |                                                                                                                         |                                                                                                                                                                                                                                             | 11.0                                           |                |                          |                  |             |  |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------|--------------------------|------------------|-------------|--|

| R/W/HS-0/0                                              |                                                                                                                         | U-0                                                                                                                                                                                                                                         | U-0                                            | U-0            | U-0                      | R/W/HS-0/0       | R/W/HS-0/0  |  |

| OSFIF                                                   | CSWIF                                                                                                                   | —                                                                                                                                                                                                                                           | _                                              | —              | —                        | ADTIF            | ADIF        |  |

| bit 7                                                   |                                                                                                                         |                                                                                                                                                                                                                                             |                                                |                |                          |                  | bit 0       |  |

|                                                         |                                                                                                                         |                                                                                                                                                                                                                                             |                                                |                |                          |                  |             |  |

| Legend:                                                 |                                                                                                                         |                                                                                                                                                                                                                                             |                                                |                |                          |                  |             |  |

| R = Readabl                                             | e bit                                                                                                                   | W = Writable                                                                                                                                                                                                                                | bit                                            | U = Unimpler   | nented bit, read         | as '0'           |             |  |

| u = Bit is und                                          | hanged                                                                                                                  | x = Bit is unkr                                                                                                                                                                                                                             | iown                                           | -n/n = Value a | at POR and BO            | R/Value at all o | ther Resets |  |

| '1' = Bit is set '0' = Bit is cleared HS = Hardware set |                                                                                                                         |                                                                                                                                                                                                                                             |                                                |                |                          |                  |             |  |

| bit 7                                                   | 1 = Oscillator                                                                                                          |                                                                                                                                                                                                                                             | pt has occurr                                  |                | eared in softwa          | re)              |             |  |

|                                                         |                                                                                                                         | tor fail-safe inte                                                                                                                                                                                                                          | •                                              |                |                          |                  |             |  |

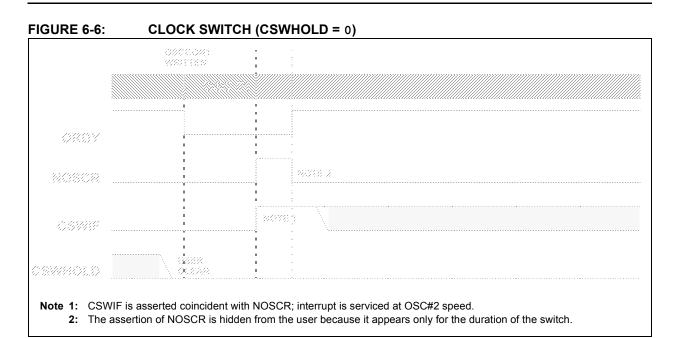

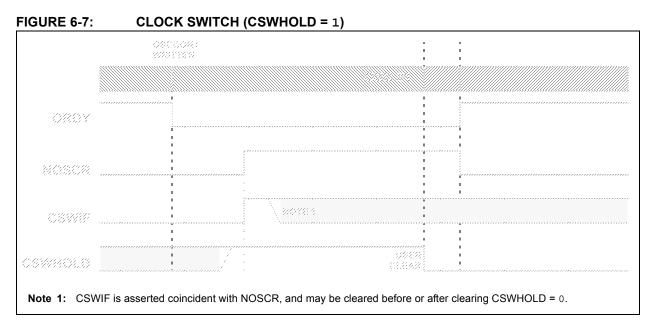

| bit 6                                                   |                                                                                                                         | k Switch Comp                                                                                                                                                                                                                               |                                                | 0              |                          |                  |             |  |

|                                                         |                                                                                                                         | switch module<br>switch does no                                                                                                                                                                                                             |                                                |                | tion (must be cl<br>tion | eared in softwa  | ire)        |  |

| bit 5-2                                                 | Unimplemen                                                                                                              | ted: Read as '                                                                                                                                                                                                                              | )'                                             |                |                          |                  |             |  |

| bit 1                                                   | 1 = An A/D m                                                                                                            | ADTIF: Analog-to-Digital Converter (ADC) Threshold Compare Interrupt Flag bit<br>1 = An A/D measurement was beyond the configured threshold (must be cleared in software)<br>0 = A/D measurements have been within the configured threshold |                                                |                |                          |                  |             |  |

| bit 0                                                   | 1 = An A/D co                                                                                                           | -to-Digital Conv<br>onversion or co<br>onversion or co                                                                                                                                                                                      | mplex operati                                  | on has comple  | ted (must be cl          | eared in softwa  | re)         |  |

| cc<br>its<br>U<br>aj                                    | terrupt flag bits a<br>ondition occurs, r<br>s corresponding<br>nable bit, GIE, c<br>ser software<br>opropriate interre | egardless of the<br>enable bit or th<br>of the INTCON<br>should ensu<br>upt flag bits a                                                                                                                                                     | e state of<br>e Global<br>register.<br>ire the |                |                          |                  |             |  |

### REGISTER 7-12: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

prior to enabling an interrupt.

### 10.4.9 WRERR BIT

The WRERR bit can be used to determine if a write error occurred.

WRERR will be set if one of the following conditions occurs:

- If WR is set while the NVMADRH:NMVADRL points to a write-protected address

- A Reset occurs while a self-write operation was in progress

- An unlock sequence was interrupted

The WRERR bit is normally set by hardware, but can be set by the user for test purposes. Once set, WRERR must be cleared in software.

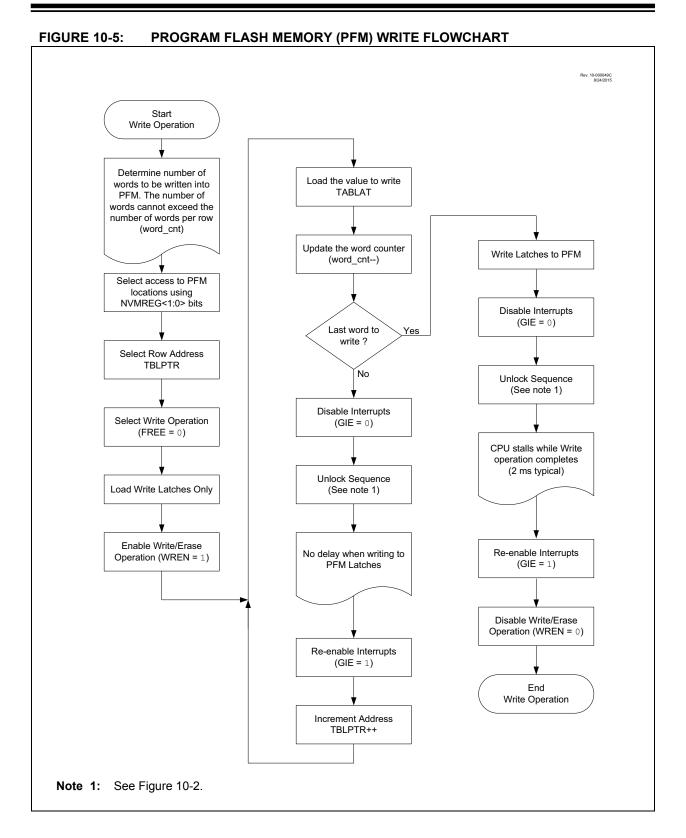

| Free | LWLO | Actions for PFM when WR = 1                                                                                    | Comments                                                                                                                                              |

|------|------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | x    | Erase the 32-word row of NVMADRH:NVMADRL<br>location. See Section 10.4.3 "NVMREG Write<br>to EEPROM"           | <ul> <li>If WP is enabled, WR is cleared and<br/>WRERR is set</li> <li>All 32 words are erased</li> <li>NVMDATH:NVMDATL is ignored</li> </ul>         |

| 0    | 1    | Copy NVMDATH:NVMDATL to the write latch corresponding to NVMADR LSBs. See Section 10.4.4 "NVMREG Erase of PFM" | <ul><li>Write protection is ignored</li><li>No memory access occurs</li></ul>                                                                         |

| 0    | 0    | Write the write-latch data to PFM row. See Sec-<br>tion 10.4.4 "NVMREG Erase of PFM"                           | <ul> <li>If WP is enabled, WR is cleared and<br/>WRERR is set</li> <li>Write latches are reset to 3FFh</li> <li>NVMDATH:NVMDATL is ignored</li> </ul> |

### TABLE 10-4: ACTIONS FOR PFM WHEN WR = 1

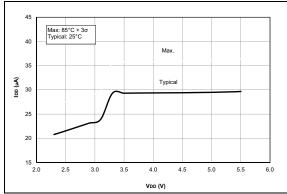

### 12.1.1 CURRENT-CONTROLLED DRIVE

Special precautions must be taken when enabling the current-controlled output drivers. An external resistor must be inserted in series with the load to dissipate most of the power. If an external resistor is not used then the pin circuity will dissipate all the power, thereby exceeding the maximum power specifications for the pin and the device. Determine the resistance and power rating of the external resistor such that the voltage at the pin is 0 for current sink and VDD for current source when the load is drawing the maximum expected power. For example, consider a load that is expected to vary from 1.0 to 1.5 volts. When VDD is 5V and the current is 1 mA then the combination of the external resistor and pin circuitry must make up the 3.5 to 4V difference. The external resistor should be sized to drop 3.5V at a current of 1 mA. The pin circuitry will then make up the 0 to 0.5 volt difference.

### 12.2 I/O Priorities

Each pin defaults to the PORT data latch after Reset. Other functions are selected with the peripheral pin select logic. See **Section 13.0** "**Peripheral Pin Select (PPS) Module**" for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx register. Digital output functions may continue to control the pin when it is in Analog mode.

Analog outputs, when enabled, take priority over the digital outputs and force the digital output driver to the high-impedance state.

### 12.3 Register Definitions: Current-Controlled Drive Configuration

### **REGISTER 12-1: CCDCON REGISTER**

| R/W-0/0              | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-x/u   | R/W-x/u |

|----------------------|-----|-----|-----|-----|-----|-----------|---------|

| CCDEN <sup>(1)</sup> | _   |     | _   | —   | —   | CCDS<1:0> |         |

| bit 7                |     |     |     |     |     |           | bit 0   |

|                      |     |     |     |     |     |           |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | <ul> <li>CCDEN: Current Controlled Drive Enable bit<sup>(1)</sup></li> <li>1 = Current-Controlled drive is enabled for all ports. Port pins enabled for current-controlled source with the CCDPxy or current-controlled sink with the CCCNxy controls will have their current limited to that selected by the CCDS selection.</li> <li>0 = Current-controlled drive disabled</li> </ul> |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-2 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                              |

| bit 1-0 | CCDS<1:0>: Current Controlled Drive Selection bits:                                                                                                                                                                                                                                                                                                                                     |

|         | Current setting (mA):                                                                                                                                                                                                                                                                                                                                                                   |

|         | 11 = 1.0                                                                                                                                                                                                                                                                                                                                                                                |

|         | 10 = 2.0                                                                                                                                                                                                                                                                                                                                                                                |

|         | 01 = 5.0                                                                                                                                                                                                                                                                                                                                                                                |

|         | 00 = 10.0                                                                                                                                                                                                                                                                                                                                                                               |

Note 1: If either CCDPxy or CCDNxy is set when CCDEN = 0, the operation of the pin is undefined.

### 12.6.5 INPUT THRESHOLD CONTROL

The INLVLB register (Register 12-9) controls the input voltage threshold for each of the available PORTB input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTB register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 37-4 for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

### 12.6.6 ANALOG CONTROL

The ANSELB register (Register 12-5) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no effect on digital output functions. A pin with its TRIS bit clear and its ANSEL bit set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELB bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

### 12.6.7 WEAK PULL-UP CONTROL

The WPUB register (Register 12-6) controls the individual weak pull-ups for each PORT pin.

### 12.6.8 CURRENT-CONTROL DRIVE MODE CONTROL

The CCDPB and CCDNB registers (Register 12-20) and (Register 12-21) control the Current-Controlled Drive mode for both the positive-going and negative-going drivers. When a CCDPB[y] or CCDNB[y] bit is set and the CCDEN bit of the CCDCON register is set, the current-controlled mode is enabled for the corresponding port pin. When the CCDPB[y] or CCDNB[y] bit is clear, the current-controlled mode for the corresponding port pin is disabled. If the CCDPB[y] or CCDNB[y] bit is set and the CCDEN bit is clear, operation of the port pin is undefined (see Section 12.1.1 "Current-Controlled Drive").

### 12.6.9 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTB pin is multiplexed with other functions.

Each pin defaults to the PORT latch data after Reset. Other output functions are selected with the peripheral pin select logic or by enabling an analog output, such as the DAC. See **Section 13.0 "Peripheral Pin Select (PPS) Module"** for more information.

Analog input functions, such as ADC and comparator inputs are not shown in the peripheral pin select lists. Digital output functions may continue to control the pin when it is in Analog mode.

### REGISTER 12-30: CCDPC: CURRENT CONTROLLED DRIVE POSITIVE PORTC REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| CCDPC7  | CCDPC6  | CCDPC5  | CCDPC4  | CCDPC3  | CCDPC2  | CCDPC1  | CCDPC0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

CCDPC<7:0>: RC<7:0> Current Controlled Drive Positive Control bits<sup>(1)</sup>

- 1 = Current-controlled source enabled

- 0 = Current-controlled source disabled

Note 1: If CCDPCy is set, when CCDEN = 0 (Register 12-1), operation of the pin is undefined.

### REGISTER 12-31: CCDNC: CURRENT CONTROLLED DRIVE NEGATIVE PORTC REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| CCDNC7  | CCDNC6  | CCDNC5  | CCDNC4  | CCDNC3  | CCDNC2  | CCDNC1  | CCDNC0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

CCDNC<7:0>: RC<7:0> Current Controlled Drive Negative Control bits<sup>(1)</sup>

1 = Current-controlled source enabled

0 = Current-controlled source disabled

**Note 1:** If CCDNCy is set, when CCDEN = 0 (Register 12-1), operation of the pin is undefined.

### 22.1.2 DATA GATING

Outputs from the input multiplexers are directed to the desired logic function input through the data gating stage. Each data gate can direct any combination of the four selected inputs.

### Note: Data gating is undefined at power-up.

The gate stage is more than just signal direction. The gate can be configured to direct each input signal as inverted or non-inverted data. Directed signals are ANDed together in each gate. The output of each gate can be inverted before going on to the logic function stage.

The gating is in essence a 1-to-4 input AND/NAND/OR/NOR gate. When every input is inverted and the output is inverted, the gate is an OR of all enabled data inputs. When the inputs and output are not inverted, the gate is an AND or all enabled inputs.

Table 22-3 summarizes the basic logic that can be obtained in gate 1 by using the gate logic select bits. The table shows the logic of four input variables, but each gate can be configured to use less than four. If no inputs are selected, the output will be zero or one, depending on the gate output polarity bit.

### TABLE 22-3: DATA GATING LOGIC

| CLCxGLSy | LCxGyPOL | Gate Logic |

|----------|----------|------------|

| 0x55     | 1        | AND        |

| 0x55     | 0        | NAND       |

| 0xAA     | 1        | NOR        |

| 0xAA     | 0        | OR         |

| 0x00     | 0        | Logic 0    |

| 0x00     | 1        | Logic 1    |

It is possible (but not recommended) to select both the true and negated values of an input. When this is done, the gate output is zero, regardless of the other inputs, but may emit logic glitches (transient-induced pulses). If the output of the channel must be zero or one, the recommended method is to set all gate bits to zero and use the gate polarity bit to set the desired level.

Data gating is configured with the logic gate select registers as follows:

- Gate 1: CLCxGLS0 (Register 22-7)

- Gate 2: CLCxGLS1 (Register 22-8)

- Gate 3: CLCxGLS2 (Register 22-9)

- Gate 4: CLCxGLS3 (Register 22-10)

Register number suffixes are different than the gate numbers because other variations of this module have multiple gate selections in the same register. Data gating is indicated in the right side of Figure 22-2. Only one gate is shown in detail. The remaining three gates are configured identically with the exception that the data enables correspond to the enables for that gate.

### 22.1.3 LOGIC FUNCTION

There are eight available logic functions including:

- AND-OR

- OR-XOR

- AND

- S-R Latch

- D Flip-Flop with Set and Reset

- D Flip-Flop with Reset

- J-K Flip-Flop with Reset

- Transparent Latch with Set and Reset

Logic functions are shown in Figure 22-2. Each logic function has four inputs and one output. The four inputs are the four data gate outputs of the previous stage. The output is fed to the inversion stage and from there to other peripherals, an output pin, and back to the CLCx itself.

### 22.1.4 OUTPUT POLARITY

The last stage in the Configurable Logic Cell is the output polarity. Setting the LCxPOL bit of the CLCxPOL register inverts the output signal from the logic stage. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

### 32.1 SMT Operation

The core of the module is the 24-bit counter, SMTxTMR combined with a complex data acquisition front-end. Depending on the mode of operation selected, the SMT can perform a variety of measurements summarized in Table 32-1.

### 32.1.1 CLOCK SOURCES

Clock sources available to the SMT include:

- Fosc

- Fosc/4

- HFINTOSC (16 MHz)

- LFINTOSC

- MFINTOSC/16 (31.25 kHz)

The SMT clock source is selected by configuring the CSEL<2:0> bits in the SMTxCLK register. The clock source can also be prescaled using the PS<1:0> bits of the SMTxCON0 register. The prescaled clock source is used to clock both the counter and any synchronization logic used by the module.

### 32.1.2 PERIOD MATCH INTERRUPT

Similar to other timers, the SMT triggers an interrupt when SMTxTMR rolls over to '0'. This happens when SMTxTMR = SMTxPR, regardless of mode. Hence, in any mode that relies on an external signal or a window to reset the timer, proper operation requires that SMTxPR be set to a period larger than that of the expected signal or window.

### 32.2 Basic Timer Function Registers

The SMTxTMR time base and the SMTxCPW/SMTxPR/SMTxCPR buffer registers serve several functions and can be manually updated using software.

### 32.2.1 TIME BASE

The SMTxTMR is the 24-bit counter that is the center of the SMT. It is used as the basic counter/timer for measurement in each of the modes of the SMT. It can be reset to a value of 24'h00\_0000 by setting the RST bit of the SMTxSTAT register. It can be written to and read from software, but it is not guarded for atomic access, therefore reads and writes to the SMTxTMR should only be made when the GO = 0, or the software should have other measures to ensure integrity of SMTxTMR reads/writes.

### 32.2.2 PULSE WIDTH LATCH REGISTERS

The SMTxCPW registers are the 24-bit SMT pulse width latch. They are used to latch in the value of the SMTxTMR when triggered by various signals, which are determined by the mode the SMT is currently in.

The SMTxCPW registers can also be updated with the current value of the SMTxTMR value by setting the CPWUP bit of the SMTxSTAT register.

### 32.2.3 PERIOD LATCH REGISTERS

The SMTxCPR registers are the 24-bit SMT period latch. They are used to latch in other values of the SMTxTMR when triggered by various other signals, which are determined by the mode the SMT is currently in.

The SMTxCPR registers can also be updated with the current value of the SMTxTMR value by setting the CPRU bit in the SMTxSTAT register.

### 32.3 Halt Operation

The counter can be prevented from rolling-over using the STP bit in the SMTxCON0 register. When halting is enabled, the period match interrupt persists until the SMTxTMR is reset (either by a manual reset, **Section 32.2.1 "Time Base**") or by clearing the SMTxGO bit of the SMTxCON1 register and writing the SMTxTMR values in software.

### 32.4 Polarity Control

The three input signals for the SMT have polarity control to determine whether or not they are active high/positive edge or active low/negative edge signals.

The following bits apply to Polarity Control:

- WSEL bit (Window Polarity)

- SSEL bit (Signal Polarity)

- CSEL bit (Clock Polarity)

These bits are located in the SMTxCON0 register.

### 32.5 Status Information

The SMT provides input status information for the user without requiring the need to deal with the polarity of the incoming signals.

### 32.5.1 WINDOW STATUS

Window status is determined by the WS bit of the SMTxSTAT register. This bit is only used in Windowed Measure, Gated Counter and Gated Window Measure modes, and is only valid when TS = 1, and will be delayed in time by synchronizer delays in non-Counter modes.

### 32.5.2 SIGNAL STATUS

Signal status is determined by the AS bit of the SMTxSTAT register. This bit is used in all modes except Window Measure, Time of Flight and Capture modes, and is only valid when TS = 1, and will be delayed in time by synchronizer delays in non-Counter modes.

### REGISTER 32-2: SMTxCON1: SMT CONTROL REGISTER 1

| R/W/HC-0/0       | R/W-0/0            | U-0                              | U-0         | R/W-0/0        | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|------------------|--------------------|----------------------------------|-------------|----------------|------------------|----------------|--------------|

| SMTxGO           | REPEAT             | —                                | —           |                | MODE             | <3:0>          |              |

| bit 7            |                    |                                  |             |                |                  |                | bit 0        |

|                  |                    |                                  |             |                |                  |                |              |

| Legend:          |                    |                                  |             |                |                  |                |              |

| HC = Bit is clea | ared by hardwa     | are                              |             | HS = Bit is se | et by hardware   |                |              |

| R = Readable b   | bit                | W = Writable                     | bit         | U = Unimpler   | nented bit, reac | l as '0'       |              |

| u = Bit is uncha | inged              | x = Bit is unkr                  | iown        | -n/n = Value a | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is set |                    | '0' = Bit is clea                | ared        | q = Value dep  | ends on condit   | tion           |              |

|                  |                    |                                  |             |                |                  |                |              |

| bit 7            |                    | /IT GO Data Ac                   |             |                |                  |                |              |

|                  |                    | ting, acquiring                  |             |                |                  |                |              |

|                  |                    | ting, acquiring                  |             |                |                  |                |              |

| bit 6            |                    | T Repeat Acquate ata Acquisition |             |                |                  |                |              |

|                  |                    | quisition mode                   |             | leu            |                  |                |              |

| bit 5-4          | -                  | ted: Read as '                   |             |                |                  |                |              |

| bit 3-0          | MODE<3:0>          | SMT Operation                    | Mode Select | bits           |                  |                |              |

|                  | 1111 <b>= Rese</b> | rved                             |             |                |                  |                |              |

|                  | •                  |                                  |             |                |                  |                |              |

|                  | •                  |                                  |             |                |                  |                |              |

|                  | 1011 <b>= Rese</b> | rved                             |             |                |                  |                |              |

|                  | 1010 = Windo       | owed counter                     |             |                |                  |                |              |

|                  | 1001 = Gated       | d counter                        |             |                |                  |                |              |

|                  | 1000 = Coun        | ter                              |             |                |                  |                |              |

|                  | 0111 = Captu       |                                  |             |                |                  |                |              |

|                  | 0110 = Time        | •                                |             |                |                  |                |              |

|                  |                    | d windowed me                    | asure       |                |                  |                |              |

|                  |                    | owed measure<br>and low time m   | oasuromont  |                |                  |                |              |

|                  |                    | d and Duty-Cyc                   |             |                |                  |                |              |

|                  | 0010 = 1  end      |                                  |             |                |                  |                |              |

|                  | 0000 = Timer       |                                  |             |                |                  |                |              |

|                  |                    |                                  |             |                |                  |                |              |

### **REGISTER 32-7:** SMTxTMRL: SMT TIMER REGISTER – LOW BYTE

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                   | SMTxTN  | /IR<7:0>       |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unkn   | nown    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                |              |

bit 7-0 SMTxTMR<7:0>: Significant bits of the SMT Counter – Low Byte

### REGISTER 32-8: SMTxTMRH: SMT TIMER REGISTER – HIGH BYTE

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | SMTxTM  | R<15:8> |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMTxTMR<15:8>: Significant bits of the SMT Counter – High Byte

### REGISTER 32-9: SMTxTMRU: SMT TIMER REGISTER – UPPER BYTE

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|---------|---------|---------|----------|---------|---------|---------|

|         |         |         | SMTxTMF | R<23:16> |         |         |         |

| bit 7   |         |         |         |          |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

### bit 7-0 SMTxTMR<23:16>: Significant bits of the SMT Counter – Upper Byte

### 33.1.2.3 Receive Interrupts

The RCIF interrupt flag bit of the PIR3 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RCIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCIF interrupts are enabled by setting all of the following bits:

- RCIE, Interrupt Enable bit of the PIE3 register

- PEIE, Peripheral Interrupt Enable bit of the INTCON register

- GIE, Global Interrupt Enable bit of the INTCON register

The RCIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

### 33.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RC1STA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RC1STA register which resets the EUSART. Clearing the CREN bit of the RC1STA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

Note: If all receive characters in the receive FIFO have framing errors, repeated reads of the RCREG will not clear the FERR bit.

### 33.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RC1STA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RC1STA register or by resetting the EUSART by clearing the SPEN bit of the RC1STA register.

### 33.1.2.6 Receiving 9-Bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RC1STA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RC1STA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

### 33.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RC1STA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

### 33.6 Register Definitions: EUSART Control

### REGISTER 33-1: TX1STA: TRANSMIT STATUS AND CONTROL REGISTER

| R/W-/0                                | R/W-0/0                                                        | R/W-0/0                                                | R/W-0/0                                             | R/W-0/0       | R/W-0/0            | R-1/1              | R/W-0/0       |

|---------------------------------------|----------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------|---------------|--------------------|--------------------|---------------|

| CSRC                                  | TX9                                                            | TXEN <sup>(1)</sup>                                    | SYNC                                                | SENDB         | BRGH               | TRMT               | TX9D          |

| pit 7                                 |                                                                |                                                        |                                                     |               |                    |                    | bit (         |

|                                       |                                                                |                                                        |                                                     |               |                    |                    |               |

| egend:                                |                                                                |                                                        |                                                     |               |                    |                    |               |

| R = Readable                          | bit                                                            | W = Writable                                           | bit                                                 | U = Unimpler  | mented bit, read   | as '0'             |               |

| I = Bit is unchangedX = Bit is unknow |                                                                | nown                                                   | -n/n = Value a                                      | at POR and BO | R/Value at all o   | other Resets       |               |

| 1' = Bit is set                       |                                                                | '0' = Bit is cle                                       | ared                                                |               |                    |                    |               |

| pit 7                                 | <u>Asynchronou</u>                                             | k Source Select<br><u>us mode</u> :<br>is mode – value |                                                     |               |                    |                    |               |

|                                       | <u>Synchronous</u><br>1 = Master                               |                                                        | nerated intern                                      |               | )                  |                    |               |

| bit 6                                 | <b>TX9:</b> 9-bit Tr<br>1 = Selects                            | ansmit Enable I<br>9-bit transmiss<br>8-bit transmiss  | oit<br>ion                                          |               |                    |                    |               |

| oit 5                                 | <b>TXEN:</b> Trans<br>1 = Transmi<br>0 = Transmi               |                                                        | 1)                                                  |               |                    |                    |               |

| bit 4                                 | SYNC: EUS<br>1 = Synchro<br>0 = Asynchr                        |                                                        | ect bit                                             |               |                    |                    |               |

| oit 3                                 | Asynchronou<br>1 = Send Syncheared<br>0 = SYNCH<br>Synchronous | /NCH BREAK c<br>by hardware up<br>BREAK transm         | on next transm<br>oon completion<br>iission disable | 1             | it, followed by 12 | 2 '0' bits, follow | ed by Stop bi |

| bit 2                                 | Asynchronou<br>1 = High spe<br>0 = Low spe<br>Synchronous      | eed<br>eed                                             |                                                     |               |                    |                    |               |

| pit 1                                 |                                                                | smit Shift Regist<br>pty                               |                                                     |               |                    |                    |               |

|                                       |                                                                |                                                        |                                                     |               |                    |                    |               |

| bit O                                 |                                                                | bit of Transmit<br>ess/data bit or a                   |                                                     |               |                    |                    |               |

## TABLE 36-3: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file                                 | 8           | 7           | 6        |                |            |          | 0         |

|----------------------------------------------------|-------------|-------------|----------|----------------|------------|----------|-----------|

| OPCODE                                             |             | d           |          |                | f (Fl      | LE #)    |           |

| d = 0 for des<br>d = 1 for des<br>f = 7-bit file r | tinati      | on f        | Ire      | ss             |            |          |           |

| Bit-oriented file r<br>13                          | egist<br>10 | -           | era<br>7 |                |            |          | 0         |

| OPCODE                                             |             | b (Bl       | T #      | <sup>t</sup> ) | f (F       | ILE #    | )         |

| b = 3-bit bit a<br>f = 7-bit file r                |             |             | lre      | ss             |            |          |           |

| iteral and contro                                  | ol op       | eratio      | ons      | ;              |            |          |           |

| General                                            |             | •           | _        |                |            |          | •         |

| 13<br>OPCODE                                       |             | 8           | 7        |                | k (lit     | eral)    | 0         |

| k = 8-bit imm                                      | odio        |             | 10       |                | ik (iit    | crui)    |           |

| K = 0-bit inin                                     | icula       |             |          |                |            |          |           |

| ALL and GOTO in<br>13 11                           | struc<br>10 | tions o     | onl      | У              |            |          | 0         |