#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detailo                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18855t-i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| RA0         2         17         19         19         ANA0         -         -         Clino-<br>C2INO-<br>C2INO-         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         Clino-         -         IOCA0         -         IOCA0         -         IOCA0         -         IOCA0         -         -         IOCA0         IOCA0         IOCA0         IOCA0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | O/i | 40-Pin PDIP | 40-Pin UQFN | 44-Pin QFN | 44-Pin TQFP | ADC                           | Voltage Reference | DAC      | Comparators | Zero-Cross Detect | MSSP (SPI/I <sup>2</sup> C)                  | EUSART | WSQ                   | Timers/SMT                                   | CCP and PWM         | CWG                   | CLC                   | NCO | Clock Reference (CLKR) | Interrupt-on-Change | Basic          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|-------------|------------|-------------|-------------------------------|-------------------|----------|-------------|-------------------|----------------------------------------------|--------|-----------------------|----------------------------------------------|---------------------|-----------------------|-----------------------|-----|------------------------|---------------------|----------------|

| Image: Region of the state of the  | RA0 | 2           | 17          | 19         | 19          | ANA0                          |                   | _        |             | —                 | _                                            |        | —                     | -                                            | _                   | —                     |                       | —   |                        | IOCA0               | _              |

| Image: Section of the secting definition of the section of | RA1 | 3           | 18          | 20         | 20          | ANA1                          |                   | —        |             |                   | —                                            |        | —                     | _                                            | _                   | —                     | CLCIN1 <sup>(1)</sup> | —   |                        | IOCA1               | _              |

| RA4       6       21       23       ANA4       -       -       -       -       -       MDCARH <sup>(1)</sup> TOCKI <sup>(1)</sup> CCP5 <sup>(1)</sup> -       -       -       IOCA4       -         RA5       7       22       24       24       ANA5       -       -       -       -       SS1 <sup>(1)</sup> -       MDSRC <sup>(1)</sup> -       -       -       -       -       IOCA4       -         RA6       14       29       33       31       ANA6       -       -       -       -       -       MDSRC <sup>(1)</sup> -       -       -       -       -       IOCA6       OCCA5       CLKOUT         RA7       13       28       32       30       ANA7       -       -       -       -       -       -       -       -       -       -       IOCA7       OSC1         RB0       33       8       9       8       ANB0       -       I       CliN1+       ZCD       SS2 <sup>(1)</sup> -       -       -       CPC4 <sup>(1)</sup> CWG1IN <sup>(1)</sup> -       -       INT <sup>(1)</sup> ICLKN         RB0       33       8       9       10       9       ANB1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RA2 | 4           | 19          | 21         | 21          | ANA2                          | VREF-             | DAC1OUT1 |             |                   |                                              |        |                       | _                                            | -                   | —                     | —                     |     |                        | IOCA2               | _              |

| RA5       7       22       24       ANA5       -       -       -       -       SS1 <sup>(1)</sup> -       MDSRC <sup>(1)</sup> -       -       -       -       0CA5       -         RA6       14       29       33       31       ANA6       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RA3 | 5           | 20          | 22         | 22          | ANA3                          | VREF+             | -        | C1IN1+      | —                 | -                                            | —      | MDCARL <sup>(1)</sup> |                                              | _                   | —                     | _                     | —   | _                      | IOCA3               | —              |

| RA6       14       29       33       31       ANA6       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RA4 | 6           | 21          | 23         | 23          | ANA4                          | —                 | -        | _           | -                 |                                              | -      | MDCARH <sup>(1)</sup> | T0CKI <sup>(1)</sup>                         | CCP5 <sup>(1)</sup> | —                     | _                     | —   | —                      | IOCA4               | —              |

| RA7         13         28         32         30         ANA7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RA5 | 7           | 22          | 24         | 24          | ANA5                          | —                 | -        | _           | -                 | SS1 <sup>(1)</sup>                           | _      | MDSRC <sup>(1)</sup>  | _                                            | -                   | —                     | _                     | _   | _                      | IOCA5               | —              |

| RB0         33         8         9         8         ANB0         -         C2IN1+         ZCD         SS2(1)         -         -         CCP4(1)         CWG1IN(1)         -         -         INT(1)         ICCB0         -         ICLKIN           RB1         34         9         10         9         ANB1         -         C1IN3-<br>C2IN3-         -         SCL2(3.4)<br>SCK2(1)         -         -         -         CWG3IN(1)         -         -         -         ICLKIN           RB2         35         10         11         10         ANB2         -         C1IN3-<br>C2IN3-         -         SCL2(3.4)<br>SCL2(3.4)         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RA6 | 14          | 29          | 33         | 31          | ANA6                          |                   | —        |             |                   | —                                            |        | -                     |                                              |                     | —                     | —                     | _   |                        | IOCA6               | OSC2<br>CLKOUT |

| RB1       34       9       10       9       ANB1        C1IN3-<br>C2IN3-        SCL2 <sup>(3,4)</sup><br>SCK2 <sup>(1)</sup> CWG2IN <sup>(1)</sup> IOCB0         RB2       35       10       11       10       ANB2        C1IN3-<br>C2IN3-        SCL2 <sup>(3,4)</sup><br>SCK2 <sup>(1)</sup> CWG2IN <sup>(1)</sup> IOCB0          RB2       35       10       11       10       ANB2                  CWG3IN <sup>(1)</sup> IOCB0          RB3       36       11       12       11       ANB3               IOCB1        IOCB2          RB4       37       12       14       14       ANB4<br>ADCACT <sup>(1)</sup> TG6 <sup>(1)</sup><br>SMTSIG2 <sup>(1)</sup> IOCB3          RB5       38       13       15       16       ANB6 </td <td>RA7</td> <td>13</td> <td>28</td> <td>32</td> <td>30</td> <td>ANA7</td> <td>-</td> <td>—</td> <td>—</td> <td>—</td> <td></td> <td> </td> <td>—</td> <td>_</td> <td></td> <td></td> <td>—</td> <td>—</td> <td> </td> <td></td> <td>OSC1<br/>CLKIN</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | RA7 | 13          | 28          | 32         | 30          | ANA7                          | -                 | —        | —           | —                 |                                              |        | —                     | _                                            |                     |                       | —                     | —   |                        |                     | OSC1<br>CLKIN  |

| Image: Normal Section       Image: Normal Sec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RB0 | 33          | 8           | 9          | 8           | ANB0                          |                   | —        | C2IN1+      | ZCD               |                                              |        | —                     | _                                            | CCP4 <sup>(1)</sup> |                       | —                     | —   |                        |                     | —              |

| RB3         36         11         12         11         ANB3          C1IN2-<br>C2IN2-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RB1 | 34          | 9           | 10         | 9           | ANB1                          |                   | _        |             |                   | SCL2 <sup>(3,4)</sup><br>SCK2 <sup>(1)</sup> | l      | _                     |                                              |                     |                       | —                     | _   |                        | IOCB1               | _              |

| Image: Note of the state o         | RB2 | 35          | 10          | 11         | 10          | ANB2                          |                   | _        |             |                   | SDA2 <sup>(3,4)</sup><br>SDI2 <sup>(1)</sup> | l      | _                     |                                              |                     | CWG3IN <sup>(1)</sup> | —                     | _   |                        | IOCB2               | _              |

| Image: Non-Structure       ADCACT <sup>(1)</sup> Image: Non-Structure       ADCACT <sup>(1)</sup> Image: Non-Structure       Image: Non-Struct                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RB3 | 36          | 11          | 12         | 11          | ANB3                          |                   | Ι        |             |                   | Ι                                            |        | _                     | _                                            | -                   | —                     | —                     |     |                        | IOCB3               | —              |

| RB6       39       14       16       16       ANB6       -       -       -       -       -       -       -       -       ICCB6       ICSPCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RB4 | 37          | 12          | 14         | 14          | ANB4<br>ADCACT <sup>(1)</sup> | _                 | —        | —           | _                 | —                                            | —      | -                     | T5G <sup>(1)</sup><br>SMTWIN2 <sup>(1)</sup> | _                   | —                     | —                     | —   | _                      | IOCB4               | —              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RB5 | 38          | 13          | 15         | 15          | ANB5                          | -                 | —        | _           | _                 | —                                            | -      | —                     | T1G <sup>(1)</sup><br>SMTSIG2 <sup>(1)</sup> | CCP3(1)             | —                     | —                     | —   | 1                      | IOCB5               | _              |

| RB7       40       15       17       17       ANB7       —       DAC10UT2       —       —       —       T6IN <sup>(1)</sup> —       —       CLCIN3 <sup>(1)</sup> —       —       IOCB7       ICSPDAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RB6 | 39          | 14          | 16         | 16          | ANB6                          | —                 | —        | —           | _                 | —                                            | —      | —                     | —                                            | —                   | —                     |                       |     | —                      | IOCB6               | ICSPCLK        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RB7 | 40          | 15          | 17         | 17          | ANB7                          | -                 | DAC10UT2 | -           | —                 | —                                            | _      | —                     | T6IN <sup>(1)</sup>                          | —                   | —                     | CLCIN3 <sup>(1)</sup> | —   | -                      | IOCB7               | ICSPDAT        |

TABLE 3: 40/44-PIN ALLOCATION TABLE (PIC16F18875)

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 13-1 for details on which port pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 13-3.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels.; The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMbus input buffer thresholds.

| TABLE 1-3: | PIC16F18875 PINOUT DESCRIPTION |

|------------|--------------------------------|

|            |                                |

| Name                                                   | Function              | Input Type | Output Type | Description                                                         |

|--------------------------------------------------------|-----------------------|------------|-------------|---------------------------------------------------------------------|

| RA0/ANA0/C1IN0-/C2IN0-/                                | RA0                   | TTL/ST     | CMOS/OD     | General purpose I/O.                                                |

| CLCIN0 <sup>(1)</sup> /IOCA0                           | ANA0                  | AN         | _           | ADC Channel A0 input.                                               |

|                                                        | C1IN0-                | AN         | _           | Comparator negative input.                                          |

|                                                        | C2IN0-                | AN         | -           | Comparator negative input.                                          |

|                                                        | CLCIN0 <sup>(1)</sup> | TTL/ST     | _           | Configurable Logic Cell source input.                               |

|                                                        | IOCA0                 | TTL/ST     | _           | Interrupt-on-change input.                                          |

| RA1/ANA1/C1IN1-/C2IN1-/                                | RA1                   | TTL/ST     | CMOS/OD     | General purpose I/O.                                                |

| CLCIN1 <sup>(1)</sup> /IOCA1                           | ANA1                  | AN         | -           | ADC Channel A1 input.                                               |

|                                                        | C1IN1-                | AN         | -           | Comparator negative input.                                          |

|                                                        | C2IN1-                | AN         | _           | Comparator negative input.                                          |

|                                                        | CLCIN1 <sup>(1)</sup> | TTL/ST     | _           | Configurable Logic Cell source input.                               |

|                                                        | IOCA1                 | TTL/ST     | _           | Interrupt-on-change input.                                          |

| RA2/ANA2/C1IN0+/C2IN0+/VREF-/                          | RA2                   | TTL/ST     | CMOS/OD     | General purpose I/O.                                                |

| DAC1OUT1/IOCA2                                         | ANA2                  | AN         | _           | ADC Channel A2 input.                                               |

|                                                        | C1IN0+                | AN         | _           | Comparator positive input.                                          |

|                                                        | C2IN0+                | AN         | _           | Comparator positive input.                                          |

|                                                        | VREF-                 | AN         | _           | External ADC and/or DAC negative reference input.                   |

|                                                        | DAC1OUT1              | _          | AN          | Digital-to-Analog Converter output.                                 |

|                                                        | IOCA2                 | TTL/ST     | -           | Interrupt-on-change input.                                          |

| RA3/ANA3/C1IN1+/VREF+/                                 | RA3                   | TTL/ST     | CMOS/OD     | General purpose I/O.                                                |

| MDCARL <sup>(1)</sup> /IOCA3                           | ANA3                  | AN         | _           | ADC Channel A3 input.                                               |

|                                                        | C1IN1+                | AN         | _           | Comparator positive input.                                          |

|                                                        | VREF+                 | AN         | -           | External ADC and/or DAC positive reference input.                   |

|                                                        | MDCARL <sup>(1)</sup> | TTL/ST     | -           | Modular Carrier input 1.                                            |

|                                                        | IOCA3                 | TTL/ST     | -           | Interrupt-on-change input.                                          |

| RA4/ANA4/MDCARH <sup>(1)</sup> /T0CKI <sup>(1)</sup> / | RA4                   | TTL/ST     | CMOS/OD     | General purpose I/O.                                                |

| CCP5 <sup>(1)</sup> /IOCA4                             | ANA4                  | AN         | _           | ADC Channel A4 input.                                               |

|                                                        | MDCARH <sup>(1)</sup> | TTL/ST     | _           | Modular Carrier input 2.                                            |

|                                                        | T0CKI <sup>(1)</sup>  | TTL/ST     | _           | Timer0 clock input.                                                 |

|                                                        | CCP5 <sup>(1)</sup>   | TTL/ST     | CMOS/OD     | Capture/compare/PWM5 (default input location for capture function). |

|                                                        | IOCA4                 | TTL/ST     | l _         | Interrupt-on-change input.                                          |

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>CHV= High Voltage XTAL= Crystal levels Note

This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 13-1 for details on which PORT pins may be used for this signal. 1:

All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 13-3. 2:

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for  $I^2C$  logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

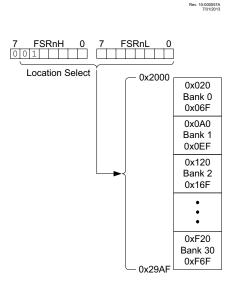

### 3.5.2 LINEAR DATA MEMORY

The linear data memory is the region from FSR address 0x2000 to FSR address 0x29AF. This region is a virtual region that points back to the 80-byte blocks of GPR memory in all the banks.

Unimplemented memory reads as 0x00. Use of the linear data memory region allows buffers to be larger than 80 bytes because incrementing the FSR beyond one bank will go directly to the GPR memory of the next bank.

The 16 bytes of common memory are not included in the linear data memory region.

# FIGURE 3-10: TRADITIONAL DATA MEMORY MAP

#### 3.5.3 DATA EEPROM MEMORY

The EEPROM memory can be read or written through NVMCONx/NVMADRx/NVMDATx the reaister interface (see section Section 10.2 "Data EEPROM Memory"). However, to make access to the EEPROM memory easier, read-only access to the EEPROM contents are also available through indirect addressing by an FSR. When the MSB of the FSR (ex: FSRxH) is set to 0x70, the lower 8-bit address value (in FSRxL) determines the EEPROM location that may be read from (through the INDF register). In other words, the EEPROM address range 0x00-0xFF is mapped into the FSR address space between 0x7000-0x70FF. Writing to the EEPROM cannot be accomplished via the FSR/INDF interface. Reads from the EEPROM through the FSR/INDF interface will require one additional instruction cycle to complete.

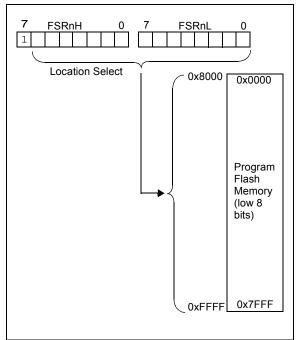

#### 3.5.4 PROGRAM FLASH MEMORY

To make constant data access easier, the entire Program Flash Memory is mapped to the upper half of the FSR address space. When the MSB of FSRnH is set, the lower 15 bits are the address in program memory which will be accessed through INDF. Only the lower eight bits of each memory location is accessible via INDF. Writing to the Program Flash Memory cannot be accomplished via the FSR/INDF interface. All instructions that access Program Flash Memory via the FSR/INDF interface will require one additional instruction cycle to complete.

#### FIGURE 3-11: PROGRAM FLASH MEMORY MAP

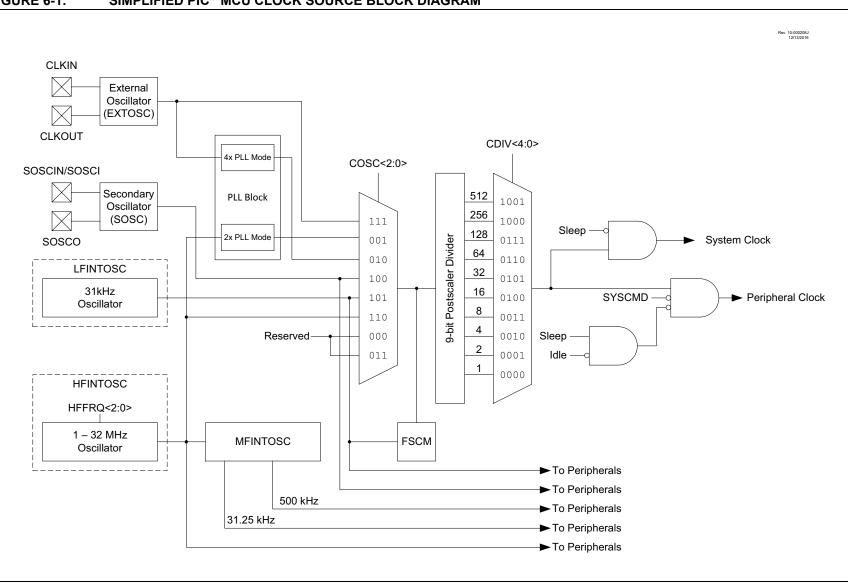

# FIGURE 6-1:

PIC16(L)F18855/75

### 6.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the RSTOSC<2:0> bits in Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the NOSC<2:0> bits in the OSCCON1 register to switch the system clock source to the internal oscillator during run-time. See Section 6.3 "Clock Switching" for more information.

In **INTOSC** mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT is available for general purpose I/O or CLKOUT.

The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators that can produce two internal system clock sources.

- The HFINTOSC (High-Frequency Internal Oscillator) is factory calibrated and operates up to 32 MHz. The frequency of HFINTOSC can be selected through the OSCFRQ Frequency Selection register, and fine-tuning can be done via the OSCTUNE register.

- The LFINTOSC (Low-Frequency Internal Oscillator) is factory-calibrated and operates at 31 kHz.

### 6.2.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a precision digitally-controlled internal clock source that produces a stable clock up to 32 MHz. The HFINTOSC can be enabled through one of the following methods:

- Programming the RSTOSC<2:0> bits in Configuration Word 1 to '110' (1 MHz) or '000' (32 MHz) to set the oscillator upon device Power-up or Reset.

- Write to the NOSC<2:0> bits of the OSCCON1 register during run-time.

The HFINTOSC frequency can be selected by setting the HFFRQ<2:0> bits of the OSCFRQ register.

The NDIV<3:0> bits of the OSCCON1 register allow for division of the HFINTOSC output from a range between 1:1 and 1:512.

# 6.5 Register Definitions: Oscillator Control

#### REGISTER 6-1: OSCCON1: OSCILLATOR CONTROL REGISTER1

| U-0   | R/W-f/f <sup>(1)</sup> | R/W-f/f <sup>(1)</sup>    | R/W-f/f <sup>(1)</sup> | R/W-q/q                      | R/W-q/q | R/W-q/q | R/W-q/q |  |  |

|-------|------------------------|---------------------------|------------------------|------------------------------|---------|---------|---------|--|--|

| _     | 1                      | NOSC<2:0> <sup>(2,3</sup> | 3)                     | NDIV<3:0> <sup>(2,3,4)</sup> |         |         |         |  |  |

| bit 7 |                        |                           |                        |                              |         |         | bit 0   |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | f = determined by fuse setting                        |

| bit 7   | Unimplemented: Read as '0'                                                  |

|---------|-----------------------------------------------------------------------------|

| bit 6-4 | NOSC<2:0>: New Oscillator Source Request bits                               |

|         | The setting requests a source oscillator and PLL combination per Table 6-1. |

|         | POR value = RSTOSC (Register 4-1).                                          |

| bit 3-0 | NDIV<3:0>: New Divider Selection Request bits                               |

|         | The setting determines the new postscaler division ratio per Table 6-1.     |

|         |                                                                             |

Note 1: The default value (f/f) is set equal to the RSTOSC Configuration bits.

- 2: If NOSC is written with a reserved value (Table 6-1), the operation is ignored and neither NOSC nor NDIV is written.

- 3: When CSWEN = 0, this register is read-only and cannot be changed from the POR value.

- 4: When NOSC = 110 (HFINTOSC 4 MHz), the NDIV bits will default to '0010' upon Reset; for all other NOSC settings the NDIV bits will default to '0000' upon Reset.

#### REGISTER 6-2: OSCCON2: OSCILLATOR CONTROL REGISTER 2

| U-0   | R-n/n <sup>(2)</sup> |  |

|-------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|--|

| —     |                      | COSC<2:0>            |                      | CDIV<3:0>            |                      |                      |                      |  |

| bit 7 |                      |                      |                      |                      |                      |                      | bit 0                |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7 | <b>Unimplemented:</b> Read as '0' |

|-------|-----------------------------------|

|       |                                   |

bit 6-4 **COSC<2:0>:** Current Oscillator Source Select bits (read-only)

Indicates the current source oscillator and PLL combination per Table 6-1.

bit 3-0 **CDIV<3:0>:** Current Divider Select bits (read-only) Indicates the current postscaler division ratio per Table 6-1.

**Note 1:** The POR value is the value present when user code execution begins.

2: The reset value (n/n) is the same as the NOSC/NDIV bits.

| U-0          | U-0                | R/W-0/0                                                                                               | R/W-0/0       | R/W-0/0         | R/W-0/0          | R/W-0/0          | R/W-0/0     |  |  |  |  |  |

|--------------|--------------------|-------------------------------------------------------------------------------------------------------|---------------|-----------------|------------------|------------------|-------------|--|--|--|--|--|

|              | _                  | RCIE                                                                                                  | TXIE          | BCL2IE          | SSP2IE           | BCL1IE           | SSP1IE      |  |  |  |  |  |

| bit 7        |                    |                                                                                                       |               |                 | I                |                  | bit 0       |  |  |  |  |  |

|              |                    |                                                                                                       |               |                 |                  |                  |             |  |  |  |  |  |

| Legend:      |                    |                                                                                                       |               |                 |                  |                  |             |  |  |  |  |  |

| R = Reada    |                    | W = Writable                                                                                          | bit           | •               | mented bit, read |                  |             |  |  |  |  |  |

|              | unchanged          | x = Bit is unkr                                                                                       | nown          | -n/n = Value    | at POR and BO    | R/Value at all o | ther Resets |  |  |  |  |  |

| '1' = Bit is | set                | '0' = Bit is cle                                                                                      | ared          |                 |                  |                  |             |  |  |  |  |  |

| bit 7-6      | Unimplemen         | nted: Read as '                                                                                       | ı,            |                 |                  |                  |             |  |  |  |  |  |

| bit 5        | •                  | T Receive Inter                                                                                       |               | it              |                  |                  |             |  |  |  |  |  |

| bit 0        |                    | the USART rec                                                                                         | •             |                 |                  |                  |             |  |  |  |  |  |

|              |                    | the USART rec                                                                                         |               |                 |                  |                  |             |  |  |  |  |  |

| bit 4        | TXIE: USAR         | T Transmit Inter                                                                                      | rupt Enable b | oit             |                  |                  |             |  |  |  |  |  |

|              |                    | the USART tra                                                                                         |               |                 |                  |                  |             |  |  |  |  |  |

| h:+ 0        |                    | the USART tra                                                                                         | •             |                 |                  |                  |             |  |  |  |  |  |

| bit 3        |                    | BCL2IE: MSSP2 Bus Collision Interrupt Enable bit<br>1 = MSSP bus Collision interrupt enabled          |               |                 |                  |                  |             |  |  |  |  |  |

|              |                    | us Collision inte                                                                                     |               |                 |                  |                  |             |  |  |  |  |  |

| bit 2        | SSP2IE: Syn        | chronous Seria                                                                                        | I Port (MSSP  | 2) Interrupt En | able bit         |                  |             |  |  |  |  |  |

|              | 1 = MSSP b         | us collision Inte                                                                                     | rrupt         |                 |                  |                  |             |  |  |  |  |  |

|              |                    | the MSSP Inte                                                                                         | •             |                 |                  |                  |             |  |  |  |  |  |

| bit 1        |                    | SP1 Bus Collisi                                                                                       |               |                 |                  |                  |             |  |  |  |  |  |

|              |                    | us collision inte<br>us collision inte                                                                |               |                 |                  |                  |             |  |  |  |  |  |

| bit 0        |                    |                                                                                                       | •             |                 | ahle hit         |                  |             |  |  |  |  |  |

| bit 0        | •                  | <b>SSP1IE:</b> Synchronous Serial Port (MSSP1) Interrupt Enable bit<br>1 = Enables the MSSP interrupt |               |                 |                  |                  |             |  |  |  |  |  |

|              |                    | the MSSP inte                                                                                         |               |                 |                  |                  |             |  |  |  |  |  |

|              |                    |                                                                                                       |               |                 |                  |                  |             |  |  |  |  |  |

| Note:        | Bit PEIE of the IN | ITCON register                                                                                        | must be       |                 |                  |                  |             |  |  |  |  |  |

|              | set to enable a    |                                                                                                       | interrupt     |                 |                  |                  |             |  |  |  |  |  |

|              | controlled by PIE1 | I-PIE8.                                                                                               |               |                 |                  |                  |             |  |  |  |  |  |

#### REGISTER 7-5: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

| U-0   | U-0 | U-0 | U-0 | U-0       | U-0 | R/W-0/0 | R/W-0/0 |  |

|-------|-----|-----|-----|-----------|-----|---------|---------|--|

| —     | —   | —   | —   | TSEL<3:0> |     |         |         |  |

| bit 7 |     |     |     |           |     |         |         |  |

|       |     |     |     |           |     |         |         |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | Unimplemented: Read as '0'                           |

|---------|------------------------------------------------------|

| bit 3-0 | TSEL<3:0>: Scanner Data Trigger Input Selection bits |

|         | 1111-1010 = Reserved                                 |

|         | 1001 = SMT2_Match                                    |

|         | 1000 = SMT1_Match                                    |

|         | 0111 = TMR5_Overflow                                 |

|         | 0110 = TMR4_postscaled                               |

|         | 0101 = TMR3_Overflow                                 |

|         | 0100 = TMR2_postscaled                               |

|         | 0011 = TMR1_Overflow                                 |

|         | 0010 = TMR0_Overflow                                 |

|         | 0001 = CLKR                                          |

0000 = LFINTOSC

#### TABLE 11-4: SUMMARY OF REGISTERS ASSOCIATED WITH CRC

| Name      | Bit 7      | Bit 6                              | Bit 5    | Bit 4    | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |  |

|-----------|------------|------------------------------------|----------|----------|--------|--------|--------|--------|---------------------|--|

| CRCACCH   | ACC<15:8>  |                                    |          |          |        |        |        |        |                     |  |

| CRCACCL   | ACC<7:0>   |                                    |          |          |        |        |        |        |                     |  |

| CRCCON0   | EN         | EN CRCGO BUSY ACCM — — SHIFTM FULL |          |          |        |        |        |        | 193                 |  |

| CRCCON1   |            | DL                                 | _EN<3:0> |          |        | PLEN   | <3:0>  |        | 193                 |  |

| CRCDATH   |            |                                    |          | DAT<     | 15:8>  |        |        |        | 194                 |  |

| CRCDATL   |            |                                    |          | DAT<     | :7:0>  |        |        |        | 194                 |  |

| CRCSHIFTH |            |                                    |          | SHIFT    | <15:8> |        |        |        | 195                 |  |

| CRCSHIFTL | SHIFT<7:0> |                                    |          |          |        |        |        |        |                     |  |

| CRCXORH   |            |                                    |          | XOR<     | 15:8>  |        |        |        | 195                 |  |

| CRCXORL   |            |                                    |          | XOR<7:1> |        |        |        | —      | 195                 |  |

| INTCON    | GIE        | PEIE                               | —        | —        | —      | —      | _      | INTEDG | 134                 |  |

| PIE4      |            |                                    | TMR6IE   | TMR5IE   | TMR4IE | TMR3IE | TMR2IE | TMR1IE | 139                 |  |

| PIR4      |            | —                                  | TMR6IF   | TMR5IF   | TMR4IF | TMR3IF | TMR2IF | TMR1IF | 148                 |  |

| SCANCON0  | EN         | SCANGO                             | BUSY     | INVALID  | INTM   | —      | MODE<  | <1:0>  | 196                 |  |

| SCANHADRH |            |                                    |          | HADR<    | <15:8> |        |        |        | 198                 |  |

| SCANHADRL |            |                                    |          | HADR     | <7:0>  |        |        |        | 198                 |  |

| SCANLADRH | LADR<15:8> |                                    |          |          |        |        |        |        | 197                 |  |

| SCANLADRL |            |                                    |          | LADR     | <7:0>  |        |        |        | 197                 |  |

| SCANTRIG  | _          |                                    |          | _        |        | TSEL   | <3:0>  |        | 199                 |  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for the CRC module.

\* Page provides register information.

# 13.0 PERIPHERAL PIN SELECT (PPS) MODULE

The Peripheral Pin Select (PPS) module connects peripheral inputs and outputs to the device I/O pins. Only digital signals are included in the selections. All analog inputs and outputs remain fixed to their assigned pins. Input and output selections are independent as shown in the simplified block diagram Figure 13-1.

|                      |                        | Default  |                      |       | Rem   | appable to | Pins of P | ORTx      |       |   |

|----------------------|------------------------|----------|----------------------|-------|-------|------------|-----------|-----------|-------|---|

| Input Signal<br>Name | Input Register<br>Name | Location | Location PIC16F18855 |       | 55    |            | I         | PIC16F188 | 75    |   |

|                      | at POR                 | PORTA    | PORTB                | PORTC | PORTA | PORTB      | PORTC     | PORTD     | PORTE |   |

| INT                  | INTPPS                 | RB0      | •                    | •     |       | •          | •         |           |       |   |

| T0CKI                | <b>T0CKIPPS</b>        | RA4      | •                    | •     |       | •          | •         |           |       |   |

| T1CKI                | T1CKIPPS               | RC0      | •                    |       | •     | •          |           | •         |       |   |

| T1G                  | T1GPPS                 | RB5      |                      | •     | •     |            | •         | •         |       |   |

| T3CKI                | T3CKIPPS               | RC0      |                      | •     | •     |            | •         | •         |       |   |

| T3G                  | T3GPPS                 | RC0      | •                    |       | •     | •          |           | •         |       |   |

| T5CKI                | T5CKIPPS               | RC2      | •                    |       | •     | •          |           | •         |       |   |

| T5G                  | T5GPPS                 | RB4      |                      | •     | •     |            | •         |           | •     |   |

| T2IN                 | T2INPPS                | RC3      | •                    |       | •     |            | •         |           | ٠     |   |

| T4IN                 | T4INPPS                | RC5      |                      | •     | •     |            | •         | •         |       |   |

| T6IN                 | T6INPPS                | RB7      |                      | •     | •     |            | •         |           | •     |   |

| CCP1                 | CCP1PPS                | RC2      |                      | •     | •     |            | •         | •         |       |   |

| CCP2                 | CCP2PPS                | RC1      |                      | •     | •     |            | •         | •         |       |   |

| CCP3                 | CCP3PPS                | RB5      |                      | •     | •     |            | •         |           | •     |   |

| CCP4                 | CCP4PPS                | RB0      |                      | •     | •     |            | •         |           | •     |   |

| CCP5                 | CCP5PPS                | RA4      | •                    |       | •     | •          |           |           |       | • |

| SMTWIN1              | SMTWIN1PPS             | RC0      |                      | •     | •     |            | •         |           |       |   |

| SMTSIG1              | SMTSIG1PPS             | RC1      |                      | •     | •     |            | •         |           |       |   |

| SMTWIN2              | SMTWIN2PPS             | RB4      |                      | •     | •     |            | •         |           | •     |   |

| SMTSIG2              | SMTSIG2PPS             | RB5      |                      | •     | •     |            | •         |           | •     |   |

| CWG1IN               | CWG1PPS                | RB0      |                      | •     | •     |            | •         |           | •     |   |

| CWG2IN               | CWG2PPS                | RB1      |                      | •     | •     |            | •         |           | •     |   |

| CWG3IN               | CWG3PPS                | RB2      |                      | •     | •     |            | •         |           | •     |   |

| MDCARL               | MDCARLPPS              | RA3      | •                    |       | •     | •          |           |           | •     |   |

| MDCARH               | MDCARHPPS              | RA4      | •                    |       | •     | •          |           |           | •     |   |

| MDMSRC               | MDSRCPPS               | RA5      | •                    |       | •     | •          |           |           | •     |   |

| CLCIN0               | CLCIN0PPS              | RA0      | •                    |       | •     | •          |           | •         |       |   |

| CLCIN1               | CLCIN1PPS              | RA1      | •                    |       | •     | •          |           | •         |       |   |

| CLCIN2               | CLCIN2PPS              | RB6      |                      | •     | ٠     |            | •         |           | ٠     |   |

TABLE 13-1:PPS INPUT SIGNAL ROUTING OPTIONS

### 20.3 Selectable Input Sources

The CWG generates the output waveforms from the input sources in Table 20-2.

#### TABLE 20-2: SELECTABLE INPUT SOURCES

| Source Peripheral | Signal Name |

|-------------------|-------------|

| CWG input PPS pin | CWGxIN PPS  |

| CCP1              | CCP1_out    |

| CCP2              | CCP2_out    |

| CCP3              | CCP3_out    |

| CCP4              | CCP4_out    |

| CCP5              | CCP5_out    |

| PWM6              | PWM6_out    |

| PWM7              | PWM7_out    |

| NCO               | NCO1_out    |

| Comparator C1     | C1OUT_sync  |

| Comparator C2     | C2OUT_sync  |

| DSM               | DSM_out     |

| CLC1              | LC1_out     |

| CLC2              | LC2_out     |

| CLC3              | LC3_out     |

| CLC4              | LC4_out     |

The input sources are selected using the CWGxISM register.

# 20.4 Output Control

#### 20.4.1 OUTPUT ENABLES

Each CWG output pin has individual output enable control. Output enables are selected with the Gx1OEx <3:0> bits. When an output enable control is cleared, the module asserts no control over the pin. When an output enable is set, the override value or active PWM waveform is applied to the pin per the port priority selection. The output pin enables are dependent on the module enable bit, EN of the CWGxCON0 register. When EN is cleared, CWG output enables and CWG drive levels have no effect.

### 20.4.2 POLARITY CONTROL

The polarity of each CWG output can be selected independently. When the output polarity bit is set, the corresponding output is active-high. Clearing the output polarity bit configures the corresponding output as active-low. However, polarity does not affect the override levels. Output polarity is selected with the POLx bits of the CWGxCON1. Auto-shutdown and steering options are unaffected by polarity.

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u                                               | R/W-x/u          | R/W-x/u  | R/W-x/u |  |

|------------------|---------|-------------------|---------|-------------------------------------------------------|------------------|----------|---------|--|

|                  |         |                   | ADRE    | S<7:0>                                                |                  |          |         |  |

| bit 7            |         |                   |         |                                                       |                  |          | bit 0   |  |

|                  |         |                   |         |                                                       |                  |          |         |  |

| Legend:          |         |                   |         |                                                       |                  |          |         |  |

| R = Readable     | bit     | W = Writable I    | bit     | U = Unimpler                                          | nented bit, read | d as '0' |         |  |

| u = Bit is unch  | anged   | x = Bit is unkn   | iown    | -n/n = Value at POR and BOR/Value at all other Resets |                  |          |         |  |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                                                       |                  |          |         |  |

#### REGISTER 23-19: ADRESL: ADC RESULT REGISTER LOW, ADFRM=1

bit 7-0 ADRES<7:0>: ADC Result Register bits. Least Significant eight bits of 10-bit conversion result.

#### REGISTER 23-20: ADPREVH: ADC PREVIOUS RESULT REGISTER

| R-x          | R-x | R-x | R-x | R-x | R-x | R-x | R-x   |  |  |

|--------------|-----|-----|-----|-----|-----|-----|-------|--|--|

| ADPREV<15:8> |     |     |     |     |     |     |       |  |  |

| bit 7        |     |     |     |     |     |     | bit 0 |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

ADPREV<15:8>: Previous ADC Results Most Significant Byte

If ADPSIS = 1:

Most Significant Byte of ADFLTR at the start of current ADC conversion

If ADPSIS = 0:

Most Significant bits of ADRES at the start of current ADC conversion<sup>(1)</sup>

**Note 1:** If ADPSIS = 0, ADPREVH and ADPREVL are formatted the same way as ADRES is, depending on the ADFRM bit.

## 24.2 FIXED DUTY CYCLE MODE

In Fixed Duty Cycle (FDC) mode, every time the accumulator overflows (NCO\_overflow), the output is toggled. This provides a 50% duty cycle, provided that the increment value remains constant. For more information, see Figure 24-2.

The FDC mode is selected by clearing the N1PFM bit in the NCO1CON register.

### 24.3 PULSE FREQUENCY MODE

In Pulse Frequency (PF) mode, every time the Accumulator overflows, the output becomes active for one or more clock periods. Once the clock period expires, the output returns to an inactive state. This provides a pulsed output. The output becomes active on the rising clock edge immediately following the overflow event. For more information, see Figure 24-2.

The value of the active and inactive states depends on the polarity bit, N1POL in the NCO1CON register.

The PF mode is selected by setting the N1PFM bit in the NCO1CON register.

#### 24.3.1 OUTPUT PULSE WIDTH CONTROL

When operating in PF mode, the active state of the output can vary in width by multiple clock periods. Various pulse widths are selected with the N1PWS<2:0> bits in the NCO1CLK register.

When the selected pulse width is greater than the Accumulator overflow time frame, then DDS operation is undefined.

## 24.4 OUTPUT POLARITY CONTROL

The last stage in the NCO module is the output polarity. The N1POL bit in the NCO1CON register selects the output polarity. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

The NCO output signal is available to the following peripherals:

- CLC

- CWG

- Timer1/3/5

- Timer2/4/6

- SMT

- DSM

- Reference Clock Output

#### 24.5 Interrupts