Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XF

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 25                                                                           |

| Program Memory Size        | 14KB (8K x 14)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 28-QFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18855t-i-ml |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                                                                              | Function              | Input Type             | Output Type | Description                                                                                 |

|-------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------|-------------|---------------------------------------------------------------------------------------------|

| RA5/ANA5/SS1 <sup>(1)</sup> /MDSRC <sup>(1)</sup> /IOCA5                                                          | RA5                   | TTL/ST                 | CMOS/OD     | General purpose I/O.                                                                        |

|                                                                                                                   | ANA5                  | AN                     | _           | ADC Channel A5 input.                                                                       |

|                                                                                                                   | SS1 <sup>(1)</sup>    | TTL/ST                 | _           | MSSP1 SPI slave select input.                                                               |

|                                                                                                                   | MDSRC <sup>(1)</sup>  | TTL/ST                 | _           | Modulator Source input.                                                                     |

|                                                                                                                   | IOCA5                 | TTL/ST                 | -           | Interrupt-on-change input.                                                                  |

| RA6/ANA6/OSC2/CLKOUT/IOCA6                                                                                        | RA6                   | TTL/ST                 | CMOS/OD     | General purpose I/O.                                                                        |

|                                                                                                                   | ANA6                  | AN                     | -           | ADC Channel A6 input.                                                                       |

|                                                                                                                   | OSC2                  | _                      | XTAL        | External Crystal/Resonator (LP, XT, HS modes) driver out-<br>put.                           |

|                                                                                                                   | CLKOUT                | —                      | CMOS/OD     | Fosc/4 digital output (in non-crystal/resonator modes).                                     |

|                                                                                                                   | IOCA6                 | TTL/ST                 | -           | Interrupt-on-change input.                                                                  |

| RA7/ANA7/OSC1/CLKIN/IOCA7                                                                                         | RA7                   | TTL/ST                 | CMOS/OD     | General purpose I/O.                                                                        |

|                                                                                                                   | ANA7                  | AN                     | _           | ADC Channel A7 input.                                                                       |

|                                                                                                                   | OSC1                  | XTAL                   | _           | External Crystal/Resonator (LP, XT, HS modes) driver input.                                 |

|                                                                                                                   | CLKIN                 | TTL/ST                 | _           | External digital clock input.                                                               |

|                                                                                                                   | IOCA7                 | TTL/ST                 | _           | Interrupt-on-change input.                                                                  |

| RB0/ANB0/C2IN1+/ZCD/SS2 <sup>(1)</sup> /<br>CCP4 <sup>(1)</sup> /CWG1IN <sup>(1)</sup> /INT <sup>(1)</sup> /IOCB0 | RB0                   | TTL/ST                 | CMOS/OD     | General purpose I/O.                                                                        |

| CCP4 <sup>(1)</sup> /CWG1IN <sup>(1)</sup> /INT <sup>(1)</sup> /IOCB0                                             | ANB0                  | AN                     | _           | ADC Channel B0 input.                                                                       |

|                                                                                                                   | C2IN1+                | AN                     | _           | Comparator positive input.                                                                  |

|                                                                                                                   | ZCD                   | AN                     | AN          | Zero-cross detect input pin (with constant current sink/<br>source).                        |

|                                                                                                                   | SS2 <sup>(1)</sup>    | TTL/ST                 | -           | MSSP2 SPI slave select input.                                                               |

|                                                                                                                   | CCP4 <sup>(1)</sup>   | TTL/ST                 | CMOS/OD     | Capture/compare/PWM4 (default input location for capture function).                         |

|                                                                                                                   | CWG1IN <sup>(1)</sup> | TTL/ST                 | -           | Complementary Waveform Generator 1 input.                                                   |

|                                                                                                                   | INT <sup>(1)</sup>    | TTL/ST                 | -           | External interrupt request input.                                                           |

|                                                                                                                   | IOCB0                 | TTL/ST                 | -           | Interrupt-on-change input.                                                                  |

| RB1/ANB1/C1IN3-/C2IN3-/SCL2 <sup>(3,4)</sup> /<br>SCK2 <sup>(1)</sup> /CWG2IN <sup>(1)</sup> /IOCB1               | RB1                   | TTL/ST                 | CMOS/OD     | General purpose I/O.                                                                        |

| SCK2 <sup>(1)</sup> /CWG2IN <sup>(1)</sup> /IOCB1                                                                 | ANB1                  | AN                     | _           | ADC Channel B1 input.                                                                       |

|                                                                                                                   | C1IN3-                | AN                     | _           | Comparator negative input.                                                                  |

|                                                                                                                   | C2IN3-                | AN                     | _           | Comparator negative input.                                                                  |

|                                                                                                                   | SCL2 <sup>(3,4)</sup> | I <sup>2</sup> C/SMBus | OD          | MSSP2 I <sup>2</sup> C clock input/output.                                                  |

|                                                                                                                   | SCK2 <sup>(1)</sup>   | TTL/ST                 | CMOS/OD     | MSSP2 SPI serial clock (default input location, SCK2 is a PPS remappable input and output). |

|                                                                                                                   | CWG2IN <sup>(1)</sup> | TTL/ST                 | _           | Complementary Waveform Generator 2 input.                                                   |

|                                                                                                                   | IOCB1                 | TTL/ST                 | _           | Interrupt-on-change input.                                                                  |

#### TABLE 1-3: PIC16F18875 PINOUT DESCRIPTION (CONTINUED)

Legend:

AN

= Analog input or output TTL

CMOS

= CMOS compatible input or output ST

OD

= Open-Drain

TTL

TTL compatible input High Voltage XTAL= Crystal levels

ST

= Schmitt Trigger input with CMOS levels

I<sup>2</sup>C

= Schmitt Trigger input with I<sup>2</sup>CHV=

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 13-1 for details on which PORT pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 13-3.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

## TABLE 3-8: PIC16(L)F18855/75 MEMORY MAP, BANK 28

|      | Bank 28  |

|------|----------|

| E0Ch | —        |

| E0Dh | —        |

| E0Eh | _        |

| E0Fh | CLCDATA  |

| E10h | CLC1CON  |

| E11h | CLC1POL  |

| E12h | CLC1SEL0 |

| E13h | CLC1SEL1 |

| E14h | CLC1SEL2 |

| E15h | CLC1SEL3 |

| E16h | CLC1GLS0 |

| E17h | CLC1GLS1 |

| E18h | CLC1GLS2 |

| E19h | CLC1GLS3 |

| E1Ah | CLC2CON  |

| E1Bh | CLC2POL  |

| E1Ch | CLC2SEL0 |

| E1Dh | CLC2SEL1 |

| E1Eh | CLC2SEL2 |

| E1Fh | CLC2SEL3 |

| E20h | CLC2GLS0 |

| E21h | CLC2GLS1 |

| E22h | CLC2GLS2 |

| E23h | CLC2GLS3 |

| E24h | CLC3CON  |

| E25h | CLC3POL  |

| E26h | CLC3SEL0 |

| E27h | CLC3SEL1 |

| E28h | CLC3SEL2 |

| E29h | CLC3SEL3 |

| E2Ah | CLC3GLS0 |

| E2Bh | CLC3GLS1 |

| E2Ch | CLC3GLS2 |

| E2Dh | CLC3GLS3 |

|      |          |

|      | Bank 28  |

|------|----------|

| E2Eh | CLC4CON  |

| E2Fh | CLC4POL  |

| E30h | CLC4SEL0 |

| E31h | CLC4SEL1 |

| E32h | CLC4SEL2 |

| E33h | CLC4SEL3 |

| E34h | CLC4GLS0 |

| E35h | CLC4GLS1 |

| E36h | CLC4GLS2 |

| E37h | CLC4GLS3 |

| E38h |          |

|      | _        |

| E6Fh |          |

Legend:

= Unimplemented data memory locations, read as '0'.

|         |                                                 |                                  |                              |                         |       | BLE 3-13: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED) |              |       |        |         |                       |                              |

|---------|-------------------------------------------------|----------------------------------|------------------------------|-------------------------|-------|--------------------------------------------------------------------|--------------|-------|--------|---------|-----------------------|------------------------------|

| Address | Name                                            | PIC16(L)F18855<br>PIC16(L)F18875 | Bit 7                        | Bit 6                   | Bit 5 | Bit 4                                                              | Bit 3        | Bit 2 | Bit 1  | Bit 0   | Value on:<br>POR, BOR | Value on all<br>other Resets |

| Bank 9  |                                                 |                                  |                              |                         |       |                                                                    |              |       |        |         |                       |                              |

|         | CPU CORE REGISTERS; see Table 3-2 for specifics |                                  |                              |                         |       |                                                                    |              |       |        |         |                       |                              |

| 48Ch \$ | SMT1TMRL                                        |                                  |                              | TMR<7:0>                |       |                                                                    |              |       |        |         | 0000 0000             | 0000 0000                    |

| 48Dh \$ | SMT1TMRH                                        |                                  |                              |                         |       |                                                                    | TMR<15:8>    |       |        |         | 0000 0000             | 0000 0000                    |

| 48Eh \$ | SMT1TMRU                                        |                                  |                              |                         |       | -                                                                  | [MR<23:16>   |       |        |         | 0000 0000             | 0000 0000                    |

| 48Fh \$ | SMT1CPRL                                        |                                  |                              | CPR<7:0>                |       |                                                                    |              |       |        |         |                       | uuuu uuuu                    |

| 490h \$ | SMT1CPRH                                        |                                  |                              | CPR<15:8>               |       |                                                                    |              |       |        |         |                       | uuuu uuuu                    |

| 491h \$ | SMT1CPRU                                        |                                  |                              | CPR<23:16>              |       |                                                                    |              |       |        |         |                       | uuuu uuuu                    |

| 492h \$ | SMT1CPWL                                        |                                  |                              | CPW<7:0>                |       |                                                                    |              |       |        |         | xxxx xxxx             | uuuu uuuu                    |

| 493h \$ | SMT1CPWH                                        |                                  |                              |                         |       |                                                                    | CPW<15:8>    |       |        |         | xxxx xxxx             | uuuu uuuu                    |

| 494h \$ | SMT1CPWU                                        |                                  |                              |                         |       | (                                                                  | CPW<23:16>   |       |        |         | xxxx xxxx             | uuuu uuuu                    |

| 495h \$ | SMT1PRL                                         |                                  |                              |                         |       |                                                                    | PR<7:0>      |       |        |         | 1111 1111             | 1111 1111                    |

| 496h \$ | SMT1PRH                                         |                                  |                              |                         |       |                                                                    | PR<15:8>     |       |        |         | 1111 1111             | 1111 1111                    |

| 497h \$ | SMT1PRU                                         |                                  |                              |                         |       |                                                                    | PR<23:16>    |       |        |         | 1111 1111             | 1111 1111                    |

| 498h \$ | SMT1CON0                                        |                                  | EN                           | _                       | STP   | WPOL                                                               | SPOL         | CPOL  | SMT1F  | PS<1:0> | 0-00 0000             | 0-00 0000                    |

| 499h \$ | SMT1CON1                                        |                                  | SMT1GO                       | SMT1GO REPEAT MODE<3:0> |       |                                                                    |              |       |        |         | 00 0000               | 00 0000                      |

| 49Ah \$ | SMT1STAT                                        |                                  | CPRUP CPWUP RST — — TS WS AS |                         |       |                                                                    |              |       | 000000 | 000000  |                       |                              |

| 49Bh \$ | SMT1CLK                                         |                                  | CSEL<2:0>                    |                         |       |                                                                    |              |       | 000    | 000     |                       |                              |

| 49Ch \$ | SMT1SIG                                         |                                  |                              |                         |       |                                                                    |              |       | 0 0000 | 0 0000  |                       |                              |

| 49Dh \$ | SMT1WIN                                         |                                  | — — — WSEL<4:0>              |                         |       |                                                                    |              |       | 0 0000 | 0 0000  |                       |                              |

| 49Eh    | _                                               | —                                |                              | Unimplemented           |       |                                                                    |              |       |        |         | —                     | —                            |

| 49Fh    | _                                               | —                                |                              |                         |       | U                                                                  | nimplemented |       |        |         | —                     | _                            |

#### CIGTED SUMMADY DANKS 0.24 (CONTINUED)

Legend: x = unknown, u = unchanged, q =depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Register present on PIC16F18855/75 devices only. Unimplemented, read as '1'. Note 1:

2:

| Address         | Name                | PIC16(L)F18855<br>PIC16(L)F18875 | Bit 7    | Bit 6    | Bit 5    | Bit 4       | Bit 3        | Bit 2    | Bit 1        | Bit 0    | Value on:<br>POR, BOR | Value on all<br>other Resets |

|-----------------|---------------------|----------------------------------|----------|----------|----------|-------------|--------------|----------|--------------|----------|-----------------------|------------------------------|

| Bank 28 (0      | Bank 28 (Continued) |                                  |          |          |          |             |              |          |              |          |                       |                              |

| E22h            | CLC2GLS2            |                                  | LC2G3D4T | LC2G3D4N | LC2G3D3T | LC2G3D3N    | LC2G3D2T     | LC2G3D2N | LC2G3D1T     | LC2G3D1N | xxxx xxxx             | uuuu uuuu                    |

| E23h            | CLC2GLS3            |                                  | LC2G4D4T | LC2G4D4N | LC2G4D3T | LC2G4D3N    | LC2G4D2T     | LC2G4D2N | LC2G4D1T     | LC2G4D1N | xxxx xxxx             | uuuu uuuu                    |

| E24h            | CLC3CON             |                                  | LC3EN    | —        | LC3OUT   | LC3INTP     | LC3INTN      |          | LC3MODE<2:0> |          | 0-x0 0000             | 0-x0 0000                    |

| E25h            | CLC3POL             |                                  | LC3POL   | —        | _        | _           | LC3G4POL     | LC3G3POL | LC3G2POL     | LC3G1POL | 0 xxxx                | 0 uuuu                       |

| E26h            | CLC3SEL0            |                                  | —        | _        |          |             | LC3          | D1S<5:0> |              |          | xx xxxx               | uu uuuu                      |

| E27h            | CLC3SEL1            |                                  | —        | —        |          |             | LC3          | D2S<5:0> |              |          | xx xxxx               | uu uuuu                      |

| E28h            | CLC3SEL2            |                                  | —        | —        |          | LC3D3S<5:0> |              |          |              |          | xx xxxx               | uu uuuu                      |

| E29h            | CLC3SEL3            |                                  | —        | _        |          | LC3D4S<5:0> |              |          |              |          | xx xxxx               | uu uuuu                      |

| E2Ah            | CLC3GLS0            |                                  | LC3G1D4T | LC3G1D4N | LC3G1D3T | LC3G1D3N    | LC3G1D2T     | LC3G1D2N | LC3G1D1T     | LC3G1D1N | xxxx xxxx             | uuuu uuuu                    |

| E2Bh            | CLC3GLS1            |                                  | LC3G2D4T | LC3G2D4N | LC3G2D3T | LC3G2D3N    | LC3G2D2T     | LC3G2D2N | LC3G2D1T     | LC3G2D1N | xxxx xxxx             | uuuu uuuu                    |

| E2Ch            | CLC3GLS2            |                                  | LC3G3D4T | LC3G3D4N | LC3G3D3T | LC3G3D3N    | LC3G3D2T     | LC3G3D2N | LC3G3D1T     | LC3G3D1N | xxxx xxxx             | uuuu uuuu                    |

| E2Dh            | CLC3GLS3            |                                  | LC3G4D4T | LC3G4D4N | LC3G4D3T | LC3G4D3N    | LC3G4D2T     | LC3G4D2N | LC3G4D1T     | LC3G4D1N | xxxx xxxx             | uuuu uuuu                    |

| E2Eh            | CLC4CON             |                                  | LC4EN    | —        | LC4OUT   | LC4INTP     | LC4INTN      |          | LC4MODE<2:0> |          | 0-x0 0000             | 0-x0 0000                    |

| E2Fh            | CLC4POL             |                                  | LC4POL   | —        | —        |             | LC4G4POL     | LC4G3POL | LC4G2POL     | LC4G1POL | 0 xxxx                | 0 uuuu                       |

| E30h            | CLC4SEL0            |                                  | —        | —        |          |             | LC4          | D1S<5:0> |              |          | xx xxxx               | uu uuuu                      |

| E31h            | CLC4SEL1            |                                  | —        | —        |          |             | LC4          | D2S<5:0> |              |          | xx xxxx               | uu uuuu                      |

| E32h            | CLC4SEL2            |                                  | —        | —        |          |             | LC4          | D3S<5:0> |              |          | xx xxxx               | uu uuuu                      |

| E33h            | CLC4SEL3            |                                  | _        | —        |          |             | LC4          | D4S<5:0> |              |          | xx xxxx               | uu uuuu                      |

| E34h            | CLC4GLS0            |                                  | LC4G1D4T | LC4G1D4N | LC4G1D3T | LC4G1D3N    | LC4G1D2T     | LC4G1D2N | LC4G1D1T     | LC4G1D1N | xxxx xxxx             | uuuu uuuu                    |

| E35h            | CLC4GLS1            |                                  | LC4G2D4T | LC4G2D4N | LC4G2D3T | LC4G2D3N    | LC4G2D2T     | LC4G2D2N | LC4G2D1T     | LC4G2D1N | xxxx xxxx             | uuuu uuuu                    |

| E36h            | CLC4GLS2            |                                  | LC4G3D4T | LC4G3D4N | LC4G3D3T | LC4G3D3N    | LC4G3D2T     | LC4G3D2N | LC4G3D1T     | LC4G3D1N | xxxx xxxx             | uuuu uuuu                    |

| E37h            | CLC4GLS3            |                                  | LC4G4D4T | LC4G4D4N | LC4G4D3T | LC4G4D3N    | LC4G4D2T     | LC4G4D2N | LC4G4D1T     | LC4G4D1N | xxxx xxxx             | uuuu uuuu                    |

| E38h to<br>E6Fh |                     | —                                |          |          |          | U           | nimplemented |          |              |          | _                     | —                            |

#### TABLE 3-13: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED)

Legend: x = unknown, u = unchanged, g =depends on condition, - = unimplemented, read as '0', x = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Register present on PIC16F18855/75 devices only.

2: Unimplemented, read as '1'.

### TABLE 3-13: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED)

| -       |                     |                |                |       |                   |       |       |              |        |        |        |                       |                              |

|---------|---------------------|----------------|----------------|-------|-------------------|-------|-------|--------------|--------|--------|--------|-----------------------|------------------------------|

| Address | Name                | PIC16(L)F18855 | PIC16(L)F18875 | Bit 7 | Bit 6             | Bit 5 | Bit 4 | Bit 3        | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on all<br>other Resets |

| Bank 30 | Bank 30 (Continued) |                |                |       |                   |       |       |              |        |        |        |                       |                              |

| F6Bh    | IOCEF               |                |                | _     | IOCEF3 0          |       |       |              |        |        | 0      |                       |                              |

| F6Ch    | CCDNE               | -              | х              | -     | -                 | _     | -     | -            | CCDNE2 | CCDNE1 | CCDNE0 | 000                   | 000                          |

|         |                     | х              | -              |       |                   |       | Uı    | nimplemented |        |        |        |                       |                              |

| F6Dh    | CCDPE               | —              | х              | —     | —                 | —     | —     | —            | CCDPE2 | CCDPE1 | CCDPE0 | 000                   | 000                          |

|         |                     | х              | —              |       | Unimplemented     |       |       |              |        |        |        |                       |                              |

| F6Eh    | _                   | _              | -              |       | Unimplemented — — |       |       |              |        |        |        |                       |                              |

| F6Fh    | _                   | -              | -              |       |                   |       | Uı    | nimplemented |        |        |        | _                     | _                            |

PIC16(L)F18855/75

Legend: x = unknown, u = unchanged, q =depends on condition, - = unimplemented, read as '0', x = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Register present on PIC16F18855/75 devices only.

2: Unimplemented, read as '1'.

### 5.12 Power Control (PCON) Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Watchdog Timer Window Violation Reset

(WDTWV)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

The PCON0 register bits are shown in Register 5-2.

Hardware will change the corresponding register bit during the Reset process; if the Reset was not caused by the condition, the bit remains unchanged (Table 5-4).

Software should reset the bit to the inactive state after the restart (hardware will not reset the bit).

Software may also set any PCON bit to the active state, so that user code may be tested, but no reset action will be generated.

# 6.0 OSCILLATOR MODULE (WITH FAIL-SAFE CLOCK MONITOR)

### 6.1 Overview

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 6-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from external oscillators, quartz-crystal resonators and ceramic resonators. In addition, the system clock source can be supplied from one of two internal oscillators and PLL circuits, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software.

- Fail-Safe Clock Monitor (FSCM) designed to detect a failure of the external clock source (LP, XT, HS, ECH, ECM, ECL) and switch automatically to the internal oscillator.

- Oscillator Start-up Timer (OST) ensures stability of crystal oscillator sources.

The RSTOSC bits of Configuration Word 1 determine the type of oscillator that will be used when the device reset, including when it is first powered up.

The internal clock modes, LFINTOSC, HFINTOSC (set at 1 MHz), or HFINTOSC (set at 32 MHz) can be set through the RSTOSC bits.

If an external clock source is selected, the FEXTOSC bits of Configuration Word 1 must be used in conjunction with the RSTOSC bits to select the external clock mode.

The external oscillator module can be configured in one of the following clock modes, by setting the FEXTOSC<2:0> bits of Configuration Word 1:

- 1. ECL External Clock Low-Power mode (below 500 kHz)

- 2. ECM External Clock Medium Power mode (500 kHz to 8 MHz)

- 3. ECH External Clock High-Power mode (above 8 MHz)

- 4. LP 32 kHz Low-Power Crystal mode.

- 5. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode (between 100 kHz and 4 MHz)

- 6. HS High Gain Crystal or Ceramic Resonator mode (above 4 MHz)

The ECH, ECM, and ECL clock modes rely on an external logic level signal as the device clock source. The LP, XT, and HS clock modes require an external crystal or resonator to be connected to the device. Each mode is optimized for a different frequency range. The INTOSC internal oscillator block produces low and high-frequency clock sources, designated LFINTOSC and HFINTOSC. (see Internal Oscillator Block, Figure 6-1). A wide selection of device clock frequencies may be derived from these clock sources.

### 6.5 Register Definitions: Oscillator Control

#### REGISTER 6-1: OSCCON1: OSCILLATOR CONTROL REGISTER1

| U-0   | R/W-f/f <sup>(1)</sup> | R/W-f/f <sup>(1)</sup>    | R/W-f/f <sup>(1)</sup> | R/W-q/q | R/W-q/q | R/W-q/q                | R/W-q/q |

|-------|------------------------|---------------------------|------------------------|---------|---------|------------------------|---------|

| _     | 1                      | NOSC<2:0> <sup>(2,3</sup> | 3)                     |         | NDIV<3  | :0> <sup>(2,3,4)</sup> |         |

| bit 7 |                        |                           |                        |         |         |                        | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | f = determined by fuse setting                        |

| bit 7   | Unimplemented: Read as '0'                                                  |

|---------|-----------------------------------------------------------------------------|

| bit 6-4 | NOSC<2:0>: New Oscillator Source Request bits                               |

|         | The setting requests a source oscillator and PLL combination per Table 6-1. |

|         | POR value = RSTOSC (Register 4-1).                                          |

| bit 3-0 | NDIV<3:0>: New Divider Selection Request bits                               |

|         | The setting determines the new postscaler division ratio per Table 6-1.     |

|         |                                                                             |

Note 1: The default value (f/f) is set equal to the RSTOSC Configuration bits.

- 2: If NOSC is written with a reserved value (Table 6-1), the operation is ignored and neither NOSC nor NDIV is written.

- 3: When CSWEN = 0, this register is read-only and cannot be changed from the POR value.

- 4: When NOSC = 110 (HFINTOSC 4 MHz), the NDIV bits will default to '0010' upon Reset; for all other NOSC settings the NDIV bits will default to '0000' upon Reset.

#### REGISTER 6-2: OSCCON2: OSCILLATOR CONTROL REGISTER 2

| U-0   | R-n/n <sup>(2)</sup> |

|-------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| —     |                      | COSC<2:0>            |                      |                      | CDIV                 | <3:0>                |                      |

| bit 7 |                      |                      |                      |                      |                      |                      | bit 0                |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7 | <b>Unimplemented:</b> Read as '0' |

|-------|-----------------------------------|

|       |                                   |

bit 6-4 **COSC<2:0>:** Current Oscillator Source Select bits (read-only)

Indicates the current source oscillator and PLL combination per Table 6-1.

bit 3-0 **CDIV<3:0>:** Current Divider Select bits (read-only) Indicates the current postscaler division ratio per Table 6-1.

**Note 1:** The POR value is the value present when user code execution begins.

2: The reset value (n/n) is the same as the NOSC/NDIV bits.

## 9.0 WINDOWED WATCHDOG TIMER (WWDT)

The Watchdog Timer (WDT) is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events. The Windowed Watchdog Timer (WDT) differs in that CLRWDT instructions are only accepted when they are performed within a specific window during the time-out period.

The WDT has the following features:

- · Selectable clock source

- · Multiple operating modes

- WDT is always on

- WDT is off when in Sleep

- WDT is controlled by software

- WDT is always off

- Configurable time-out period is from 1 ms to 256 seconds (nominal)

- Configurable window size from 12.5 to 100 percent of the time-out period

- Multiple Reset conditions

- Operation during Sleep

## 11.0 CYCLIC REDUNDANCY CHECK (CRC) MODULE

The Cyclic Redundancy Check (CRC) module provides a software-configurable hardware-implemented CRC checksum generator. This module includes the following features:

- · Any standard CRC up to 16 bits can be used

- · Configurable Polynomial

- · Any seed value up to 16 bits can be used

- · Standard and reversed bit order available

- Augmented zeros can be added automatically or by the user

- Memory scanner for fast CRC calculations on program memory user data

- Software loadable data registers for calculating CRC values not from the memory scanner

### 11.1 CRC Module Overview

The CRC module provides a means for calculating a check value of program memory. The CRC module is coupled with a memory scanner for faster CRC calculations. The memory scanner can automatically provide data to the CRC module. The CRC module can also be operated by directly writing data to SFRs, without using the scanner.

#### 11.2 CRC Functional Overview

The CRC module can be used to detect bit errors in the Flash memory using the built-in memory scanner or through user input RAM memory. The CRC module can accept up to a 16-bit polynomial with up to a 16-bit seed value. A CRC calculated check value (or checksum) will then be generated into the CRCACC<15:0> registers for user storage. The CRC module uses an XOR shift register implementation to perform the polynomial division required for the CRC calculation.

#### EXAMPLE 11-1: BASIC CRC OPERATION EXAMPLE

#### CRC-16-ANSI

```

x<sup>16</sup> + x<sup>15</sup> + x<sup>2</sup> + 1 (17 bits)

```

Standard 16-bit representation = 0x8005

CRCXORH = 0b10000000 CRCXORL = 0b0000010- (1)

Data Sequence: 0x55, 0x66, 0x77, 0x88

DLEN = 0b0111 PLEN = 0b1111

Data entered into the CRC: SHIFTM = 0:

01010101 01100110 01110111 10001000

SHIFTM = 1: 10101010 01100110 11101110 00010001

Check Value (ACCM = 1):

SHIFTM = 0: 0x32D6 CRCACCH = 0b00110010 CRCACCL = 0b11010110

SHIFTM = 1: 0x6BA2 CRCACCH = 0b01101011 CRCACCL = 0b10100010

Note 1: Bit 0 is unimplemented. The LSb of any CRC polynomial is always '1' and will always be treated as a '1' by the CRC for calculating the CRC check value. This bit will be read in software as a '0'.

## 11.3 CRC Polynomial Implementation

Any standard polynomial up to 17 bits can be used. The PLEN<3:0> bits are used to specify how long the polynomial used will be. For an  $x^n$  polynomial, PLEN = n-2. In an n-bit polynomial the  $x^n$  bit and the LSb will be used as a '1' in the CRC calculation because the MSb and LSb must always be a '1' for a CRC polynomial. For example, if using CRC-16-ANSI, the polynomial will look like 0x8005. This will be implemented into the CRCXOR<15:1> registers, as shown in Example 11-1.

## 21.10 Register Definitions: ZCD Control

#### REGISTER 21-1: ZCDCON: ZERO-CROSS DETECTION CONTROL REGISTER

| EN<br>bit 7      |                                                   | - · · ·                                                                                                                                                                                |                                 |                                                                   | U-0              | R/W-0/0                            | R/W-0/0     |  |  |

|------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------------------------------------------------------|------------------|------------------------------------|-------------|--|--|

| bit 7            |                                                   | OUT                                                                                                                                                                                    | POL                             |                                                                   |                  | INTP                               | INTN        |  |  |

|                  |                                                   |                                                                                                                                                                                        |                                 |                                                                   |                  |                                    | bit 0       |  |  |

|                  |                                                   |                                                                                                                                                                                        |                                 |                                                                   |                  |                                    |             |  |  |

| Legend:          |                                                   |                                                                                                                                                                                        |                                 |                                                                   |                  |                                    |             |  |  |

| R = Readable     | bit                                               | W = Writable                                                                                                                                                                           | bit                             | U = Unimplem                                                      | nented bit, read | d as '0'                           |             |  |  |

| u = Bit is uncha | anged                                             | x = Bit is unki                                                                                                                                                                        | nown                            | -n/n = Value a                                                    | t POR and BO     | R/Value at all o                   | ther Resets |  |  |

| '1' = Bit is set |                                                   | '0' = Bit is cle                                                                                                                                                                       | ared                            | q = value dep                                                     | ends on config   | uration bits                       |             |  |  |

| bit 7            |                                                   | s detect is en                                                                                                                                                                         | abled. ZCD pir                  |                                                                   |                  | and sink currer<br>and TRIS contro |             |  |  |

| bit 6            | Unimplement                                       | ted: Read as '                                                                                                                                                                         | 0'                              |                                                                   |                  |                                    |             |  |  |

| bit 5            | $\frac{\text{POL bit} = 0}{1 = \text{ZCD pin i}}$ |                                                                                                                                                                                        | rent<br>ent                     | t                                                                 |                  |                                    |             |  |  |

| bit 4            | POL: Zero-Cr<br>1 = ZCD logic<br>0 = ZCD logic    |                                                                                                                                                                                        | erted                           | Polarity bit                                                      |                  |                                    |             |  |  |

| bit 3-2          | Unimplement                                       | ted: Read as '                                                                                                                                                                         | 0'                              |                                                                   |                  |                                    |             |  |  |

| bit 1            | 1 = ZCDIF bit                                     | INTP: Zero-Cross Positive Edge Interrupt Enable bit<br>1 = ZCDIF bit is set on low-to-high ZCDx_output transition<br>0 = ZCDIF bit is unaffected by low-to-high ZCDx output transition |                                 |                                                                   |                  |                                    |             |  |  |

| bit 0            | 0 = ZCDIF bit                                     | t is set on high<br>t is unaffected                                                                                                                                                    | -to-low ZCDx_<br>by high-to-low | t Enable bit<br>_output transitic<br>/ ZCDx_output<br>CIATED WITI | transition       |                                    |             |  |  |

| Name    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on page |

|---------|-------|-------|-------|-------|--------|--------|--------|--------|---------------------|

| PIE3    |       | _     | RCIE  | TXIE  | BCL2IE | SSP2IE | BCL1IE | SSP1IE | 138                 |

| PIR3    | _     | _     | RCIF  | TXIF  | BCL2IF | SSP2IF | BCL1IF | SSP1IF | 147                 |

| ZCDxCON | EN    |       | OUT   | POL   | —      | —      | INTP   | INTN   | 319                 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the ZCD module.

#### TABLE 21-2: SUMMARY OF CONFIGURATION WORD WITH THE ZCD MODULE

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1    | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|------------|---------|---------------------|

| CONFIG2 | 13:8 | DEBUG   | STVREN  | PPS1WAY  | ZCDDIS   | BORV     | —        | BOREN<1:0> |         | 94                  |

|         | 7:0  | LPBOREN |         | _        |          | PWRTE    | MCLRE    | WRT        | <1:0>   |                     |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the ZCD module.

| <b>TABLE 23-3</b> : | COMPUTATION MODES |

|---------------------|-------------------|

|                     |                   |

|                   |      | Clear Canditiana                                      |                                                                                          |                                             | Three                                                                                                                                                                                  | hald Oneratio          |                        | Value                    |                          |       |  |

|-------------------|------|-------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------|--------------------------|--------------------------|-------|--|

|                   | -    | Clear Conditions                                      | value after Trig                                                                         | ger completion                              | Threshold Operations                                                                                                                                                                   |                        |                        | Value at ADTIF interrupt |                          |       |  |

| Mode              | ADMD | ADACC and ADCNT                                       | ADACC                                                                                    | ADCNT                                       | Retrigger                                                                                                                                                                              | Threshold<br>Test      | Interrupt              | ADAOV                    | ADFLTR                   | ADCNT |  |

| Basic             | 0    | ADACLR = 1                                            | Unchanged                                                                                | Unchanged                                   | No                                                                                                                                                                                     | Every<br>Sample        | If thresh-<br>old=true | N/A                      | N/A                      | count |  |

| Accumulate        | 1    | ADACLR = 1                                            | S + ADACC<br>or<br>(S2-S1) + ADACC                                                       | If (ADCNT=FF): ADCNT,<br>otherwise: ADCNT+1 | No                                                                                                                                                                                     | Every<br>Sample        | If thresh-<br>old=true | ADACC Overflow           | ADACC/2 <sup>ADCRS</sup> | count |  |

| Average           | 2    | ADACLR = 1 or<br>ADCNT>=ADRPT at ADGO<br>or retrigger | S + ADACC<br>or<br>(S2-S1) + ADACC                                                       | If (ADCNT>=ADRPT):1,<br>otherwise: ADCNT+1  | No                                                                                                                                                                                     | lf<br>ADCNT>=<br>ADRPT | If thresh-<br>old=true | ADACC Overflow           | ADACC/2 <sup>ADCRS</sup> | count |  |

| Burst<br>Average  | 3    | ADACLR = 1 or ADGO set or<br>retrigger                | Each repetition: same as<br>Average<br>End with sum of all<br>samples                    | Reset and count up until<br>ADCNT=ADRPT     | Repeat while<br>ADCNT <adrpt< td=""><td>lf<br/>ADCNT&gt;=<br/>ADRPT</td><td>If thresh-<br/>old=true</td><td>ADACC Overflow</td><td>ADACC/2<sup>ADCRS</sup></td><td>ADRPT</td></adrpt<> | lf<br>ADCNT>=<br>ADRPT | If thresh-<br>old=true | ADACC Overflow           | ADACC/2 <sup>ADCRS</sup> | ADRPT |  |

| Lowpass<br>Filter | 4    | ADACLR = 1                                            | S+ADACC-ADACC/<br>2 <sup>ADCRS</sup><br>or<br>(S2-S1)+ADACC-ADACC/<br>2 <sup>ADCRS</sup> | If (ADCNT=FF): ADCNT,<br>otherwise: ADCNT+1 | No                                                                                                                                                                                     | lf<br>ADCNT>=<br>ADRPT | If thresh-<br>old=true | ADACC Overflow           | Filtered Value           | count |  |

Note 1: S, S1, and S2 are abbreviations for ADRES, ADRES(n), and ADRES(n+1), respectively. When ADDSEN = 0: S = ADRES. When ADDSEN = 1: S1 = ADPREV, and S2 = ADRES.

2: All results of divisions using the ADCRS bits are truncated, not rounded.

## 25.6 Register Definitions: DAC Control

### REGISTER 25-1: DAC1CON0: VOLTAGE REFERENCE CONTROL REGISTER 0

| R/W-0/0          | U-0                                                 | R/W-0/0                                               | R/W-0/0        | R/W-0/0        | R/W-0/0          | U-0            | R/W-0/0      |

|------------------|-----------------------------------------------------|-------------------------------------------------------|----------------|----------------|------------------|----------------|--------------|

| DAC1EN           | _                                                   | DAC10E1                                               | DAC10E2        | DAC1F          | PSS<1:0>         | _              | DAC1NSS      |

| bit 7            |                                                     |                                                       |                |                |                  |                | bit 0        |

|                  |                                                     |                                                       |                |                |                  |                |              |

| Legend:          |                                                     |                                                       |                |                |                  |                |              |

| R = Readable     | bit                                                 | W = Writable                                          | bit            | U = Unimpler   | mented bit, read | as '0'         |              |

| u = Bit is unch  | anged                                               | x = Bit is unkr                                       | nown           | -n/n = Value a | at POR and BOF   | R/Value at all | other Resets |

| '1' = Bit is set |                                                     | '0' = Bit is clea                                     | ared           |                |                  |                |              |

| bit 7            | <b>DAC1EN:</b> DA<br>1 = DAC is er<br>0 = DAC is di |                                                       |                |                |                  |                |              |

| bit 6            | Unimplement                                         | ted: Read as '                                        | 0'             |                |                  |                |              |

| bit 5            | 1 = DAC volta                                       | AC1 Voltage C<br>age level is als<br>age level is dis | o an output or | the DAC1OU     |                  |                |              |

| bit 4            | 1 = DAC volta                                       | AC1 Voltage C<br>age level is als<br>age level is dis | o an output or | the DAC1OU     |                  |                |              |

| bit 3-2          |                                                     |                                                       | itive Source S | elect bits     |                  |                |              |

| bit 1            | Unimplement                                         | ted: Read as '                                        | 0'             |                |                  |                |              |

| bit 0            | <b>DAC1NSS:</b> D<br>1 = VREF- pin<br>0 = VSS       | AC1 Negative                                          | Source Selec   | t bits         |                  |                |              |

#### REGISTER 25-2: DAC1CON1: VOLTAGE REFERENCE CONTROL REGISTER 1

| U-0   | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0    | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|---------|------------|---------|---------|

| —     | —   | —   |         |         | DAC1R<4:0> |         |         |

| bit 7 |     |     |         |         |            |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-5 | Unimplemented: Read as '0'                    |

|---------|-----------------------------------------------|

| bit 4-0 | DAC1R<4:0>: DAC1 Voltage Output Select bits   |

|         | Vout = (Vsrc+ - Vsrc-)*(DAC1R<4:0>/32) + Vsrc |

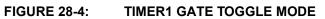

| TMRxGE                                                         |

|----------------------------------------------------------------|

| TxGPOL                                                         |

| TxGTM                                                          |

| selected                                                       |

|                                                                |

| TxGVAL                                                         |

| TMRxH: TMRxL N XN+1 XN+2 XN+3 N+4 XN+5 XN+6 XN+7 XN+8<br>Count |

### FIGURE 28-5: TIMER1 GATE SINGLE-PULSE MODE

| <b>REGISTER 3</b>                                                                                                                                                                                                                    | 0-6: CCPTI                                                                                                                                           | MRS1: CCP                                                                    | TIMERS COI                                     | NTROL 1 REG    | GISTER           |                |             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------|----------------|------------------|----------------|-------------|

| U-0                                                                                                                                                                                                                                  | U-0                                                                                                                                                  | R/W-0/0                                                                      | R/W-1/1                                        | R/W-0/0        | R/W-1/1          | R/W-0/0        | R/W-1/1     |

| —                                                                                                                                                                                                                                    | —                                                                                                                                                    | P7TSE                                                                        | L<1:0>                                         | P6TSE          | L<1:0>           | C5TSE          | EL<1:0>     |

| bit 7                                                                                                                                                                                                                                |                                                                                                                                                      |                                                                              |                                                |                |                  |                | bit 0       |

|                                                                                                                                                                                                                                      |                                                                                                                                                      |                                                                              |                                                |                |                  |                |             |

| Legend:                                                                                                                                                                                                                              |                                                                                                                                                      |                                                                              |                                                |                |                  |                |             |

| R = Readable                                                                                                                                                                                                                         | bit                                                                                                                                                  | W = Writable                                                                 | bit                                            | U = Unimplen   | nented bit, read | d as '0'       |             |

| u = Bit is unch                                                                                                                                                                                                                      | nanged                                                                                                                                               | x = Bit is unkr                                                              | nown                                           | -n/n = Value a | at POR and BO    | R/Value at all | other Reset |

| '1' = Bit is set                                                                                                                                                                                                                     |                                                                                                                                                      | '0' = Bit is cle                                                             | ared                                           |                |                  |                |             |

| bit 7-6<br>bit 5-4<br>bit 3-2                                                                                                                                                                                                        | P7TSEL<1:0><br>11 = PWM7 b<br>10 = PWM7 b<br>01 = PWM7 b<br>00 = Reserve<br>P6TSEL<1:0><br>11 = PWM6 b<br>01 = PWM6 b<br>01 = PWM6 b<br>00 = Reserve | >: PWM6 Time<br>based on TMR<br>based on TMR<br>based on TMR<br>based on TMR | r Selection<br>4<br>2<br>r Selection<br>4<br>2 |                |                  |                |             |

| bit 1-0<br>Diff 1-0<br>Diff 1-0<br>Diff 1= CCP5 based on TMR5 (Capture/Compare) or TMR6 (PWM)<br>10 = CCP5 based on TMR3 (Capture/Compare) or TMR4 (PWM)<br>01 = CCP5 based on TMR1 (Capture/Compare) or TMR2 (PWM)<br>00 = Reserved |                                                                                                                                                      |                                                                              |                                                |                |                  |                |             |

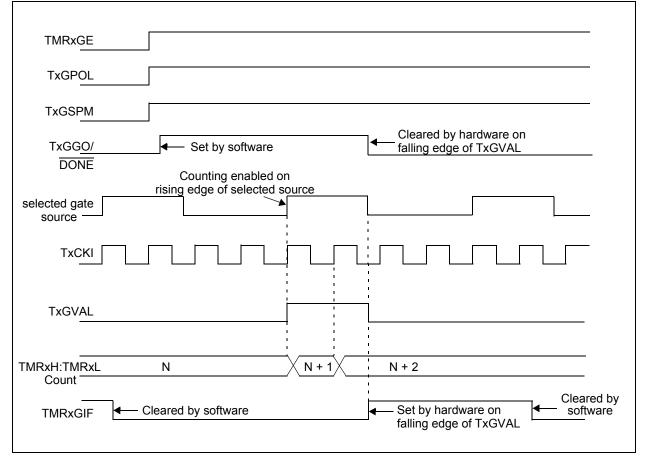

#### 31.2.1 SPI MODE REGISTERS

The MSSP module has five registers for SPI mode operation. These are:

- MSSP STATUS register (SSPxSTAT)

- MSSP Control register 1 (SSPxCON1)

- MSSP Control register 3 (SSPxCON3)

- MSSP Data Buffer register (SSPxBUF)

- MSSP Address register (SSPxADD)

- MSSP Shift register (SSPxSR) (Not directly accessible)

SSPxCON1 and SSPxSTAT are the control and status registers in SPI mode operation. The SSPxCON1 register is readable and writable. The lower six bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

In one SPI master mode, SSPxADD can be loaded with a value used in the Baud Rate Generator. More information on the Baud Rate Generator is available in **Section 31.7 "Baud Rate Generator"**.

SSPxSR is the shift register used for shifting data in and out. SSPxBUF provides indirect access to the SSPxSR register. SSPxBUF is the buffer register to which data bytes are written, and from which data bytes are read.

In receive operations, SSPxSR and SSPxBUF together create a buffered receiver. When SSPxSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not buffered. A write to SSPxBUF will write to both SSPxBUF and SSPxSR.

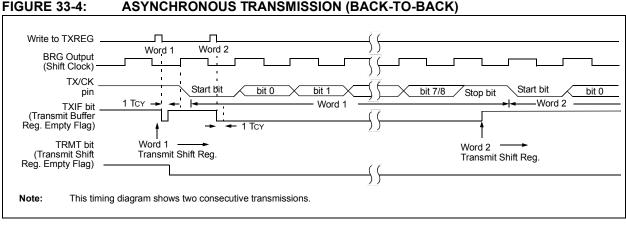

## 33.1.2 EUSART ASYNCHRONOUS

RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 33-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCREG register.

#### 33.1.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RC1STA register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TX1STA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RC1STA register enables the EUSART. The programmer must set the corresponding TRIS bit to configure the RX/DT I/O pin as an input.

If the RX/DT function is on an analog pin, Note: the corresponding ANSEL bit must be cleared for the receiver to function.

#### 33.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 33.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RCIF interrupt flag bit of the PIR3 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCREG register.

If the receive FIFO is overrun, no additional Note: characters will be received until the overrun condition is cleared. See Section 33.1.2.5 "Receive Overrun Error" for more information on overrun errors.

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

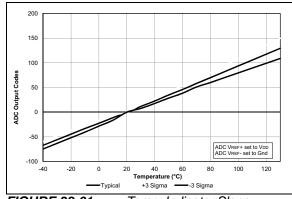

FIGURE 38-61: Temp. Indicator Slope Normalized to 20°C, Low Range, VDD = 2.3V.

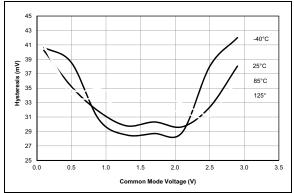

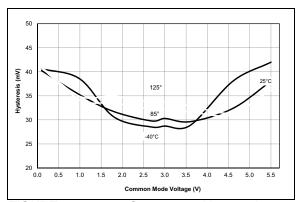

**FIGURE 38-62:** Comparator Hysteresis, NP Mode (CxSP = 1), VDD = 3.0V, Typical Measured Values.

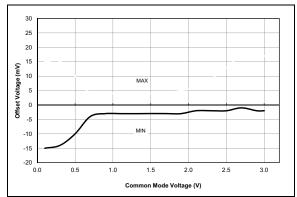

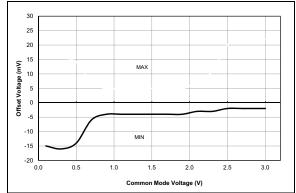

**FIGURE 38-63:** Comparator Offset, NP Mode (CxSP = 1), VDD = 3.0V, Typical Measured Values at  $25^{\circ}$ C.

**FIGURE 38-64:** Comparator Offset, NP Mode (CxSP = 1), VDD = 3.0V, Typical Measured Values from -40°C to 125°C.

**FIGURE 38-65:** Comparator Hysteresis, NP Mode (CxSP = 1), VDD = 5.5V, Typical Measured Values, PIC16F18855/75 Only.

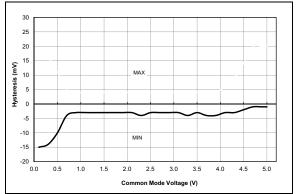

**FIGURE 38-66:** Comparator Offset, NP Mode (CxSP = 1), VDD = 5.0V, Typical Measured Values at 25°C, PIC16F18855/75 Only.

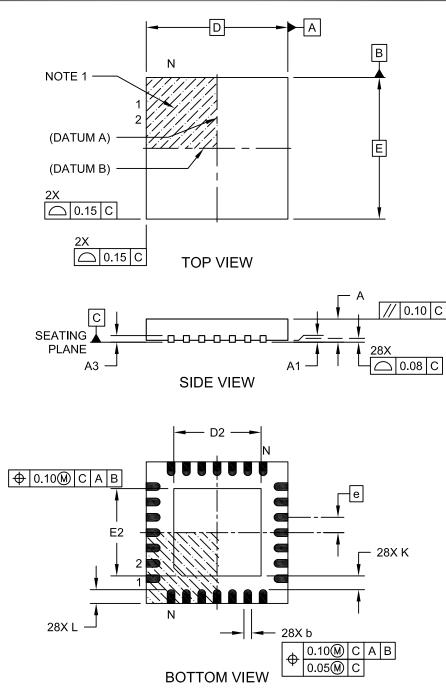

### 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

Microchip Technology Drawing C04-105C Sheet 1 of 2