Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 25                                                                           |

| Program Memory Size        | 14KB (8K x 14)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18855t-i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| RA0         2         17         19         19         ANA0         -         -         Clino-<br>C2INO-<br>C2INO-         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         Clino-         -         IOCA0         -         IOCA0         -         IOCA0         -         IOCA0         -         -         IOCA0         IOCA0         IOCA0         IOCA0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | O/i | 40-Pin PDIP | 40-Pin UQFN | 44-Pin QFN | 44-Pin TQFP | ADC                           | Voltage Reference | DAC      | Comparators | Zero-Cross Detect | MSSP (SPI/I <sup>2</sup> C)                  | EUSART | WSQ                   | Timers/SMT                                   | CCP and PWM         | CWG                   | CLC                   | NCO | Clock Reference (CLKR) | Interrupt-on-Change | Basic          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|-------------|------------|-------------|-------------------------------|-------------------|----------|-------------|-------------------|----------------------------------------------|--------|-----------------------|----------------------------------------------|---------------------|-----------------------|-----------------------|-----|------------------------|---------------------|----------------|

| Image: Region of the state of the  | RA0 | 2           | 17          | 19         | 19          | ANA0                          |                   | _        |             | —                 | _                                            |        | —                     | -                                            | _                   | —                     |                       | —   |                        | IOCA0               | _              |

| Image: Section of the secting definition of the section of | RA1 | 3           | 18          | 20         | 20          | ANA1                          |                   | —        |             |                   | _                                            |        | —                     | _                                            | _                   | —                     | CLCIN1 <sup>(1)</sup> | —   |                        | IOCA1               | _              |

| RA4       6       21       23       ANA4       -       -       -       -       -       MDCARH <sup>(1)</sup> TOCKI <sup>(1)</sup> CCP5 <sup>(1)</sup> -       -       -       IOCA4       -         RA5       7       22       24       24       ANA5       -       -       -       -       SS1 <sup>(1)</sup> -       MDSRC <sup>(1)</sup> -       -       -       -       -       IOCA4       -         RA6       14       29       33       31       ANA6       -       -       -       -       -       MDSRC <sup>(1)</sup> -       -       -       -       -       IOCA6       OCCA5       CLKOUT         RA7       13       28       32       30       ANA7       -       -       -       -       -       -       -       -       -       -       IOCA7       OSC1         RB0       33       8       9       8       ANB0       -       I       CliN1+       ZCD       SS2 <sup>(1)</sup> -       -       -       CPC4 <sup>(1)</sup> CWG1IN <sup>(1)</sup> -       -       INT <sup>(1)</sup> ICLKN         RB1       34       9       10       9       ANB1       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RA2 | 4           | 19          | 21         | 21          | ANA2                          | VREF-             | DAC1OUT1 |             |                   |                                              |        |                       | _                                            | -                   | —                     | —                     |     |                        | IOCA2               | _              |

| RA5       7       22       24       ANA5       -       -       -       -       SS1 <sup>(1)</sup> -       MDSRC <sup>(1)</sup> -       -       -       -       0CA5       -         RA6       14       29       33       31       ANA6       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RA3 | 5           | 20          | 22         | 22          | ANA3                          | VREF+             | -        | C1IN1+      | —                 | -                                            | —      | MDCARL <sup>(1)</sup> |                                              | _                   | —                     | _                     | —   | _                      | IOCA3               | —              |

| RA6       14       29       33       31       ANA6       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RA4 | 6           | 21          | 23         | 23          | ANA4                          | —                 | -        | _           | -                 |                                              | -      | MDCARH <sup>(1)</sup> | T0CKI <sup>(1)</sup>                         | CCP5 <sup>(1)</sup> | —                     | _                     | —   | —                      | IOCA4               | —              |

| RA7         13         28         32         30         ANA7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RA5 | 7           | 22          | 24         | 24          | ANA5                          | —                 | -        | _           | -                 | SS1 <sup>(1)</sup>                           | _      | MDSRC <sup>(1)</sup>  | _                                            | -                   | —                     | _                     | _   | _                      | IOCA5               | —              |

| RB0         33         8         9         8         ANB0         -         C2IN1+         ZCD         SS2(1)         -         -         CCP4(1)         CWG1IN(1)         -         -         INT(1)         ICCB0         -         ICLKIN           RB1         34         9         10         9         ANB1         -         C1IN3-<br>C2IN3-         -         SCL2(3.4)<br>SCK2(1)         -         -         -         CWG3IN(1)         -         -         -         ICLKIN           RB2         35         10         11         10         ANB2         -         C1IN3-<br>C2IN3-         -         SCL2(3.4)<br>SCL2(3.4)         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RA6 | 14          | 29          | 33         | 31          | ANA6                          |                   | —        |             |                   | —                                            |        | -                     |                                              |                     | —                     | —                     | _   |                        | IOCA6               | OSC2<br>CLKOUT |

| RB1       34       9       10       9       ANB1        C1IN3-<br>C2IN3-        SCL2 <sup>(3,4)</sup><br>SCK2 <sup>(1)</sup> CWG2IN <sup>(1)</sup> IOCB0         RB2       35       10       11       10       ANB2        C1IN3-<br>C2IN3-        SCL2 <sup>(3,4)</sup><br>SCK2 <sup>(1)</sup> CWG2IN <sup>(1)</sup> IOCB0          RB2       35       10       11       10       ANB2                  CWG3IN <sup>(1)</sup> IOCB0          RB3       36       11       12       11       ANB3               IOCB1        IOCB2          RB4       37       12       14       14       ANB4<br>ADCACT <sup>(1)</sup> TG6 <sup>(1)</sup><br>SMTSIG2 <sup>(1)</sup> IOCB3          RB5       38       13       15       16       ANB6 </td <td>RA7</td> <td>13</td> <td>28</td> <td>32</td> <td>30</td> <td>ANA7</td> <td>-</td> <td>—</td> <td>_</td> <td>_</td> <td></td> <td> </td> <td>—</td> <td>_</td> <td></td> <td></td> <td>—</td> <td>—</td> <td> </td> <td></td> <td>OSC1<br/>CLKIN</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | RA7 | 13          | 28          | 32         | 30          | ANA7                          | -                 | —        | _           | _                 |                                              |        | —                     | _                                            |                     |                       | —                     | —   |                        |                     | OSC1<br>CLKIN  |

| Image: Normal Section       Image: Normal Sec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RB0 | 33          | 8           | 9          | 8           | ANB0                          |                   | —        | C2IN1+      | ZCD               |                                              |        | —                     | _                                            | CCP4 <sup>(1)</sup> |                       | —                     | —   |                        |                     | —              |

| RB3         36         11         12         11         ANB3          C1IN2-<br>C2IN2-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RB1 | 34          | 9           | 10         | 9           | ANB1                          | l                 | _        |             |                   | SCL2 <sup>(3,4)</sup><br>SCK2 <sup>(1)</sup> | l      | _                     |                                              |                     |                       | —                     | _   |                        | IOCB1               | _              |

| Image: Note of the state o         | RB2 | 35          | 10          | 11         | 10          | ANB2                          |                   | _        |             |                   | SDA2 <sup>(3,4)</sup><br>SDI2 <sup>(1)</sup> | l      | _                     |                                              |                     | CWG3IN <sup>(1)</sup> | —                     | _   |                        | IOCB2               | _              |

| Image: Non-Structure       ADCACT <sup>(1)</sup> Image: Non-Structure       ADCACT <sup>(1)</sup> Image: Non-Structure       Image: Non-Struct                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RB3 | 36          | 11          | 12         | 11          | ANB3                          |                   | Ι        |             |                   | Ι                                            |        | _                     | _                                            | -                   | —                     | —                     |     |                        | IOCB3               | —              |

| RB6       39       14       16       16       ANB6       -       -       -       -       -       -       -       -       ICCB6       ICSPCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RB4 | 37          | 12          | 14         | 14          | ANB4<br>ADCACT <sup>(1)</sup> | _                 | —        | —           | _                 | —                                            | —      | -                     | T5G <sup>(1)</sup><br>SMTWIN2 <sup>(1)</sup> | _                   | —                     | —                     | —   | _                      | IOCB4               | —              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RB5 | 38          | 13          | 15         | 15          | ANB5                          | 1                 | —        | _           | _                 | —                                            | -      | —                     | T1G <sup>(1)</sup><br>SMTSIG2 <sup>(1)</sup> | CCP3(1)             | —                     | —                     | —   | 1                      | IOCB5               | _              |

| RB7       40       15       17       17       ANB7       —       DAC10UT2       —       —       —       T6IN <sup>(1)</sup> —       —       CLCIN3 <sup>(1)</sup> —       —       IOCB7       ICSPDAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RB6 | 39          | 14          | 16         | 16          | ANB6                          | —                 | —        | —           | _                 | —                                            | —      | —                     | —                                            | —                   | —                     |                       |     | —                      | IOCB6               | ICSPCLK        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RB7 | 40          | 15          | 17         | 17          | ANB7                          | -                 | DAC10UT2 | -           | —                 | —                                            | _      | —                     | T6IN <sup>(1)</sup>                          | —                   | —                     | CLCIN3 <sup>(1)</sup> | —   | -                      | IOCB7               | ICSPDAT        |

TABLE 3: 40/44-PIN ALLOCATION TABLE (PIC16F18875)

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 13-1 for details on which port pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 13-3.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels.; The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMbus input buffer thresholds.

# TABLE 3-11: PIC16(L)F18875 MEMORY MAP, BANK 30

| TADLE J-II. |         |      | , <b>DANK 30</b> |      |

|-------------|---------|------|------------------|------|

|             | Bank 30 |      | Bank 30          |      |

| F0Ch        | —       | F40h | CCDNA            | F64h |

| F0Dh        | _       | F41h | CCDPA            | F65h |

| F0Eh        | —       | F42h | _                | F66h |

| F0Fh        | —       | F43h | ANSELB           | F67h |

| F10h        | RA0PPS  | F44h | WPUB             | F68h |

| F11h        | RA1PPS  | F45h | ODCONB           | F69h |

| F12h        | RA2PPS  | F46h | SLRCONB          | F6Ah |

| F13h        | RA3PPS  | F47h | INLVLB           | F6Bh |

| F14h        | RA4PPS  | F48h | IOCBP            | F6Ch |

| F15h        | RA5PPS  | F49h | IOCBN            | F6Dh |

| F16h        | RA6PPS  | F4Ah | IOCBF            | F6Eh |

| F17h        | RA7PPS  | F4Bh | CCDNB            | F6Fh |

| F18h        | RB0PPS  | F4Ch | CCDPB            |      |

| F19h        | RB1PPS  | F4Dh | _                |      |

| F1Ah        | RB2PPS  | F4Eh | ANSELC           |      |

| F1Bh        | RB3PPS  | F4Fh | WPUC             |      |

| F1Ch        | RB4PPS  | F50h | ODCONC           |      |

| F1Dh        | RB5PPS  | F51h | SLRCONC          |      |

| F1Eh        | RB6PPS  | F52h | INLVLC           |      |

| F1Fh        | RB7PPS  | F53h | IOCCP            |      |

| F20h        | RC0PPS  | F54h | IOCCN            |      |

| F21h        | RC1PPS  | F55h | IOCCF            |      |

| F22h        | RC2PPS  | F56h | CCDNC            |      |

| F23h        | RC3PPS  | F57h | CCDPC            |      |

| F24h        | RC4PPS  | F58h | —                |      |

| F25h        | RC5PPS  | F59h | ANSELD           |      |

| F26h        | RC6PPS  | F5Ah | WPUD             |      |

| F27h        | RC7PPS  | F5Bh | ODCOND           |      |

| F28h        |         | F5Ch | SLRCOND          |      |

|             | —       | F5Dh | INLVLD           |      |

| F37h        |         | F5Eh | —                |      |

| F38h        | ANSELA  | F5Fh | _                |      |

| F39h        | WPUA    | F60h |                  |      |

| F3Ah        | ODCONA  | F61h | CCDND            |      |

| F3Bh        | SLRCONA | F62h | CCDPD            |      |

| F3Ch        | INLVLA  | F63h | _                |      |

| F3Dh        | IOCAP   |      |                  |      |

| F3Eh        | IOCAN   |      |                  |      |

| F3Fh        | IOCAF   |      |                  |      |

|             |         |      |                  |      |

| F64h | ANSELE  |

|------|---------|

| F65h | WPUE    |

| F66h | ODCONE  |

| F67h | SLRCONE |

| -68h | INLVLE  |

| F69h | IOCEP   |

| -6Ah | IOCEN   |

| -6Bh | IOCEF   |

| -6Ch | CCDNE   |

| -6Dh | CCDPE   |

| -6Eh | _       |

| -6Fh | —       |

|      |         |

Bank 30

Legend:

= Unimplemented data memory locations, read as '0'.

| Address         | Name        | PIC16(L)F18855<br>PIC16(L)F18875 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3         | Bit 2           | Bit 1  | Bit 0 | Value on:<br>POR, BOR | Value on all<br>other Resets |

|-----------------|-------------|----------------------------------|-------|-------|-------|-------|---------------|-----------------|--------|-------|-----------------------|------------------------------|

| Bank 29         | (Continued) |                                  |       |       |       |       |               |                 |        |       |                       |                              |

| EBAh            | MDSRCPPS    |                                  | —     | _     | _     |       |               | MDSRCPPS<4:0>   |        |       | 0 0101                | u uuuu                       |

| EBBh            | CLCIN0PPS   |                                  | _     | —     | —     |       |               | 0 0000          | u uuuu |       |                       |                              |

| EBCh            | CLCIN1PPS   |                                  | _     | —     | —     |       |               | 0 0001          | u uuuu |       |                       |                              |

| EBDh            | CLCIN2PPS   |                                  | _     | _     | —     |       |               | 0 1110          | u uuuu |       |                       |                              |

| EBEh            | CLCIN3PPS   |                                  | _     | —     | —     |       |               | CLCIN3PPS<4:0>  |        |       | 0 1111                | u uuuu                       |

| EBFh            | —           | —                                |       |       | •     | U     | Inimplemented |                 |        |       | —                     | _                            |

| EC0h            | —           | —                                |       |       |       | U     | Unimplemented |                 |        |       |                       | _                            |

| EC1h            | —           | —                                |       |       |       | U     | Inimplemented |                 |        |       | -                     | -                            |

| EC2h            | —           | —                                |       |       |       | U     | Inimplemented |                 |        |       | -                     | -                            |

| EC3h            | ADCACTPPS   |                                  | _     | —     | —     |       |               | ADCACTPPS<4:0>  |        |       | 0 1100                | u uuuu                       |

| EC4h            | —           | _                                |       |       |       | U     | Inimplemented |                 |        |       | -                     | -                            |

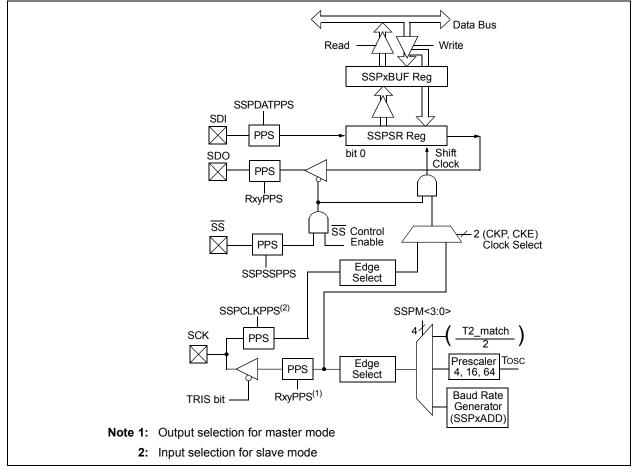

| EC5h            | SSP1CLKPPS  |                                  | _     | —     | —     |       |               | SSP1CLKPPS<4:0> |        |       | 1 0011                | u uuuu                       |

| EC6h            | SSP1DATPPS  |                                  | _     | —     | —     |       |               | SSP1DATPPS<4:0> |        |       | 1 0100                | u uuuu                       |

| EC7h            | SSP1SSPPS   |                                  | _     | —     | —     |       |               | SSP1SSPPS<4:0>  |        |       | 0 0101                | u uuuu                       |

| EC8h            | SSP2CLKPPS  |                                  | _     | —     | —     |       |               | SSP2CLKPPS<4:0> |        |       | 0 1001                | u uuuu                       |

| EC9h            | SSP2DATPPS  |                                  | _     | —     | —     |       |               | SSP2DATPPS<4:0> |        |       | 0 0010                | u uuuu                       |

| ECAh            | SSP2SSPPS   |                                  | _     | —     | —     |       |               | SSP2SSPPS<4:0>  |        |       | 0 1000                | u uuuu                       |

| ECBh            | RXPPS       |                                  | _     | —     | —     |       |               | RXPPS<4:0>      |        |       | 1 0111                | u uuuu                       |

| ECCh            | TXPPS       |                                  | _     | —     | —     |       |               | TXPPS<4:0>      |        |       | 1 0110                | u uuuu                       |

| ECDh to<br>EEFh | —           | —                                |       |       |       | U     | Inimplemented |                 |        |       | —                     | —                            |

#### TABLE 3-13: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED)

Legend: x = unknown, u = unchanged, q =depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

**Note 1:** Register present on PIC16F18855/75 devices only.

2: Unimplemented, read as '1'.

| Address      | Name        | PIC16(L)F18855 | PIC16(L)F18875 | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3        | Bit 2   | Bit 1   | Bit 0   | Value on:<br>POR, BOR | Value on all other Resets |

|--------------|-------------|----------------|----------------|---------|---------|---------|---------|--------------|---------|---------|---------|-----------------------|---------------------------|

| Bank 30      | (Continued) |                |                |         |         |         |         |              |         |         |         |                       |                           |

| F47h         | INLVLB      |                |                | INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | INLVLB3      | INLVLB2 | INLVLB1 | INLVLB0 | 1111 1111             | 1111 1111                 |

| F48h         | IOCBP       |                |                | IOCBP7  | IOCBP6  | IOCBP5  | IOCBP4  | IOCBP3       | IOCBP2  | IOCBP1  | IOCBP0  | 0000 0000             | 0000 0000                 |

| F49h         | IOCBN       |                |                | IOCBN7  | IOCBN6  | IOCBN5  | IOCBN4  | IOCBN3       | IOCBN2  | IOCBN1  | IOCBN0  | 0000 0000             | 0000 0000                 |

| F4Ah         | IOCBF       |                |                | IOCBF7  | IOCBF6  | IOCBF5  | IOCBF4  | IOCBF3       | IOCBF2  | IOCBF1  | IOCBF0  | 0000 0000             | 0000 0000                 |

| F4Bh         | CCDNB       |                |                | CCDNB7  | CCDNB6  | CCDNB5  | CCDNB4  | CCDNB3       | CCDNB2  | CCDNB1  | CCDNB0  | 0000 0000             | 0000 0000                 |

| F4Ch         | CCDPB       |                |                | CCDPB7  | CCDPB6  | CCDPB5  | CCDPB4  | CCDPB3       | CCDPB2  | CCDPB1  | CCDPB0  | 0000 0000             | 0000 0000                 |

| F4Dh         | —           | -              | -              |         |         |         | U       | nimplemented |         |         |         | —                     | _                         |

| F4Eh         | ANSELC      |                |                | ANSC7   | ANSC6   | ANSC5   | ANSC4   | ANSC3        | ANSC2   | ANSC1   | ANSC0   | 1111 1111             | 1111 1111                 |

| F4Fh         | WPUC        |                |                | WPUC7   | WPUC6   | WPUC5   | WPUC4   | WPUC3        | WPUC2   | WPUC1   | WPUC0   | 0000 0000             | 0000 0000                 |

| F50h         | ODCONC      |                |                | ODCC7   | ODCC6   | ODCC5   | ODCC4   | ODCC3        | ODCC2   | ODCC1   | ODCC0   | 0000 0000             | 0000 0000                 |

| F51h         | SLRCONC     |                |                | SLRC7   | SLRC6   | SLRC5   | SLRC4   | SLRC3        | SLRC2   | SLRC1   | SLRC0   | 1111 1111             | 1111 1111                 |

| F52h         | INLVLC      |                |                | INLVLC7 | INLVLC6 | INLVLC5 | INLVLC4 | INLVLC3      | INLVLC2 | INLVLC1 | INLVLC0 | 1111 1111             | 1111 1111                 |

| F53h         | IOCCP       |                |                | IOCCP7  | IOCCP6  | IOCCP5  | IOCCP4  | IOCCP3       | IOCCP2  | IOCCP1  | IOCCP0  | 0000 0000             | 0000 0000                 |

| F54h         | IOCCN       |                |                | IOCCN7  | IOCCN6  | IOCCN5  | IOCCN4  | IOCCN3       | IOCCN2  | IOCCN1  | IOCCN0  | 0000 0000             | 0000 0000                 |

| F55h         | IOCCF       |                |                | IOCCF7  | IOCCF6  | IOCCF5  | IOCCF4  | IOCCF3       | IOCCF2  | IOCCF1  | IOCCF0  | 0000 0000             | 0000 0000                 |

| F56h         | CCDNC       |                |                | CCDNC7  | CCDNC6  | CCDNC5  | CCDNC4  | CCDNC3       | CCDNC2  | CCDNC1  | CCDNC0  | 0000 0000             | 0000 0000                 |

| F57h         | CCDPC       |                |                | CCDPC7  | CCDPC6  | CCDPC5  | CCDPC4  | CCDPC3       | CCDPC2  | CCDPC1  | CCDPC0  | 0000 0000             | 0000 0000                 |

| F58h         | —           | -              | -              |         | 1       |         | U       | nimplemented |         |         |         | —                     | —                         |

| F59h         | ANSELD      | —              | Х              | ANSD7   | ANSD6   | ANSD5   | ANSD4   | ANSD3        | ANSD2   | ANSD1   | ANSD0   | 1111 1111             | 1111 1111                 |

| F3911        | ANGELD      | Х              | —              |         |         |         | U       | nimplemented |         |         |         |                       |                           |

| <b>FEA</b> b |             | —              | х              | WPUD7   | WPUD6   | WPUD5   | WPUD4   | WPUD3        | WPUD2   | WPUD1   | WPUD0   | 0000 0000             | 0000 0000                 |

| F5Ah         | WPUD        | Х              | —              |         |         |         | U       | nimplemented |         |         |         |                       |                           |

| FEDh         |             | —              | Х              | ODCD7   | ODCD6   | ODCD5   | ODCD4   | ODCD3        | ODCD2   | ODCD1   | ODCD0   | 0000 0000             | 0000 0000                 |

| F5Bh         | ODCOND      | Х              | —              |         |         |         | U       | nimplemented |         |         |         |                       |                           |

### TABLE 3-13: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED)

x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Register present on PIC16F18855/75 devices only. Legend:

Note 1:

2: Unimplemented, read as '1'.

# 6.0 OSCILLATOR MODULE (WITH FAIL-SAFE CLOCK MONITOR)

# 6.1 Overview

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 6-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from external oscillators, quartz-crystal resonators and ceramic resonators. In addition, the system clock source can be supplied from one of two internal oscillators and PLL circuits, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software.

- Fail-Safe Clock Monitor (FSCM) designed to detect a failure of the external clock source (LP, XT, HS, ECH, ECM, ECL) and switch automatically to the internal oscillator.

- Oscillator Start-up Timer (OST) ensures stability of crystal oscillator sources.

The RSTOSC bits of Configuration Word 1 determine the type of oscillator that will be used when the device reset, including when it is first powered up.

The internal clock modes, LFINTOSC, HFINTOSC (set at 1 MHz), or HFINTOSC (set at 32 MHz) can be set through the RSTOSC bits.

If an external clock source is selected, the FEXTOSC bits of Configuration Word 1 must be used in conjunction with the RSTOSC bits to select the external clock mode.

The external oscillator module can be configured in one of the following clock modes, by setting the FEXTOSC<2:0> bits of Configuration Word 1:

- 1. ECL External Clock Low-Power mode (below 500 kHz)

- 2. ECM External Clock Medium Power mode (500 kHz to 8 MHz)

- 3. ECH External Clock High-Power mode (above 8 MHz)

- 4. LP 32 kHz Low-Power Crystal mode.

- 5. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode (between 100 kHz and 4 MHz)

- 6. HS High Gain Crystal or Ceramic Resonator mode (above 4 MHz)

The ECH, ECM, and ECL clock modes rely on an external logic level signal as the device clock source. The LP, XT, and HS clock modes require an external crystal or resonator to be connected to the device. Each mode is optimized for a different frequency range. The INTOSC internal oscillator block produces low and high-frequency clock sources, designated LFINTOSC and HFINTOSC. (see Internal Oscillator Block, Figure 6-1). A wide selection of device clock frequencies may be derived from these clock sources.

### 6.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (ECH, ECM, ECL mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes).

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators and a dedicated Phase Lock Loop (PLL) that are used to generate internal system clock sources. The High-Frequency Internal Oscillator (HFINTOSC) can produce a range from 1 to 32 MHz. The Low-Frequency Internal Oscillator (LFINTOSC) generates a 31 kHz frequency. The external oscillator block can also be used with the PLL. See **Section 6.2.1.4 "4x PLL"** for more details.

The system clock can be selected between external or internal clock sources via the NOSC bits in the OSCCON1 register. See **Section 6.3** "Clock **Switching**" for additional information.

#### 6.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the RSTOSC<2:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset

- Write the NOSC<2:0> and NDIV<4:0> bits in the OSCCON1 register to switch the system clock source

See **Section 6.3 "Clock Switching**" for more information.

#### 6.2.1.1 EC Mode

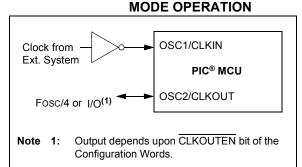

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 6-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through Configuration Words:

- ECH High power, 4-32 MHz

- ECM Medium power, 0.1-4 MHz

- ECL Low power, 0-0.1 MHz

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### 6.2.1.2 LP, XT, HS Modes

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 6-3). The three modes select a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 6-3 and Figure 6-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

# 6.4 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM is enabled by setting the FCMEN bit in the Configuration Words. The FSCM is applicable to all external Oscillator modes (LP, XT, HS, EC and Secondary Oscillator).

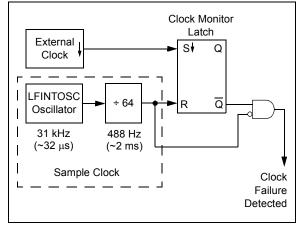

FIGURE 6-9: FSCM BLOCK DIAGRAM

### 6.4.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 6-9. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the external clock goes low.

#### 6.4.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to the HFINTOSC at 1 MHz clock frequency and sets the bit flag OSFIF of the PIR1 register. Setting this flag will generate an interrupt if the OSFIE bit of the PIE1 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation, by writing to the NOSC and NDIV bits of the OSCCON1 register.

#### 6.4.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or changing the NOSC and NDIV bits of the OSCCON1 register. When switching to the external oscillator or PLL, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON1. When the OST times out, the Fail-Safe condition is cleared after successfully switching to the external clock source. The OSFIF bit should be cleared prior to switching to the external clock source. If the Fail-Safe condition still exists, the OSFIF flag will again become set by hardware.

| REGISTE<br>R/W-0/0 | -                   | R/W-0/0                             | R/W-0/0      | U-0                                | R/W-0/0          | R/W-0/0          | R/W-0/0     |  |  |  |

|--------------------|---------------------|-------------------------------------|--------------|------------------------------------|------------------|------------------|-------------|--|--|--|

| SCANIE             |                     | NVMIE                               | NCO1IE       | 0-0                                | CWG3IE           | CWG2IE           | CWG1IE      |  |  |  |

| bit 7              |                     |                                     | NCOTE        |                                    | CWG3IE           | CWGZIE           | bit C       |  |  |  |

|                    |                     |                                     |              |                                    |                  |                  |             |  |  |  |

| Legend:            |                     |                                     |              |                                    |                  |                  |             |  |  |  |

| R = Reada          | able bit            | W = Writable                        | bit          | U = Unimplemented bit, read as '0' |                  |                  |             |  |  |  |

| u = Bit is u       | inchanged           | x = Bit is unk                      | nown         | -n/n = Value                       | at POR and BO    | R/Value at all o | ther Resets |  |  |  |

| '1' = Bit is       | set                 | '0' = Bit is cle                    | ared         | HS = Hardwa                        | are set          |                  |             |  |  |  |

| bit 7              | SCANIE: Sca         | anner Interrupt                     | Enable bit   |                                    |                  |                  |             |  |  |  |

|                    |                     | ,<br>the scanner ir                 |              |                                    |                  |                  |             |  |  |  |

|                    | 0 = Disable         | s the scanner i                     | nterrupt     |                                    |                  |                  |             |  |  |  |

| bit 6              |                     | Interrupt Enab                      |              |                                    |                  |                  |             |  |  |  |

|                    |                     | the CRC inter                       |              |                                    |                  |                  |             |  |  |  |

|                    |                     | s the CRC inte                      | •            |                                    |                  |                  |             |  |  |  |

| bit 5              |                     | Interrupt Enat                      |              | -1                                 |                  |                  |             |  |  |  |

|                    |                     | sk complete int<br>errupt not enal  |              | a                                  |                  |                  |             |  |  |  |

| bit 4              | NCO1IE: NC          | O Interrupt Ena                     | able bit     |                                    |                  |                  |             |  |  |  |

|                    |                     | llover interrupt                    |              |                                    |                  |                  |             |  |  |  |

|                    |                     | llover interrupt                    |              |                                    |                  |                  |             |  |  |  |

| bit 3              | •                   | ted: Read as '                      |              |                                    |                  |                  |             |  |  |  |

| bit 2              |                     |                                     |              | nerator (CWG)                      | 3 Interrupt Enat | ole bit          |             |  |  |  |

|                    |                     | nterrupt enable<br>nterrupt disable |              |                                    |                  |                  |             |  |  |  |

| bit 1              |                     | -                                   |              | erator (CMG)                       | 2 Interrupt Enat | ale hit          |             |  |  |  |

|                    |                     | nterrupt is ena                     |              |                                    |                  |                  |             |  |  |  |

|                    |                     | nterrupt disable                    |              |                                    |                  |                  |             |  |  |  |

| bit 0              | CWG1IE: Co          | mplementary V                       | Vaveform Ger | nerator (CWG)                      | 2 Interrupt Enat | ole bit          |             |  |  |  |

|                    |                     | nterrupt is ena                     |              |                                    | -                |                  |             |  |  |  |

|                    | 0 = CWG1 i          | nterrupt disable                    | ed           |                                    |                  |                  |             |  |  |  |

| Note:              | Bit PEIE of the IN  | TCON register                       | must be      |                                    |                  |                  |             |  |  |  |

|                    | set to enable a     | ny peripheral                       | interrupt    |                                    |                  |                  |             |  |  |  |

|                    | controlled by regis | ters PIE1-PIE8                      | 3.           |                                    |                  |                  |             |  |  |  |

# **REGISTER 7-9: PIE7: PERIPHERAL INTERRUPT ENABLE REGISTER 7**

| U-0                     | U-0                                                                          | U-0                                                                                                                                                                                                              | R/W/HS-0/0                                                  | R/W/HS-0/0                                                                                                                                                      | R/W/HS-0/                                                                                                                                | 0 R/W/HS-0/0                                                                                                                                                                                          | R/W/HS-0/                                                                                    |  |  |

|-------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|

| _                       | —                                                                            | —                                                                                                                                                                                                                | CCP5IF                                                      | CCP4IF                                                                                                                                                          | CCP3IF                                                                                                                                   | CCP2IF                                                                                                                                                                                                | CCP1IF                                                                                       |  |  |

| oit 7                   |                                                                              |                                                                                                                                                                                                                  |                                                             |                                                                                                                                                                 |                                                                                                                                          |                                                                                                                                                                                                       | b                                                                                            |  |  |

| .egend:                 |                                                                              |                                                                                                                                                                                                                  |                                                             |                                                                                                                                                                 |                                                                                                                                          |                                                                                                                                                                                                       |                                                                                              |  |  |

| R = Readable            | bit                                                                          | W = Writable bi                                                                                                                                                                                                  | ł                                                           | U = Unimpleme                                                                                                                                                   | ented bit read                                                                                                                           | l as '0'                                                                                                                                                                                              |                                                                                              |  |  |

| u = Bit is unch         |                                                                              | x = Bit is unkno                                                                                                                                                                                                 |                                                             | •                                                                                                                                                               |                                                                                                                                          | R/Value at all othe                                                                                                                                                                                   | er Resets                                                                                    |  |  |

| 1' = Bit is set         | 0                                                                            | '0' = Bit is clear                                                                                                                                                                                               |                                                             | HS = Hardware                                                                                                                                                   |                                                                                                                                          |                                                                                                                                                                                                       |                                                                                              |  |  |

|                         |                                                                              |                                                                                                                                                                                                                  |                                                             |                                                                                                                                                                 |                                                                                                                                          |                                                                                                                                                                                                       |                                                                                              |  |  |

| bit 7-5                 | Unimpleme                                                                    | nted: Read as '0'                                                                                                                                                                                                |                                                             |                                                                                                                                                                 |                                                                                                                                          |                                                                                                                                                                                                       |                                                                                              |  |  |

| bit 4                   | CCP5IF: CC                                                                   | CP5 Interrupt Flag bi                                                                                                                                                                                            | t                                                           |                                                                                                                                                                 |                                                                                                                                          |                                                                                                                                                                                                       |                                                                                              |  |  |