#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 25                                                                           |

| Program Memory Size        | 14KB (8K x 14)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 1K × 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18855t-i-ss |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|              | BANK 24                             |              | BANK 25                             |              | BANK 26                             |              | BANK 27                             |              | BANK 28                                          | _            | BANK 29                                          |              | BANK 30                                           |                                                                      | BANK 31                                                                                                                                                             |

|--------------|-------------------------------------|--------------|-------------------------------------|--------------|-------------------------------------|--------------|-------------------------------------|--------------|--------------------------------------------------|--------------|--------------------------------------------------|--------------|---------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C00h<br>C0Bh | Core Registers<br>(Table 3-2)       | C80h<br>C8Bh | Core Registers<br>(Table 3-2)       | D00h<br>D0Bh | Core Registers<br>(Table 3-2)       | D80h<br>D8Bh | Core Registers<br>(Table 3-2)       | E00h<br>E0Bh | Core Registers<br>(Table 3-2)                    | E80h<br>E8Bh | Core Registers<br>(Table 3-2)                    | F00h<br>F0Bh | Core Registers<br>(Table 3-2)                     | F80h<br>F8Bh                                                         | Core Registers<br>(Table 3-2)                                                                                                                                       |

| COCh         | Unimplemented<br>Read as '0'        | C8Ch         | Unimplemented<br>Read as '0'        | DOCH         | Unimplemented<br>Read as '0'        | D&Ch         | Unimplemented<br>Read as '0'        | EOCh         | See Table 3-8 for<br>register mapping<br>details | E8Ch         | See Table 3-9 for<br>register mapping<br>details | FOCh         | See Table 3-10<br>for register<br>mapping details | FE3h<br>FE3h<br>FE4h<br>FE5h<br>FE8h<br>FE9h<br>FEAh<br>FEBh<br>FECh | Unimplemented<br>Read as '0'<br>STATUS_SHAD<br>WREG_SHAD<br>BSR_SHAD<br>PCLATH_SHAD<br>FSR0L_SHAD<br>FSR0L_SHAD<br>FSR1L_SHAD<br>FSR1L_SHAD<br>FSR1L_SHAD<br>STKPTR |

| C6Fh         |                                     | CEFh         |                                     | D6Fh         |                                     | DEFh         |                                     | E6Fh         |                                                  | EEFh         |                                                  | F6Fh         |                                                   | FEEh<br>FEFh                                                         | TOSL<br>TOSH                                                                                                                                                        |

| C70h<br>CFFh | Common RAM<br>Accesses<br>70h – 7Fh | CF0h<br>CFFh | Common RAM<br>Accesses<br>70h – 7Fh | D70h<br>D7Fh | Common RAM<br>Accesses<br>70h – 7Fh | DF0h<br>DFFh | Common RAM<br>Accesses<br>70h – 7Fh | E70h<br>E7Fh | Common RAM<br>Accesses<br>70h – 7Fh              | EF0h<br>EFFh | Common RAM<br>Accesses<br>70h – 7Fh              | F70h<br>F7Fh | Common RAM<br>Accesses<br>70h – 7Fh               | FF0h<br>FFFh                                                         | Common RAM<br>Accesses<br>70h – 7Fh                                                                                                                                 |

## TABLE 3-7: PIC16(L)F18855/75 MEMORY MAP BANK 24-31

Legend: = Unimplemented data memory locations, read as '0'.

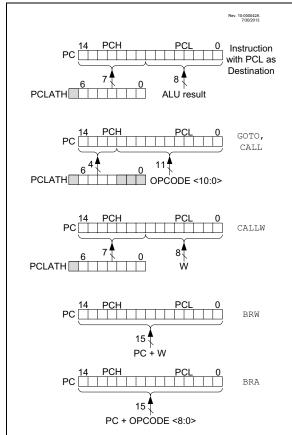

## 3.3 PCL and PCLATH

The Program Counter (PC) is 15 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<14:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 3-3 shows the five situations for the loading of the PC.

FIGURE 3-3: LOADING OF PC IN DIFFERENT SITUATIONS

## 3.3.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<14:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper seven bits to the PCLATH register. When the lower eight bits are written to the PCL register, all 15 bits of the program counter will change to the values contained in the PCLATH register.

## 3.3.2 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to Application Note AN556, *"Implementing a Table Read"* (DS00556).

## 3.3.3 COMPUTED FUNCTION CALLS

A computed function CALL allows programs to maintain tables of functions and provide another way to execute state machines or look-up tables. When performing a table read using a computed function CALL, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block).

If using the CALL instruction, the PCH<2:0> and PCL registers are loaded with the operand of the CALL instruction. PCH<6:3> is loaded with PCLATH<6:3>.

The CALLW instruction enables computed calls by combining PCLATH and W to form the destination address. A computed CALLW is accomplished by loading the W register with the desired address and executing CALLW. The PCL register is loaded with the value of W and PCH is loaded with PCLATH.

## 3.3.4 BRANCHING

The branching instructions add an offset to the PC. This allows relocatable code and code that crosses page boundaries. There are two forms of branching, BRW and BRA. The PC will have incremented to fetch the next instruction in both cases. When using either branching instruction, a PCL memory boundary may be crossed.

If using BRW, load the W register with the desired unsigned address and execute BRW. The entire PC will be loaded with the address PC + 1 + W.

If using BRA, the entire PC will be loaded with PC + 1, the signed value of the operand of the BRA instruction.

## 4.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection and data memory are controlled independently. Internal access to the program memory is unaffected by any code protection setting.

## 4.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Self-writing the program memory is dependent upon the write protection setting. See **Section 4.4** "Write **Protection**" for more information.

## 4.3.2 DATA MEMORY PROTECTION

The entire data EEPROM memory space is protected from external reads and writes by the CPD bit in the Configuration Words. When CPD = 0, external reads and writes of EEPROM memory are inhibited and a read will return all '0's. The CPU can continue to read EEPROM memory, regardless of the protection bit settings.

## 4.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as boot loader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Words define the size of the program memory block that is protected.

## 4.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See Section 10.4.7 "NVMREG Data EEPROM Memory, User ID, Device ID and Configuration Word Access" for more information on accessing these memory locations. For more information on checksum calculation, see the "*PIC16(L)F188XX Memory Programming Specification*" (DS40001753).

## 5.3 Register Definitions: Brown-out Reset Control

#### REGISTER 5-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u               | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|-----------------------|-----|-----|-----|-----|-----|-----|--------|

| SBOREN <sup>(1)</sup> | —   | —   | —   | —   | —   | —   | BORRDY |

| bit 7                 |     |     |     |     |     |     | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | <pre>SBOREN: Software Brown-out Reset Enable bit<sup>(1)</sup> If BOREN &lt;1:0&gt; in Configuration Words ≠ 01: SBOREN is read/write, but has no effect on the BOR. If BOREN &lt;1:0&gt; in Configuration Words = 01: 1 = BOR Enabled 0 = BOR Disabled</pre> |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-1 | Unimplemented: Read as '0'                                                                                                                                                                                                                                    |

| bit 0   | <b>BORRDY:</b> Brown-out Reset Circuit Ready Status bit<br>1 = The Brown-out Reset circuit is active<br>0 = The Brown-out Reset circuit is inactive                                                                                                           |

**Note 1:** BOREN<1:0> bits are located in Configuration Words.

## 5.4 MCLR

The  $\overline{\text{MCLR}}$  is an optional external input that can reset the device. The  $\overline{\text{MCLR}}$  function is controlled by the MCLRE bit of Configuration Words and the LVP bit of Configuration Words (Table 5-2).

| TABLE 5-2: MO | CLR CONFIGURATION |

|---------------|-------------------|

|---------------|-------------------|

| MCLRE | LVP | MCLR     |

|-------|-----|----------|

| 0     | 0   | Disabled |

| 1     | 0   | Enabled  |

| x     | 1   | Enabled  |

## 5.4.1 MCLR ENABLED

When MCLR is enabled and the pin is held low, the device is held in Reset. The MCLR pin is connected to VDD through an internal weak pull-up.

The device has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

| <b>Note:</b> A Reset does not drive the MCLR pin low. |

|-------------------------------------------------------|

|-------------------------------------------------------|

## 5.4.2 MCLR DISABLED

When MCLR is disabled, the pin functions as a general purpose input and the internal weak pull-up is under software control. See **Section 12.2 "I/O Priorities"** for more information.

## 5.5 Windowed Watchdog Timer (WWDT) Reset

The Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period and the window is open. The TO and PD bits in the STATUS register and the WDT bit in PCON are changed to indicate a WDT Reset caused by the timer overflowing, and WDTWV bit in the PCON register is changed to indicate a WDT Reset caused by a window violation. See **Section 9.0 "Windowed Watchdog Timer (WWDT)"** for more information.

# 6.0 OSCILLATOR MODULE (WITH FAIL-SAFE CLOCK MONITOR)

## 6.1 Overview

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 6-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from external oscillators, quartz-crystal resonators and ceramic resonators. In addition, the system clock source can be supplied from one of two internal oscillators and PLL circuits, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software.

- Fail-Safe Clock Monitor (FSCM) designed to detect a failure of the external clock source (LP, XT, HS, ECH, ECM, ECL) and switch automatically to the internal oscillator.

- Oscillator Start-up Timer (OST) ensures stability of crystal oscillator sources.

The RSTOSC bits of Configuration Word 1 determine the type of oscillator that will be used when the device reset, including when it is first powered up.

The internal clock modes, LFINTOSC, HFINTOSC (set at 1 MHz), or HFINTOSC (set at 32 MHz) can be set through the RSTOSC bits.

If an external clock source is selected, the FEXTOSC bits of Configuration Word 1 must be used in conjunction with the RSTOSC bits to select the external clock mode.

The external oscillator module can be configured in one of the following clock modes, by setting the FEXTOSC<2:0> bits of Configuration Word 1:

- 1. ECL External Clock Low-Power mode (below 500 kHz)

- 2. ECM External Clock Medium Power mode (500 kHz to 8 MHz)

- 3. ECH External Clock High-Power mode (above 8 MHz)

- 4. LP 32 kHz Low-Power Crystal mode.

- 5. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode (between 100 kHz and 4 MHz)

- 6. HS High Gain Crystal or Ceramic Resonator mode (above 4 MHz)

The ECH, ECM, and ECL clock modes rely on an external logic level signal as the device clock source. The LP, XT, and HS clock modes require an external crystal or resonator to be connected to the device. Each mode is optimized for a different frequency range. The INTOSC internal oscillator block produces low and high-frequency clock sources, designated LFINTOSC and HFINTOSC. (see Internal Oscillator Block, Figure 6-1). A wide selection of device clock frequencies may be derived from these clock sources.

| <b>REGISTER 12-14:</b> | LATB: PORTB | DATA LATCH REGISTER |

|------------------------|-------------|---------------------|

|------------------------|-------------|---------------------|

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATB7   | LATB6   | LATB5   | LATB4   | LATB3   | LATB2   | LATB1   | LATB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

## bit 7-0 LATB<7:0>: RB<7:0> Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

## REGISTER 12-15: ANSELB: PORTB ANALOG SELECT REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ANSB7   | ANSB6   | ANSB5   | ANSB4   | ANSB3   | ANSB2   | ANSB1   | ANSB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ANSB<7:0>**: Analog Select between Analog or Digital Function on pins RB<7:0>, respectively

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

0 = Digital I/O. Pin is assigned to port or digital special function.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

### REGISTER 12-25: ANSELC: PORTC ANALOG SELECT REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ANSC7   | ANSC6   | ANSC5   | ANSC4   | ANSC3   | ANSC2   | ANSC1   | ANSC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ANSC<7:0>: Analog Select between Analog or Digital Function on Pins RC<7:0>, respectively<sup>(1)</sup> 0 = Digital I/O. Pin is assigned to port or digital special function. 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

#### REGISTER 12-26: WPUC: WEAK PULL-UP PORTC REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WPUC7   | WPUC6   | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 WPUC<7:0>: Weak Pull-up Register bits<sup>(1)</sup>

- 1 = Pull-up enabled

- 0 = Pull-up disabled

Note 1: The weak pull-up device is automatically disabled if the pin is configured as an output.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

|                      |                        |                     |       |           | Rem   | appable to Pins of PORTx |       |           |       |       |

|----------------------|------------------------|---------------------|-------|-----------|-------|--------------------------|-------|-----------|-------|-------|

| Input Signal<br>Name | Input Register<br>Name | Default<br>Location | P     | PIC16F188 | 55    |                          | I     | PIC16F188 | 75    |       |

|                      |                        | at POR              | PORTA | PORTB     | PORTC | PORTA                    | PORTB | PORTC     | PORTD | PORTE |

| CLCIN3               | CLCIN3PPS              | RB7                 |       | •         | •     |                          | •     |           | •     |       |

| ADCACT               | ADCACTPPS              | RB4                 |       | •         | •     |                          | •     |           | •     |       |

| SCK1/SCL1            | SSP1CLKPPS             | RC3                 |       | •         | •     |                          | •     | •         |       |       |

| SDI1/SDA1            | SSP1DATPPS             | RC4                 |       | •         | •     |                          | •     | •         |       |       |

| SS1                  | SSPSS1PPS              | RA5                 | •     |           | •     | •                        |       |           | •     |       |

| SCK2/SCL2            | SSP2CLKPPS             | RB1                 |       | •         | •     |                          | •     |           | •     |       |

| SDI2/SDA2            | SSP2DATPPS             | RB2                 |       | •         | •     |                          | •     |           | •     |       |

| SS2                  | SSP2SSPPS              | RB0                 |       | •         | •     |                          | •     |           | •     |       |

| RX/DT                | RXPPS                  | RC7                 |       | •         | •     |                          | •     | •         |       |       |

| СК                   | TXPPS                  | RC6                 |       | •         | •     |                          | •     | •         |       |       |

## TABLE 13-1: PPS INPUT SIGNAL ROUTING OPTIONS (CONTINUED)

## 19.2 Register Definitions: PWM Control

## REGISTER 19-1: PWMxCON: PWM CONTROL REGISTER

| R/W-0/0          | U-0                                                            | R-0               | R/W-0/0  | U-0            | U-0              | U-0            | U-0          |  |

|------------------|----------------------------------------------------------------|-------------------|----------|----------------|------------------|----------------|--------------|--|

| PWMxEN           | —                                                              | PWMxOUT           | PWMxPOL  | —              | —                | —              | —            |  |

| bit 7            |                                                                |                   |          |                |                  |                | bit 0        |  |

|                  |                                                                |                   |          |                |                  |                |              |  |

| Legend:          |                                                                |                   |          |                |                  |                |              |  |

| R = Readable     | bit                                                            | W = Writable      | bit      | U = Unimpler   | nented bit, read | l as '0'       |              |  |

| u = Bit is unch  | anged                                                          | x = Bit is unkr   | nown     | -n/n = Value a | at POR and BO    | R/Value at all | other Resets |  |

| '1' = Bit is set |                                                                | '0' = Bit is clea | ared     |                |                  |                |              |  |

|                  |                                                                |                   |          |                |                  |                |              |  |

| bit 7            | PWMxEN: PV                                                     | VM Module En      | able bit |                |                  |                |              |  |

|                  | 1 = PWM mo                                                     | dule is enable    | b        |                |                  |                |              |  |

|                  | 0 = PWM mo                                                     | dule is disable   | d        |                |                  |                |              |  |

| bit 6            | Unimplemen                                                     | ted: Read as '    | 0'       |                |                  |                |              |  |

| bit 5            | bit 5 <b>PWMxOUT:</b> PWM Module Output Level when Bit is Read |                   |          |                |                  |                |              |  |

| bit 4            | PWMxPOL: PWMx Output Polarity Select bit                       |                   |          |                |                  |                |              |  |

|                  | 1 = PWM output is active-low                                   |                   |          |                |                  |                |              |  |

|                  | 0 = PWM out                                                    | tput is active-hi | gh       |                |                  |                |              |  |

| bit 3-0          | Unimplemented: Read as '0'                                     |                   |          |                |                  |                |              |  |

|                  |                                                                |                   |          |                |                  |                |              |  |

© 2015-2017 Microchip Technology Inc.

| R/W-x/u          | R/W-x/u     | R/W-x/u                               | R/W-x/u         | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u      |

|------------------|-------------|---------------------------------------|-----------------|----------------|------------------|------------------|--------------|

| LCxG4D4T         | LCxG4D4N    | LCxG4D3T                              | LCxG4D3N        | LCxG4D2T       | LCxG4D2N         | LCxG4D1T         | LCxG4D1N     |

| bit 7            |             |                                       |                 |                |                  |                  | bit C        |

|                  |             |                                       |                 |                |                  |                  |              |

| Legend:          |             |                                       |                 |                |                  |                  |              |

| R = Readable     | bit         | W = Writable                          | bit             | •              | nented bit, read |                  |              |

| u = Bit is unch  | anged       | x = Bit is unkr                       | nown            | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set |             | '0' = Bit is cle                      | ared            |                |                  |                  |              |

|                  |             |                                       |                 |                |                  |                  |              |

| bit 7            |             | Gate 3 Data 4                         | •               |                |                  |                  |              |

|                  |             | (true) is gated i<br>(true) is not ga |                 |                |                  |                  |              |

| bit 6            |             | Gate 3 Data 4                         |                 |                |                  |                  |              |

| bit o            |             | (inverted) is ga                      | •               | ,              |                  |                  |              |

|                  |             | (inverted) is no                      |                 |                |                  |                  |              |

| bit 5            | LCxG4D3T: ( | Gate 3 Data 3                         | True (non-inve  | rted) bit      |                  |                  |              |

|                  | 1 = CLCIN2  | (true) is gated                       | into CLCx Gat   | e 3            |                  |                  |              |

|                  | 0 = CLCIN2  | (true) is not ga                      | ted into CLCx   | Gate 3         |                  |                  |              |

| bit 4            |             | Gate 3 Data 3                         | •               | ,              |                  |                  |              |

|                  |             | (inverted) is ga                      |                 |                |                  |                  |              |

| hit 2            |             | (inverted) is no                      | •               |                |                  |                  |              |

| bit 3            |             | Gate 3 Data 2 3<br>(true) is gated    |                 | ,              |                  |                  |              |

|                  |             | (true) is gated (true) is not ga      |                 |                |                  |                  |              |

| bit 2            |             | Gate 3 Data 2                         |                 |                |                  |                  |              |

|                  |             | (inverted) is ga                      | •               | ,              |                  |                  |              |

|                  | 0 = CLCIN1  | (inverted) is no                      | t gated into Cl | _Cx Gate 3     |                  |                  |              |

| bit 1            | LCxG4D1T: ( | Gate 4 Data 1                         | True (non-inve  | rted) bit      |                  |                  |              |

|                  |             | (true) is gated                       |                 |                |                  |                  |              |

|                  |             | (true) is not ga                      |                 |                |                  |                  |              |

| bit 0            |             | Gate 3 Data 1                         |                 |                |                  |                  |              |

|                  |             | (inverted) is ga<br>(inverted) is no  |                 |                |                  |                  |              |

|                  |             |                                       |                 |                |                  |                  |              |

## REGISTER 22-10: CLCxGLS3: GATE 3 LOGIC SELECT REGISTER

## 23.0 ANALOG-TO-DIGITAL CONVERTER WITH COMPUTATION (ADC<sup>2</sup>) MODULE

The Analog-to-Digital Converter with Computation (ADC<sup>2</sup>) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESH:ADRESL register pair).

Additionally, the following features are provided within the ADC module:

- 8-bit Acquisition Timer

- Hardware Capacitive Voltage Divider (CVD) support:

- 8-bit Precharge Timer

- Adjustable sample and hold capacitor array

- Guard ring digital output drive

- Automatic repeat and sequencing:

- Automated double sample conversion for CVD

- Two sets of result registers (Result and Previous result)

- Auto-conversion trigger

- Internal retrigger

- Computation features:

- Averaging and Low-Pass Filter functions

- Reference Comparison

- 2-level Threshold Comparison

- Selectable Interrupts

Figure 23-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion and upon threshold comparison. These interrupts can be used to wake-up the device from Sleep.

## 26.0 DATA SIGNAL MODULATOR (DSM) MODULE

The Data Signal Modulator (DSM) is a peripheral which allows the user to mix a data stream, also known as a modulator signal, with a carrier signal to produce a modulated output.

Both the carrier and the modulator signals are supplied to the DSM module either internally, from the output of a peripheral, or externally through an input pin.

The modulated output signal is generated by performing a logical "AND" operation of both the carrier and modulator signals and then provided to the MDOUT pin.

The carrier signal is comprised of two distinct and separate signals. A carrier high (CARH) signal and a carrier low (CARL) signal. During the time in which the modulator (MOD) signal is in a logic high state, the DSM mixes the carrier high signal with the modulator signal. When the modulator signal is in a logic low state, the DSM mixes the carrier low signal with the modulator signal.

Using this method, the DSM can generate the following types of Key Modulation schemes:

- Frequency-Shift Keying (FSK)

- Phase-Shift Keying (PSK)

- On-Off Keying (OOK)

Additionally, the following features are provided within the DSM module:

- Carrier Synchronization

- · Carrier Source Polarity Select

- · Carrier Source Pin Disable

- · Programmable Modulator Data

- Modulator Source Pin Disable

- · Modulated Output Polarity Select

- Slew Rate Control

Figure 26-1 shows a Simplified Block Diagram of the Data Signal Modulator peripheral.

# PIC16(L)F18855/75

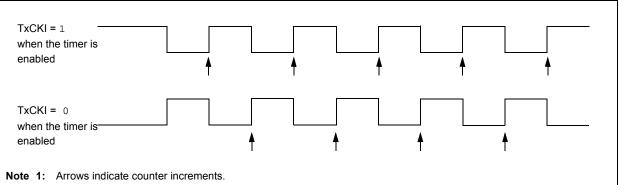

2: In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge of the clock.

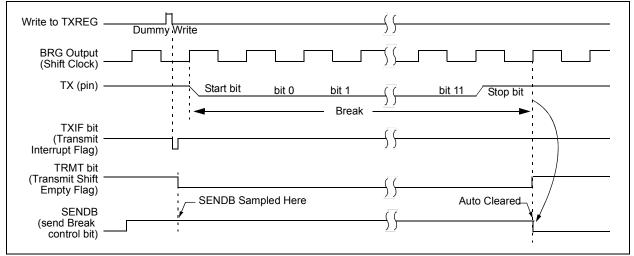

## FIGURE 28-3: TIMER1 GATE ENABLE MODE

## 29.5.2 HARDWARE GATE MODE

The Hardware Gate modes operate the same as the Software Gate mode except the TMRx\_ers external signal can also gate the timer. When used with the CCP the gating extends the PWM period. If the timer is stopped when the PWM output is high then the duty cycle is also extended.

When MODE<4:0> = 00001 then the timer is stopped when the external signal is high. When MODE<4:0> = 00010 then the timer is stopped when the external signal is low.

Figure 29-5 illustrates the Hardware Gating mode for MODE<4:0> = 00001 in which a high input level starts the counter.

|                                 | Rev. 10-00 1999<br>5500201 4                                                                                                                                                                                                                                                                                         |  |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MODE                            | 0b00001                                                                                                                                                                                                                                                                                                              |  |

| TMRx_dk                         |                                                                                                                                                                                                                                                                                                                      |  |

| TMRx_ers_                       |                                                                                                                                                                                                                                                                                                                      |  |

| PRx                             | 5                                                                                                                                                                                                                                                                                                                    |  |

| TMRx                            | $0 \qquad \begin{pmatrix} 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 1 \\ 2 \\ 1 \\ 2 \\ 1 \\ 1 \\ 2 \\ 1 \\ 1$ |  |

| TMRx_postscaled_                |                                                                                                                                                                                                                                                                                                                      |  |

| PWM Duty<br>Cycle<br>PWM Output | 3                                                                                                                                                                                                                                                                                                                    |  |

## 29.6 Timer2 Operation During Sleep

When PSYNC = 1, Timer2 cannot be operated while the processor is in Sleep mode. The contents of the TMR2 and T2PR registers will remain unchanged while processor is in Sleep mode.

When PSYNC = 0, Timer2 will operate in Sleep as long as the clock source selected is also still running. Selecting the LFINTOSC, MFINTOSC, or HFINTOSC oscillator as the timer clock source will keep the selected oscillator running during Sleep.

## 30.2.1 CCPX PIN CONFIGURATION

The software must configure the CCPx pin as an output by clearing the associated TRIS bit and defining the appropriate output pin through the RxyPPS registers. See **Section 13.0 "Peripheral Pin Select (PPS) Module"** for more details.

The CCP output can also be used as an input for other peripherals.

Note: Clearing the CCPxCON register will force the CCPx compare output latch to the default low level. This is not the PORT I/O data latch.

## 30.2.2 TIMER1 MODE RESOURCE

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

See Section 28.0 "Timer1/3/5 Module with Gate Control" for more information on configuring Timer1.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Compare mode. In order for Compare mode to recognize the trigger event on the CCPx pin, TImer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

## 30.2.3 AUTO-CONVERSION TRIGGER

All CCPx modes set the CCP interrupt flag (CCPxIF). When this flag is set and a match occurs, an Auto-conversion Trigger can take place if the CCP module is selected as the conversion trigger source.

Refer to **Section 23.2.6 "Auto-Conversion Trigger"** for more information.

| Note: | Removing the match condition by            |

|-------|--------------------------------------------|

|       | changing the contents of the CCPRxH        |

|       | and CCPRxL register pair, between the      |

|       | clock edge that generates the              |

|       | Auto-conversion Trigger and the clock      |

|       | edge that generates the Timer1 Reset, will |

|       | preclude the Reset from occurring          |

## 30.2.4 COMPARE DURING SLEEP

Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep, unless the timer is running. The device will wake on interrupt (if enabled).

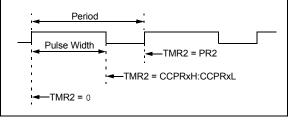

## 30.3 PWM Overview

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully on and fully off states. The PWM signal resembles a square wave where the high portion of the signal is considered the on state and the low portion of the signal is considered the off state. The high portion, also known as the pulse width, can vary in time and is defined in steps. A larger number of steps applied, which lengthens the pulse width, also supplies more power to the load. Lowering the number of steps applied, which shortens the pulse width, supplies less power. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse width time and in turn the power that is applied to the load.

The term duty cycle describes the proportion of the on time to the off time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied.

Figure 30-3 shows a typical waveform of the PWM signal.

## 30.3.1 STANDARD PWM OPERATION

The standard PWM function described in this section is available and identical for all CCP modules.

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCPx pin with up to ten bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PR2 registers

- T2CON registers

- CCPRxL registers

- CCPxCON registers

Figure 30-4 shows a simplified block diagram of PWM operation.

Note: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

#### FIGURE 30-3: CCP PWM OUTPUT SIGNAL

## 32.6.3 PERIOD AND DUTY-CYCLE MODE

In Duty-Cycle mode, either the duty cycle or period (depending on polarity) of the SMTx\_signal can be acquired relative to the SMT clock. The CPW register is updated on a falling edge of the signal, and the CPR register is updated on a rising edge of the signal, along with the SMTxTMR resetting to 0x0001. In addition, the SMTxGO bit is reset on a rising edge when the SMT is in Single Acquisition mode. See Figure 32-6 and Figure 32-7.

## 32.6.7 TIME OF FLIGHT MEASURE MODE

This mode measures the time interval between a rising edge on the SMTWINx input and a rising edge on the SMTx\_signal input, beginning to increment the timer upon observing a rising edge on the SMTWINx input, while updating the SMTxCPR register and resetting the timer upon observing a rising edge on the SMTx\_signal input. In the event of two SMTWINx rising edges without an SMTx\_signal rising edge, it will update the SMTxCPW register with the current value of the timer and reset the timer value. See Figure 32-14 and Figure 32-15.

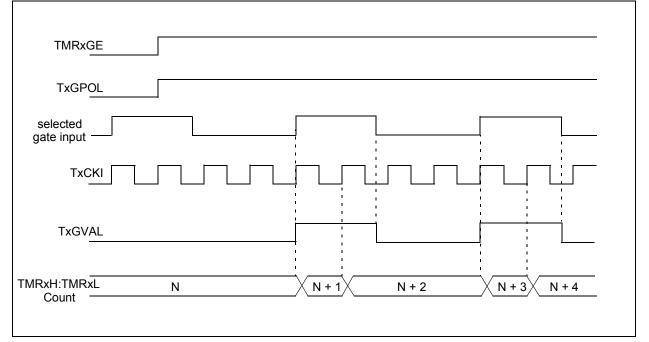

## 33.3.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUD1CON register starts the auto-baud calibration sequence. While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPBRG begins counting up using the BRG counter clock as shown in Figure 33-6. The fifth rising edge will occur on the RX pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPBRGH, SPBRGL register pair, the ABDEN bit is automatically cleared and the RCIF interrupt flag is set. The value in the RCREG needs to be read to clear the RCIF interrupt. RCREG content should be discarded. When calibrating for modes that do not use the SPBRGH register the user can verify that the SPBRGL register did not overflow by checking for 00h in the SPBRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 33-1. During ABD, both the SPBRGH and SPBRGL registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPBRGH and SPBRGL registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte <u>following</u> the Break character (see Section 33.3.3 "Auto-Wake-up on Break").

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- 3: During the auto-baud process, the auto-baud counter starts counting at one. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SPBRGH:SPBRGL register pair.

#### TABLE 33-1: BRG COUNTER CLOCK RATES

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

**Note:** During the ABD sequence, SPBRGL and SPBRGH registers are both used as a 16-bit counter, independent of the BRG16 setting.

#### 0000h XXXXh 001Ch **BRG** Value Edge #5 Edge #1 Edge #2 Edge #3 Edge #4 bit 0 bit 1 bit 2 bit 3 bit 5 bit 6 bit 7 RX pin Start bit 4 Stop bit Auto Cleared Set by User ABDEN bit RCIDL RCIF bit (Interrupt) Read RCREG SPBRGL XXh 1Ch XXh 00h SPBRGH Note 1: The ABD sequence requires the EUSART module to be configured in Asynchronous mode.

#### FIGURE 33-6: AUTOMATIC BAUD RATE CALIBRATION

## 33.3.5 RECEIVING A BREAK CHARACTER

The Enhanced EUSART module can receive a Break character in two ways.

The first method to detect a Break character uses the FERR bit of the RC1STA register and the received data as indicated by RCREG. The Baud Rate Generator is assumed to have been initialized to the expected baud rate.

A Break character has been received when:

- · RCIF bit is set

- FERR bit is set

- RCREG = 00h

The second method uses the Auto-Wake-up feature described in **Section 33.3.3 "Auto-Wake-up on Break"**. By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt, and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Detect feature. For both methods, the user can set the ABDEN bit of the BAUD1CON register before placing the EUSART in Sleep mode.