Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0 0              |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 40-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 40-UQFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18875-e-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                       | Function              | Input<br>Type              | Output Type | Description                                                                                      |

|------------------------------------------------------------|-----------------------|----------------------------|-------------|--------------------------------------------------------------------------------------------------|

| RC4/ANC4/SDA1 <sup>(3,4)</sup> /SDI1 <sup>(1)</sup> /IOCC4 | RC4                   | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                                             |

|                                                            | ANC4                  | AN                         | _           | ADC Channel C4 input.                                                                            |

|                                                            | SDA1 <sup>(3,4)</sup> | l <sup>2</sup> C/<br>SMBus | OD          | MSSP1 I <sup>2</sup> C serial data input/output.                                                 |

|                                                            | SDI1 <sup>(1)</sup>   | TTL/ST                     | -           | MSSP1 SPI serial data input.                                                                     |

|                                                            | IOCC4                 | TTL/ST                     | _           | Interrupt-on-change input.                                                                       |

| RC5/ANC5/T4IN <sup>(1)</sup> /IOCC5                        | RC5                   | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                                             |

|                                                            | ANC5                  | AN                         | _           | ADC Channel C5 input.                                                                            |

|                                                            | T4IN <sup>(1)</sup>   | TTL/ST                     | -           | Timer4 external input.                                                                           |

|                                                            | IOCC5                 | TTL/ST                     | _           | Interrupt-on-change input.                                                                       |

| RC6/ANC6/CK <sup>(3)</sup> /IOCC6                          | RC6                   | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                                             |

|                                                            | ANC6                  | AN                         | -           | ADC Channel C6 input.                                                                            |

|                                                            | CK <sup>(3)</sup>     | TTL/ST                     | CMOS/OD     | EUSART synchronous mode clock input/output.                                                      |

|                                                            | IOCC6                 | TTL/ST                     | -           | Interrupt-on-change input.                                                                       |

| RC7/ANC7/RX <sup>(1)</sup> /DT <sup>(3)</sup> /IOCC7       | RC7                   | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                                             |

|                                                            | ANC7                  | AN                         | -           | ADC Channel C7 input.                                                                            |

|                                                            | RX <sup>(1)</sup>     | TTL/ST                     | -           | EUSART Asynchronous mode receiver data input.                                                    |

|                                                            | DT <sup>(3)</sup>     | TTL/ST                     | CMOS/OD     | EUSART Synchronous mode data input/output.                                                       |

|                                                            | IOCC7                 | TTL/ST                     | _           | Interrupt-on-change input.                                                                       |

| RE3/IOCE3/MCLR/Vpp                                         | RE3                   | TTL/ST                     | _           | General purpose input only (when $\overline{\text{MCLR}}$ is disabled by the Configuration bit). |

|                                                            | IOCE3                 | TTL/ST                     | _           | Interrupt-on-change input.                                                                       |

|                                                            | MCLR                  | ST                         | -           | Master clear input with internal weak pull up resistor.                                          |

|                                                            | Vpp                   | HV                         | -           | ICSP™ High-Voltage Programming mode entry input.                                                 |

| Vdd                                                        | Vdd                   | Power                      | _           | Positive supply voltage input.                                                                   |

#### **TABLE 1-2:** PIC16F18855 PINOUT DESCRIPTION (CONTINUED)

CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels Legend: AN = Analog input or output TTL = TTL compatible input ST

= Open-Drain = Schmitt Trigger input with I<sup>2</sup>C

1<sup>2</sup>C

Note

HV = High Voltage XTAL = Crystal levels This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx This is a PPS remappable input signal. The input function may be used for this signal. 1:

All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options 2: as described in Table 13-3.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and 3: PPS output registers.

These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS 4: assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

| TABLE   | ABLE 3-13: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED) |                                  |        |                |            |               |                    |               |             |         |                       |                              |  |

|---------|---------------------------------------------------------------------|----------------------------------|--------|----------------|------------|---------------|--------------------|---------------|-------------|---------|-----------------------|------------------------------|--|

| Address | Name                                                                | PIC16(L)F18855<br>PIC16(L)F18875 | Bit 7  | Bit 6          | Bit 5      | Bit 4         | Bit 3              | Bit 2         | Bit 1       | Bit 0   | Value on:<br>POR, BOR | Value on all<br>other Resets |  |

| Bank 1  |                                                                     |                                  |        |                |            |               |                    |               |             |         |                       |                              |  |

|         |                                                                     |                                  |        |                | CPU        | CORE REGISTER | S; see Table 3-2 f | for specifics |             |         |                       |                              |  |

| 08Ch    |                                                                     |                                  |        |                |            |               |                    |               |             |         |                       |                              |  |

| 08Dh    | ADRESH                                                              |                                  |        |                |            | A             | DRESH<7:0>         |               |             |         | 0000 0000             | 0000 0000                    |  |

| 08Eh    | ADPREVL                                                             |                                  |        |                |            | 0000 0000     | 0000 0000          |               |             |         |                       |                              |  |

| 08Fh    | ADPREVH                                                             |                                  |        |                |            | 0000 0000     | 0000 0000          |               |             |         |                       |                              |  |

| 090h    | ADACCL                                                              |                                  |        | ADACCL<7:0>    |            |               |                    |               |             |         |                       | uuuu uuuu                    |  |

| 091h    | ADACCH                                                              |                                  |        | ADACCH<7:0>    |            |               |                    |               |             |         |                       | uuuu uuuu                    |  |

| 092h    | —                                                                   | —                                |        |                |            | U             | nimplemented       |               |             |         | _                     | _                            |  |

| 093h    | ADCON0                                                              |                                  | ADON   | ADCONT         | —          | ADCS          | —                  | ADFRM0        | —           | ADGO    | 00-0 -0-0             | 00-0 -0-0                    |  |

| 094h    | ADCON1                                                              |                                  | ADPPOL | ADIPEN         | ADGPOL     | _             | —                  | —             | _           | ADDSEN  | 0000                  | 0000                         |  |

| 095h    | ADCON2                                                              |                                  | ADPSIS |                | ADCRS<2:0> |               | ADACLR             |               | ADMD<2:0>   |         | 0000 0000             | 0000 0000                    |  |

| 096h    | ADCON3                                                              |                                  | -      |                | ADCALC<2:0 | >             | ADSOI              |               | ADTMD<2:0>  |         | -000 0000             | -000 0000                    |  |

| 097h    | ADSTAT                                                              |                                  | ADAOV  | ADUTHR         | ADLTHR     | ADMATH        | —                  |               | ADSTAT<2:0> |         | 0000 -000             | 0000 -000                    |  |

| 098h    | ADCLK                                                               |                                  | _      | —              |            |               | ADO                | CCS<5:0>      |             |         | 00 0000               | 00 0000                      |  |

| 099h    | ADACT                                                               |                                  | _      | —              | _          |               |                    | ADACT<4:0>    |             |         | 0 0000                | 0 0000                       |  |

| 09Ah    | ADREF                                                               |                                  | —      | —              | _          | ADNREF        | —                  | —             | ADPRE       | F<1:0>  | 000                   | 000                          |  |

| 09Bh    | ADCAP                                                               |                                  | —      | —              | —          |               |                    | ADCAP<4:0>    |             |         | 0 0000                | 0 0000                       |  |

| 09Ch    | ADPRE                                                               |                                  |        |                |            | ŀ             | ADPRE<7:0>         |               |             |         | 0000 0000             | 0000 0000                    |  |

| 09Dh    | ADACQ                                                               |                                  |        |                |            | ŀ             | ADACQ<7:0>         |               |             |         | 0000 0000             | 0000 0000                    |  |

| 09Eh    | ADPCH                                                               |                                  | _      | — — ADPCH<5:0> |            |               |                    |               |             | 00 0000 | 00 0000               |                              |  |

| 09Fh    | —                                                                   | _                                |        |                |            | —             | _                  |               |             |         |                       |                              |  |

© 2015-2017 Microchip Technology Inc.

Legend: x = unknown, u = unchanged, q =depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Register present on PIC16F18855/75 devices only. Unimplemented, read as '1'. Note 1:

2:

| TABLE   | ABLE 3-13: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED) |                                  |                                      |               |             |                                       |                  |               |           |           |                       |                              |  |

|---------|---------------------------------------------------------------------|----------------------------------|--------------------------------------|---------------|-------------|---------------------------------------|------------------|---------------|-----------|-----------|-----------------------|------------------------------|--|

| Address | Name                                                                | PIC16(L)F18855<br>PIC16(L)F18875 | Bit 7                                | Bit 6         | Bit 5       | Bit 4                                 | Bit 3            | Bit 2         | Bit 1     | Bit 0     | Value on:<br>POR, BOR | Value on all<br>other Resets |  |

| Bank 6  |                                                                     |                                  |                                      |               |             |                                       |                  |               |           |           |                       |                              |  |

|         |                                                                     |                                  |                                      |               | CPU         | CORE REGISTER                         | S; see Table 3-2 | for specifics |           |           |                       |                              |  |

| 30Ch    | CCPR1L                                                              |                                  | Capture/Comp                         | are/PWM Regis | ter 1 (LSB) |                                       |                  |               |           |           | xxxx xxxx             | xxxx xxxx                    |  |

| 30Dh    | CCPR1H                                                              |                                  | Capture/Comp                         | are/PWM Regis |             | xxxx xxxx                             | xxxx xxxx        |               |           |           |                       |                              |  |

| 30Eh    | CCP1CON                                                             |                                  | EN                                   | —             | OUT         | FMT                                   |                  | MODE<3:0>     |           |           |                       | 0-00 0000                    |  |

| 30Fh    | CCP1CAP                                                             |                                  | —                                    | _             | —           | -                                     | _                |               | 0000      | 0000      |                       |                              |  |

| 310h    | CCPR2L                                                              |                                  | Capture/Compare/PWM Register 2 (LSB) |               |             |                                       |                  |               |           |           |                       | xxxx xxxx                    |  |

| 311h    | CCPR2H                                                              |                                  | Capture/Compare/PWM Register 2 (MSB) |               |             |                                       |                  |               |           |           |                       | xxxx xxxx                    |  |

| 312h    | CCP2CON                                                             |                                  | EN                                   | _             | OUT         | FMT                                   |                  | MODE          | 0-00 0000 | 0-00 0000 |                       |                              |  |

| 313h    | CCP2CAP                                                             |                                  | —                                    | —             | _           | -                                     | —                |               | CTS<2:0>  |           | 0000                  | 0000                         |  |

| 314h    | CCPR3L                                                              |                                  | Capture/Compa                        | are/PWM Regis | ter 3 (LSB) |                                       |                  |               |           |           | xxxx xxxx             | xxxx xxxx                    |  |

| 315h    | CCPR3H                                                              |                                  | Capture/Comp                         | are/PWM Regis | ter 3 (MSB) |                                       |                  |               |           |           | xxxx xxxx             | xxxx xxxx                    |  |

| 316h    | CCP3CON                                                             |                                  | EN                                   | —             | OUT         | FMT                                   |                  | MODE          | <3:0>     |           | 0-00 0000             | 0-00 0000                    |  |

| 317h    | CCP3CAP                                                             |                                  | —                                    | —             | —           | -                                     |                  | CTS<          | :3:0>     |           | 0000                  | 0000                         |  |

| 318h    | CCPR4L                                                              |                                  | Capture/Compa                        | are/PWM Regis | ter 4 (LSB) |                                       |                  |               |           |           | xxxx xxxx             | xxxx xxxx                    |  |

| 319h    | CCPR4H                                                              |                                  | Capture/Compa                        | are/PWM Regis | ter 4 (MSB) |                                       |                  |               |           |           | xxxx xxxx             | xxxx xxxx                    |  |

| 31Ah    | CCP4CON                                                             |                                  | EN                                   | —             | OUT         | FMT                                   |                  | MODE          | <3:0>     |           | 0-00 0000             | 0-00 0000                    |  |

| 31Bh    | CCP4CAP                                                             |                                  |                                      | —             | _           | —                                     |                  | CTS<          | :3:0>     |           | 0000                  | 0000                         |  |

| 31Ch    | CCPR5L                                                              |                                  | Capture/Compa                        | are/PWM Regis | ter 5 (LSB) | · · · · · · · · · · · · · · · · · · · |                  |               |           |           | xxxx xxxx             | xxxx xxxx                    |  |

| 31Dh    | CCPR5H                                                              |                                  | Capture/Compa                        | are/PWM Regis | ter 5 (MSB) |                                       |                  |               |           |           | xxxx xxxx             | xxxx xxxx                    |  |

| 31Eh    | CCP5CON                                                             |                                  | EN                                   | —             | OUT         | FMT                                   |                  | MODE          | <3:0>     |           | 0-00 0000             | 0-00 0000                    |  |

| 31Fh    | CCP5CAP                                                             |                                  | —                                    | _             | —           | —                                     |                  | CTS<          | :3:0>     |           | 0000                  | 0000                         |  |

© 2015-2017 Microchip Technology Inc.

Legend: x = unknown, u = unchanged, q =depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Register present on PIC16F18855/75 devices only. Unimplemented, read as '1'. Note 1:

2:

| Address         | Name       | PIC16(L)F18855<br>PIC16(L)F18875 | Bit 7    | Bit 6    | Bit 5       | Bit 4    | Bit 3        | Bit 2        | Bit 1        | Bit 0    | Value on:<br>POR, BOR | Value on all<br>other Resets |

|-----------------|------------|----------------------------------|----------|----------|-------------|----------|--------------|--------------|--------------|----------|-----------------------|------------------------------|

| Bank 28 (0      | Continued) |                                  |          |          |             |          |              |              |              |          |                       |                              |

| E22h            | CLC2GLS2   |                                  | LC2G3D4T | LC2G3D4N | LC2G3D3T    | LC2G3D3N | LC2G3D2T     | LC2G3D2N     | LC2G3D1T     | LC2G3D1N | xxxx xxxx             | uuuu uuuu                    |

| E23h            | CLC2GLS3   |                                  | LC2G4D4T | LC2G4D4N | LC2G4D3T    | LC2G4D3N | LC2G4D2T     | LC2G4D2N     | LC2G4D1T     | LC2G4D1N | xxxx xxxx             | uuuu uuuu                    |

| E24h            | CLC3CON    |                                  | LC3EN    | —        | LC3OUT      | LC3INTP  | LC3INTN      | LC3MODE<2:0> |              |          | 0-x0 0000             | 0-x0 0000                    |

| E25h            | CLC3POL    |                                  | LC3POL   | —        | _           | _        | LC3G4POL     | LC3G3POL     | LC3G2POL     | LC3G1POL | 0 xxxx                | 0 uuuu                       |

| E26h            | CLC3SEL0   |                                  | —        | _        |             |          | LC3          | D1S<5:0>     |              |          | xx xxxx               | uu uuuu                      |

| E27h            | CLC3SEL1   |                                  | —        | —        |             |          | LC3          | D2S<5:0>     |              |          | xx xxxx               | uu uuuu                      |

| E28h            | CLC3SEL2   |                                  | —        | —        |             |          | LC3          | D3S<5:0>     |              |          | xx xxxx               | uu uuuu                      |

| E29h            | CLC3SEL3   |                                  | —        | _        | LC3D4S<5:0> |          |              |              |              | xx xxxx  | uu uuuu               |                              |

| E2Ah            | CLC3GLS0   |                                  | LC3G1D4T | LC3G1D4N | LC3G1D3T    | LC3G1D3N | LC3G1D2T     | LC3G1D2N     | LC3G1D1T     | LC3G1D1N | xxxx xxxx             | uuuu uuuu                    |

| E2Bh            | CLC3GLS1   |                                  | LC3G2D4T | LC3G2D4N | LC3G2D3T    | LC3G2D3N | LC3G2D2T     | LC3G2D2N     | LC3G2D1T     | LC3G2D1N | xxxx xxxx             | uuuu uuuu                    |

| E2Ch            | CLC3GLS2   |                                  | LC3G3D4T | LC3G3D4N | LC3G3D3T    | LC3G3D3N | LC3G3D2T     | LC3G3D2N     | LC3G3D1T     | LC3G3D1N | xxxx xxxx             | uuuu uuuu                    |

| E2Dh            | CLC3GLS3   |                                  | LC3G4D4T | LC3G4D4N | LC3G4D3T    | LC3G4D3N | LC3G4D2T     | LC3G4D2N     | LC3G4D1T     | LC3G4D1N | xxxx xxxx             | uuuu uuuu                    |

| E2Eh            | CLC4CON    |                                  | LC4EN    | —        | LC4OUT      | LC4INTP  | LC4INTN      |              | LC4MODE<2:0> |          | 0-x0 0000             | 0-x0 0000                    |

| E2Fh            | CLC4POL    |                                  | LC4POL   | —        | —           |          | LC4G4POL     | LC4G3POL     | LC4G2POL     | LC4G1POL | 0 xxxx                | 0 uuuu                       |

| E30h            | CLC4SEL0   |                                  | —        | —        |             |          | LC4          | D1S<5:0>     |              |          | xx xxxx               | uu uuuu                      |

| E31h            | CLC4SEL1   |                                  | —        | —        |             |          | LC4          | D2S<5:0>     |              |          | xx xxxx               | uu uuuu                      |

| E32h            | CLC4SEL2   |                                  | —        | —        |             |          | LC4          | D3S<5:0>     |              |          | xx xxxx               | uu uuuu                      |

| E33h            | CLC4SEL3   |                                  | _        | —        |             |          | LC4          | D4S<5:0>     |              |          | xx xxxx               | uu uuuu                      |

| E34h            | CLC4GLS0   |                                  | LC4G1D4T | LC4G1D4N | LC4G1D3T    | LC4G1D3N | LC4G1D2T     | LC4G1D2N     | LC4G1D1T     | LC4G1D1N | xxxx xxxx             | uuuu uuuu                    |

| E35h            | CLC4GLS1   |                                  | LC4G2D4T | LC4G2D4N | LC4G2D3T    | LC4G2D3N | LC4G2D2T     | LC4G2D2N     | LC4G2D1T     | LC4G2D1N | xxxx xxxx             | uuuu uuuu                    |

| E36h            | CLC4GLS2   |                                  | LC4G3D4T | LC4G3D4N | LC4G3D3T    | LC4G3D3N | LC4G3D2T     | LC4G3D2N     | LC4G3D1T     | LC4G3D1N | xxxx xxxx             | uuuu uuuu                    |

| E37h            | CLC4GLS3   |                                  | LC4G4D4T | LC4G4D4N | LC4G4D3T    | LC4G4D3N | LC4G4D2T     | LC4G4D2N     | LC4G4D1T     | LC4G4D1N | xxxx xxxx             | uuuu uuuu                    |

| E38h to<br>E6Fh |            | —                                |          |          |             | U        | nimplemented |              |              |          | _                     | —                            |

#### TABLE 3-13: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED)

Legend: x = unknown, u = unchanged, g =depends on condition, - = unimplemented, read as '0', x = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Register present on PIC16F18855/75 devices only.

2: Unimplemented, read as '1'.

# 11.7 Configuring the CRC

The following steps illustrate how to properly configure the CRC.

- Determine if the automatic Program Memory scan will be used with the scanner or manual calculation through the SFR interface and perform the actions specified in Section 11.4 "CRC Data Sources", depending on which decision was made.

- 2. If desired, seed a starting CRC value into the CRCACCH/L registers.

- 3. Program the CRCXORH/L registers with the desired generator polynomial.

- Program the DLEN<3:0> bits of the CRCCON1 register with the length of the data word – 1 (refer to Example 11-1). This determines how many times the shifter will shift into the accumulator for each data word.

- Program the PLEN<3:0> bits of the CRCCON1 register with the length of the polynomial – 2 (refer to Example 11-1).

- Determine whether shifting in trailing zeros is desired and set the ACCM bit of CRCCON0 register appropriately.

- 7. Likewise, determine whether the MSb or LSb should be shifted first and write the SHIFTM bit of CRCCON0 register appropriately.

- 8. Write the CRCGO bit of the CRCCON0 register to begin the shifting process.

- 9a. If manual SFR entry is used, monitor the FULL bit of CRCCON0 register. When FULL = 0, another word of data can be written to the CRCDATH/L registers, keeping in mind that CRCDATH should be written first if the data has >8 bits, as the shifter will begin upon the CRCDATL register being written.

- 9b. If the scanner is used, the scanner will automatically stuff words into the CRCDATH/L registers as needed, as long as the SCANGO bit is set.

- 10a. If using the Flash memory scanner, monitor the SCANIF (or the SCANGO bit) for the scanner to finish pushing information into the CRCDATA registers. After the scanner is completed, monitor the CRCIF (or the BUSY bit) to determine that the CRC has been completed and the check value can be read from the CRCACC registers. If both the interrupt flags are set (or both BUSY and SCANGO bits are cleared), the completed CRC calculation can be read from the CRCACCH/L registers.

- 10b.If manual entry is used, monitor the CRCIF (or BUSY bit) to determine when the CRCACC registers will hold the check value.

# 11.8 Program Memory Scan Configuration

If desired, the Program Memory Scan module may be used in conjunction with the CRC module to perform a CRC calculation over a range of program memory addresses. In order to set up the Scanner to work with the CRC you need to perform the following steps:

- Set the EN bit to enable the module. This can be performed at any point preceding the setting of the SCANGO bit, but if it gets disabled, all internal states of the Scanner are reset (registers are unaffected).

- Choose which memory access mode is to be used (see Section 11.10 "Scanning Modes") and set the MODE bits of the SCANCON0 register appropriately.

- 3. Based on the memory access mode, set the INTM bits of the SCANCON0 register to the appropriate interrupt mode (see Section 11.10.5 "Interrupt Interaction")

- 4. Set the SCANLADRL/H and SCANHADRL/H registers with the beginning and ending locations in memory that are to be scanned.

- 5. Begin the scan by setting the SCANGO bit in the SCANCON0 register. The scanner will wait (CRCGO must be set) for the signal from the CRC that it is ready for the first Flash memory location, then begin loading data into the CRC. It will continue to do so until it either hits the configured end address or an address that is unimplemented on the device, at which point the SCANGO bit will clear, Scanner functions will cease, and the SCANIF interrupt will be triggered. Alternately, the SCANGO bit can be cleared in software if desired.

# 11.9 Scanner Interrupt

The scanner will trigger an interrupt when the SCANGO bit transitions from '1' to '0'. The SCANIF interrupt flag of PIR7 is set when the last memory location is reached and the data is entered into the CRCDATA registers. The SCANIF bit can only be cleared in software. The SCAN interrupt enable is the SCANIE bit of the PIE7 register.

# 11.10 Scanning Modes

The memory scanner can scan in four modes: Burst, Peek, Concurrent, and Triggered. These modes are controlled by the MODE bits of the SCANCON0 register. The four modes are summarized in Table 11-1.

#### REGISTER 12-4: LATA: PORTA DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATA7   | LATA6   | LATA5   | LATA4   | LATA3   | LATA2   | LATA1   | LATA0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LATA<7:0>: RA<7:0> Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

### REGISTER 12-5: ANSELA: PORTA ANALOG SELECT REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ANSA7   | ANSA6   | ANSA5   | ANSA4   | ANSA3   | ANSA2   | ANSA1   | ANSA0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ANSA<7:0>: Analog Select between Analog or Digital Function on pins RA<7:0>, respectively

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

- 0 = Digital I/O. Pin is assigned to port or digital special function.

- **Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

| R/W-1/1   | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |  |  |  |

|-----------|---------|---------|---------|---------|---------|---------|---------|--|--|--|--|

| SLRA7     | SLRA6   | SLRA5   | SLRA4   | SLRA3   | SLRA2   | SLRA1   | SLRA0   |  |  |  |  |

| bit 7 bit |         |         |         |         |         |         |         |  |  |  |  |

|           |         |         |         |         |         |         |         |  |  |  |  |

| Legend:   |         |         |         |         |         |         |         |  |  |  |  |

## REGISTER 12-8: SLRCONA: PORTA SLEW RATE CONTROL REGISTER

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **SLRA<7:0>:** PORTA Slew Rate Enable bits For RA<7:0> pins, respectively 1 = Port pin slew rate is limited 0 = Port pin slews at maximum rate

0 = Port pin slews at maximum rate

### REGISTER 12-9: INLVLA: PORTA INPUT LEVEL CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLA7 | INLVLA6 | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 INLVLA<7:0>: PORTA Input Level Select bits

For RA<7:0> pins, respectively

1 = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

# 12.11 Register Definitions: PORTD

#### REGISTER 12-32: PORTD: PORTD REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RD7     | RD6     | RD5     | RD4     | RD3     | RD2     | RD1     | RD0     |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **RD<7:0>**: PORTD I/O Value bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

**Note 1:** Writes to PORTD are actually written to corresponding LATD register. Reads from PORTD register is return of actual I/O pin values.

## REGISTER 12-33: TRISD: PORTD TRI-STATE REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISD7  | TRISD6  | TRISD5  | TRISD4  | TRISD3  | TRISD2  | TRISD1  | TRISD0  |

| bit 7   |         | •       | •       | •       |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **TRISD<7:0>**: TRISD I/O Value bits 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|-------------|

| WPUD7            | WPUD6   | WPUD5             | WPUD4   | WPUD3          | WPUD2            | WPUD1            | WPUD0       |

| bit 7            |         |                   |         |                |                  |                  | bit 0       |

|                  |         |                   |         |                |                  |                  |             |

| Legend:          |         |                   |         |                |                  |                  |             |

| R = Readable     | bit     | W = Writable I    | bit     | U = Unimpler   | mented bit, read | as '0'           |             |

| u = Bit is unch  | anged   | x = Bit is unkn   | own     | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |             |

|                  |         |                   |         |                |                  |                  |             |

### REGISTER 12-36: WPUD: WEAK PULL-UP PORTD REGISTER

bit 7-0 WPUD<7:0>: WPUD I/O Value bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

Note 1: The weak pull-up device is automatically disabled if the pin is configured as an output.

### REGISTER 12-37: ODCOND: PORTD OPEN-DRAIN CONTROL REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ODCD7   | ODCD6   | ODCD5   | ODCD4   | ODCD3   | ODCD2   | ODCD1   | ODCD0   |

| bit 7   | •       |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ODCD<7:0>**: ODCD I/O Value bits 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

# 16.3 Register Definitions: FVR Control

#### REGISTER 16-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0 | R-q/q                 | R/W-0/0             | R/W-0/0              | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|-----------------------|---------------------|----------------------|-------------|---------|---------|---------|

| FVREN   | FVRRDY <sup>(1)</sup> | TSEN <sup>(3)</sup> | TSRNG <sup>(3)</sup> | CDAFVR<1:0> |         | ADFVI   | R<1:0>  |

| bit 7   |                       |                     |                      |             |         |         | bit 0   |

| Legend:             |                                                                                                                                                    |                                                                                                                                                         |                                                            |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|--|

| R = Read            | able bit                                                                                                                                           | W = Writable bit                                                                                                                                        | U = Unimplemented bit, read as '0'                         |  |  |

| u = Bit is          | unchanged                                                                                                                                          | x = Bit is unknown                                                                                                                                      | -n/n = Value at POR and BOR/Value at all other Resets      |  |  |

| '1' = Bit is        | set                                                                                                                                                | '0' = Bit is cleared                                                                                                                                    | q = Value depends on condition                             |  |  |

| bit 7               | 1 = Fixed                                                                                                                                          | ixed Voltage Reference Ena<br>Voltage Reference is enable<br>Voltage Reference is disabl                                                                | ed                                                         |  |  |

| bit 6               | 1 = Fixed                                                                                                                                          | Fixed Voltage Reference Re<br>Voltage Reference output is<br>Voltage Reference output is                                                                | s ready for use                                            |  |  |

| bit 5               | it 5 <b>TSEN:</b> Temperature Indicator Enable bit <sup>(3)</sup><br>1 = Temperature Indicator is enabled<br>0 = Temperature Indicator is disabled |                                                                                                                                                         |                                                            |  |  |

| bit 4               | 1 = VOUT                                                                                                                                           | Femperature Indicator Range<br>= VDD - 4VT (High Range)<br>= VDD - 2VT (Low Range)                                                                      | e Selection bit <sup>(3)</sup>                             |  |  |

| bit 3-2             | 11 = Com<br>10 = Com<br>01 = Com                                                                                                                   | <1:0>: Comparator FVR Buff<br>parator FVR Buffer Gain is 4<br>parator FVR Buffer Gain is 2<br>parator FVR Buffer Gain is 1<br>parator FVR Buffer is off | lx, (4.096V) <sup>(2)</sup><br>2x, (2.048V) <sup>(2)</sup> |  |  |

| bit 1-0             | 11 = ADC<br>10 = ADC<br>01 = ADC                                                                                                                   | :0>: ADC FVR Buffer Gain S<br>FVR Buffer Gain is 4x, (4.09<br>FVR Buffer Gain is 2x, (2.04<br>FVR Buffer Gain is 1x, (1.02<br>FVR Buffer is off         | 96V) <sup>(2)</sup><br>48V) <sup>(2)</sup>                 |  |  |

| Note 1:<br>2:<br>3: | Fixed Voltage F                                                                                                                                    | vays '1' for PIC16F18855/75<br>Reference output cannot exc<br><b>7.0 "Temperature Indicator</b>                                                         | •                                                          |  |  |

| Name     | Bit 7        | Bit 6            | Bit 5           | Bit 4          | Bit 3    | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |  |  |

|----------|--------------|------------------|-----------------|----------------|----------|--------|--------|--------|---------------------|--|--|

| PWM6CON  | PWM6EN       |                  | PWM6OUT         | PWM6POL        | —        | -      | —      | —      | 287                 |  |  |

| PWM6DCH  |              | PWM6DC<9:2>      |                 |                |          |        |        |        |                     |  |  |

| PWM6DCL  | PWM6D        | )C<1:0>          | _               | _              | _        | _      | _      | _      | 288                 |  |  |

| PWM7CON  | PWM7EN       |                  | PWM7OUT         | PWM7POL        | _        | _      | _      | _      | 287                 |  |  |

| PWM7DCH  |              |                  |                 | PWM7DC<        | <9:2>    |        |        |        | 288                 |  |  |

| PWM7DCL  | PWM7D        | )C<1:0>          | _               | _              | _        | _      | _      | _      | 288                 |  |  |

| T2CON    | ON           |                  | CKPS<2:0>       |                |          | OUTPS  | <3:0>  |        | 441                 |  |  |

| T4CON    | ON           |                  | CKPS<2:0>       |                |          | OUTPS  | <3:0>  |        | 441                 |  |  |

| T6CON    | ON           |                  | CKPS<2:0>       |                |          | OUTPS  | <3:0>  |        | 441                 |  |  |

| T2TMR    | Holding Regi | ster for the 8-l | oit TMR2 Regist | er             |          |        |        |        |                     |  |  |

| T4TMR    | Holding Regi | ster for the 8-l | oit TMR4 Regist | er             |          |        |        |        |                     |  |  |

| T6TMR    | Holding Regi | ster for the 8-l | oit TMR6 Regist | er             |          |        |        |        |                     |  |  |

| T2PR     | TMR2 Period  | Register         |                 |                |          |        |        |        |                     |  |  |

| T4PR     | TMR4 Period  | Register         |                 |                |          |        |        |        |                     |  |  |

| T6PR     | TMR6 Period  | Register         |                 |                |          |        |        |        |                     |  |  |

| RxyPPS   | —            | —                |                 |                | RxyPPS<  | 5:0>   |        |        | 250                 |  |  |

| CWG1ISM  | _            | _                | _               | —              |          | IS<3   | :0>    |        | 312                 |  |  |

| CWG2ISM  |              |                  |                 |                |          | IS<3   | :0>    |        | 312                 |  |  |

| CWG3ISM  |              |                  |                 |                |          | IS<3   | :0>    |        | 312                 |  |  |

| CLCxSELy | _            | _                |                 |                | LCxDyS<5 | 5:0>   |        |        | 329                 |  |  |

| MDSRC    | —            | — — — MDMS<4:0>  |                 |                |          |        |        |        | 399                 |  |  |

| MDCARH   | —            | — — — MDCHS<3:0> |                 |                |          |        |        | 400    |                     |  |  |

| MDCARL   | _            |                  | _               | — — MDCLS<3:0> |          |        |        |        |                     |  |  |

| TRISA    | TRISA7       | TRISA6           | TRISA5          | TRISA4         | TRISA3   | TRISA2 | TRISA1 | TRISA0 | 204                 |  |  |

| TRISC    | TRISC7       | TRISC6           | TRISC5          | TRISC4         | TRISC3   | TRISC2 | TRISC1 | TRISC0 | 220                 |  |  |

# TABLE 19-3: SUMMARY OF REGISTERS ASSOCIATED WITH PWMx

Legend: - = Unimplemented locations, read as '0'. Shaded cells are not used by the PWMx module.

### 20.1.2 PUSH-PULL MODE

In Push-Pull mode, two output signals are generated, alternating copies of the input as illustrated in Figure 20-2. This alternation creates the push-pull effect required for driving some transformer-based power supply designs.

The push-pull sequencer is reset whenever EN = 0 or if an auto-shutdown event occurs. The sequencer is clocked by the first input pulse, and the first output appears on CWGxA.

The unused outputs CWGxC and CWGxD drive copies of CWGxA and CWGxB, respectively, but with polarity controlled by the POLC and POLD bits of the CWGxCON1 register, respectively.

#### 20.1.3 FULL-BRIDGE MODES

In Forward and Reverse Full-Bridge modes, three outputs drive static values while the fourth is modulated by the input data signal. In Forward Full-Bridge mode, CWGxA is driven to its active state, CWGxB and CWGxC are driven to their inactive state, and CWGxD is modulated by the input signal. In Reverse Full-Bridge mode, CWGxC is driven to its active state, CWGxA and CWGxD are driven to their inactive states, and CWGxB is modulated by the input signal. In Full-Bridge mode, the dead-band period is used when there is a switch from forward to reverse or vice-versa. This dead-band control is described in Section 20.5 "Dead-Band Control", with additional details in Section 20.6 "Rising Edge and Reverse Dead Band" and Section 20.7 "Falling Edge and Forward Dead Band".

The mode selection may be toggled between forward and reverse toggling the MODE<0> bit of the CWGxCON0 while keeping MODE<2:1> static, without disabling the CWG module.

## TABLE 23-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

| ADC Clock           | Period (TAD)          | Device Frequency (Fosc)   |                           |                           |                           |                           |                           |

|---------------------|-----------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|

| ADC<br>Clock Source | ADCCS<5:0>            | 32 MHz                    | 20 MHz                    | 16 MHz                    | 8 MHz                     | 4 MHz                     | 1 MHz                     |

| Fosc/2              | 000000                | 62.5ns <sup>(2)</sup>     | 100 ns <sup>(2)</sup>     | 125 ns <sup>(2)</sup>     | 250 ns <sup>(2)</sup>     | 500 ns <sup>(2)</sup>     | 2.0 μs                    |

| Fosc/4              | 000001                | 125 ns <sup>(2)</sup>     | 200 ns <sup>(2)</sup>     | 250 ns <sup>(2)</sup>     | 500 ns <sup>(2)</sup>     | 1.0 μs                    | 4.0 μs                    |

| Fosc/6              | 000010                | 187.5 ns <sup>(2)</sup>   | 300 ns <sup>(2)</sup>     | 375 ns <sup>(2)</sup>     | 750 ns <sup>(2)</sup>     | 1.5 μs                    | 6.0 μs                    |

| Fosc/8              | 000011                | 250 μs <sup>(2)</sup>     | 400 ns <sup>(2)</sup>     | 500 μs <sup>(2)</sup>     | 1.0 μs                    | 2.0 μs                    | 8.0 μs <sup>(3)</sup>     |

|                     |                       |                           |                           |                           |                           |                           |                           |

| Fosc/16             | 000111                | 500 ns <sup>(2)</sup>     | 800 ns <sup>(2)</sup>     | 1.0 μs                    | 2.0 μs                    | 4.0 μs                    | 16.0 μs <sup>(2)</sup>    |

|                     |                       |                           |                           |                           |                           |                           |                           |

| Fosc/128            | 111111                | 4.0 μs                    | 6.4 μs                    | 8.0 μs                    | 16.0 μs <sup>(3)</sup>    | 32.0 μs <sup>(2)</sup>    | 128.0 μs <sup>(2)</sup>   |

| FRC                 | ADCS(ADCON0<br><4>)=1 | 1.0-6.0 μs <sup>(1)</sup> |

Legend: Shaded cells are outside of recommended range.

**Note 1:** See TAD parameter for FRC source typical TAD value.

- **2:** These values violate the required TAD time.

- **3:** Outside the recommended TAD time.

- 4: The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock FOSC. However, the FRC oscillator source must be used when conversions are to be performed with the device in Sleep mode.

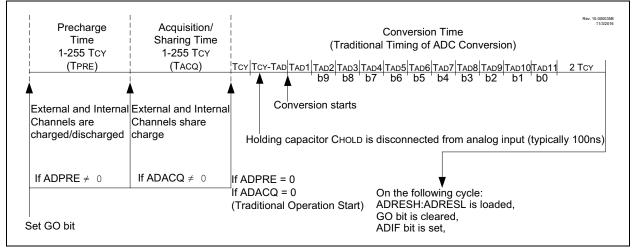

### FIGURE 23-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES (ADSC = 0)

# 29.3 External Reset Sources

In addition to the clock source, the Timer2 also takes in an external Reset source. This external Reset source is selected for Timer2, Timer4, and Timer6 with the T2RST, T4RST, and T6RST registers, respectively. This source can control starting and stopping of the timer, as well as resetting the timer, depending on which mode the timer is in. The mode of the timer is controlled by the MODE<4:0> bits of the TMRxHLT register. Edge-Triggered modes require six Timer clock periods between external triggers. Level-Triggered modes require the triggering level to be at least three Timer clock periods long. External triggers are ignored while in Debug Freeze mode.

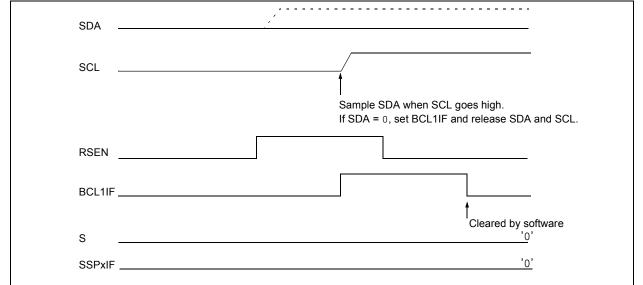

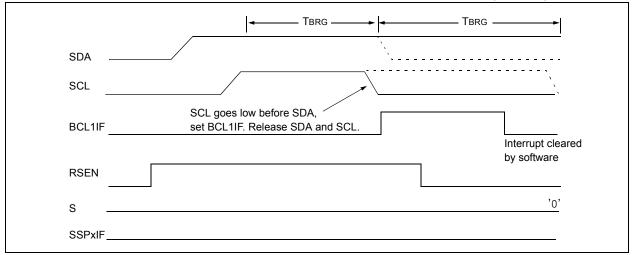

# 31.6.13.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level (Case 1).

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1' (Case 2).

When the user releases SDA and the pin is allowed to float high, the BRG is loaded with SSPxADD and counts down to zero. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 31-36). If SDA is sampled high, the BRG is reloaded and begins

counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 31-37.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

#### FIGURE 31-37: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

F

|            |            |            |     | <b>•</b> • <b>-</b> • • |       |

|------------|------------|------------|-----|-------------------------|-------|

| R/W/HC-0/0 | R/W/HC-0/0 | R/W/HC-0/0 | U-0 | U-0                     | R-0/0 |

| CPRUP      | CPWUP      | RST        | _   | _                       | TS    |

# REGISTER 32-3: SMTxSTAT: SMT STATUS REGISTER

|                                 |                                                                    |                    | •••                               | •••                                                   |    |    |       |  |  |

|---------------------------------|--------------------------------------------------------------------|--------------------|-----------------------------------|-------------------------------------------------------|----|----|-------|--|--|

| CPRUP                           | CPWUP                                                              | RST                |                                   | _                                                     | TS | WS | AS    |  |  |

| bit 7                           | ·                                                                  |                    |                                   |                                                       |    |    | bit 0 |  |  |

|                                 |                                                                    |                    |                                   |                                                       |    |    |       |  |  |

| Legend:                         |                                                                    |                    |                                   |                                                       |    |    |       |  |  |

| HC = Bit is cleared by hardware |                                                                    |                    | HS = Bit is set by hardware       |                                                       |    |    |       |  |  |

| R = Readable bit V              |                                                                    | W = Writable bit   |                                   | U = Unimplemented bit, read as '0'                    |    |    |       |  |  |

| u = Bit is unch                 | nanged                                                             | x = Bit is unknown |                                   | -n/n = Value at POR and BOR/Value at all other Resets |    |    |       |  |  |

| '1' = Bit is set                |                                                                    | '0' = Bit is cle   | ared                              | q = Value depends on condition                        |    |    |       |  |  |

|                                 |                                                                    |                    |                                   |                                                       |    |    |       |  |  |

| bit 7                           |                                                                    |                    | d Buffer Updat                    |                                                       |    |    |       |  |  |

|                                 |                                                                    |                    | xPRx registers<br>ate is complete |                                                       |    |    |       |  |  |

| bit 6                           |                                                                    | 0 1                | e Width Buffer                    |                                                       |    |    |       |  |  |

|                                 |                                                                    |                    | xCPW register                     |                                                       |    |    |       |  |  |

|                                 |                                                                    |                    | date is comple                    |                                                       |    |    |       |  |  |

| bit 5                           | RST: SMT Ma                                                        | anual Timer Re     | eset bit                          |                                                       |    |    |       |  |  |

|                                 |                                                                    |                    | TMR registers                     |                                                       |    |    |       |  |  |

|                                 |                                                                    | •                  | date is complet                   | e                                                     |    |    |       |  |  |

| bit 4-3                         | •                                                                  | ted: Read as '     |                                   |                                                       |    |    |       |  |  |

| bit 2                           |                                                                    | Value Status b     |                                   |                                                       |    |    |       |  |  |

|                                 | 1 = SMT timer is incrementing<br>0 = SMT timer is not incrementing |                    |                                   |                                                       |    |    |       |  |  |

| bit 1                           |                                                                    | IN Value Status    | 0                                 |                                                       |    |    |       |  |  |

|                                 | 1 = SMT wind                                                       |                    |                                   |                                                       |    |    |       |  |  |

|                                 | 0 = SMT wind                                                       | dow is closed      |                                   |                                                       |    |    |       |  |  |

| bit 0                           |                                                                    | nal Value Statu    |                                   |                                                       |    |    |       |  |  |

|                                 | •                                                                  | uisition is in pro | •                                 |                                                       |    |    |       |  |  |

|                                 | 0 = SMT acqu                                                       | uisition is not ir | n progress                        |                                                       |    |    |       |  |  |

R-0/0

R-0/0

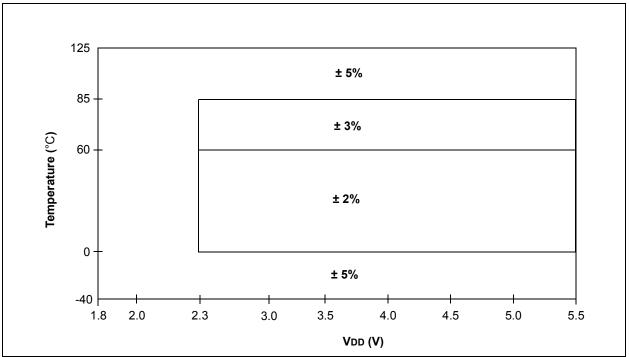

# FIGURE 37-6: PRECISION CALIBRATED HFINTOSC FREQUENCY ACCURACY OVER DEVICE VDD AND TEMPERATURE

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

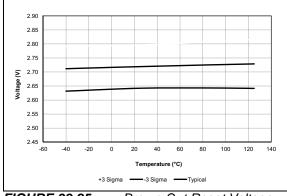

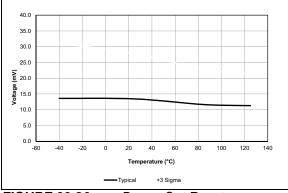

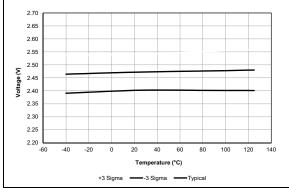

**FIGURE 38-25:** Brown-Out Reset Voltage, Trip Point (BORV = 01).

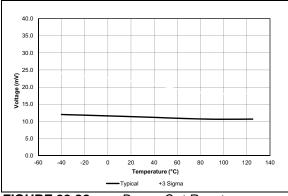

FIGURE 38-26: Brown-Out Reset Hysteresis, Trip Point (BORV = 01).

**FIGURE 38-27:** Brown-Out Reset Voltage, Trip Point (BORV = 1x).

**FIGURE 38-28:** Brown-Out Reset Hysteresis, Trip Point (BORV = 1x).

**FIGURE 38-29:** Brown-Out Reset Voltage, Trip Point (BORV = 11).

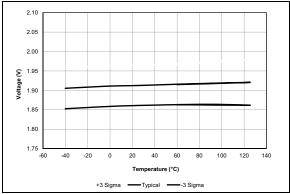

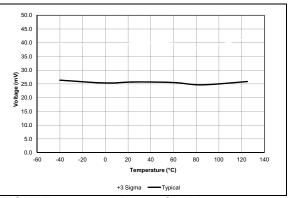

FIGURE 38-30: Brown-Out Reset Hysteresis, Trip Point (BORV = 11), PIC16LF18855/75 Only.

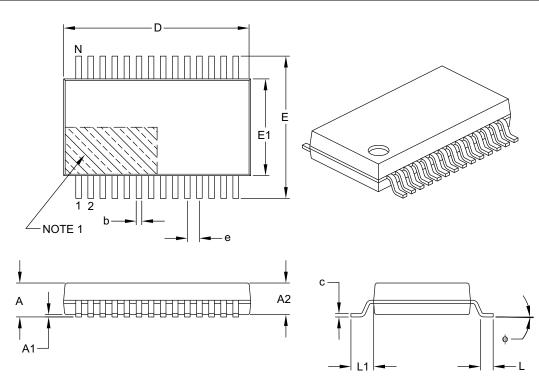

## 28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            | MILLIMETERS |       |       |  |

|--------------------------|------------------|-------------|-------|-------|--|

|                          | Dimension Limits | MIN         | NOM   | MAX   |  |

| Number of Pins           | N                |             | 28    |       |  |

| Pitch                    | е                | 0.65 BSC    |       |       |  |

| Overall Height           | А                | _           | -     | 2.00  |  |

| Molded Package Thickness | A2               | 1.65        | 1.75  | 1.85  |  |

| Standoff                 | A1               | 0.05        | -     | -     |  |

| Overall Width            | E                | 7.40        | 7.80  | 8.20  |  |

| Molded Package Width     | E1               | 5.00        | 5.30  | 5.60  |  |

| Overall Length           | D                | 9.90        | 10.20 | 10.50 |  |

| Foot Length              | L                | 0.55        | 0.75  | 0.95  |  |

| Footprint                | L1               | 1.25 REF    |       |       |  |

| Lead Thickness           | С                | 0.09        | -     | 0.25  |  |

| Foot Angle               | φ                | 0°          | 4°    | 8°    |  |

| Lead Width               | b                | 0.22        | -     | 0.38  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B