Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18875-e-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Program Flash Memory RAM CLKOUT /OSC2 Timing Generation CPU JLKIN, OSC1 ☑─► CLKIN/ INTRC Oscillator (Note 3) ADC Temp TMR0 TMR6 TMR5 TMR4 TMR3 TMR2 TMR1 CRC DSM C2 C1 DAC FVR Scanner 10-bit Indicator CWG1 CWG2 CWG3 SMT2 SMT1 NCO1 EUSART MSSP2 MSSP1 CLC4 CLC3 CLC2 CLC1 ZCD1 PWM6/7 CCPs(5)

Note 1: See applicable chapters for more information on peripherals.

2: See Table 1-1 for peripherals available on specific devices.

PIC16(L)F18855/75 BLOCK DIAGRAM

- 3: See Figure 2-1.

- 4: PIC16(L)F18875 only.

FIGURE 1-1:

Rev. 10-000039J 11/20/2015

PORTA

PORTB

PORTC

PORTD

PORTE

# TABLE 3-8: PIC16(L)F18855/75 MEMORY MAP, BANK 28

|      | Bank 28  |

|------|----------|

| E0Ch | —        |

| E0Dh | —        |

| E0Eh | _        |

| E0Fh | CLCDATA  |

| E10h | CLC1CON  |

| E11h | CLC1POL  |

| E12h | CLC1SEL0 |

| E13h | CLC1SEL1 |

| E14h | CLC1SEL2 |

| E15h | CLC1SEL3 |

| E16h | CLC1GLS0 |

| E17h | CLC1GLS1 |

| E18h | CLC1GLS2 |

| E19h | CLC1GLS3 |

| E1Ah | CLC2CON  |

| E1Bh | CLC2POL  |

| E1Ch | CLC2SEL0 |

| E1Dh | CLC2SEL1 |

| E1Eh | CLC2SEL2 |

| E1Fh | CLC2SEL3 |

| E20h | CLC2GLS0 |

| E21h | CLC2GLS1 |

| E22h | CLC2GLS2 |

| E23h | CLC2GLS3 |

| E24h | CLC3CON  |

| E25h | CLC3POL  |

| E26h | CLC3SEL0 |

| E27h | CLC3SEL1 |

| E28h | CLC3SEL2 |

| E29h | CLC3SEL3 |

| E2Ah | CLC3GLS0 |

| E2Bh | CLC3GLS1 |

| E2Ch | CLC3GLS2 |

| E2Dh | CLC3GLS3 |

|      |          |

|      | Bank 28  |

|------|----------|

| E2Eh | CLC4CON  |

| E2Fh | CLC4POL  |

| E30h | CLC4SEL0 |

| E31h | CLC4SEL1 |

| E32h | CLC4SEL2 |

| E33h | CLC4SEL3 |

| E34h | CLC4GLS0 |

| E35h | CLC4GLS1 |

| E36h | CLC4GLS2 |

| E37h | CLC4GLS3 |

| E38h |          |

|      | _        |

| E6Fh |          |

Legend:

= Unimplemented data memory locations, read as '0'.

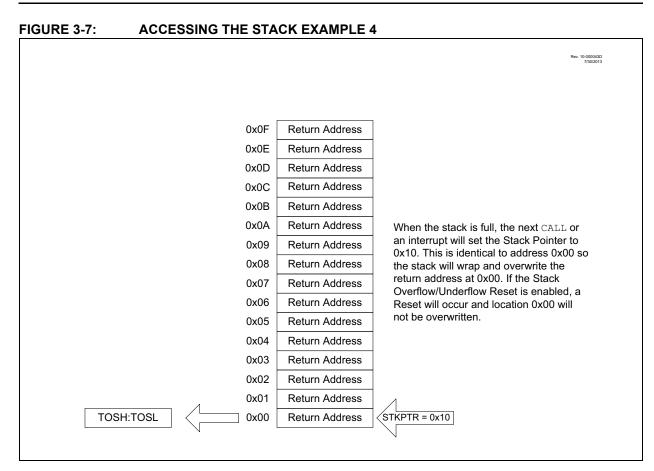

### 3.4.2 OVERFLOW/UNDERFLOW RESET

If the STVREN bit in Configuration Words is programmed to '1', the device will be Reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

### 3.5 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- Traditional Data Memory

- · Linear Data Memory

- Data EEPROM Memory

- Program Flash Memory

|                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                           |                                 | 11.0 |                |                          |                  |             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------|----------------|--------------------------|------------------|-------------|

| R/W/HS-0/0                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                           | U-0                             | U-0  | U-0            | U-0                      | R/W/HS-0/0       | R/W/HS-0/0  |

| OSFIF                                                                                                                                                                                                                                                                         | CSWIF                                                                                                                                                                                                                                                     | —                               | _    | —              | —                        | ADTIF            | ADIF        |

| bit 7                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                           |                                 |      |                |                          |                  | bit 0       |

|                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                           |                                 |      |                |                          |                  |             |

| Legend:                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                           |                                 |      |                |                          |                  |             |

| R = Readabl                                                                                                                                                                                                                                                                   | e bit                                                                                                                                                                                                                                                     | W = Writable                    | bit  | U = Unimpler   | nented bit, read         | as '0'           |             |

| u = Bit is und                                                                                                                                                                                                                                                                | hanged                                                                                                                                                                                                                                                    | x = Bit is unkr                 | iown | -n/n = Value a | at POR and BO            | R/Value at all o | ther Resets |

| '1' = Bit is se                                                                                                                                                                                                                                                               | t                                                                                                                                                                                                                                                         | '0' = Bit is clea               | ared | HS = Hardwa    | are set                  |                  |             |

| bit 7 <b>OSFIF</b> : Oscillator Fail-Safe Interrupt Flag bit<br>1 = Oscillator fail-safe interrupt has occurred (must be cleared in software)                                                                                                                                 |                                                                                                                                                                                                                                                           |                                 |      |                |                          |                  |             |

|                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                           | tor fail-safe inte              | •    |                |                          |                  |             |

| bit 6                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                           | k Switch Comp                   |      | 0              |                          |                  |             |

|                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                           | switch module<br>switch does no |      |                | tion (must be cl<br>tion | eared in softwa  | ire)        |

| bit 5-2                                                                                                                                                                                                                                                                       | Unimplemen                                                                                                                                                                                                                                                | ted: Read as '                  | )'   |                |                          |                  |             |

| bit 1                                                                                                                                                                                                                                                                         | bit 1 <b>ADTIF</b> : Analog-to-Digital Converter (ADC) Threshold Compare Interrupt Flag bit<br>1 = An A/D measurement was beyond the configured threshold (must be cleared in software)<br>0 = A/D measurements have been within the configured threshold |                                 |      |                |                          |                  | tware)      |

| bit 0                                                                                                                                                                                                                                                                         | ADIF: Analog-to-Digital Converter (ADC) Interrupt Flag bit<br>1 = An A/D conversion or complex operation has completed (must be cleared in software)<br>0 = An A/D conversion or complex operation is not complete                                        |                                 |      |                |                          |                  |             |

| Note: Interrupt flag bits are set when an interrupt<br>condition occurs, regardless of the state of<br>its corresponding enable bit or the Global<br>Enable bit, GIE, of the INTCON register.<br>User software should ensure the<br>appropriate interrupt flag bits are clear |                                                                                                                                                                                                                                                           |                                 |      |                |                          |                  |             |

### REGISTER 7-12: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

prior to enabling an interrupt.

| R/W/HS-0/0                      | R/W/HS-0/0                                                                                                                                                             | R/W/HS-0/0                            | R/W/HS-0/0      | U-0             | R/W/HS-0/0                 | R/W/HS-0/0       | R/W/HS-0/0   |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------|-----------------|----------------------------|------------------|--------------|

| SCANIF                          | CRCIF                                                                                                                                                                  | NVMIF                                 | NCO1IF          | —               | CWG3IF                     | CWG2IF           | CWG1IF       |

| bit 7                           |                                                                                                                                                                        |                                       |                 |                 |                            |                  | bit (        |

|                                 |                                                                                                                                                                        |                                       |                 |                 |                            |                  |              |

| Legend:                         | •••                                                                                                                                                                    |                                       |                 |                 |                            |                  |              |

| R = Readable I                  |                                                                                                                                                                        | W = Writable                          |                 | •               | nented bit, read           |                  |              |

| u = Bit is uncha                | anged                                                                                                                                                                  | x = Bit is unkr                       |                 |                 | at POR and BO              | R/value at all o | itner Resets |

| '1' = Bit is set                |                                                                                                                                                                        | '0' = Bit is clea                     | ared            | HS = Hardwa     | are set                    |                  |              |

| bit 7                           | SCANIF: Prog                                                                                                                                                           | gram Memory S                         | Scanner Interr  | upt Flag bit    |                            |                  |              |

|                                 |                                                                                                                                                                        | ation has comp<br>tion is pending     | ,               |                 | nsition has occu<br>ogress | ırred)           |              |

| bit 6                           | CRCIF: CRC Interrupt Flag bit                                                                                                                                          |                                       |                 |                 |                            |                  |              |

|                                 | <ul> <li>1 = The operation has completed (a BUSY 1 to 0 transition has occurred)</li> <li>0 = No operation is pending or the operation is still in progress</li> </ul> |                                       |                 |                 |                            |                  |              |

| bit 5                           | NVMIF: Non-Volatile Memory (NVM) Interrupt Flag bit                                                                                                                    |                                       |                 |                 |                            |                  |              |

|                                 | •                                                                                                                                                                      | ested NVM ope<br>rrupt not assert     |                 | npleted         |                            |                  |              |

| bit 4                           | NCO1IF: Nun                                                                                                                                                            | nerically Contro                      | lled Oscillator | (NCO) Interru   | upt Flag bit               |                  |              |

|                                 |                                                                                                                                                                        | has rolled ove<br>interrupt event     |                 |                 |                            |                  |              |

| bit 3                           | Unimplemen                                                                                                                                                             | ted: Read as '                        | )'              |                 |                            |                  |              |

| bit 2                           | CWG3IF: CW                                                                                                                                                             | G3 Interrupt Fl                       | ag bit          |                 |                            |                  |              |

|                                 |                                                                                                                                                                        | s gone into shu                       |                 |                 |                            |                  |              |

| <b>L</b> :4 4                   |                                                                                                                                                                        | operating norm                        | •               | pt cleared      |                            |                  |              |

| bit 1                           |                                                                                                                                                                        | G2 Interrupt Fl                       |                 |                 |                            |                  |              |

|                                 | <ol> <li>CWG2 has gone into shutdown</li> <li>CWG3 is operating normally, or interrupt cleared</li> </ol>                                                              |                                       |                 |                 |                            |                  |              |

| bit 0                           | CWG1IF: CWG1 Interrupt Flag bit                                                                                                                                        |                                       |                 |                 |                            |                  |              |

| 1 = CWG1 has gone into shutdown |                                                                                                                                                                        |                                       |                 |                 |                            |                  |              |

|                                 | 0 = CWG1 is                                                                                                                                                            | · · · · · · · · · · · · · · · · · · · |                 | we the lease of |                            |                  |              |

## REGISTER 7-19: PIR7: PERIPHERAL INTERRUPT REQUEST REGISTER 7

| Note: | Interrupt flag bits are set when an interrupt |

|-------|-----------------------------------------------|

|       | condition occurs, regardless of the state of  |

|       | its corresponding enable bit or the Global    |

|       | Enable bit, GIE, of the INTCON register.      |

|       | User software should ensure the               |

|       | appropriate interrupt flag bits are clear     |

|       | prior to enabling an interrupt.               |

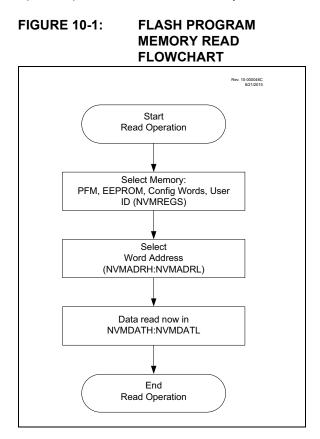

Upon completion, the RD bit is cleared by hardware.

#### EXAMPLE 10-1: PFM PROGRAM MEMORY READ

| data will be returned in the variables,                                                                                                        |                 |                                     |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------|--|--|--|--|

| BANKSEL                                                                                                                                        | NVMADRL         | ; Select Bank for NVMCON registers  |  |  |  |  |

| MOVLW                                                                                                                                          | PROG_ADDR_LO    | ;                                   |  |  |  |  |

| MOVWF                                                                                                                                          | NVMADRL         | ; Store LSB of address              |  |  |  |  |

| MOVLW                                                                                                                                          | PROG_ADDR_HI    | ;                                   |  |  |  |  |

| MOVWF                                                                                                                                          | NVMADRH         | ; Store MSB of address              |  |  |  |  |

| BCF                                                                                                                                            | NVMCON1,NVMREGS | ; Do not select Configuration Space |  |  |  |  |

| BSF                                                                                                                                            | NVMCON1,RD      | ; Initiate read                     |  |  |  |  |

| MOVFNVMDATL,W; Get LSB of wordMOVWFPROG_DATA_LO; Store in user locationMOVFNVMDATH,W; Get MSB of wordMOVWFPROG_DATA_HI; Store in user location |                 |                                     |  |  |  |  |

### REGISTER 11-7: CRCSHIFTH: CRC SHIFT HIGH BYTE REGISTER

| R-0                  | R-0 | R-0                  | R-0  | R-0               | R-0                  | R-0                 | R-0   |

|----------------------|-----|----------------------|------|-------------------|----------------------|---------------------|-------|

|                      |     |                      | SHIF | T<15:8>           |                      |                     |       |

| bit 7                |     |                      |      |                   |                      |                     | bit C |

|                      |     |                      |      |                   |                      |                     |       |

| Legend:              |     |                      |      |                   |                      |                     |       |

| R = Readable bit     |     | W = Writable bit     |      | U = Unimpleme     | nted bit, read as '0 | ,                   |       |

| u = Bit is unchanged |     | x = Bit is unknown   |      | -n/n = Value at F | OR and BOR/Val       | ue at all other Res | ets   |

| '1' = Bit is set     |     | '0' = Bit is cleared |      |                   |                      |                     |       |

bit 7-0

SHIFT<15:8>: CRC Shifter Register bits

Reading from this register reads the CRC Shifter.

### REGISTER 11-8: CRCSHIFTL: CRC SHIFT LOW BYTE REGISTER

| R-0   | R-0 | R-0 | R-0   | R-0    | R-0 | R-0 | R-0   |

|-------|-----|-----|-------|--------|-----|-----|-------|

|       |     |     | SHIFT | ۲<7:0> |     |     |       |

| bit 7 |     |     |       |        |     |     | bit 0 |

|       |     |     |       |        |     |     |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

SHIFT<7:0>: CRC Shifter Register bits

Reading from this register reads the CRC Shifter.

### REGISTER 11-9: CRCXORH: CRC XOR HIGH BYTE REGISTER

| R/W   | R/W | R/W | R/W | R/W  | R/W | R/W | R/W   |

|-------|-----|-----|-----|------|-----|-----|-------|

|       |     |     | X<1 | 5:8> |     |     |       |

| bit 7 |     |     |     |      |     |     | bit 0 |

|       |     |     |     |      |     |     |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 X<15:8>: XOR of Polynomial Term X<sub>N</sub> Enable bits

### REGISTER 11-10: CRCXORL: CRC XOR LOW BYTE REGISTER

| R/W-x/x | U-1   |

|---------|---------|---------|---------|---------|---------|---------|-------|

|         |         |         | X<7:1>  |         |         |         | _     |

| bit 7   |         |         |         |         |         |         | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-1 XOR<7:1>: XOR of Polynomial Term X<sub>N</sub> Enable bits

bit 0 Unimplemented: Read as '1'

| Name     | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3      | Bit 2   | Bit 1    | Bit 0   | Register<br>on page |

|----------|--------|--------|---------|---------|------------|---------|----------|---------|---------------------|

| FVRCON   | FVREN  | FVRRDY | TSEN    | TSRNG   | CDAFV      | ′R<1:0> | ADFV     | R<1:0>  | 269                 |

| ADREF    |        |        |         | ADNREF  |            |         | ADPRE    | F<1:0>  | 362                 |

| ADPCH    |        |        |         |         | ADPCH      | 1<5:0>  |          |         | 363                 |

| CM1CON1  | _      |        | _       | —       | _          | _       | INTP     | INTN    | 280                 |

| CM1NSEL  | _      | _      | _       | _       | _          |         | NCH<2:0> |         | 281                 |

| CM1PSEL  | _      | _      | _       | _       | _          |         | PCH<2:0> |         | 281                 |

| CM2CON1  | _      | _      | _       | _       | _          | _       | INTP     | INTN    | 280                 |

| CM2NSEL  | -      | _      | _       | -       | _          |         | NCH<2:0> |         | 281                 |

| CM2PSEL  | _      | _      | _       | _       | — PCH<2:0> |         | 281      |         |                     |

| DAC1CON0 | DAC1EN |        | DAC10E1 | DAC10E2 | DAC1PS     | SS<1:0> | _        | DAC1NSS | 389                 |

### TABLE 16-1: SUMMARY OF REGISTERS ASSOCIATED WITH FIXED VOLTAGE REFERENCE

Legend: -= unimplemented locations read as '0'. Shaded cells are not used with the Fixed Voltage Reference.

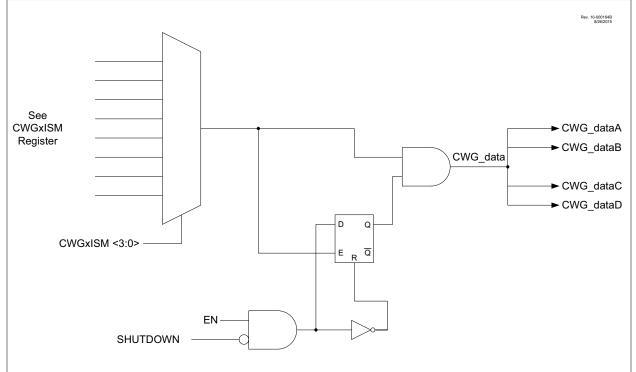

### 20.1.4 STEERING MODES

In Steering modes, the data input can be steered to any or all of the four CWG output pins. In Synchronous Steering mode, changes to steering selection registers take effect on the next rising input.

In Non-Synchronous mode, steering takes effect on the next instruction cycle. Additional details are provided in **Section 20.9 "CWG Steering Mode"**.

### 20.2 Clock Source

The CWG module allows the following clock sources to be selected:

- Fosc (system clock)

- HFINTOSC (16 MHz only)

The clock sources are selected using the CS bit of the CWGxCLKCON register.

| R/W-x/u          | R/W-x/u      | R/W-x/u                                | R/W-x/u         | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|------------------|--------------|----------------------------------------|-----------------|----------------|------------------|------------------|-------------|

| LCxG3D4T         | LCxG3D4N     | LCxG3D3T                               | LCxG3D3N        | LCxG3D2T       | LCxG3D2N         | LCxG3D1T         | LCxG3D1N    |

| bit 7            |              |                                        |                 |                |                  |                  | bit (       |

|                  |              |                                        |                 |                |                  |                  |             |

| Legend:          |              |                                        |                 |                |                  |                  |             |

| R = Readable     | bit          | W = Writable                           | bit             | U = Unimpler   | nented bit, read | as '0'           |             |

| u = Bit is unch  | anged        | x = Bit is unkr                        | nown            | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |              | '0' = Bit is clea                      | ared            |                |                  |                  |             |

|                  |              |                                        |                 |                |                  |                  |             |

| bit 7            |              | Gate 2 Data 4 1                        |                 | ,              |                  |                  |             |

|                  |              | (true) is gated i<br>(true) is not gat |                 |                |                  |                  |             |

| bit 6            |              | Gate 2 Data 4 l                        |                 |                |                  |                  |             |

| DILO             |              | (inverted) is ga                       | •               | ,              |                  |                  |             |

|                  |              | (inverted) is ga                       |                 |                |                  |                  |             |

| bit 5            |              | Gate 2 Data 3 1                        | -               |                |                  |                  |             |

|                  |              | (true) is gated i                      | •               | ,              |                  |                  |             |

|                  | 0 = CLCIN2 ( | (true) is not gat                      | ted into CLCx   | Gate 2         |                  |                  |             |

| bit 4            | LCxG3D3N:    | Gate 2 Data 3 I                        | Negated (inver  | rted) bit      |                  |                  |             |

|                  |              | (inverted) is ga                       |                 |                |                  |                  |             |

|                  |              | (inverted) is no                       | •               |                |                  |                  |             |

| bit 3            |              | Gate 2 Data 2 T                        |                 | ,              |                  |                  |             |

|                  |              | (true) is gated i<br>(true) is not gat |                 |                |                  |                  |             |

| bit 2            |              | Gate 2 Data 2                          |                 |                |                  |                  |             |

|                  |              | (inverted) is ga                       | • ·             | ,              |                  |                  |             |

|                  |              | (inverted) is no                       |                 |                |                  |                  |             |

| bit 1            |              | Sate 2 Data 1 1                        | •               |                |                  |                  |             |

|                  |              | (true) is gated i                      |                 |                |                  |                  |             |

|                  | 0 = CLCIN0   | (true) is not gat                      | ted into CLCx   | Gate 2         |                  |                  |             |

| bit 0            | LCxG3D1N:    | Gate 2 Data 1 I                        | Negated (inver  | ted) bit       |                  |                  |             |

|                  |              | (inverted) is ga                       |                 |                |                  |                  |             |

|                  | 0 = CLCINO ( | (inverted) is no                       | t gated into CL | Cx Gate 2      |                  |                  |             |

## REGISTER 22-9: CLCxGLS2: GATE 2 LOGIC SELECT REGISTER

| Name      | Bit 7   | Bit 6   | Bit 5   | Bit 4    | Bit 3   | Bit 2      | Bit 1    | Bit 0    | Register<br>on Page |

|-----------|---------|---------|---------|----------|---------|------------|----------|----------|---------------------|

| ANSELA    | ANSA7   | ANSA6   | ANSA5   | ANSA4    | ANSA3   | ANSA2      | ANSA1    | ANSA0    | 205                 |

| ANSELC    | ANSC7   | ANSC6   | ANSC5   | ANSC4    | ANSC3   | ANSC2      | ANSC1    | ANSC0    | 221                 |

| INLVLA    | INLVLA7 | INLVLA6 | INLVLA5 | INLVLA4  | INLVLA3 | INLVLA2    | INLVLA1  | INLVLA0  | 207                 |

| INLVLC    | INLVLC7 | INLVLC6 | INLVLC5 | INLVLC4  | INLVLC3 | INLVLC2    | INLVLC1  | INLVLC0  | 222                 |

| MDCON0    | MDEN    | _       | MDOUT   | MDOPOL   |         |            | _        | MDBIT    | 397                 |

| MDCON1    |         | _       | MDCHPOL | MDCHSYNC |         |            | MDCLPOL  | MDCLSYNC | 398                 |

| MDSRC     | _       | _       | —       |          |         | MDMS<4:0>  | >        | •        | 399                 |

| MDCARH    |         | _       |         | —        |         | MDC        | :HS<3:0> |          | 400                 |

| MDCARL    | _       | _       | —       | —        |         | MDC        | CLS<3:0> |          | 401                 |

| MDCARLPPS | _       | _       | —       |          | ME      | CARLPPS<   | 4:0>     |          | 249                 |

| MDCARHPPS | _       | _       | —       |          | MD      | CARHPPS<   | :4:0>    |          | 249                 |

| MDSRCPPS  | _       | _       | —       |          | M       | DSRCPPS<4  | 4:0>     |          | 249                 |

| RxyPPS    |         |         | —       |          |         | RxyPPS<4:0 | )>       |          | 250                 |

| SLRCONA   | SLRA7   | SLRA6   | SLRA5   | SLRA4    | SLRA3   | SLRA2      | SLRA1    | SLRA0    | 207                 |

| SLRCONC   | SLRC7   | SLRC6   | SLRC5   | SLRC4    | SLRC3   | SLRC2      | SLRC1    | SLRC0    | 222                 |

| TRISA     | TRISA7  | TRISA6  | TRISA5  | TRISA4   | TRISA3  | TRISA2     | TRISA1   | TRISA0   | 204                 |

| TRISC     | TRISC7  | TRISC6  | TRISC5  | TRISC4   | TRISC3  | TRISC2     | TRISC1   | TRISC0   | 220                 |

### TABLE 26-1: SUMMARY OF REGISTERS ASSOCIATED WITH DATA SIGNAL MODULATOR MODE

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used in the Data Signal Modulator mode.

| Name     | Bit 7       | Bit 6           | Bit 5                          | Bit 4  | Bit 3 | Bit 2     | Bit 1   | Bit 0  | Register<br>on Page |  |

|----------|-------------|-----------------|--------------------------------|--------|-------|-----------|---------|--------|---------------------|--|

| CCP1CON  | EN          | _               | OUT                            | FMT    |       | MODE<3:0> |         |        |                     |  |

| CCP2CON  | EN          | —               | OUT                            | FMT    |       | MODE      | E<3:0>  |        | 452                 |  |

| CCPTMRS0 | C4TSE       | L<1:0>          | C3TSE                          | L<1:0> | C2TSE | L<1:0>    | C1TSE   | L<1:0> | 455                 |  |

| CCPTMRS1 | —           | —               | P7TSE                          | L<1:0> | P6TSE | L<1:0>    | C5TSE   | L<1:0> | 455                 |  |

| INTCON   | GIE         | PEIE            | —                              | —      | —     | —         | —       | INTEDG | 134                 |  |

| PIE1     | OSFIE       | CSWIE           | —                              | —      | —     | _         | ADTIE   | ADIE   | 136                 |  |

| PIR1     | OSFIF       | CSWIF           | —                              | —      | —     | _         | ADTIF   | ADIF   | 145                 |  |

| PR2      | Timer2 Mod  | ule Period Re   | gister                         |        |       |           |         | L      | 425*                |  |

| TMR2     | Holding Reg | ister for the 8 | r for the 8-bit TMR2 Register  |        |       |           |         |        | 425*                |  |

| T2CON    | ON          |                 | CKPS<2:0>                      |        |       | OUTP      | S<3:0>  |        | 441                 |  |

| T2CLKCON | _           | _               | _                              | _      |       | CS<       | <3:0>   |        | 440                 |  |

| T2RST    | —           | —               | —                              |        |       | RSEL<4:0> |         |        | 443                 |  |

| T2HLT    | PSYNC       | CKPOL           | CKSYNC                         | —      |       | 442       |         |        |                     |  |

| PR4      | Timer4 Mod  | ule Period Re   | gister                         |        |       | 425*      |         |        |                     |  |

| TMR4     | Holding Reg | ister for the 8 | -bit TMR4 Re                   | gister |       |           |         |        | 425*                |  |

| T4CON    | ON          |                 | CKPS<2:0>                      |        |       | OUTP      | S<3:0>  |        | 441                 |  |

| T4CLKCON | —           | —               | —                              | _      | —     |           | CS<3:0> |        | 440                 |  |

| T4RST    | —           | _               | _                              |        |       | RSEL<4:0> |         |        | 443                 |  |

| T4HLT    | PSYNC       | CKPOL           | CKSYNC                         | —      |       | MODE      | E<3:0>  |        | 442                 |  |

| PR6      | Timer6 Mod  | ule Period Re   | Period Register                |        |       |           |         |        | 425*                |  |

| TMR6     | Holding Reg | ister for the 8 | er for the 8-bit TMR6 Register |        |       |           |         | 425*   |                     |  |

| T6CON    | ON          |                 | CKPS<2:0> OUTPS<3:0>           |        |       |           |         | 441    |                     |  |

| T6CLKCON | —           | —               | —                              | —      | —     |           | CS<2:0> |        | 440                 |  |

| T6RST    | —           | _               | _                              |        |       | RSEL<4:0> |         |        | 443                 |  |

| T6HLT    | PSYNC       | CKPOL           | CKSYNC                         | —      |       | MOD       | E<3:0>  |        | 442                 |  |

### TABLE 29-3: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Timer2 module. \* Page provides register information.

### 30.3.4 TIMER2 TIMER RESOURCE

This device has a newer version of the TMR2 module that has many new modes, which allow for greater customization and control of the PWM signals than on older parts. Refer to Section 29.5, Operation Examples for examples of PWM signal generation using the different modes of Timer2. The CCP operation requires that the timer used as the PWM time base has the FOSC/4 clock source selected

### 30.3.5 PWM PERIOD

The PWM period is specified by the PR2/4/6 register of Timer2/4/6. The PWM period can be calculated using the formula of Equation 30-1.

### EQUATION 30-1: PWM PERIOD

$$PWM Period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$$

$$(TMR2 Prescale Value)$$

Note 1: Tosc = 1/Fosc

When TMR2/4/6 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2/4/6 is cleared

- The CCPx pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is transferred from the CCPRxL/H register pair into a 10-bit buffer.

| Note: | The Timer postscaler (see Section 29.4 |

|-------|----------------------------------------|

|       | "Timer2 Interrupt") is not used in the |

|       | determination of the PWM frequency.    |

### 30.3.6 PWM DUTY CYCLE

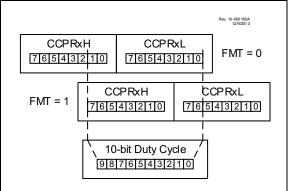

The PWM duty cycle is specified by writing a 10-bit value to the CCPRxH:CCPRxL register pair. The alignment of the 10-bit value is determined by the CCPRxFMT bit of the CCPxCON register (see Figure 30-5). The CCPRxH:CCPRxL register pair can be written to at any time; however the duty cycle value is not latched into the 10-bit buffer until after a match between PR2 and TMR2.

Equation 30-2 is used to calculate the PWM pulse width.

Equation 30-3 is used to calculate the PWM duty cycle ratio.

#### FIGURE 30-5: PWM 10-BIT ALIGNMENT

### EQUATION 30-2: PULSE WIDTH

Pulse Width = (CCPRxH:CCPRxL register pair) •

TOSC • (TMR2 Prescale Value)

### EQUATION 30-3: DUTY CYCLE RATIO

Duty Cycle Ratio =

$$\frac{(CCPRxH:CCPRxL register pair)}{4(PR2 + 1)}$$

CCPRxH:CCPRxL register pair are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (FOSC), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH:CCPRxL register pair, then the CCPx pin is cleared (see Figure 30-4).

### 30.3.7 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 30-4.

### EQUATION 30-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2 + 1)]}{\log(2)}$$

bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

#### TABLE 30-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

### TABLE 30-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

### 30.3.8 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

### 30.3.9 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 6.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional details.

#### 30.3.10 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

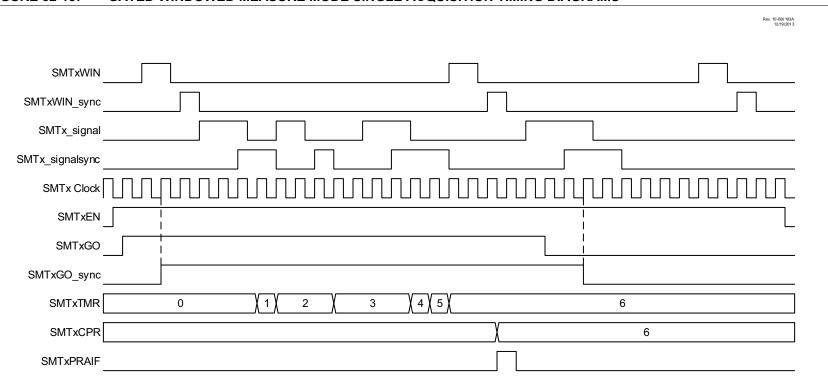

### FIGURE 32-13: GATED WINDOWED MEASURE MODE SINGLE ACQUISITION TIMING DIAGRAMS

PIC16(L)F18855/75

### **37.3 DC Characteristics**

### TABLE 37-1:SUPPLY VOLTAGE

| PIC16LF       | PIC16LF18855/75 |                                |            | Standard Operating Conditions (unless otherwise stated) |            |        |                                      |  |  |

|---------------|-----------------|--------------------------------|------------|---------------------------------------------------------|------------|--------|--------------------------------------|--|--|

| PIC16F1       | 18855/75        |                                |            |                                                         |            |        |                                      |  |  |

| Param.<br>No. | Sym.            | Characteristic                 | Min.       | Typ.†                                                   | Max.       | Units  | Conditions                           |  |  |

| Supply '      | Voltage         |                                |            |                                                         |            |        | ·                                    |  |  |

| D002          | Vdd             |                                | 1.8<br>2.5 | -                                                       | 3.6<br>3.6 | V<br>V | Fosc ≤ 16 MHz<br>Fosc > 16 MHz       |  |  |

| D002          | Vdd             |                                | 2.3<br>2.5 | _                                                       | 5.5<br>5.5 | V<br>V | Fosc ≤ 16 MHz<br>Fosc ≥ 16 MHz       |  |  |

| RAM Da        | ita Retent      | tion <sup>(1)</sup>            |            |                                                         |            |        |                                      |  |  |

| D003          | Vdr             |                                | 1.5        | —                                                       |            | V      | Device in Sleep mode                 |  |  |

| D003          | Vdr             |                                | 1.5        | —                                                       | _          | V      | Device in Sleep mode                 |  |  |

| Power-c       | on Reset        | Release Voltage <sup>(2)</sup> |            |                                                         |            |        |                                      |  |  |

| D004          | VPOR            |                                |            | 1.6                                                     |            | V      | BOR or LPBOR disabled <sup>(3)</sup> |  |  |

| D004          | VPOR            |                                | _          | 1.6                                                     |            | V      | BOR or LPBOR disabled <sup>(3)</sup> |  |  |

| Power-c       | on Reset        | Rearm Voltage <sup>(2)</sup>   |            |                                                         |            |        |                                      |  |  |

| D005          | VPORR           |                                |            | 0.8                                                     |            | V      | BOR or LPBOR disabled <sup>(3)</sup> |  |  |

| D005          | VPORR           |                                |            | 1.2                                                     |            | V      | BOR or LPBOR disabled <sup>(3)</sup> |  |  |

| VDD Ris       | e Rate to       | ensure internal Power-on F     | Reset sig  | gnal <sup>(2)</sup>                                     |            |        | •                                    |  |  |

| D006          | SVDD            |                                | 0.05       | —                                                       |            | V/ms   | BOR or LPBOR disabled <sup>(3)</sup> |  |  |

| D006          | SVDD            |                                | 0.05       | —                                                       |            | V/ms   | BOR or LPBOR disabled <sup>(3)</sup> |  |  |

† Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

2: See Figure 37-3, POR and POR REARM with Slow Rising VDD.

3: Please see Table 37-11 for BOR and LPBOR trip point information.

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

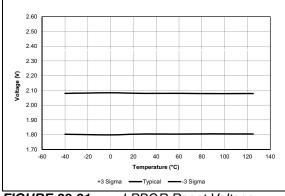

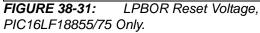

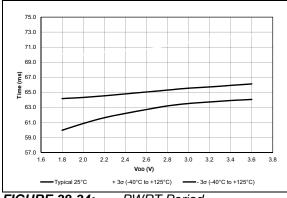

FIGURE 38-32: LPBOR Reset Hysteresis, PIC16LF18855/75 Only.

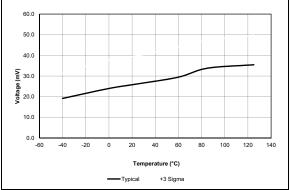

FIGURE 38-33: PWRT Period, PIC16F18855/75 Only.

FIGURE 38-34: PWRT Period, PIC16LF18855/75 Only.

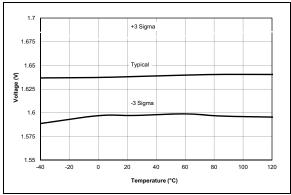

FIGURE 38-35: POR Release Voltage.

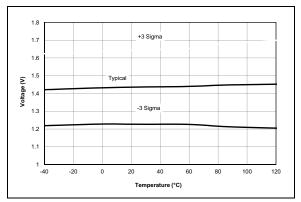

FIGURE 38-36: POR Rearm Voltage, VREGPM1 = 0, PIC16F18855/75 Only.

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.                 | T T T                                                                                                     | Examples:       a)     PIC16F18855- E/SP       Extended temperature                                                                                                                                                                                                                            |

|--------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device:                  | PIC16F18855; PIC16LF18855;<br>PIC16F18875; PIC16LF18875                                                   | SPDIP package<br>b) PIC16F18875- I/P<br>Industrial temperature<br>PDIP package                                                                                                                                                                                                                 |

| Tape and Reel<br>Option: | Blank = Standard packaging (tube or tray)<br>T = Tape and Reel <sup>(1)</sup>                             |                                                                                                                                                                                                                                                                                                |

| Temperature<br>Range:    | I = $-40^{\circ}$ C to $+85^{\circ}$ C (Industrial)<br>E = $-40^{\circ}$ C to $+125^{\circ}$ C (Extended) |                                                                                                                                                                                                                                                                                                |

| Package: <sup>(2)</sup>  | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                      | Note 1: Tape and Reel identifier only appears in<br>the catalog part number description. This<br>identifier is used for ordering purposes and<br>is not printed on the device package.<br>Check with your Microchip Sales Office<br>for package availability with the Tape and<br>Reel option. |

| Pattern:                 | QTP, SQTP, Code or Special Requirements (blank otherwise)                                                 | 2: Small form-factor packaging options may<br>be available. Please check<br>www.microchip.com/packaging for<br>small-form factor package availability, or<br>contact your local Sales Office.                                                                                                  |