#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | AVR                                                                        |

| Core Size                  | 8/16-Bit                                                                   |

| Speed                      | 32MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                      |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 78                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                                |

| Data Converters            | A/D 16x12b; D/A 4x12b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-TQFP                                                                   |

| Supplier Device Package    | 100-TQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega128a1u-an |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 11. Power Management and Sleep Modes

## 11.1 Features

- Power management for adjusting power consumption and functions

- Five sleep modes

- Idle

- Power down

- Power save

- Standby

- Extended standby

- Power reduction register to disable clock and turn off unused peripherals in active and idle modes

## 11.2 Overview

Various sleep modes and clock gating are provided in order to tailor power consumption to application requirements. This enables the Atmel AVR XMEGA microcontroller to stop unused modules to save power.

All sleep modes are available and can be entered from active mode. In active mode, the CPU is executing application code. When the device enters sleep mode, program execution is stopped and interrupts or a reset is used to wake the device again. The application code decides which sleep mode to enter and when. Interrupts from enabled peripherals and all enabled reset sources can restore the microcontroller from sleep to active mode.

In addition, power reduction registers provide a method to stop the clock to individual peripherals from software. When this is done, the current state of the peripheral is frozen, and there is no power consumption from that peripheral. This reduces the power consumption in active mode and idle sleep modes and enables much more fine-tuned power management than sleep modes alone.

## 11.3 Sleep Modes

Sleep modes are used to shut down modules and clock domains in the microcontroller in order to save power. XMEGA microcontrollers have five different sleep modes tuned to match the typical functional stages during application execution. A dedicated sleep instruction (SLEEP) is available to enter sleep mode. Interrupts are used to wake the device from sleep, and the available interrupt wake-up sources are dependent on the configured sleep mode. When an enabled interrupt occurs, the device will wake up and execute the interrupt service routine before continuing normal program execution from the first instruction after the SLEEP instruction. If other, higher priority interrupts are pending when the wake-up occurs, their interrupt service routines will be executed according to their priority before the interrupt service routine for the wake-up interrupt is executed. After wake-up, the CPU is halted for four cycles before execution starts.

The content of the register file, SRAM and registers are kept during sleep. If a reset occurs during sleep, the device will reset, start up, and execute from the reset vector.

## 11.3.1 Idle Mode

In idle mode the CPU and nonvolatile memory are stopped (note that any ongoing programming will be completed), but all peripherals, including the interrupt controller, event system and DMA controller are kept running. Any enabled interrupt will wake the device.

## 11.3.2 Power-down Mode

In power-down mode, all clocks, including the real-time counter clock source, are stopped. This allows operation only of asynchronous modules that do not require a running clock. The only interrupts that can wake up the MCU are the twowire interface address match interrupt, asynchronous port interrupts, and the USB resume interrupt.

# 18. AWeX – Advanced Waveform Extension

## 18.1 Features

- Waveform output with complementary output from each compare channel

- Four dead-time insertion (DTI) units

- 8-bit resolution

- Separate high and low side dead-time setting

- Double buffered dead time

- Optionally halts timer during dead-time insertion

- Pattern generation unit creating synchronised bit pattern across the port pins

- Double buffered pattern generation

- Optional distribution of one compare channel output across the port pins

- Event controlled fault protection for instant and predictable fault triggering

## 18.2 Overview

The advanced waveform extension (AWeX) provides extra functions to the timer/counter in waveform generation (WG) modes. It is primarily intended for use with different types of motor control and other power control applications. It enables low- and high side output with dead-time insertion and fault protection for disabling and shutting down external drivers. It can also generate a synchronized bit pattern across the port pins.

Each of the waveform generator outputs from the Timer/Counter 0 are split into a complimentary pair of outputs when any AWeX features are enabled. These output pairs go through a dead-time insertion (DTI) unit that generates the non-inverted low side (LS) and inverted high side (HS) of the WG output with dead-time insertion between LS and HS switching. The DTI output will override the normal port value according to the port override setting.

The pattern generation unit can be used to generate a synchronized bit pattern on the port it is connected to. In addition, the WG output from compare channel A can be distributed to and override all the port pins. When the pattern generator unit is enabled, the DTI unit is bypassed.

The fault protection unit is connected to the event system, enabling any event to trigger a fault condition that will disable the AWeX output. The event system ensures predictable and instant fault reaction, and gives great flexibility in the selection of fault triggers.

The AWeX is available for TCC0 and TCE0. The notation of these are AWEXC and AWEXE.

#### Table 33-3. Port C - alternate functions.

| PORT C | PIN# | INTERRUPT  | TCC0 <sup>(1)(2)</sup> | AWEXC  | TCC1 | USARTC0 <sup>(3)</sup> | USARTC1 | SPIC <sup>(4)</sup> | TWIC | CLOCKOUT <sup>(5)</sup> | EVENTOUT <sup>(6)</sup> |

|--------|------|------------|------------------------|--------|------|------------------------|---------|---------------------|------|-------------------------|-------------------------|

| GND    | 13   |            |                        |        |      |                        |         |                     |      |                         |                         |

| vcc    | 14   |            |                        |        |      |                        |         |                     |      |                         |                         |

| PC0    | 15   | SYNC       | OC0A                   | OC0ALS |      |                        |         |                     | SDA  |                         |                         |

| PC1    | 16   | SYNC       | OC0B                   | OC0AHS |      | XCK0                   |         |                     | SCL  |                         |                         |

| PC2    | 17   | SYNC/ASYNC | OC0C                   | OCOBLS |      | RXD0                   |         |                     |      |                         |                         |

| PC3    | 18   | SYNC       | OC0D                   | OC0BHS |      | TXD0                   |         |                     |      |                         |                         |

| PC4    | 19   | SYNC       |                        | OC0CLS | OC1A |                        |         | SS                  |      |                         |                         |

| PC5    | 20   | SYNC       |                        | OC0CHS | OC1B |                        | XCK1    | MOSI                |      |                         |                         |

| PC6    | 21   | SYNC       |                        | OC0DLS |      |                        | RXD1    | MISO                |      | clk <sub>RTC</sub>      |                         |

| PC7    | 22   | SYNC       |                        | OC0DHS |      |                        | TXD1    | SCK                 |      | clk <sub>PER</sub>      | EVOUT                   |

Notes: 1. Pin mapping of all TC0 can optionally be moved to high nibble of port. Refer to Pin Remap register in I/O Ports in the XMEGA AU Manual.

2. If TC0 is configured as TC2 all eight pins can be used for PWM output. Refer to Pin Remap register in I/O Ports in the XMEGA AU Manual.

3. Pin mapping of all USART0 can optionally be moved to high nibble of port. Refer to Pin Remap register in I/O Ports in the XMEGA AU Manual..

4. Pins MOSI and SCK for all SPI can optionally be swapped.Refer to Pin Remap register in I/O Ports in the XMEGA AU Manual.

5. CLKOUT can optionally be moved between port C, D and E and between pin 4 and 7. Refer to CLKEVOUT register in I/O port configuration in the XMEGA AU Manual.

6. EVOUT can optionally be moved between port C, D and E and between pin 4 and 7. Refer to CLKEVOUT register in I/O port configuration in the XMEGA AU Manual.

## Table 33-4. Port D - alternate functions.

| PORT D | PIN# | INTERRUPT      | TCD0 | TCD1 | USBD | USARTD0 | USARTD1 | SPID | TWID | CLOCKOUT           | EVENTOUT |

|--------|------|----------------|------|------|------|---------|---------|------|------|--------------------|----------|

| GND    | 23   |                |      |      |      |         |         |      |      |                    |          |

| vcc    | 24   |                |      |      |      |         |         |      |      |                    |          |

| PD0    | 25   | SYNC           | OC0A |      |      |         |         |      | SDA  |                    |          |

| PD1    | 26   | SYNC           | OC0B |      |      | XCK0    |         |      | SCL  |                    |          |

| PD2    | 27   | SYNC/ASYN<br>C | OC0C |      |      | RXD0    |         |      |      |                    |          |

| PD3    | 28   | SYNC           | OC0D |      |      | TXD0    |         |      |      |                    |          |

| PD4    | 29   | SYNC           |      | OC1A |      |         |         | SS   |      |                    |          |

| PD5    | 30   | SYNC           |      | OC1B |      |         | XCK1    | MOSI |      |                    |          |

| PD6    | 31   | SYNC           |      |      | D-   |         | RXD1    | MISO |      |                    |          |

| PD7    | 32   | SYNC           |      |      | D+   |         | TXD1    | SCK  |      | clk <sub>PER</sub> | EVOUT    |

## Table 33-5. Port E - alternate functions.

| PORT E | PIN # | INTERRUPT | TCE0 | AWEXE  | TCE1 | USARTE0 | USARTE1 | SPIE | TWIE | CLOCKOUT | EVENTOUT |

|--------|-------|-----------|------|--------|------|---------|---------|------|------|----------|----------|

| GND    | 33    |           |      |        |      |         |         |      |      |          |          |

| vcc    | 34    |           |      |        |      |         |         |      |      |          |          |

| PE0    | 35    | SYNC      | OC0A | OC0ALS |      |         |         |      | SDA  |          |          |

| PE1    | 36    | SYNC      | OC0B | OC0AHS |      | XCK0    |         |      | SCL  |          |          |

| PORT J | PIN # | INTERRUPT  | SDRAM 3P | SRAM ALE1 | SRAM ALE12 | LPC3 ALE1 | LPC2 ALE1 | LPC2 ALE12 |

|--------|-------|------------|----------|-----------|------------|-----------|-----------|------------|

| GND    | 63    |            |          |           |            |           |           |            |

| VCC    | 64    |            |          |           |            |           |           |            |

| PJ0    | 65    | SYNC       | D0       | D0        | D0         | D0/A0     | D0/A0     | D0/A0/A8   |

| PJ1    | 66    | SYNC       | D1       | D1        | D1         | D1/A1     | D1/A1     | D1/A1/A9   |

| PJ2    | 67    | SYNC/ASYNC | D2       | D2        | D2         | D2/A2     | D2/A2     | D2/A2/A10  |

| PJ3    | 68    | SYNC       | D3       | D3        | D3         | D3/A3     | D3/A3     | D3/A3/A11  |

| PJ4    | 69    | SYNC       | A8       | D4        | D4         | D4/A4     | D4/A4     | D4/A4/A12  |

| PJ5    | 70    | SYNC       | A9       | D5        | D5         | D5/A5     | D5/A5     | D5/A5/A13  |

| PJ6    | 71    | SYNC       | A10      | D6        | D6         | D6/A6     | D6/A6     | D6/A6/A14  |

| PJ7    | 72    | SYNC       | A11      | D7        | D7         | D7/A7     | D7/A7     | D7/A7/A15  |

#### Table 33-8. Port J - alternate functions.

## Table 33-9. Port K - alternate functions.

| PORT K | PIN # | INTERRUPT  | SDRAM 3P | SRAM ALE1 | SRAM ALE2  | LPC3 ALE1 |

|--------|-------|------------|----------|-----------|------------|-----------|

| GND    | 73    |            |          |           |            |           |

| vcc    | 74    |            |          |           |            |           |

| PK0    | 75    | SYNC       | A0       | A0/A8     | A0/A8/A16  | A8        |

| PK1    | 76    | SYNC       | A1       | A1/A9     | A1/A9/A17  | A9        |

| PK2    | 77    | SYNC/ASYNC | A2       | A2/A10    | A2/A10/A18 | A10       |

| PK3    | 78    | SYNC       | A3       | A3/A11    | A3/A11/A19 | A11       |

| PK4    | 79    | SYNC       | A4       | A4/A12    | A4/A12/A20 | A12       |

| PK5    | 80    | SYNC       | A5       | A5/A13    | A5/A13/A21 | A13       |

| PK6    | 81    | SYNC       | A6       | A6/A14    | A6/A14/A22 | A14       |

| PK7    | 82    | SYNC       | A7       | A7/A15    | A7/A15/A23 | A15       |

Table 33-10. Port Q - alternate functions.

| PORT Q | PIN # | INTERRUPT  | TOSC  |

|--------|-------|------------|-------|

| VCC    | 83    |            |       |

| GND    | 84    |            |       |

| PQ0    | 85    | SYNC       | TOSC1 |

| PQ1    | 86    | SYNC       | TOSC2 |

| PQ2    | 87    | SYNC/ASYNC |       |

| PQ3    | 88    | SYNC       |       |

# 35. Instruction Set Summary

| Mnemonics | Operands | Description                              | Opera                                                 | ation  |                                          | Flags       | #Clocks   |

|-----------|----------|------------------------------------------|-------------------------------------------------------|--------|------------------------------------------|-------------|-----------|

|           |          | Arithmetic                               | and Logic Instructions                                |        |                                          |             | 1         |

| ADD       | Rd, Rr   | Add without Carry                        | Rd                                                    | ~      | Rd + Rr                                  | Z,C,N,V,S,H | 1         |

| ADC       | Rd, Rr   | Add with Carry                           | Rd                                                    | ←      | Rd + Rr + C                              | Z,C,N,V,S,H | 1         |

| ADIW      | Rd, K    | Add Immediate to Word                    | Rd                                                    | ←      | Rd + 1:Rd + K                            | Z,C,N,V,S   | 2         |

| SUB       | Rd, Rr   | Subtract without Carry                   | Rd                                                    | ~      | Rd - Rr                                  | Z,C,N,V,S,H | 1         |

| SUBI      | Rd, K    | Subtract Immediate                       | Rd                                                    | ←      | Rd - K                                   | Z,C,N,V,S,H | 1         |

| SBC       | Rd, Rr   | Subtract with Carry                      | Rd                                                    | ~      | Rd - Rr - C                              | Z,C,N,V,S,H | 1         |

| SBCI      | Rd, K    | Subtract Immediate with Carry            | Rd                                                    | ←      | Rd - K - C                               | Z,C,N,V,S,H | 1         |

| SBIW      | Rd, K    | Subtract Immediate from Word             | Rd + 1:Rd                                             | ~      | Rd + 1:Rd - K                            | Z,C,N,V,S   | 2         |

| AND       | Rd, Rr   | Logical AND                              | Rd                                                    | ←      | Rd • Rr                                  | Z,N,V,S     | 1         |

| ANDI      | Rd, K    | Logical AND with Immediate               | Rd                                                    | ~      | Rd • K                                   | Z,N,V,S     | 1         |

| OR        | Rd, Rr   | Logical OR                               | Rd                                                    | ←      | Rd v Rr                                  | Z,N,V,S     | 1         |

| ORI       | Rd, K    | Logical OR with Immediate                | Rd                                                    | ~      | Rd v K                                   | Z,N,V,S     | 1         |

| EOR       | Rd, Rr   | Exclusive OR                             | Rd                                                    | ←      | Rd ⊕ Rr                                  | Z,N,V,S     | 1         |

| СОМ       | Rd       | One's Complement                         | Rd                                                    | ~      | \$FF - Rd                                | Z,C,N,V,S   | 1         |

| NEG       | Rd       | Two's Complement                         | Rd                                                    | ←      | \$00 - Rd                                | Z,C,N,V,S,H | 1         |

| SBR       | Rd,K     | Set Bit(s) in Register                   | Rd                                                    | ←      | Rd v K                                   | Z,N,V,S     | 1         |

| CBR       | Rd,K     | Clear Bit(s) in Register                 | Rd                                                    | ←      | Rd • (\$FFh - K)                         | Z,N,V,S     | 1         |

| INC       | Rd       | Increment                                | Rd                                                    | ←      | Rd + 1                                   | Z,N,V,S     | 1         |

| DEC       | Rd       | Decrement                                | Rd                                                    | ←      | Rd - 1                                   | Z,N,V,S     | 1         |

| TST       | Rd       | Test for Zero or Minus                   | Rd                                                    | ←      | Rd • Rd                                  | Z,N,V,S     | 1         |

| CLR       | Rd       | Clear Register                           | Rd                                                    | ←      | $Rd \oplus Rd$                           | Z,N,V,S     | 1         |

| SER       | Rd       | Set Register                             | Rd                                                    | ←      | \$FF                                     | None        | 1         |

| MUL       | Rd,Rr    | Multiply Unsigned                        | R1:R0                                                 | ←      | Rd x Rr (UU)                             | Z,C         | 2         |

| MULS      | Rd,Rr    | Multiply Signed                          | R1:R0                                                 | ~      | Rd x Rr (SS)                             | Z,C         | 2         |

| MULSU     | Rd,Rr    | Multiply Signed with Unsigned            | R1:R0                                                 | ←      | Rd x Rr (SU)                             | Z,C         | 2         |

| FMUL      | Rd,Rr    | Fractional Multiply Unsigned             | R1:R0                                                 | ←      | Rd x Rr<<1 (UU)                          | Z,C         | 2         |

| FMULS     | Rd,Rr    | Fractional Multiply Signed               | R1:R0                                                 | ←      | Rd x Rr<<1 (SS)                          | Z,C         | 2         |

| FMULSU    | Rd,Rr    | Fractional Multiply Signed with Unsigned | R1:R0                                                 | ←      | Rd x Rr<<1 (SU)                          | Z,C         | 2         |

| DES       | К        | Data Encryption                          | if (H = 0) then R15:R0<br>else if (H = 1) then R15:R0 | ←<br>← | Encrypt(R15:R0, K)<br>Decrypt(R15:R0, K) |             | 1/2       |

|           |          | Bra                                      | nch instructions                                      |        |                                          |             |           |

| RJMP      | k        | Relative Jump                            | PC                                                    | ←      | PC + k + 1                               | None        | 2         |

| IJMP      |          | Indirect Jump to (Z)                     | PC(15:0)<br>PC(21:16)                                 | ←<br>← | Z,<br>0                                  | None        | 2         |

| EIJMP     |          | Extended Indirect Jump to (Z)            | PC(15:0)<br>PC(21:16)                                 | ←<br>← | Z,<br>EIND                               | None        | 2         |

| JMP       | k        | Jump                                     | PC                                                    | ←      | k                                        | None        | 3         |

| RCALL     | k        | Relative Call Subroutine                 | PC                                                    | ←      | PC + k + 1                               | None        | 2 / 3 (1) |

| Table 37-5. | Current consum | ption for modules | and peripherals. |

|-------------|----------------|-------------------|------------------|

|-------------|----------------|-------------------|------------------|

| Symbol          | Parameter                 | Condition <sup>(1)</sup>              |                                  | Min. | Тур. | Max. | Units |

|-----------------|---------------------------|---------------------------------------|----------------------------------|------|------|------|-------|

|                 | ULP oscillator            |                                       |                                  |      | 1.0  |      |       |

|                 | 32.768kHz int. oscillator |                                       |                                  |      | 27   |      |       |

|                 | 2MHz int. oscillator      |                                       |                                  |      | 85   |      |       |

|                 |                           | DFLL enabled with                     | 32.768kHz int. osc. as reference |      | 120  |      |       |

|                 | 32MHz int. oscillator     |                                       |                                  |      | 310  |      |       |

|                 |                           | DFLL enabled with                     |                                  | 560  |      | μA   |       |

|                 | Watchdog timer            |                                       |                                  |      | 1.0  |      |       |

|                 | BOD                       | Continuous mode                       |                                  |      | 126  |      |       |

|                 | 666                       | Sampled mode, in                      | cludes ULP oscillator            |      | 1.2  |      |       |

|                 | Internal 1.0V reference   |                                       |                                  |      | 89   |      |       |

|                 | Temperature sensor        |                                       |                                  |      | 83   |      |       |

| I <sub>CC</sub> |                           |                                       |                                  |      | 3.0  |      |       |

|                 | ADC                       | 250ksps<br>V <sub>REF</sub> = Ext ref | CURRLIMIT = LOW                  |      | 2.6  |      | mA    |

|                 |                           |                                       | CURRLIMIT = MEDIUM               |      | 2.1  |      |       |

|                 |                           |                                       | CURRLIMIT = HIGH                 |      | 1.6  |      |       |

|                 | DAC                       | 250ksps<br>V <sub>REF</sub> = Ext ref | Normal mode                      |      | 1.9  |      |       |

|                 | DAC                       | No load                               | Low Power mode                   |      | 1.1  |      |       |

|                 | AC                        | High speed mode                       |                                  |      | 324  |      |       |

|                 | AC                        | Low power mode                        |                                  |      | 122  |      |       |

|                 | DMA                       | 615KBps between                       | I/O registers and SRAM           |      | 140  |      | μA    |

|                 | Timer/counter             |                                       |                                  |      | 20   |      |       |

|                 | USART                     | Rx and Tx enabled                     | d, 9600 BAUD                     |      | 4.0  |      |       |

|                 | Flash memory and EEPRC    | M programming                         |                                  |      | 4.0  | 8.0  | mA    |

Note: 1. All parameters measured as the difference in current consumption between module enabled and disabled. All data at V<sub>CC</sub> = 3.0V, Clk<sub>SYS</sub> = 1MHz external clock without prescaling, T = 25°C unless other conditions are given.

## 37.1.11 External Reset Characteristics

## Table 37-18. External reset characteristics.

| Symbol           | Parameter                                  | Condition                    | Min. | Тур.                 | Max. | Units |

|------------------|--------------------------------------------|------------------------------|------|----------------------|------|-------|

| t <sub>EXT</sub> | Minimum reset pulse width                  |                              |      | 86                   | 1000 | ns    |

| Popot            | Posst threshold voltage $(V_{ij})$         | V <sub>CC</sub> = 2.7 - 3.6V |      | 0.60*V <sub>CC</sub> |      |       |

| M                | Reset threshold voltage (V <sub>IH</sub> ) | V <sub>CC</sub> = 1.6 - 2.7V |      | 0.60*V <sub>CC</sub> |      | V     |

| V <sub>RST</sub> |                                            | V <sub>CC</sub> = 2.7 - 3.6V |      | 0.40*V <sub>CC</sub> |      | V     |

|                  | Reset threshold voltage (V <sub>IL</sub> ) | V <sub>CC</sub> = 1.6 - 2.7V |      | 0.40*V <sub>CC</sub> |      |       |

## 37.1.12 Power-on Reset Characteristics

#### Table 37-19. Power-on reset characteristics.

| Symbol                                                                        | Parameter                                     | Condition                         | Min. | Тур. | Max. | Units |

|-------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------|------|------|------|-------|

| V <sub>POT-</sub> <sup>(1)</sup> POR threshold voltage falling V <sub>C</sub> | $V_{\rm CC}$ falls faster than 1V/ms          | 0.4                               | 1.0  |      |      |       |

|                                                                               | POR threshold voltage failing V <sub>CC</sub> | $V_{CC}$ falls at 1V/ms or slower | 0.8  | 1.0  |      | V     |

| V <sub>POT+</sub>                                                             | POR threshold voltage rising $\rm V_{\rm CC}$ |                                   |      | 1.3  | 1.59 |       |

Note: 1.  $V_{POT-}$  values are only valid when BOD is disabled. When BOD is enabled  $V_{POT-} = V_{POT+}$ .

## 37.1.13 Flash and EEPROM Memory Characteristics

## Table 37-20. Endurance and data retention.

| Symbol | Parameter | Condition          |       | Min. | Тур. | Max. | Units |

|--------|-----------|--------------------|-------|------|------|------|-------|

|        | Flash     | Write/Erase cycles | 25°C  | 10K  |      |      |       |

|        |           |                    | 85°C  | 10K  |      |      | Cycle |

|        |           |                    | 105°C | 2K   |      |      |       |

|        |           | Data retention     | 25°C  | 100  |      |      | Year  |

|        |           |                    | 85°C  | 25   |      |      |       |

|        |           |                    | 105°C | 10   |      |      |       |

|        |           | Write/Erase cycles | 25°C  | 100K |      |      | Cycle |

|        |           |                    | 85°C  | 100K |      |      |       |

|        |           |                    | 105°C | 30K  |      |      |       |

|        |           |                    | 25°C  | 100  |      |      |       |

|        |           | Data retention     | 85°C  | 25   |      |      | Year  |

|        |           |                    | 105°C | 10   |      |      |       |

## 37.2.3 Current consumption

|  | Table 37-38. | Current consum | ption for Active | mode and sleep | o modes. |

|--|--------------|----------------|------------------|----------------|----------|

|--|--------------|----------------|------------------|----------------|----------|

| Symbol          | Parameter                                  | Condition                                          |                        | Min. | Тур. | Max. | Units |

|-----------------|--------------------------------------------|----------------------------------------------------|------------------------|------|------|------|-------|

|                 |                                            |                                                    | V <sub>CC</sub> = 1.8V |      | 50   |      |       |

|                 |                                            | 32kHz, Ext. Clk                                    | V <sub>CC</sub> = 3.0V |      | 95   |      | μA    |

| ldle p          |                                            |                                                    | V <sub>CC</sub> = 1.8V |      | 350  |      |       |

|                 | Active power<br>consumption <sup>(1)</sup> | 1MHz, Ext. Clk                                     | V <sub>CC</sub> = 3.0V |      | 700  |      |       |

|                 |                                            |                                                    | V <sub>CC</sub> = 1.8V |      | 650  | 700  |       |

|                 |                                            | 2MHz, Ext. Clk                                     | y = 2.0y               |      | 1.2  | 1.4  | m (   |

|                 |                                            | 32MHz, Ext. Clk                                    | V <sub>CC</sub> = 3.0V |      | 15   | 20   | mA    |

|                 |                                            |                                                    | V <sub>CC</sub> = 1.8V |      | 3.5  |      |       |

|                 |                                            | 32kHz, Ext. Clk                                    | V <sub>CC</sub> = 3.0V |      | 6.4  |      | _     |

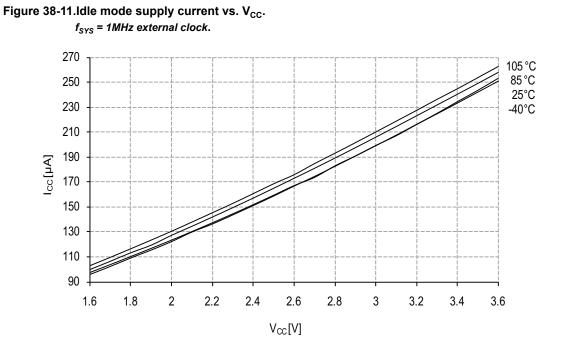

|                 |                                            |                                                    | V <sub>CC</sub> = 1.8V |      | 109  |      |       |

|                 | Idle power<br>consumption <sup>(1)</sup>   | 1MHz, Ext. Clk                                     | V <sub>CC</sub> = 3.0V |      | 200  |      | μA    |

|                 |                                            |                                                    | V <sub>CC</sub> = 1.8V |      | 290  | 380  |       |

|                 |                                            | 2MHz, Ext. Clk                                     | y = 2.0y               |      | 476  | 650  | _     |

|                 |                                            | 32MHz, Ext. Clk                                    | V <sub>CC</sub> = 3.0V |      | 6.6  | 9.2  | mA    |

| I <sub>CC</sub> | Power-down power<br>consumption            | T = 25°C                                           | V <sub>CC</sub> = 1.8V |      | 0.1  | 1.0  | μΑ    |

| -00             |                                            | T = 25°C                                           |                        |      | 0.1  | 1.0  |       |

|                 |                                            | T = 85°C                                           | V <sub>CC</sub> = 3.0V |      | 1.7  | 5.0  |       |

|                 |                                            | T = 105°C                                          |                        |      | 6.0  | 10   |       |

|                 |                                            | WDT and sampled BOD enabled,<br>T = $25^{\circ}$ C | V <sub>CC</sub> = 3.0V |      | 1.3  | 3.0  |       |

|                 |                                            | WDT and sampled BOD enabled, T = $85^{\circ}$ C    |                        |      | 3.1  | 10   |       |

|                 |                                            | WDT and sampled BOD enabled,<br>T = 105°C          | _                      |      | 7.0  | 12   |       |

|                 |                                            | RTC on ULP clock, WDT and                          | V <sub>CC</sub> = 1.8V |      | 1.2  |      |       |

|                 |                                            | sampled BOD enabled, $T = 25^{\circ}C$             | V <sub>CC</sub> = 3.0V |      | 1.3  |      |       |

|                 | Power-save power                           | RTC on 1.024kHz low power                          | V <sub>CC</sub> = 1.8V |      | 0.7  | 2.0  |       |

|                 | consumption <sup>(2)</sup>                 | 32.768kHz TOSC, T = 25°C                           | V <sub>CC</sub> = 3.0V |      | 0.8  | 2.0  |       |

|                 |                                            | RTC from low power 32.768kHz                       | V <sub>CC</sub> = 1.8V |      | 0.9  | 3.0  |       |

|                 |                                            | TOSC, $T = 25^{\circ}C$                            | V <sub>CC</sub> = 3.0V |      | 1.0  | 3.0  |       |

|                 | Reset power consumption                    | Current through RESET pin subtracted               | V <sub>CC</sub> = 3.0V |      | 914  |      |       |

Notes: 1. All Power Reduction Registers set.

2. Maximum limits are based on characterization, and not tested in production.

## 37.2.11 External Reset Characteristics

#### Table 37-52. External reset characteristics.

| Symbol           | Parameter                                                                                | Condition                    | Min. | Тур.                 | Max. | Units |

|------------------|------------------------------------------------------------------------------------------|------------------------------|------|----------------------|------|-------|

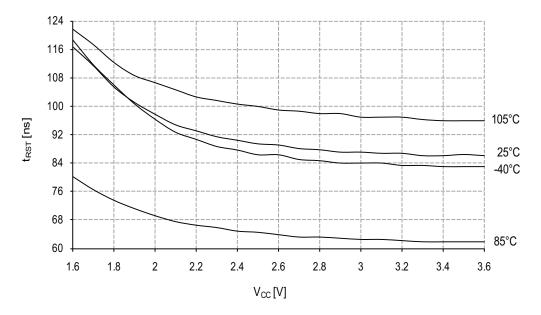

| t <sub>EXT</sub> | Minimum reset pulse width                                                                |                              |      | 86                   | 1000 | ns    |

|                  | Reset threshold voltage (V <sub>IH</sub> )<br>Reset threshold voltage (V <sub>IL</sub> ) | V <sub>CC</sub> = 2.7 - 3.6V |      | 0.60*V <sub>CC</sub> |      |       |

|                  |                                                                                          | V <sub>CC</sub> = 1.6 - 2.7V |      | 0.60*V <sub>CC</sub> |      | V     |

| V <sub>RST</sub> |                                                                                          | V <sub>CC</sub> = 2.7 - 3.6V |      | 0.40*V <sub>CC</sub> |      | v     |

|                  |                                                                                          | V <sub>CC</sub> = 1.6 - 2.7V |      | 0.40*V <sub>CC</sub> |      |       |

## 37.2.12 Power-on Reset Characteristics

#### Table 37-53. Power-on reset characteristics.

| Symbol                           | Parameter                                     | Condition                               | Min. | Тур. | Max. | Units |

|----------------------------------|-----------------------------------------------|-----------------------------------------|------|------|------|-------|

| V (1)                            | POR threshold voltage falling $V_{CC}$        | $V_{\text{CC}}$ falls faster than 1V/ms | 0.4  | 1.0  |      |       |

| V <sub>POT-</sub> <sup>(1)</sup> | FOR Intestion voltage failing V <sub>CC</sub> | $V_{CC}$ falls at 1V/ms or slower       | 0.8  | 1.0  |      | V     |

| V <sub>POT+</sub>                | POR threshold voltage rising $\rm V_{\rm CC}$ |                                         |      | 1.3  | 1.59 |       |

Note: 1.  $V_{POT-}$  values are only valid when BOD is disabled. When BOD is enabled  $V_{POT-} = V_{POT+}$ .

## 37.2.13 Flash and EEPROM Memory Characteristics

## Table 37-54. Endurance and data retention.

| Symbol | Parameter | Condition          |       | Min. | Тур. | Max. | Units |

|--------|-----------|--------------------|-------|------|------|------|-------|

|        | Flash     | Write/Erase cycles | 25°C  | 10K  |      |      |       |

|        |           |                    | 85°C  | 10K  |      |      | Cycle |

|        |           |                    | 105°C | 2K   |      |      |       |

|        |           | Data retention     | 25°C  | 100  |      |      | Year  |

|        |           |                    | 85°C  | 25   |      |      |       |

|        |           |                    | 105°C | 10   |      |      |       |

|        |           | Write/Erase cycles | 25°C  | 100K |      |      | Cycle |

|        |           |                    | 85°C  | 100K |      |      |       |

|        |           |                    | 105°C | 30K  |      |      |       |

|        |           |                    | 25°C  | 100  |      |      |       |

|        |           | Data retention     | 85°C  | 25   |      |      | Year  |

|        |           |                    | 105°C | 10   |      |      |       |

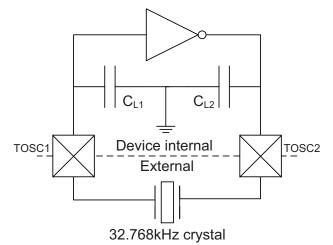

#### 37.2.14.8 External 32.768kHz crystal oscillator and TOSC characteristics

| Table 37-64. E | xternal 32.768kHz crystal oscillator and TOSC characteristics. |

|----------------|----------------------------------------------------------------|

|----------------|----------------------------------------------------------------|

| Symbol             | Parameter                          | Condition                                        | Min. | Тур. | Max. | Units |

|--------------------|------------------------------------|--------------------------------------------------|------|------|------|-------|

|                    | Recommended crystal                | Crystal load capacitance 6.5pF                   |      |      | 60   | ko    |

| ESR/R1             | equivalent series resistance (ESR) | Crystal load capacitance 9.0pF                   |      |      | 35   | kΩ    |

| C <sub>TOSC1</sub> | Parasitic capacitance TOSC1 pin    |                                                  |      | 4.0  |      |       |

| C <sub>TOSC2</sub> | Parasitic capacitance TOSC2 pin    |                                                  |      | 4.1  |      | pF    |

| CL                 | Parasitic capacitance load         |                                                  |      | 2.0  |      | -     |

|                    | Recommended safety factor          | Capacitive load matched to crystal specification | 3    |      |      |       |

Note: 1. See Figure 37-11 for definition.

## Figure 37-11.TOSC input capacitance.

The parasitic capacitance between the TOSC pins is  $C_{L1} + C_{L2}$  in series as seen from the crystal when oscillating without external capacitors.

Table 37-68. Two-wire interface characteristics.

| Symbol              | Parameter                                                      | Condition                                                         | Min.                                   | Тур. | Max.                      | Units |

|---------------------|----------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------|------|---------------------------|-------|

| V <sub>IH</sub>     | Input high voltage                                             |                                                                   | 0.7*V <sub>CC</sub>                    |      | V <sub>CC</sub> +0.5      |       |

| V <sub>IL</sub>     | Input low voltage                                              |                                                                   | -0.5                                   |      | 0.3*V <sub>CC</sub>       | V     |

| V <sub>hys</sub>    | Hysteresis of Schmitt trigger inputs                           |                                                                   | 0.05*V <sub>CC</sub> <sup>(1)</sup>    |      | 0                         | V     |

| V <sub>OL</sub>     | Output low voltage                                             | 3mA, sink current                                                 | 0                                      |      | 0.4                       |       |

| t <sub>r</sub>      | Rise time for both SDA and SCL                                 |                                                                   | 20+0.1C <sub>b</sub> <sup>(1)(2)</sup> |      | 0                         |       |

| t <sub>of</sub>     | Output fall time from $V_{\text{IHmin}}$ to $V_{\text{ILmax}}$ | $10pF < C_b < 400pF^{(2)}$                                        | 20+0.1C <sub>b</sub> <sup>(1)(2)</sup> |      | 300                       | ns    |

| t <sub>SP</sub>     | Spikes suppressed by input filter                              |                                                                   | 0                                      |      | 50                        |       |

| I <sub>I</sub>      | Input current for each I/O pin                                 | $0.1V_{CC} < V_{I} < 0.9V_{CC}$                                   | -10                                    |      | 10                        | μA    |

| CI                  | Capacitance for each I/O pin                                   |                                                                   |                                        |      | 10                        | pF    |

| f <sub>SCL</sub>    | SCL clock frequency                                            | f <sub>PER</sub> <sup>(3)</sup> >max(10f <sub>SCL</sub> , 250kHz) | 0                                      |      | 400                       | kHz   |

| R <sub>P</sub>      | Value of pull-up resistor                                      | f <sub>SCL</sub> ≤ 100kHz                                         | $\frac{V_{CC} - 0.4V}{3mA}$            |      | $\frac{100ns}{C_b}$ 300ns | Ω     |

|                     |                                                                | f <sub>SCL</sub> > 100kHz                                         |                                        |      | $\frac{500hs}{C_b}$       |       |

| t <sub>HD;STA</sub> | Hold time (repeated) START condition                           | f <sub>SCL</sub> ≤ 100kHz                                         | 4.0                                    |      |                           | μs    |

| 110,017             |                                                                | f <sub>SCL</sub> > 100kHz                                         | 0.6                                    |      |                           | _     |

| t <sub>LOW</sub>    | Low period of SCL clock                                        | $f_{SCL} \le 100 kHz$                                             | 4.7                                    |      |                           | _     |

| 2011                | ·                                                              | f <sub>SCL</sub> > 100kHz                                         | 1.3                                    |      |                           | _     |

| t <sub>HIGH</sub>   | High period of SCL clock                                       | $f_{SCL} \le 100 kHz$                                             | 4.0                                    |      |                           | _     |

| nigh                | <b>3 F 1 1 1 1 1 1 1 1 1 1</b>                                 | f <sub>SCL</sub> > 100kHz                                         | 0.6                                    |      |                           | μs    |

| t <sub>su;sta</sub> | Set-up time for a repeated START                               | $f_{SCL} \leq 100 kHz$                                            | 4.7                                    |      |                           |       |

| *50;51A             | condition                                                      | f <sub>SCL</sub> > 100kHz                                         | 0.6                                    |      |                           | _     |

| t <sub>HD;DAT</sub> | Data hold time                                                 | $f_{SCL} \leq 100 kHz$                                            | 0                                      |      | 3.5                       |       |

| "HD;DAI             |                                                                | f <sub>SCL</sub> > 100kHz                                         | 0                                      |      | 0.9                       |       |

| t                   | Data setup time                                                | $f_{SCL} {\leq 100 kHz}$                                          | 250                                    |      |                           | ns    |

| t <sub>su;dat</sub> |                                                                | f <sub>SCL</sub> > 100kHz                                         | 100                                    |      |                           |       |

| +                   | Setup time for STOP condition                                  | $f_{SCL} {\leq 100 kHz}$                                          | 4.0                                    |      |                           |       |

| t <sub>su;sto</sub> |                                                                | f <sub>SCL</sub> > 100kHz                                         | 0.6                                    |      |                           | μs    |

| +                   | Bus free time between a STOP and                               | $f_{SCL} \leq 100 kHz$                                            | 4.7                                    |      |                           |       |

| t <sub>BUF</sub>    | START condition                                                | f <sub>SCL</sub> > 100kHz                                         | 1.3                                    |      |                           |       |

Notes:

Required only for f<sub>SCL</sub> > 100kHz.

C<sub>b</sub> = Capacitance of one bus line in pF.

f<sub>PER</sub> = Peripheral clock frequency.

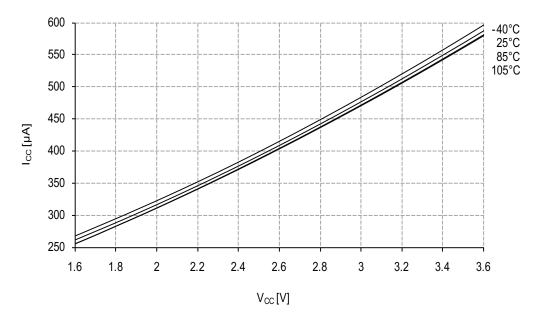

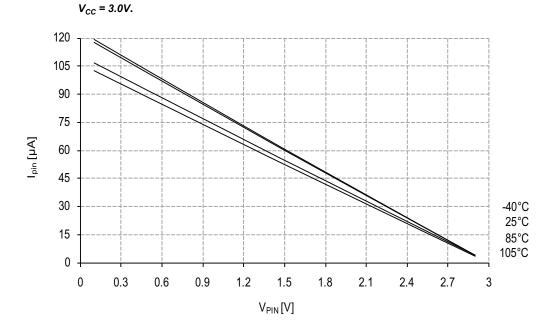

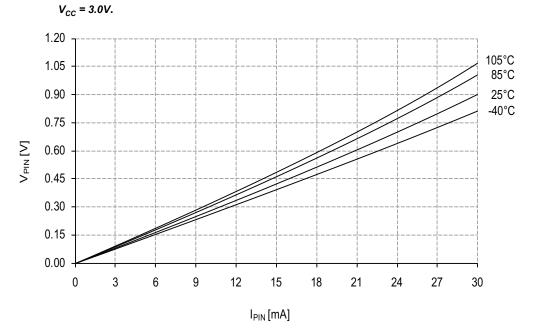

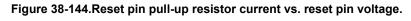

Figure 38-21. I/O pin pull-up resistor current vs. pin voltage.

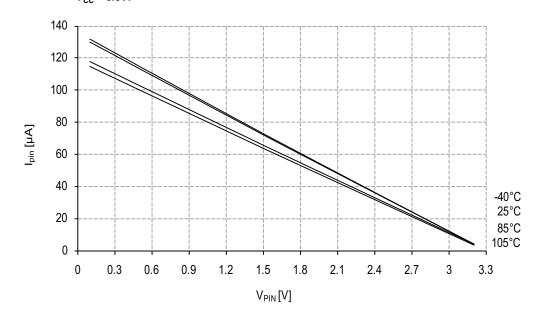

Figure 38-22. I/O pin pull-up resistor current vs. pin voltage.  $V_{cc} = 3.3V.$

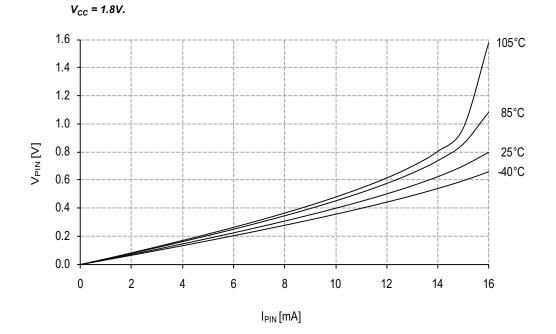

Figure 38-27.I/O pin output voltage vs. sink current.

Figure 38-28.I/O pin output voltage vs. sink current.

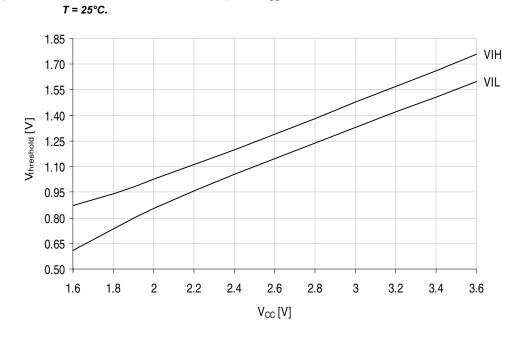

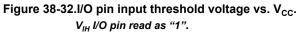

Figure 38-31.I/O pin input threshold voltage vs.  $\ensuremath{\text{V}_{\text{CC}}}$  .

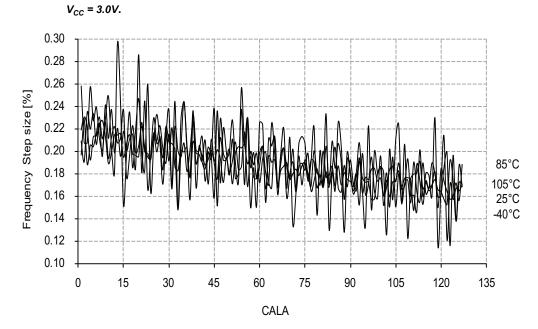

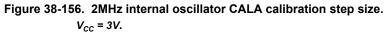

Figure 38-77. 32MHz internal oscillator CALA calibration step size.

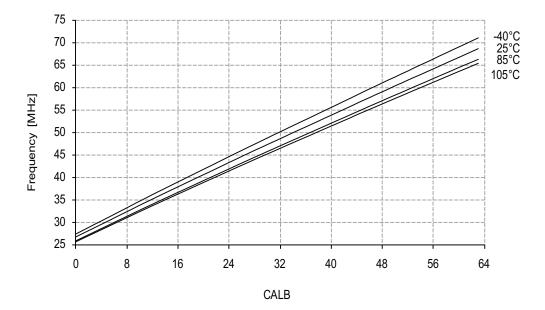

Figure 38-78. 32MHz internal oscillator frequency vs. CALB calibration value.  $V_{CC}$  = 3.0V, DFLL disabled.

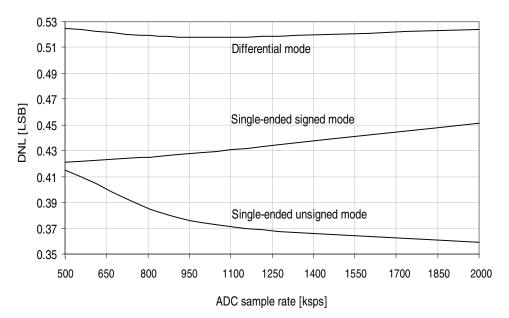

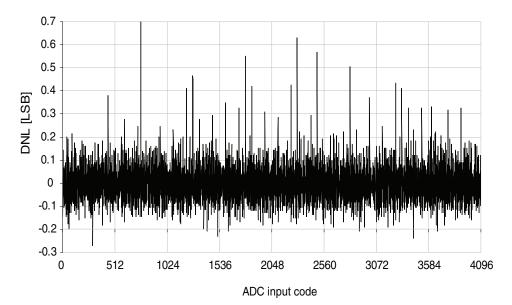

Figure 38-121.DNL error vs. sample rate.

*T* = 25 °C, *V*<sub>CC</sub> = 3.6*V*, *V*<sub>REF</sub> = 2.0*V* external.

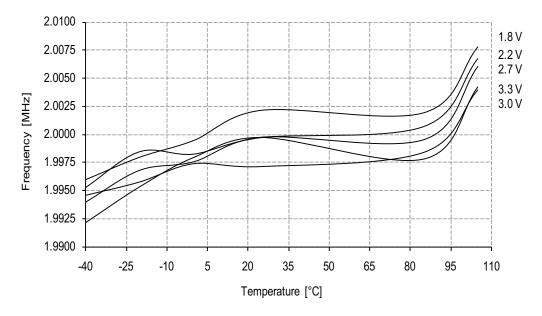

Figure 38-155. 2MHz internal oscillator frequency vs. temperature. *DFLL enabled*.

## 15. ADC has increased linearity error when using the gain stage above 500ksps

The INL error for gain stage is increased to above 20LSB for sampling speed exceeding 500 ksps.

#### Problem fix/Workaround

None.

## 16. DAC Offset calibration range too small when using AVCC as reference

If using AVCC as reference, the DAC offset calibration will not totally remove the offset error. Offset could be up to 100LSB after calibration.

## Problem fix/Workaround

Offset adjustment must be partly handled in software.

## 17. DAC clock noise

The system clock is visible as clock noise on the output of the DAC. Peak to peak noise is in the range 0.7mV - 1.6mV at 2MHz and 0.05mV to 0.1mV at 32MHz. If external clock is used as system clock, the noise is up to three times higher.

## Problem fix/Workaround

Add external low-pass filter to remove the noise.

## 18. Internal 1V reference has noise at low temperature

The internal 1.0V reference for the ADC and DAC has increased noise at low temperatures. The noise can result in INL numbers up to +/- 20 LSB at temperatures below 0C.

## Problem fix/Workaround

For the ADC, use oversampling to reduce noise. For the DAC use external filter to reduce the noise.

## 39.2.2 Rev. A - K

Not sampled.