#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | AVR                                                                         |

| Core Size                  | 8/16-Bit                                                                    |

| Speed                      | 32MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                  |

| Number of I/O              | 78                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 2K x 8                                                                      |

| RAM Size                   | 8K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                                 |

| Data Converters            | A/D 16x12b; D/A 4x12b                                                       |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-TQFP                                                                    |

| Supplier Device Package    | 100-TQFP (14x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega128a1u-anr |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Ordering Information

| Ordering code                     | Flash (bytes) | EEPROM<br>(bytes) | SRAM<br>(bytes) | Speed (MHz)     | Power<br>supply | Package<br>(1)(2)(3) | Temp.         |

|-----------------------------------|---------------|-------------------|-----------------|-----------------|-----------------|----------------------|---------------|

| ATxmega128A1U-AU                  | 128K + 8K     | 2K                | 8K              |                 |                 |                      |               |

| ATxmega128A1U-AUR <sup>(4)</sup>  | 128K + 8K     | 2K                | 8K              |                 |                 | 100A                 |               |

| ATxmega64A1U-AU                   | 64K + 4K      | 2K                | 4K              | _               |                 | TUUA                 |               |

| ATxmega64A1U-AUR <sup>(4)</sup>   | 64K + 4K      | 2K                | 4K              |                 |                 |                      |               |

| ATxmega128A1U-CU                  | 128K + 8K     | 2K                | 8K              | _               |                 |                      | -             |

| ATxmega128A1U-CUR <sup>(4)</sup>  | 128K + 8K     | 2K                | 8K              |                 |                 | 100C1                | -40°C - 85°C  |

| ATxmega64A1U-CU                   | 64K + 4K      | 2K                | 4K              |                 |                 | 10001                | -40°C - 85°C  |

| ATxmega64A1U-CUR <sup>(4)</sup>   | 64K + 4K      | 2K                | 4K              |                 | 4.0. 0.01       |                      | _             |

| ATxmega128A1U-C7U                 | 128K + 8K     | 2K                | 8K              | - 32 1.0 - 3.0V | 32 1.6 - 3.6V   |                      |               |

| ATxmega128A1U-C7UR <sup>(4)</sup> | 128K + 8K     | 2K                | 8K              |                 |                 | 100C2                |               |

| ATxmega64A1U-C7U                  | 64K + 4K      | 2K                | 4K              | _               |                 | 10002                |               |

| ATxmega64A1U-C7UR <sup>(4)</sup>  | 64K + 4K      | 2K                | 4K              |                 |                 |                      |               |

| ATxmega128A1U-AN                  | 128K + 8K     | 2K                | 8K              |                 |                 |                      |               |

| ATxmega128A1U-ANR <sup>(4)</sup>  | 128K + 8K     | 2K                | 8K              |                 |                 | 100A                 | -40°C - 105°C |

| ATxmega64A1U-AN                   | 64K + 4K      | 2K                | 4K              |                 |                 | TUUA                 | -40°C - 105°C |

| ATxmega64A1U-ANR <sup>(4)</sup>   | 64K + 4K      | 2K                | 4K              |                 |                 |                      |               |

1. This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering information.

2. Pb-free packaging, complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). Also Halide free and fully Green.

3. For packaging information, see "Packaging information" on page 71.

4. Tape and Reel.

Notes:

|       | Package Type                                                                                  |

|-------|-----------------------------------------------------------------------------------------------|

| 100A  | 100-lead, 14 x 14 x 1.0mm, 0.5mm lead pitch, thin profile plastic quad flat package (TQFP)    |

| 100C1 | 100-ball, 9 x 9 x 1.2mm body, ball pitch 0.80mm, chip ball grid array (CBGA)                  |

| 100C2 | 100-ball, 7 x 7 x 1.0mm body, ball pitch 0.65mm, very thin fine-pitch ball grid array (VFBGA) |

# **Typical Applications**

| Industrial control | Climate control            | Low power battery applications |

|--------------------|----------------------------|--------------------------------|

| Factory automation | RF and ZigBee <sup>®</sup> | Power tools                    |

| Building control   | USB connectivity           | HVAC                           |

| Board control      | Sensor control             | Utility metering               |

| White goods        | Optical                    | Medical applications           |

# Table 7-3. Number of Bytes and Pages in the EEPROM.

| Devices       | EEPROM | Page Size | E2BYTE    | E2PAGE     | No of Pages |

|---------------|--------|-----------|-----------|------------|-------------|

|               | Size   | bytes     |           |            |             |

| ATxmega64A1U  | 2К     | 32        | ADDR[4:0] | ADDR[10:5] | 64          |

| ATxmega128A1U | 2K     | 32        | ADDR[4:0] | ADDR[10:5] | 64          |

# 9. Event System

# 9.1 Features

- System for direct peripheral-to-peripheral communication and signaling

- Peripherals can directly send, receive, and react to peripheral events

- CPU and DMA controller independent operation

- 100% predictable signal timing

- Short and guaranteed response time

- Eight event channels for up to eight different and parallel signal routing configurations

- Events can be sent and/or used by most peripherals, clock system, and software

- Additional functions include

- Quadrature decoders

- Digital filtering of I/O pin state

- Works in active mode and idle sleep mode

# 9.2 Overview

The event system enables direct peripheral-to-peripheral communication and signaling. It allows a change in one peripheral's state to automatically trigger actions in other peripherals. It is designed to provide a predictable system for short and predictable response times between peripherals. It allows for autonomous peripheral control and interaction without the use of interrupts, CPU, or DMA controller resources, and is thus a powerful tool for reducing the complexity, size and execution time of application code. It also allows for synchronized timing of actions in several peripheral modules.

A change in a peripheral's state is referred to as an event, and usually corresponds to the peripheral's interrupt conditions. Events can be directly passed to other peripherals using a dedicated routing network called the event routing network. How events are routed and used by the peripherals is configured in software.

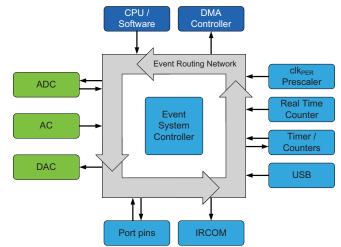

Figure 9-1 on page 18 shows a basic diagram of all connected peripherals. The event system can directly connect together analog and digital converters, analog comparators, I/O port pins, the real-time counter, timer/counters, IR communication module (IRCOM), and USB interface. It can also be used to trigger DMA transactions (DMA controller). Events can also be generated from software and the peripheral clock.

#### Figure 9-1. Event system overview and connected peripherals.

The event routing network consists of eight software-configurable multiplexers that control how events are routed and used. These are called event channels, and allow for up to eight parallel event routing configurations. The maximum routing latency is two peripheral clock cycles. The event system works in both active mode and idle sleep mode.

# 11. Power Management and Sleep Modes

# 11.1 Features

- Power management for adjusting power consumption and functions

- Five sleep modes

- Idle

- Power down

- Power save

- Standby

- Extended standby

- Power reduction register to disable clock and turn off unused peripherals in active and idle modes

# 11.2 Overview

Various sleep modes and clock gating are provided in order to tailor power consumption to application requirements. This enables the Atmel AVR XMEGA microcontroller to stop unused modules to save power.

All sleep modes are available and can be entered from active mode. In active mode, the CPU is executing application code. When the device enters sleep mode, program execution is stopped and interrupts or a reset is used to wake the device again. The application code decides which sleep mode to enter and when. Interrupts from enabled peripherals and all enabled reset sources can restore the microcontroller from sleep to active mode.

In addition, power reduction registers provide a method to stop the clock to individual peripherals from software. When this is done, the current state of the peripheral is frozen, and there is no power consumption from that peripheral. This reduces the power consumption in active mode and idle sleep modes and enables much more fine-tuned power management than sleep modes alone.

# 11.3 Sleep Modes

Sleep modes are used to shut down modules and clock domains in the microcontroller in order to save power. XMEGA microcontrollers have five different sleep modes tuned to match the typical functional stages during application execution. A dedicated sleep instruction (SLEEP) is available to enter sleep mode. Interrupts are used to wake the device from sleep, and the available interrupt wake-up sources are dependent on the configured sleep mode. When an enabled interrupt occurs, the device will wake up and execute the interrupt service routine before continuing normal program execution from the first instruction after the SLEEP instruction. If other, higher priority interrupts are pending when the wake-up occurs, their interrupt service routines will be executed according to their priority before the interrupt service routine for the wake-up interrupt is executed. After wake-up, the CPU is halted for four cycles before execution starts.

The content of the register file, SRAM and registers are kept during sleep. If a reset occurs during sleep, the device will reset, start up, and execute from the reset vector.

# 11.3.1 Idle Mode

In idle mode the CPU and nonvolatile memory are stopped (note that any ongoing programming will be completed), but all peripherals, including the interrupt controller, event system and DMA controller are kept running. Any enabled interrupt will wake the device.

# 11.3.2 Power-down Mode

In power-down mode, all clocks, including the real-time counter clock source, are stopped. This allows operation only of asynchronous modules that do not require a running clock. The only interrupts that can wake up the MCU are the twowire interface address match interrupt, asynchronous port interrupts, and the USB resume interrupt.

| Symbol | Parameter                       | Condition             |                                                 | Min. | Тур. | Max. | Units     |

|--------|---------------------------------|-----------------------|-------------------------------------------------|------|------|------|-----------|

|        |                                 | 1x gain, normal mode  |                                                 |      | -0.7 |      |           |

|        | Gain Error                      | 8x gain, normal mode  |                                                 |      | -3.0 |      | %         |

|        |                                 | 64x gain, normal mode |                                                 |      | -4.8 |      |           |

|        |                                 | 1x gain, normal mode  |                                                 |      | 0.4  |      |           |

|        | Offset Error,<br>input referred | 8x gain, normal mode  |                                                 |      | 0.4  |      | mV        |

|        |                                 | 64x gain, normal mode |                                                 |      | 0.4  |      |           |

|        |                                 | 1x gain, normal mode  |                                                 |      | 0.6  |      |           |

|        | Noise                           | 8x gain, normal mode  | V <sub>CC</sub> = 3.6V<br>Ext. V <sub>REF</sub> |      | 2.0  |      | mV<br>rms |

|        |                                 | 64x gain, normal mode | NLI                                             |      | 11   |      |           |

Note: 1. Maximum numbers are based on characterisation and not tested in production, and valid for 5% to 95% input voltage range.

# 37.1.7 DAC Characteristics

| Table 37-12 | . Power | supply, | reference | and | output | range. |

|-------------|---------|---------|-----------|-----|--------|--------|

|-------------|---------|---------|-----------|-----|--------|--------|

| Symbol               | Parameter                   | Condition                               | Min.                  | Тур. | Max.                       | Units |

|----------------------|-----------------------------|-----------------------------------------|-----------------------|------|----------------------------|-------|

| AV <sub>CC</sub>     | Analog supply voltage       |                                         | V <sub>CC</sub> - 0.3 |      | V <sub>CC</sub> + 0.3      | V     |

| AV <sub>REF</sub>    | External reference voltage  |                                         | 1.0                   |      | V <sub>CC</sub> - 0.6      | v     |

| R <sub>channel</sub> | DC output impedance         |                                         |                       |      | 50                         | Ω     |

|                      | Linear output voltage range |                                         | 0.15                  |      | AV <sub>CC</sub> -0.15     | V     |

| R <sub>AREF</sub>    | Reference input resistance  |                                         |                       | >10  |                            | MΩ    |

| CAREF                | Reference input capacitance | Static load                             |                       | 7    |                            | pF    |

|                      | Minimum resistance load     |                                         | 1.0                   |      |                            | kΩ    |

|                      | Maximum canacitance load    |                                         |                       |      | 100                        | pF    |

|                      | Maximum capacitance load    | 1000 $\Omega$ serial resistance         |                       |      | 1.0                        | nF    |

|                      | Output sink/source          | Operating within accuracy specification |                       |      | AV <sub>CC</sub> /100<br>0 | mA    |

|                      |                             | Safe operation                          |                       |      | 10                         |       |

# Table 37-13. Clock and timing.

| Symbol | Parameter       | Condition                 |                | Min. | Тур. | Max. | Units |

|--------|-----------------|---------------------------|----------------|------|------|------|-------|

| f      | Conversion rate | C <sub>load</sub> =100pF, | Normal mode    | 0    |      | 1000 | kene  |

| DAC    | Conversion rate | maximum step size         | Low power mode |      |      | 500  | ksps  |

## Table 37-14. Accuracy characteristics.

| Symbol             | Parameter                    | Condition                          |                         | Min.                   | Тур. | Max. | Units |

|--------------------|------------------------------|------------------------------------|-------------------------|------------------------|------|------|-------|

| RES                | Input resolution             |                                    |                         |                        |      | 12   | Bits  |

|                    |                              | $\gamma = E_{\rm V} + 1.0 \gamma$  | V <sub>CC</sub> = 1.6V  |                        | ±2.0 | ±3   |       |

|                    |                              | V <sub>REF</sub> = Ext 1.0V        | V <sub>CC</sub> = 3.6V  |                        | ±1.5 | ±2.5 |       |

| INL <sup>(1)</sup> | Integral non-linearity       |                                    | V <sub>CC</sub> = 1.6V  |                        | ±2.0 | ±4   | _     |

|                    | integral non-intearity       | V <sub>REF</sub> =AV <sub>CC</sub> | V <sub>CC</sub> = 3.6V  |                        | ±1.5 | ±4   |       |

|                    |                              | \/ -INIT1\/                        | V <sub>CC</sub> = 1.6V  |                        | ±5.0 |      |       |

|                    |                              | V                                  | V <sub>REF</sub> =INT1V | V <sub>CC</sub> = 3.6V |      | ±5.0 |       |

|                    | Differentiel new linearity   | V <sub>REF</sub> =Ext 1.0V         | V <sub>CC</sub> = 1.6V  |                        | ±1.5 | 3.0  | lsb   |

|                    |                              |                                    | V <sub>CC</sub> = 3.6V  |                        | ±0.6 | 1.5  |       |

| DNL <sup>(1)</sup> |                              |                                    | V <sub>CC</sub> = 1.6V  |                        | ±1.0 | 3.5  | -     |

| DINL               | Differential non-linearity   | V <sub>REF</sub> =AV <sub>CC</sub> | V <sub>CC</sub> = 3.6V  |                        | ±0.6 | 1.5  | -     |

|                    |                              |                                    | V <sub>CC</sub> = 1.6V  |                        | ±4.5 |      |       |

|                    |                              | V <sub>REF</sub> =INT1V            | V <sub>CC</sub> = 3.6V  |                        | ±4.5 |      | -     |

|                    | Gain error                   | After calibration                  |                         |                        | <4.0 |      | -     |

|                    | Gain calibration step size   |                                    |                         |                        | 4.0  |      |       |

|                    | Gain calibration drift       | V <sub>REF</sub> = Ext 1.0V        |                         |                        | <0.2 |      | mV/K  |

|                    | Offset error                 | After calibration                  |                         |                        | <1.0 |      | lsb   |

|                    | Offset calibration step size |                                    |                         |                        | 1.0  |      |       |

Note: 1. Maximum numbers are based on characterisation and not tested in production, and valid for 5% to 95% output voltage range.

# 37.1.8 Analog Comparator Characteristics

## Table 37-15. Analog Comparator characteristics.

| Symbol            | Parameter             | Condition              | Min. | Тур. | Max.                  | Units |

|-------------------|-----------------------|------------------------|------|------|-----------------------|-------|

| V <sub>off</sub>  | Input offset voltage  |                        |      | <±10 |                       | mV    |

| I <sub>lk</sub>   | Input leakage current |                        |      | <1   |                       | nA    |

|                   | Input voltage range   |                        | -0.1 |      | AV <sub>CC</sub> +0.1 | V     |

| V <sub>hys1</sub> | Hysteresis, none      |                        |      | 0    |                       |       |

| M                 |                       | mode = High Speed (HS) |      | 22   |                       |       |

| V <sub>hys2</sub> | Hysteresis, small     | mode = Low Power (LP)  |      | 30   |                       | mV    |

| M                 |                       | mode = HS              |      | 43   |                       |       |

| V <sub>hys3</sub> | Hysteresis, large     | mode = LP              |      | 60   |                       |       |

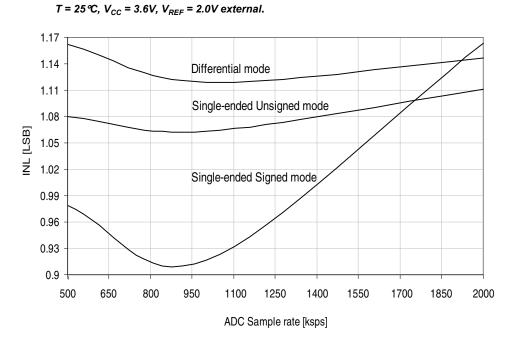

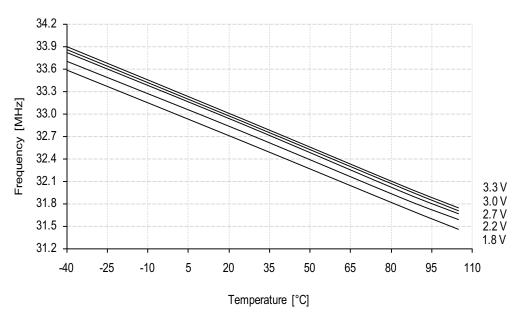

#### 37.1.14.3 Calibrated and tunable 32MHz internal oscillator characteristics

## Table 37-24. 32MHz internal oscillator characteristics.

| Symbol | Parameter                    | Condition                                                    | Min. | Тур. | Max. | Units |

|--------|------------------------------|--------------------------------------------------------------|------|------|------|-------|

|        | Tunable frequency range      | DFLL can tune to this frequency over voltage and temperature | 30   |      | 35   | MHz   |

|        | Factory calibrated frequency |                                                              |      | 32   |      |       |

|        | Factory calibration accuracy | T = 85°C, V <sub>CC</sub> = 3.0V                             | -1.5 |      | 1.5  | %     |

|        | DFLL calibration step size   |                                                              |      | 0.24 |      | 70    |

#### 37.1.14.4 32kHz Internal ULP Oscillator characteristics

#### Table 37-25. 32kHz internal ULP oscillator characteristics.

| Symbol | Parameter        | Condition | Min. | Тур. | Max. | Units |

|--------|------------------|-----------|------|------|------|-------|

|        | Output frequency |           |      | 32   |      | kHz   |

|        | Accuracy         |           | -30  |      | 30   | %     |

## 37.1.14.5 Internal Phase Locked Loop (PLL) characteristics

# Table 37-26. Internal PLL characteristics.

| Symbol           | Parameter                       | Condition                                                   | Min. | Тур. | Max. | Units |  |

|------------------|---------------------------------|-------------------------------------------------------------|------|------|------|-------|--|

| f <sub>IN</sub>  | Input frequency                 | Output frequency must be within $\mathbf{f}_{\text{OUT}}$   | 0.4  |      | 64   | 64    |  |

|                  |                                 | V <sub>CC</sub> = 1.6V                                      | 20   | 0.4  | 32   | MHz   |  |

| f <sub>OUT</sub> | Output frequency <sup>(1)</sup> | V <sub>CC</sub> = 2.7V                                      | 20   |      | 96   |       |  |

|                  |                                 | V <sub>CC</sub> = 3.6V                                      | 20   |      | 128  |       |  |

|                  | Duty cycle                      |                                                             |      | 50   |      | %     |  |

|                  | Start-up lock time              | f <sub>OUT</sub> = 48MHz                                    |      | 18   |      |       |  |

|                  | Re-lock time                    | f <sub>OUT-init</sub> = 10MHz, f <sub>OUT-end</sub> = 64MHz |      | 17   |      | μs    |  |

Note: 1. The maximum output frequency vs. supply voltage is linear between 1.8V and 2.7V, and can never be higher than four times the maximum CPU frequency.

### 37.2.5 I/O Pin Characteristics

The I/O pins complies with the JEDEC LVTTL and LVCMOS specification and the high- and low level input and output voltage limits reflect or exceed this specification.

#### Table 37-41. I/O pin characteristics.

| Symbol                                                             | Parameter                         | Con                           | ndition                | Min.                   | Тур.                 | Max.                 | Units |  |

|--------------------------------------------------------------------|-----------------------------------|-------------------------------|------------------------|------------------------|----------------------|----------------------|-------|--|

| I <sub>OH</sub> <sup>(1)</sup> /<br>I <sub>OL</sub> <sup>(2)</sup> | I/O pin source/sink current       |                               |                        | -20                    |                      | 20                   | mA    |  |

| V <sub>IH</sub>                                                    |                                   | V <sub>CC</sub> = 2.7 - 3.6V  |                        | 2                      |                      | V <sub>CC</sub> +0.3 |       |  |

|                                                                    | High level input voltage          | V <sub>CC</sub> = 2.0 - 2.7V  |                        | 0.7*V <sub>CC</sub>    |                      | V <sub>CC</sub> +0.3 |       |  |

|                                                                    |                                   | V <sub>CC</sub> = 1.6 - 2.0V  |                        | 0.7*V <sub>CC</sub>    |                      | V <sub>CC</sub> +0.3 |       |  |

|                                                                    |                                   | V <sub>CC</sub> = 2.7- 3.6V   |                        | -0.3                   |                      | 0.3*V <sub>CC</sub>  |       |  |

| V <sub>IL</sub>                                                    | Low level input voltage           | V <sub>CC</sub> = 2.0 - 2.7V  |                        | -0.3                   |                      | 0.3*V <sub>CC</sub>  |       |  |

|                                                                    |                                   | V <sub>CC</sub> = 1.6 - 2.0V  |                        | -0.3                   |                      | 0.3*V <sub>CC</sub>  |       |  |

|                                                                    |                                   | V <sub>CC</sub> = 3.0 - 3.6V  | I <sub>OH</sub> = -2mA | 2.4                    | 0.94*V <sub>CC</sub> |                      |       |  |

|                                                                    |                                   | V <sub>CC</sub> = 2.3 - 2.7V  | I <sub>OH</sub> = -1mA | 2.0                    | 0.96*V <sub>CC</sub> |                      |       |  |

| V                                                                  | High level output voltage         | $V_{\rm CC} = 2.3 - 2.7 V$    | I <sub>OH</sub> = -2mA | 1.7                    | 0.92*V <sub>CC</sub> |                      | V     |  |

| V <sub>OH</sub>                                                    |                                   | V <sub>CC</sub> = 3.3V        | I <sub>OH</sub> = -8mA | 2.6                    | 2.9                  |                      | v     |  |

|                                                                    |                                   | V <sub>CC</sub> = 3.0V        | I <sub>OH</sub> = -6mA | 2.1                    | 2.6                  |                      |       |  |

|                                                                    |                                   | ν                             | V <sub>CC</sub> = 1.8V | I <sub>OH</sub> = -2mA | 1.4                  | 1.6                  |       |  |

|                                                                    |                                   | V <sub>CC</sub> = 3.0 - 3.6V  | I <sub>OL</sub> = 2mA  |                        | 0.05*V <sub>CC</sub> | 0.4                  |       |  |

|                                                                    |                                   | V <sub>CC</sub> = 2.3 - 2.7V  | I <sub>OL</sub> = 1mA  |                        | 0.03*V <sub>CC</sub> | 0.4                  |       |  |

| V                                                                  | Low level output voltage          | V <sub>CC</sub> - 2.3 - 2.7 V | I <sub>OL</sub> = 2mA  |                        | 0.06*V <sub>CC</sub> | 0.7                  |       |  |

| V <sub>OL</sub>                                                    | Low level output voltage          | V <sub>CC</sub> = 3.3V        | I <sub>OL</sub> = 15mA |                        | 0.4                  | 0.76                 |       |  |

|                                                                    |                                   | V <sub>CC</sub> = 3.0V        | I <sub>OL</sub> = 10mA |                        | 0.3                  | 0.64                 |       |  |

|                                                                    |                                   | V <sub>CC</sub> = 1.8V        | I <sub>OL</sub> = 5mA  |                        | 0.3                  | 0.46                 |       |  |

| I <sub>IN</sub>                                                    | Input leakage current             |                               |                        |                        | <0.001               | 0.1                  | μA    |  |

| R <sub>P</sub>                                                     | I/O pin Pull/Buss keeper resistor |                               |                        |                        | 25                   |                      | kΩ    |  |

| R <sub>RST</sub>                                                   | Reset pin pull-up resistor        |                               |                        |                        | 25                   |                      | NS2   |  |

| +                                                                  | Pad rise time                     | Noload                        |                        |                        | 4.0                  |                      | ne    |  |

| t <sub>r</sub> I                                                   | Pad rise time                     | d rise time No load           | slew rate limitation   |                        | 7.0                  |                      | ns    |  |

1. The sum of all  $I_{OH}$  for PORTA, PORTC, PORTD, PORTF, PORTH, PORTJ, PORTK must for each port not exceed 200mA. The sum of all  $I_{OH}$  for PORTB must not exceed 100mA. The sum of all  $I_{OH}$  for PORTQ, PORTR and PDI must not exceed 100mA. Notes:

The sum of all  $I_{OL}$  for PORTA, PORTC, PORTD, PORTF, PORTH, PORTJ, PORTK must for each port not exceed 200mA. The sum of all  $I_{OL}$  for PORTB must not exceed 100mA. The sum of all  $I_{OL}$  for PORTQ, PORTR and PDI must not exceed 100mA. 2.

# 37.2.6 ADC characteristics

| Symbol            | Parameter                   | Condition                        | Min.                  | Тур. | Max.                   | Units |

|-------------------|-----------------------------|----------------------------------|-----------------------|------|------------------------|-------|

| AV <sub>CC</sub>  | Analog supply voltage       |                                  | V <sub>CC</sub> - 0.3 |      | V <sub>CC</sub> + 0.3  | V     |

| V <sub>REF</sub>  | Reference voltage           |                                  | 1                     |      | AV <sub>CC</sub> - 0.6 | v     |

| R <sub>in</sub>   | Input resistance            | Switched                         |                       | 5.0  |                        | kΩ    |

| C <sub>in</sub>   | Input capacitance           | Switched                         |                       | 5.0  |                        | pF    |

| R <sub>AREF</sub> | Reference input resistance  | (leakage only)                   |                       | >10  |                        | MΩ    |

| C <sub>AREF</sub> | Reference input capacitance | Static load                      |                       | 7    |                        | pF    |

| V <sub>IN</sub>   | Input range                 |                                  | -0.1                  |      | AV <sub>CC</sub> +0.1  |       |

|                   | Conversion range            | Differential mode, Vinp - Vinn   | -V <sub>REF</sub>     |      | V <sub>REF</sub>       | V     |

| V <sub>IN</sub>   | Conversion range            | Single ended unsigned mode, Vinp | -ΔV                   |      | $V_{REF}$ - $\Delta V$ |       |

| ΔV                | Fixed offset voltage        |                                  |                       | 190  |                        | LSB   |

Table 37-42. Power supply, reference and input range.

# Table 37-43. Clock and timing.

| Symbol             | Parameter                 | Condition                                          | Min.                               | Тур. | Max. | Units                        |

|--------------------|---------------------------|----------------------------------------------------|------------------------------------|------|------|------------------------------|

| Clk <sub>ADC</sub> | ADC Clock frequency       | Maximum is 1/4 of peripheral clock<br>frequency    | 100                                |      | 2000 | kHz                          |

|                    |                           | Measuring internal signals                         | 100                                |      | 125  |                              |

|                    |                           | Current limitation (CURRLIMIT) off                 | 100                                |      | 2000 |                              |

| £                  | Comple rote               | CURRLIMIT = LOW                                    | 100                                |      | 1500 | kana                         |

| f <sub>ADC</sub>   | Sample rate               | CURRLIMIT = MEDIUM                                 | 100       100       100       0.25 | 1000 | ksps |                              |

|                    |                           | CURRLIMIT = HIGH                                   |                                    |      | 500  |                              |

|                    | Sampling time             | 1/2 Clk <sub>ADC</sub> cycle                       | 0.25                               |      | 5    | μs                           |

|                    | Conversion time (latency) | (RES+2)/2+(GAIN !=0)<br>RES (Resolution) = 8 or 12 | 5                                  |      | 8    | Clk <sub>ADC</sub><br>cycles |

|                    | Start-up time             | ADC clock cycles                                   |                                    | 12   | 24   | Clk <sub>ADC</sub><br>cycles |

|                    | ADC sottling time         | After changing reference or input mode             |                                    | 7    | 7    | Clk <sub>ADC</sub>           |

|                    | ADC settling time         | After ADC flush                                    |                                    | 1    | 1    | cycles                       |

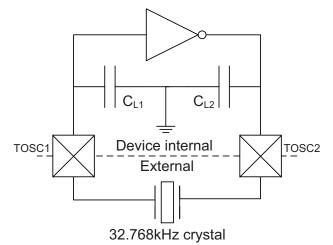

#### 37.2.14.8 External 32.768kHz crystal oscillator and TOSC characteristics

| Table 37-64. E | xternal 32.768kHz crystal oscillator and TOSC characteristics. |

|----------------|----------------------------------------------------------------|

|----------------|----------------------------------------------------------------|

| Symbol             | Parameter                                    | Condition                                        | Min. | Тур. | Max. | Units |

|--------------------|----------------------------------------------|--------------------------------------------------|------|------|------|-------|

|                    | Recommended crystal                          | Crystal load capacitance 6.5pF                   |      |      | 60   | ko    |

| ESR/RI             | ESR/R1 equivalent series resistance<br>(ESR) | Crystal load capacitance 9.0pF                   |      |      | 35   | kΩ    |

| C <sub>TOSC1</sub> | Parasitic capacitance TOSC1 pin              |                                                  |      | 4.0  |      |       |

| C <sub>TOSC2</sub> | Parasitic capacitance TOSC2 pin              |                                                  |      | 4.1  |      | pF    |

| CL                 | Parasitic capacitance load                   |                                                  |      | 2.0  |      | -     |

|                    | Recommended safety factor                    | Capacitive load matched to crystal specification | 3    |      |      |       |

Note: 1. See Figure 37-11 for definition.

### Figure 37-11.TOSC input capacitance.

The parasitic capacitance between the TOSC pins is  $C_{L1} + C_{L2}$  in series as seen from the crystal when oscillating without external capacitors.

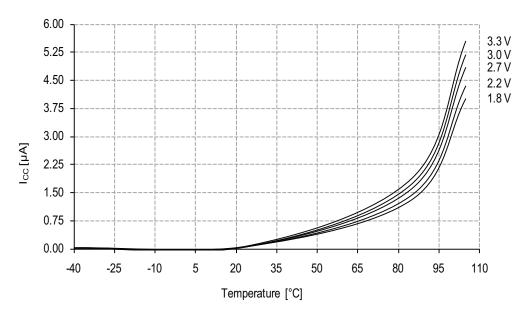

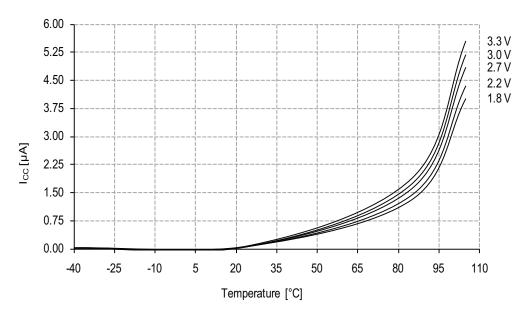

#### 38.1.1.3 Power-down mode supply current

Figure 38-15.Power-down mode supply current vs. Temperature. *All functions disabled.*

Figure 38-16.Power-down mode supply current vs. Temperature. Sampled BOD with Watchdog Timer running on ULP oscillator.

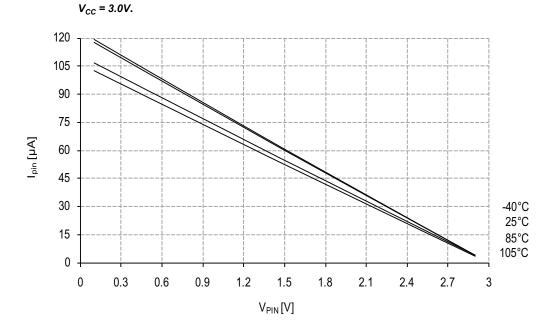

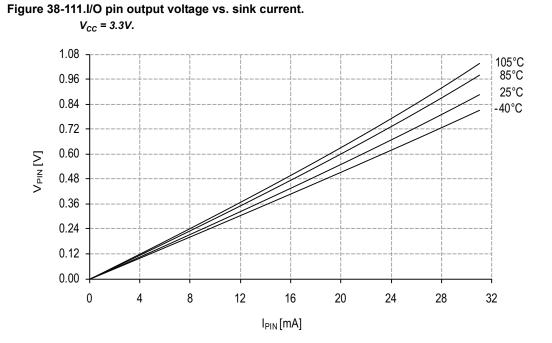

Figure 38-21. I/O pin pull-up resistor current vs. pin voltage.

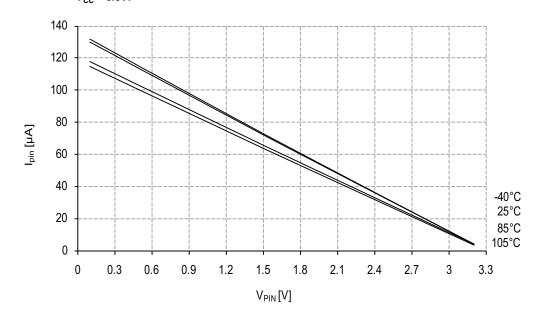

Figure 38-22. I/O pin pull-up resistor current vs. pin voltage.  $V_{cc} = 3.3V.$

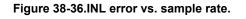

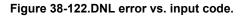

#### 38.1.3 ADC Characteristics

# **Atmel**

Figure 38-75. 32MHz internal oscillator frequency vs. temperature. *DFLL disabled*.

Figure 38-76. 32MHz internal oscillator frequency vs. temperature. DFLL enabled, from the 32.768kHz internal oscillator.

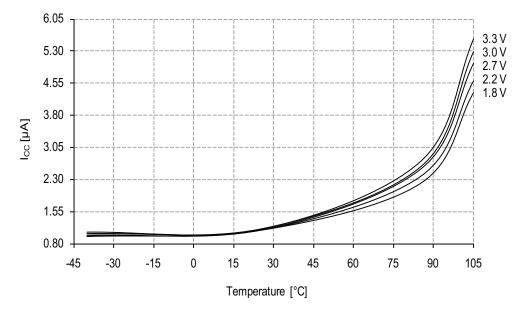

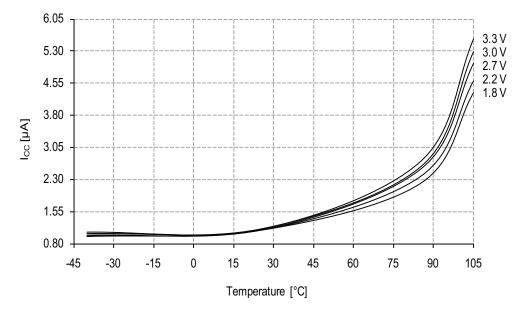

#### 38.2.1.3 Power-down mode supply current

Figure 38-97.Power-down mode supply current vs. Temperature. *All functions disabled*.

Figure 38-98.Power-down mode supply current vs. Temperature. Sampled BOD with Watchdog Timer running on ULP oscillator.

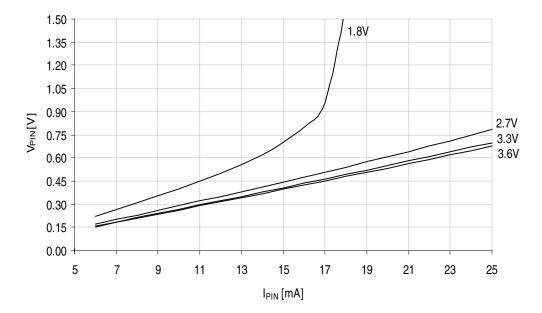

Figure 38-112.I/O pin output voltage vs. sink current.

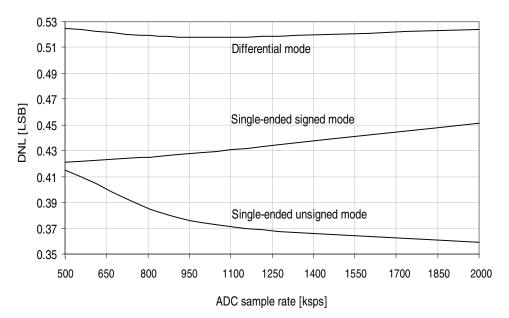

Figure 38-121.DNL error vs. sample rate.

*T* = 25 °C, *V*<sub>CC</sub> = 3.6*V*, *V*<sub>REF</sub> = 2.0*V* external.

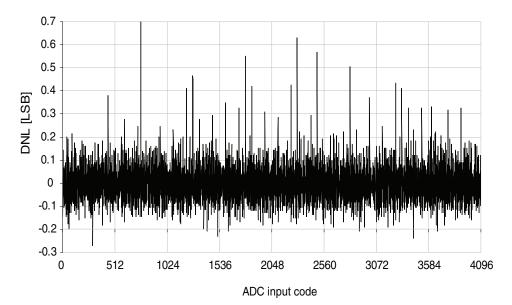

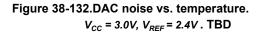

Figure 38-131.DAC DNL error vs. V<sub>REF</sub>.

Atmel

# 39. Errata

# 39.1 ATxmega64A1U

## 39.1.1 Rev. L

- Register ANAINIT in MCUR will always read as zero

- Enabling DFLL with illegal reference oscillator will lock the DFLL

- XOSCPWR configuration is non-functional

- Configuration of PGM and CWCM is not as described in XMEGA AU Manual

- AWEX PWM output after fault restarted with wrong values

- RTC Counter value not correctly read after sleep

- RTC clock output option is non-functional

- USB, when receiving 1023 byte length isochronous frame, it will corrupt 1024th SRAM location

- USB endpoint table is 16-byte alignment

- USB Auto ZLP feature is non-functional

- Disabling the USART transmitter does not automatically set the TxD pin direction to input

- TWI, SDAHOLD configuration in the TWI CTRL register is one bit

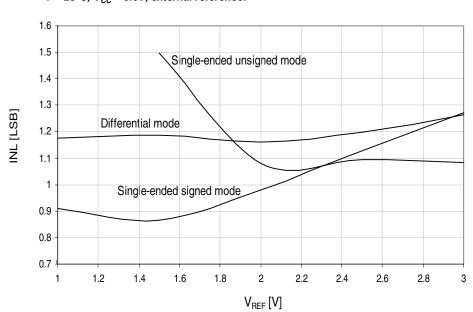

- ADC has increased INL error in when used in SE unsigned mode at low temperatures

- ADC is non-functional in SE unsigned mode with VREF below 1.8V

- ADC has increased linearity error when using the gain stage above 500ksps

- DAC Offset calibration range too small when using AVCC as reference

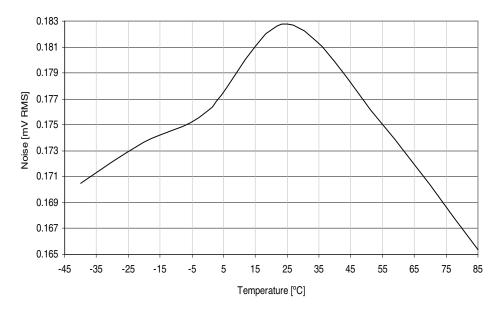

- DAC clock noise

- Internal 1V reference has noise at low temperature

# 1 Register ANAINIT in MCUR will always read as zero

The ANAINIT register in the MCUR module will always be read as zero even if written to a value. The actual content of the register is correct.

#### Problem fix/Workaround

Do not use software that reads these registers to get the Analog Initialization configuration.

#### 2. Enabling DFLL with illegal reference oscillator will lock the clock system

If external crystal is selected as reference for DFLL, but no crystal is connected and DFLL is enabled, the DFLL will be locked until reset is issued.

### Problem fix/Workaround

Do not enable DFLL before reference clock is present, enabled and ready.

# 3. XOSCPWR configuration is non-functional

The Crystal oscillator drive (XOSCPWR) option in the XOSC Control register is non-functional.

# Problem fix/Workaround

None.

#### Problem fix/Workaround

Allocate 1024bytes RAM buffer when using 1023 isochronous endpoint. This workaround is implemented in all USB software and source code delivered from Atmel in the AVR Software Framework.

#### 9. USB endpoint table is 16-byte alignment

The USB endpoint table uses 16-byte alignment, instead of 16-bit alignment.

## Problem fix/Workaround

Align the endpoint configuration table pointer in SRAM to a 16-byte. This workaround is implemented in all USB software and source code delivered from Atmel in the AVR Software Framework.

#### 10. USB Auto ZLP feature is non-functional

The Auto ZLP feature is non-functional and can not be used.

# Problem fix/Workaround

None.

#### 11. Disabling the USART transmitter does not automatically set the TxD pin direction to input

If the USART transmitter is idle with no frames to transmit, setting TXEN to zero will not automatically set the TxD pin direction to input.

#### Problem fix/Workaround

The TxD pin direction can be set to input using the Port pin direction to input using the port direction (DIR) register. When the port pin direction is input, it will be immediate and ongoing transmissions will be truncated.

#### 12. TWI, SDAHOLD configuration in the TWI CTRL register is one bit

The SDAHOLD configuration in the TWI Control register (CTRL) is one bit. Due to this the SDA hold time can be configured for maximum ~50ns when enabled. Configuring for longer hold time will have no effect.

#### Problem fix/Workaround

If longer SDA hold time than 50nS is required it must be handled in software.

#### 13. ADC has increased INL error in when used in SE unsigned mode at low temperatures

When the ADC is used on single ended (SE) unsigned mode, -INL error is increased up to +/- 5 LSB in temperatures below -20C.

### Problem fix/Workaround

Use the ADC in single ended signed mode.

## 14. ADC is non-functional in SE unsigned mode with $\rm V_{REF}$ below 1.8V

When the ADC is used on single ended unsigned mode and  $V_{REF}$  is below 1.8V, INL and DNL error is increased above +/- 10LSB, i.e. the ADC have missing codes under this condition.

## Problem fix/Workaround

Use the ADC in single ended signed mode.