Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | AVR                                                                        |

| Core Size                  | 8/16-Bit                                                                   |

| Speed                      | 32MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                      |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 78                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                                |

| Data Converters            | A/D 16x12b; D/A 4x12b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-TQFP                                                                   |

| Supplier Device Package    | 100-TQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega128a1u-au |

# 8. DMAC - Direct Memory Access Controller

### 8.1 Features

- Allows high speed data transfers with minimal CPU intervention

- from data memory to data memory

- · from data memory to peripheral

- from peripheral to data memory

- from peripheral to peripheral

- Four DMA channels with separate

- transfer triggers

- interrupt vectors

- addressing modes

- Programmable channel priority

- From 1 byte to 16MB of data in a single transaction

- Up to 64KB block transfers with repeat

- 1, 2, 4, or 8 byte burst transfers

- Multiple addressing modes

- Static

- Incremental

- Decremental

- Optional reload of source and destination addresses at the end of each

- Burst

- Block

- Transaction

- Optional interrupt on end of transaction

- Optional connection to CRC generator for CRC on DMA data

#### 8.2 Overview

The four-channel direct memory access (DMA) controller can transfer data between memories and peripherals, and thus offload these tasks from the CPU. It enables high data transfer rates with minimum CPU intervention, and frees up CPU time. The four DMA channels enable up to four independent and parallel transfers.

The DMA controller can move data between SRAM and peripherals, between SRAM locations and directly between peripheral registers. With access to all peripherals, the DMA controller can handle automatic transfer of data to/from communication modules. The DMA controller can also read from memory mapped EEPROM.

Data transfers are done in continuous bursts of 1, 2, 4, or 8 bytes. They build block transfers of configurable size from 1 byte to 64KB. A repeat counter can be used to repeat each block transfer for single transactions up to 16MB. Source and destination addressing can be static, incremental or decremental. Automatic reload of source and/or destination addresses can be done after each burst or block transfer, or when a transaction is complete. Application software, peripherals, and events can trigger DMA transfers.

The four DMA channels have individual configuration and control settings. This include source, destination, transfer triggers, and transaction sizes. They have individual interrupt settings. Interrupt requests can be generated when a transaction is complete or when the DMA controller detects an error on a DMA channel.

To allow for continuous transfers, two channels can be interlinked so that the second takes over the transfer when the first is finished, and vice versa.

# 10. System Clock and Clock options

### 10.1 Features

- Fast start-up time

- Safe run-time clock switching

- Internal oscillators:

- 32MHz run-time calibrated and tunable oscillator

- 2MHz run-time calibrated oscillator

- 32.768kHz calibrated oscillator

- 32kHz ultra low power (ULP) oscillator with 1kHz output

- External clock options

- 0.4MHz 16MHz crystal oscillator

- 32.768kHz crystal oscillator

- External clock

- PLL with 20MHz 128MHz output frequency

- Internal and external clock options and 1x to 31x multiplication

- Lock detector

- Clock prescalers with 1x to 2048x division

- Fast peripheral clocks running at two and four times the CPU clock

- Automatic run-time calibration of internal oscillators

- External oscillator and PLL lock failure detection with optional non-maskable interrupt

#### 10.2 Overview

Atmel AVR XMEGA devices have a flexible clock system supporting a large number of clock sources. It incorporates both accurate internal oscillators and external crystal oscillator and resonator support. A high-frequency phase locked loop (PLL) and clock prescalers can be used to generate a wide range of clock frequencies. A calibration feature (DFLL) is available, and can be used for automatic run-time calibration of the internal oscillators to remove frequency drift over voltage and temperature. An oscillator failure monitor can be enabled to issue a non-maskable interrupt and switch to the internal oscillator if the external oscillator or PLL fails.

When a reset occurs, all clock sources except the 32kHz ultra low power oscillator are disabled. After reset, the device will always start up running from the 2MHz internal oscillator. During normal operation, the system clock source and prescalers can be changed from software at any time.

Figure 10-1 on page 20 presents the principal clock system in the XMEGA A1U family devices. Not all of the clocks need to be active at a given time. The clocks for the CPU and peripherals can be stopped using sleep modes and power reduction registers as described in "Power Management and Sleep Modes" on page 22.

# 11. Power Management and Sleep Modes

## 11.1 Features

- Power management for adjusting power consumption and functions

- Five sleep modes

- Idle

- Power down

- Power save

- Standby

- Extended standby

- Power reduction register to disable clock and turn off unused peripherals in active and idle modes

### 11.2 Overview

Various sleep modes and clock gating are provided in order to tailor power consumption to application requirements. This enables the Atmel AVR XMEGA microcontroller to stop unused modules to save power.

All sleep modes are available and can be entered from active mode. In active mode, the CPU is executing application code. When the device enters sleep mode, program execution is stopped and interrupts or a reset is used to wake the device again. The application code decides which sleep mode to enter and when. Interrupts from enabled peripherals and all enabled reset sources can restore the microcontroller from sleep to active mode.

In addition, power reduction registers provide a method to stop the clock to individual peripherals from software. When this is done, the current state of the peripheral is frozen, and there is no power consumption from that peripheral. This reduces the power consumption in active mode and idle sleep modes and enables much more fine-tuned power management than sleep modes alone.

# 11.3 Sleep Modes

Sleep modes are used to shut down modules and clock domains in the microcontroller in order to save power. XMEGA microcontrollers have five different sleep modes tuned to match the typical functional stages during application execution. A dedicated sleep instruction (SLEEP) is available to enter sleep mode. Interrupts are used to wake the device from sleep, and the available interrupt wake-up sources are dependent on the configured sleep mode. When an enabled interrupt occurs, the device will wake up and execute the interrupt service routine before continuing normal program execution from the first instruction after the SLEEP instruction. If other, higher priority interrupts are pending when the wake-up occurs, their interrupt service routines will be executed according to their priority before the interrupt service routine for the wake-up interrupt is executed. After wake-up, the CPU is halted for four cycles before execution starts.

The content of the register file, SRAM and registers are kept during sleep. If a reset occurs during sleep, the device will reset, start up, and execute from the reset vector.

#### 11.3.1 Idle Mode

In idle mode the CPU and nonvolatile memory are stopped (note that any ongoing programming will be completed), but all peripherals, including the interrupt controller, event system and DMA controller are kept running. Any enabled interrupt will wake the device.

#### 11.3.2 Power-down Mode

In power-down mode, all clocks, including the real-time counter clock source, are stopped. This allows operation only of asynchronous modules that do not require a running clock. The only interrupts that can wake up the MCU are the two-wire interface address match interrupt, asynchronous port interrupts, and the USB resume interrupt.

# 12. System Control and Reset

### 12.1 Features

- Reset the microcontroller and set it to initial state when a reset source goes active

- Multiple reset sources that cover different situations

- Power-on reset

- External reset

- Watchdog reset

- Brownout reset

- PDI reset

- Software reset

- Asynchronous operation

- No running system clock in the device is required for reset

- Reset status register for reading the reset source from the application code

#### 12.2 Overview

The reset system issues a microcontroller reset and sets the device to its initial state. This is for situations where operation should not start or continue, such as when the microcontroller operates below its power supply rating. If a reset source goes active, the device enters and is kept in reset until all reset sources have released their reset. The I/O pins are immediately tri-stated. The program counter is set to the reset vector location, and all I/O registers are set to their initial values. The SRAM content is kept. However, if the device accesses the SRAM when a reset occurs, the content of the accessed location can not be guaranteed.

After reset is released from all reset sources, the default oscillator is started and calibrated before the device starts running from the reset vector address. By default, this is the lowest program memory address, 0, but it is possible to move the reset vector to the lowest address in the boot section.

The reset functionality is asynchronous, and so no running system clock is required to reset the device. The software reset feature makes it possible to issue a controlled system reset from the user software.

The reset status register has individual status flags for each reset source. It is cleared at power-on reset, and shows which sources have issued a reset since the last power-on.

## 12.3 Reset Sequence

A reset request from any reset source will immediately reset the device and keep it in reset as long as the request is active. When all reset requests are released, the device will go through three stages before the device starts running again:

- Reset counter delay

- Oscillator startup

- Oscillator calibration

If another reset requests occurs during this process, the reset sequence will start over again.

#### 12.4 Reset Sources

#### 12.4.1 Power-on Reset

A power-on reset (POR) is generated by an on-chip detection circuit. The POR is activated when the  $V_{CC}$  rises and reaches the POR threshold voltage ( $V_{POT}$ ), and this will start the reset sequence.

The POR is also activated to power down the device properly when the V<sub>CC</sub> falls and drops below the V<sub>POT</sub> level.

The  $V_{POT}$  level is higher for falling  $V_{CC}$  than for rising  $V_{CC}$ . Consult the datasheet for POR characteristics data.

| Base address | Name    | Description                           |

|--------------|---------|---------------------------------------|

| 0x0440       | EBI     | External Bus Interface                |

| 0x0480       | TWIC    | Two Wire Interface on port C          |

| 0x0490       | TWID    | Two Wire Interface on port D          |

| 0x04A0       | TWIE    | Two Wire Interface on port E          |

| 0x04B0       | TWIF    | Two Wire Interface on port F          |

| 0x04C0       | USB     | USB Device                            |

| 0x0600       | PORTA   | Port A                                |

| 0x0620       | PORTB   | Port B                                |

| 0x0640       | PORTC   | Port C                                |

| 0x0660       | PORTD   | Port D                                |

| 0x0680       | PORTE   | Port E                                |

| 0x06A0       | PORTF   | Port F                                |

| 0x06E0       | PORTH   | Port H                                |

| 0x0700       | PORTJ   | Port J                                |

| 0x0720       | PORTK   | Port K                                |

| 0x07C0       | PORTQ   | Port Q                                |

| 0x07E0       | PORTR   | Port R                                |

| 0x0800       | TCC0    | Timer/Counter 0 on port C             |

| 0x0840       | TCC1    | Timer/Counter 1 on port C             |

| 0x0880       | AWEXC   | Advanced Waveform Extension on port C |

| 0x0890       | HIRESC  | High Resolution Extension on port C   |

| 0x08A0       | USARTC0 | USART 0 on port C                     |

| 0x08B0       | USARTC1 | USART 1 on port C                     |

| 0x08C0       | SPIC    | Serial Peripheral Interface on port C |

| 0x08F8       | IRCOM   | Infrared Communication Module         |

| 0x0900       | TCD0    | Timer/Counter 0 on port D             |

| 0x0940       | TCD1    | Timer/Counter 1 on port D             |

| 0x0990       | HIRESD  | High Resolution Extension on port D   |

| 0x09A0       | USARTD0 | USART 0 on port D                     |

| 0x09B0       | USARTD1 | USART 1 on port D                     |

| 0x09C0       | SPID    | Serial Peripheral Interface on port D |

| 0x0A00       | TCE0    | Timer/Counter 0 on port E             |

| 0x0A40       | TCE1    | Timer/Counter 1 on port E             |

| Symbol          | Parameter                                         | Condition                    | Min. | Тур. | Max. | Units |

|-----------------|---------------------------------------------------|------------------------------|------|------|------|-------|

| t <sub>CL</sub> | Clock Low Time                                    | V <sub>CC</sub> = 1.6 - 1.8V | 4.5  |      |      | ns    |

|                 |                                                   | V <sub>CC</sub> = 2.7 - 3.6V | 2.4  |      |      |       |

| +               | Piso Time (for maximum fraguency)                 | V <sub>CC</sub> = 1.6 - 1.8V |      |      | 1.5  | ns    |

| t <sub>CR</sub> | Rise Time (for maximum frequency)                 | V <sub>CC</sub> = 2.7 - 3.6V |      |      | 1.0  | 115   |

| 4               | Fall Time (for maximum fraguency)                 | V <sub>CC</sub> = 1.6 - 1.8V |      |      | 1.5  | no    |

| t <sub>CF</sub> | Fall Time (for maximum frequency)                 | V <sub>CC</sub> = 2.7 - 3.6V |      |      | 1.0  | ns    |

| $\Delta t_{CK}$ | Change in period from one clock cycle to the next |                              |      |      | 10   | %     |

Notes:

- 1. System Clock Prescalers must be set so that maximum CPU clock frequency for device is not exceeded.

- 2. The maximum frequency vs. supply voltage is linear between 1.6V and 2.7V, and the same applies for all other parameters with supply voltage conditions.

# 37.1.14.7 External 16MHz crystal oscillator and XOSC characteristics

Table 37-29. External 16MHz crystal oscillator and XOSC characteristics.

| Symbol | Parameter             | Condition        | Min. | Тур.   | Max. | Units |

|--------|-----------------------|------------------|------|--------|------|-------|

|        | Cycle to cycle jitter | FRQRANGE=0       |      | <10    |      | ns    |

|        |                       | FRQRANGE=1, 2, 3 |      | <1     |      | 115   |

|        |                       | FRQRANGE=0       |      | <0.5   |      |       |

|        | Frequency error       | FRQRANGE=1       |      | <0.05  |      |       |

|        | Frequency entor       | FRQRANGE=2       |      | <0.005 |      |       |

|        |                       | FRQRANGE=3       |      | <0.005 |      | %     |

|        |                       | FRQRANGE=0       |      | 50     |      | /0    |

|        | Duty cycle            | FRQRANGE=1       |      | 50     |      |       |

|        |                       | FRQRANGE=2       |      | 50     |      |       |

|        |                       | FRQRANGE=3       |      | 50     |      |       |

Table 37-34. Two-wire interface characteristics.

| Symbol              | Parameter                                        | Condition                                             | Min.                        | Тур. | Max.                        | Units |

|---------------------|--------------------------------------------------|-------------------------------------------------------|-----------------------------|------|-----------------------------|-------|

| V <sub>IH</sub>     | Input high voltage                               |                                                       | 0.7*V <sub>CC</sub>         |      | V <sub>CC</sub> +0.5        |       |

| $V_{IL}$            | Input low voltage                                |                                                       | -0.5                        |      | 0.3*V <sub>CC</sub>         | V     |

| V <sub>hys</sub>    | Hysteresis of Schmitt trigger inputs             |                                                       | 0.05*V <sub>CC</sub> (1)    |      | 0                           | V     |

| V <sub>OL</sub>     | Output low voltage                               | 3mA, sink current                                     | 0                           |      | 0.4                         |       |

| t <sub>r</sub>      | Rise time for both SDA and SCL                   |                                                       | 20+0.1C <sub>b</sub> (1)(2) |      | 0                           |       |

| t <sub>of</sub>     | Output fall time from $V_{IHmin}$ to $V_{ILmax}$ | 10pF < C <sub>b</sub> < 400pF (2)                     | 20+0.1C <sub>b</sub> (1)(2) |      | 300                         | ns    |

| t <sub>SP</sub>     | Spikes suppressed by input filter                |                                                       | 0                           |      | 50                          |       |

| I <sub>I</sub>      | Input current for each I/O pin                   | $0.1V_{CC} < V_{I} < 0.9V_{CC}$                       | -10                         |      | 10                          | μA    |

| Cı                  | Capacitance for each I/O pin                     |                                                       |                             |      | 10                          | pF    |

| f <sub>SCL</sub>    | SCL clock frequency                              | f <sub>PER</sub> (3)>max(10f <sub>SCL</sub> , 250kHz) | 0                           |      | 400                         | kHz   |

| $R_P$               | Value of pull-up resistor                        | f <sub>SCL</sub> ≤ 100kHz                             | $\frac{V_{CC} - 0.4V}{3mA}$ |      | $\frac{100ns}{C_b}$ $300ns$ | Ω     |

|                     |                                                  | f <sub>SCL</sub> > 100kHz                             | SMA                         |      | $\frac{300ns}{C_b}$         |       |

| t <sub>HD;STA</sub> | Hold time (repeated) START condition             | $f_{SCL} \le 100 kHz$                                 | 4.0                         |      |                             |       |

| HD;SIA              | riola time (repeated) e in tre contaiten         | f <sub>SCL</sub> > 100kHz                             | 0.6                         |      |                             |       |

| $t_{LOW}$           | Low period of SCL clock                          | $f_{SCL} \le 100 kHz$                                 | 4.7                         |      |                             |       |

| LOW                 | 2500 police of 002 olook                         | f <sub>SCL</sub> > 100kHz                             | 1.3                         |      |                             | μs    |

| t <sub>HIGH</sub>   | High period of SCL clock                         | $f_{SCL} \le 100 kHz$                                 | 4.0                         |      |                             | μο    |

| HIGH                | Thigh period of GGE disork                       | f <sub>SCL</sub> > 100kHz                             | 0.6                         |      |                             |       |

| t                   | Set-up time for a repeated START                 | $f_{SCL} \le 100 kHz$                                 | 4.7                         |      |                             |       |

| t <sub>SU;STA</sub> | condition                                        | f <sub>SCL</sub> > 100kHz                             | 0.6                         |      |                             |       |

| t                   | Data hold time                                   | $f_{SCL} \le 100 kHz$                                 | 0                           |      | 3.5                         |       |

| t <sub>HD;DAT</sub> | Bata field time                                  | f <sub>SCL</sub> > 100kHz                             | 0                           |      | 0.9                         |       |

| t                   | Data setup time                                  | $f_{SCL} \le 100 kHz$                                 | 250                         |      |                             |       |

| t <sub>SU;DAT</sub> | Data sotup timo                                  | f <sub>SCL</sub> > 100kHz                             | 100                         |      |                             | μs    |

| t                   | Setup time for STOP condition                    | $f_{SCL} \le 100kHz$                                  | 4.0                         |      |                             | μο    |

| t <sub>su;sto</sub> | Setup time for STOT Condition                    | f <sub>SCL</sub> > 100kHz                             | 0.6                         |      |                             |       |

| t                   | Bus free time between a STOP and                 | $f_{SCL} \le 100 kHz$                                 | 4.7                         |      |                             |       |

| t <sub>BUF</sub>    | START condition                                  | f <sub>SCL</sub> > 100kHz                             | 1.3                         |      |                             |       |

Notes: 1. Required only for  $f_{SCL} > 100 kHz$ .

2.  $C_b$  = Capacitance of one bus line in pF.

3.  $f_{PER}$  = Peripheral clock frequency.

## 37.2 ATxmega128A1U

## 37.2.1 Absolute Maximum Ratings

Stresses beyond those listed in Table 37-35 on page 97 under may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 37-35. Absolute maximum ratings.

| Symbol           | Parameter                                           | Condition | Min. | Тур. | Max.                 | Units |

|------------------|-----------------------------------------------------|-----------|------|------|----------------------|-------|

| V <sub>CC</sub>  | Power supply voltage                                |           | -0.3 |      | 4                    | V     |

| I <sub>vcc</sub> | Current into a V <sub>CC</sub> pin                  |           |      |      | 200                  | mA    |

| I <sub>GND</sub> | Current out of a Gnd pin                            |           |      |      | 200                  | IIIA  |

| V <sub>PIN</sub> | Pin voltage with respect to Gnd and $V_{\text{CC}}$ |           | -0.5 |      | V <sub>CC</sub> +0.5 | V     |

| I <sub>PIN</sub> | I/O pin sink/source current                         |           | -25  |      | 25                   | mA    |

| T <sub>A</sub>   | Storage temperature                                 |           | -65  |      | 150                  | °C    |

| T <sub>j</sub>   | Junction temperature                                |           |      |      | 150                  | C     |

## 37.2.2 General Operating Ratings

The device must operate within the ratings listed in Table 37-36 in order for all other electrical characteristics and typical characteristics of the device to be valid.

Table 37-36. General operating conditions.

| Symbol           | Parameter             | Condition | Min. | Тур. | Max. | Units |

|------------------|-----------------------|-----------|------|------|------|-------|

| V <sub>CC</sub>  | Power supply voltage  |           | 1.60 |      | 3.6  | V     |

| AV <sub>CC</sub> | Analog supply voltage |           | 1.60 |      | 3.6  | V     |

| T <sub>A</sub>   | Temperature range     |           | -40  |      | 85   | °C    |

| T <sub>j</sub>   | Junction temperature  |           | -40  |      | 105  |       |

Table 37-37. Operating voltage and frequency.

| Symbol             | Parameter           | Condition              | Min. | Тур. | Max. | Units   |

|--------------------|---------------------|------------------------|------|------|------|---------|

| Clk <sub>CPU</sub> | CPU clock frequency | V <sub>CC</sub> = 1.6V | 0    |      | 12   |         |

|                    |                     | V <sub>CC</sub> = 1.8V | 0    |      | 12   | MHz     |

|                    |                     | V <sub>CC</sub> = 2.7V | 0    |      | 32   | IVII IZ |

|                    |                     | V <sub>CC</sub> = 3.6V | 0    |      | 32   |         |

The maximum CPU clock frequency depends on  $V_{CC}$ . As shown in Figure 37-8 the Frequency vs.  $V_{CC}$  curve is linear between 1.8V <  $V_{CC}$  < 2.7V.

Table 37-39. Current consumption for modules and peripherals.

| Symbol          | Parameter                 | Condition <sup>(1)</sup>              |                                    | Min. | Тур. | Max. | Units |

|-----------------|---------------------------|---------------------------------------|------------------------------------|------|------|------|-------|

|                 | ULP oscillator            |                                       |                                    |      | 1.0  |      |       |

|                 | 32.768kHz int. oscillator |                                       |                                    |      | 27   |      |       |

|                 | 2MHz int. oscillator      |                                       |                                    |      | 85   |      |       |

|                 | ZIVII IZ IIII. OSCIIIAIOI | DFLL enabled wit                      | h 32.768kHz int. osc. as reference |      | 120  |      |       |

|                 | 32MHz int. oscillator     |                                       |                                    |      | 310  |      |       |

|                 | 32WHZ IIII. OSCIIIAIOI    | DFLL enabled wit                      | h 32.768kHz int. osc. as reference |      | 560  |      | μA    |

|                 | Watchdog timer            |                                       |                                    |      | 1.0  |      |       |

|                 | BOD                       | Continuous mode                       |                                    |      | 126  |      |       |

|                 | ВОВ                       | Sampled mode, in                      | ncludes ULP oscillator             |      | 1.2  |      |       |

|                 | Internal 1.0V reference   |                                       |                                    |      | 89   |      |       |

|                 | Temperature sensor        |                                       |                                    |      | 83   |      |       |

| I <sub>CC</sub> | ADC                       |                                       |                                    |      | 3.0  |      |       |

|                 |                           | 250ksps                               | CURRLIMIT = LOW                    |      | 2.6  |      |       |

|                 |                           | V <sub>REF</sub> = Ext ref            | CURRLIMIT = MEDIUM                 |      | 2.1  |      | A     |

|                 |                           |                                       | CURRLIMIT = HIGH                   |      | 1.6  |      | mA    |

|                 | DAG                       | 250ksps                               | Normal mode                        |      | 1.9  |      |       |

|                 | DAC                       | V <sub>REF</sub> = Ext ref<br>No load | Low Power mode                     |      | 1.1  |      |       |

|                 | 40                        | High speed mode                       |                                    |      | 324  |      |       |

|                 | AC                        | Low power mode                        |                                    |      | 122  |      |       |

|                 | DMA                       | 615KBps betweer                       | I/O registers and SRAM             |      | 140  |      | μA    |

|                 | Timer/counter             |                                       |                                    |      | 20   |      |       |

|                 | USART                     | Rx and Tx enable                      | d, 9600 BAUD                       |      | 4    |      |       |

|                 | Flash memory and EEPRC    | OM programming                        |                                    |      | 4    |      | mA    |

Note:

<sup>1.</sup> All parameters measured as the difference in current consumption between module enabled and disabled. All data at V<sub>CC</sub> = 3.0V, Clk<sub>SYS</sub> = 1MHz external clock without prescaling, T = 25°C unless other conditions are given.

| Symbol             | Parameter                  | Condition                                 | Min.      | Тур. | Max. | Units |     |

|--------------------|----------------------------|-------------------------------------------|-----------|------|------|-------|-----|

|                    |                            | V <sub>CC</sub> = 3.0V, T= 85°C           | mode = HS |      | 60   | 90    |     |

| t <sub>delay</sub> | Propagation delay          | mode = HS                                 |           |      | 60   |       | ns  |

|                    |                            | V <sub>CC</sub> = 3.0V, T= 85°C mode = LP |           |      | 130  |       |     |

|                    | Current source calibration | Single mode                               |           | 2    |      | 8     | 110 |

|                    | range                      | Double mode                               |           | 4    |      | 16    | μs  |

|                    | 64-Level Voltage Scaler    | Integral non-linearity (INL)              |           |      | 0.3  | 0.5   | Isb |

# 37.2.9 Bandgap and Internal 1.0V Reference Characteristics

Table 37-50. Bandgap and Internal 1.0V reference characteristics.

| Symbol | Parameter                                | Condition                                   | Min. | Тур.                     | Max. | Units |

|--------|------------------------------------------|---------------------------------------------|------|--------------------------|------|-------|

|        | Startup time                             | As reference for ADC or DAC                 | 1 (  | Clk <sub>PER</sub> + 2.5 | īμs  |       |

|        | Startup time                             | As input voltage to ADC and AC              |      | 1.5                      |      | μs    |

|        | Bandgap voltage                          |                                             |      | 1.1                      |      | V     |

| INT1V  | Internal 1.00V reference for ADC and DAC | T= 85°C, after calibration                  | 0.99 | 1                        | 1.01 | V     |

|        | Variation over voltage and temperature   | Relative to T= 85°C, V <sub>CC</sub> = 3.0V |      | ±1.0                     |      | %     |

# **37.2.10 Brownout Detection Characteristics**

Table 37-51. Brownout detection characteristics.

| Symbol            | Parameter                           | Condition       | Min. | Тур. | Max. | Units |

|-------------------|-------------------------------------|-----------------|------|------|------|-------|

|                   | BOD level 0 falling V <sub>CC</sub> |                 | 1.60 | 1.62 | 1.72 |       |

|                   | BOD level 1 falling V <sub>CC</sub> |                 |      | 1.8  |      |       |

|                   | BOD level 2 falling V <sub>CC</sub> |                 |      | 2.0  |      |       |

| V                 | BOD level 3 falling V <sub>CC</sub> |                 |      | 2.2  |      | V     |

| V <sub>BOT</sub>  | BOD level 4 falling V <sub>CC</sub> |                 |      | 2.4  |      | V     |

|                   | BOD level 5 falling V <sub>CC</sub> |                 |      | 2.6  |      |       |

|                   | BOD level 6 falling V <sub>CC</sub> |                 |      | 2.8  |      |       |

|                   | BOD level 7 falling V <sub>CC</sub> |                 |      | 3.0  |      |       |

| t                 | Detection time                      | Continuous mode |      | 0.4  |      | 116   |

| t <sub>BOD</sub>  | Detection time                      | Sampled mode    |      | 1000 |      | μs    |

| V <sub>HYST</sub> | Hysteresis                          |                 |      | 1.4  |      | %     |

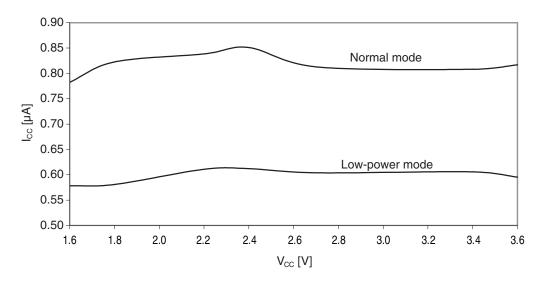

## 38.1.1.4 Power-save mode supply current

Figure 38-17.Power-save mode supply current vs.  $V_{CC}$ .

Real Time Counter enabled and running from 1.024kHz output of 32.768kHz TOSC.

# 38.1.1.5 Standby mode supply current

Figure 38-18. Standby supply current vs.  $V_{CC}$ . Standby,  $f_{SYS} = 1MHz$ .

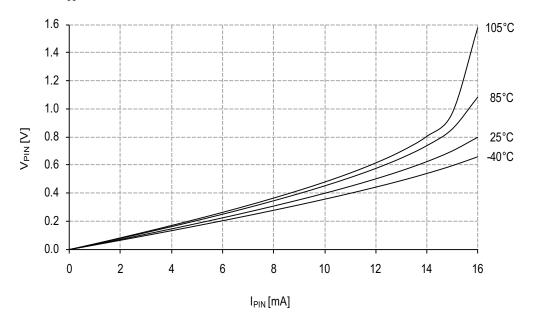

Figure 38-27.I/O pin output voltage vs. sink current.

$$V_{CC} = 1.8V.$$

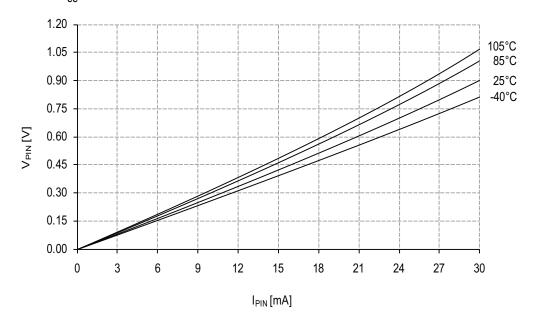

Figure 38-28.I/O pin output voltage vs. sink current.

$$V_{CC} = 3.0V.$$

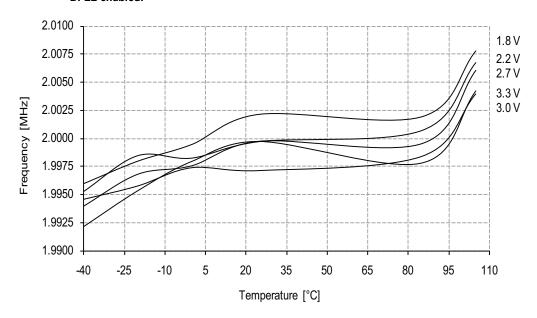

Figure 38-73. 2MHz internal oscillator frequency vs. temperature. DFLL enabled.

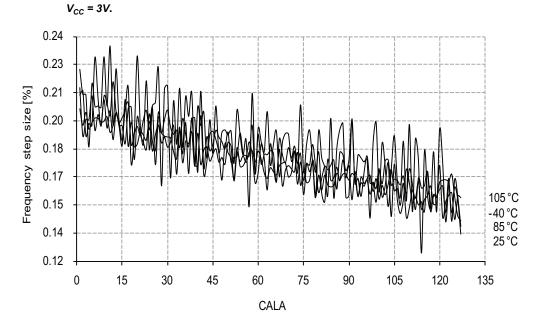

Figure 38-74. 2MHz internal oscillator CALA calibration step size.

# 38.2 ATxmega128A1U

# 38.2.1 Current consumption

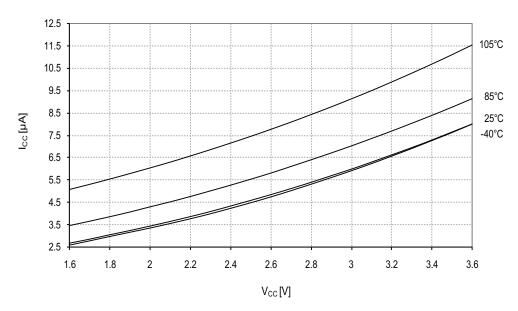

## 38.2.1.1 Active mode supply current

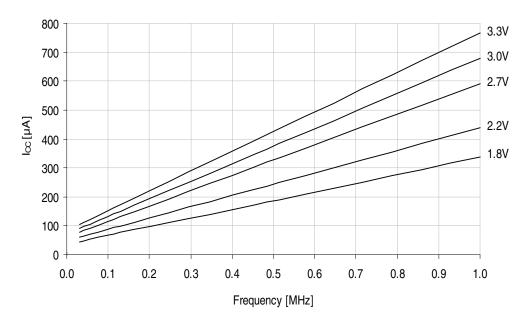

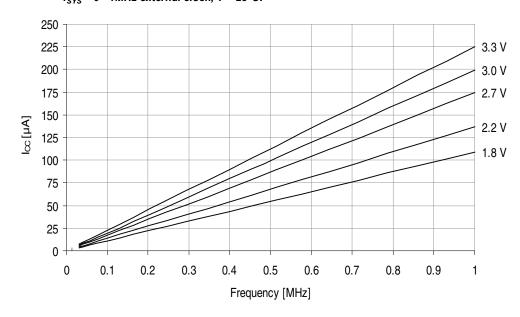

Figure 38-83. Active supply current vs. frequency.  $f_{SYS} = 0$  - 1MHz external clock,  $T = 25^{\circ}$ C.

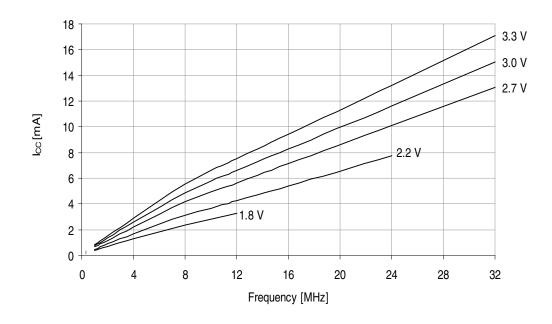

Figure 38-84. Active supply current vs. frequency.  $f_{SYS} = 1 - 32MHz$  external clock, T = 25°C.

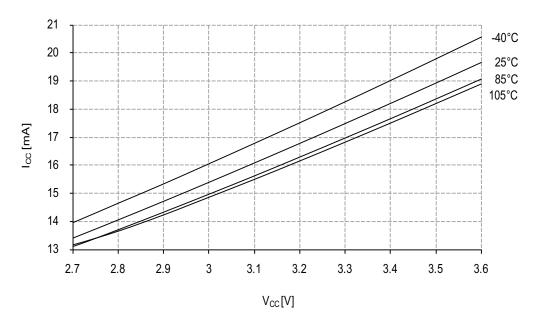

Figure 38-89. Active mode supply current vs.  $V_{CC}$ .  $f_{SYS} = 32MHz$  internal oscillator.

# 38.2.1.2 Idle mode supply current

Figure 38-90.ldle mode supply current vs. frequency.  $f_{SYS} = 0 - 1MHz$  external clock,  $T = 25^{\circ}C$ .

## 38.2.1.4 Power-save mode supply current

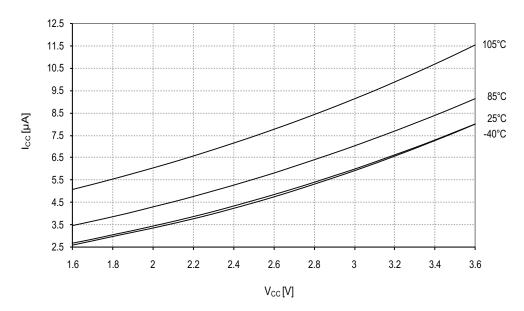

Figure 38-99.Power-save mode supply current vs.  $V_{CC}$ .

Real Time Counter enabled and running from 1.024kHz output of 32.768kHz TOSC.

# 38.2.1.5 Standby mode supply current

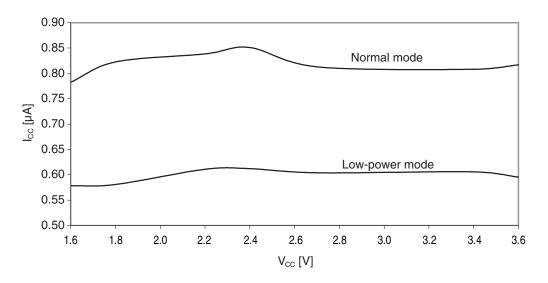

Figure 38-100. Standby supply current vs.  $V_{CC}$ . Standby,  $f_{SYS} = 1MHz$ .

## 38.2.3 ADC Characteristics

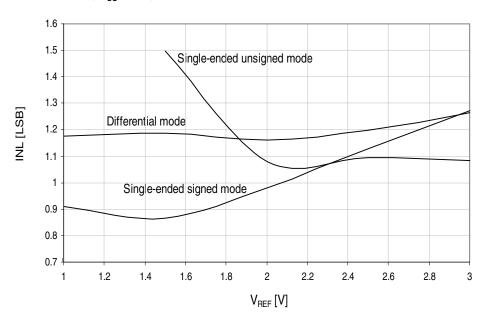

Figure 38-117.INL error vs. external  $V_{REF}$ .  $T = 25 \, \text{C}$ ,  $V_{CC} = 3.6 V$ , external reference.

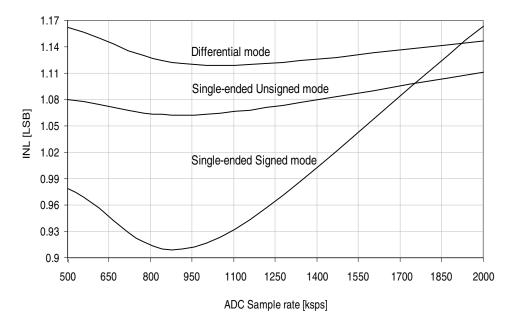

Figure 38-118.INL error vs. sample rate.

$$T=25\,\mathrm{C},~V_{CC}=3.6V,~V_{REF}=2.0V$$

external.

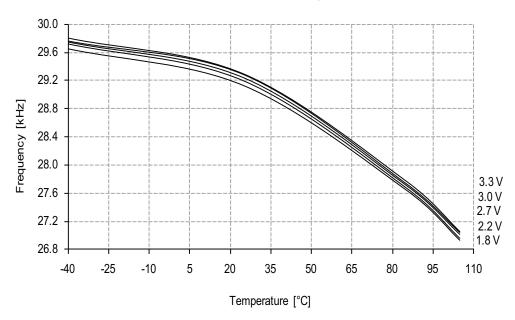

### 38.2.10 Oscillator Characteristics

#### 38.2.10.1 Ultra Low-Power internal oscillator

Figure 38-151.Ultra Low-Power internal oscillator frequency vs. temperature.

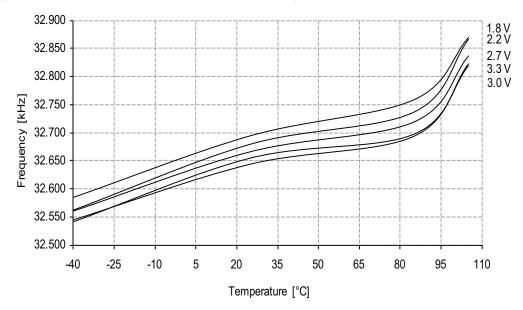

#### 38.2.10.2 32.768kHz Internal Oscillator

Figure 38-152. 32.768kHz internal oscillator frequency vs. temperature.

## 4. Configuration of PGM and CWCM is not as described in XMEGA AU Manual

Configuration of common waveform channel mode (CWCM) and pattern generation mode (PGM), is not as described in the XMEGA AU manual.

#### Problem fix/Workaround

Configure PWM and CWCM according to the Table 39-1 on page 203.

Table 39-1. PWM and CWCM configuration.

| PGM | смсм | Description           |

|-----|------|-----------------------|

| 0   | 0    | PGM and CWCM disabled |

| 0   | 1    | PGM enabled           |

| 1   | 0    | PGM and CWCM enabled  |

| 1   | 1    | PGM enabled           |

## 5. AWEX PWM output after fault restarted with wrong values

When recovering from fault state, the PWM output will drive wrong values to the port for up to two  $CLK_{PER}$  + one  $CLK_{PER4}$  cycles.

#### Problem fix/Workaround

The following segence can be used in Latched Mode:

- a. Disable DTI outputs (Write DTICCxEN to 0)

- b. Clear fault flag

- c. Wait for Overflow

- d. Re-enable DTI (Write DTICCxEN to 1)

- e. Set pin direction to Output

This will remove the glitch, but the following period will be shorter. In Cycle-by-cycle mode the same procedure can be followed as long as the Pattern Generation Mode is not enabled.

For Pattern generation mode, there is no workaround.

#### 6. RTC Counter value not correctly read after sleep

If a real time counter (RTC) interrupt is used wake up the device from sleep, and bit 0 of RTC count register (CNT) has the same value as when the device entered sleep, CNT will not be read correctly during the first prescaled RTC clock cycle after wakeup. The value read will be the same as the value in the register was when entering sleep.

#### Problem fix/Workaround

Wait at least one prescaled RTC clock cycle before reading CNT.

## 7. RTC clock output option is non-functional

The real time counter (RTC) as clock output option is non-functional, and setting the RTCOUT bit in the clock and event out register (CLKEVOUT) will have no effect.

#### Problem fix/Workaround

None

|     | 22.1 Features         22.2 Overview                                                              |      |

|-----|--------------------------------------------------------------------------------------------------|------|

| 23. | SPI – Serial Peripheral Interface                                                                | . 43 |

| 24. | USART                                                                                            | . 44 |

| 25. | IRCOM – IR Communication Module  25.1 Features  25.2 Overview                                    | . 45 |

| 26. | AES and DES Crypto Engine                                                                        | . 46 |

| 27. | CRC – Cyclic Redundancy Check Generator  27.1 Features  27.2 Overview                            | . 47 |

| 28. | EBI – External Bus Interface  28.1 Features  28.2 Overview                                       | . 48 |

| 29. | ADC – 12-bit Analog to Digital Converter  29.1 Features  29.2 Overview                           | . 49 |

| 30. | DAC – 12-bit Digital to Analog Converter  30.1 Features  30.2 Overview                           | . 51 |

| 31. | AC – Analog Comparator  31.1 Features  31.2 Overview                                             | . 53 |

| 32. | PDI – Programming and Debugging                                                                  | . 55 |

| 33. | Pinout and Pin Functions  33.1 Alternate Pin Function Description  33.2 Alternate Pin Functions. | . 56 |

| 34. | Peripheral Module Address Map                                                                    | 63   |

| 35. | Instruction Set Summary                                                                          | 66   |

|     | Packaging information                                                                            | 71   |