#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | AVR                                                                         |

| Core Size                  | 8/16-Bit                                                                    |

| Speed                      | 32MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                  |

| Number of I/O              | 78                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 2K x 8                                                                      |

| RAM Size                   | 8K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                                 |

| Data Converters            | A/D 16x12b; D/A 4x12b                                                       |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-TQFP                                                                    |

| Supplier Device Package    | 100-TQFP (14x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega128a1u-aur |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 6. AVR CPU

# 6.1 Features

- 8/16-bit, high-performance Atmel AVR RISC CPU

- 142 instructions

- Hardware multiplier

- 32x8-bit registers directly connected to the ALU

- Stack in RAM

- Stack pointer accessible in I/O memory space

- Direct addressing of up to 16MB of program memory and 16MB of data memory

- True 16/24-bit access to 16/24-bit I/O registers

- Efficient support for 8-, 16-, and 32-bit arithmetic

- Configuration change protection of system-critical features

## 6.2 Overview

All Atmel AVR XMEGA devices use the 8/16-bit AVR CPU. The main function of the CPU is to execute the code and perform all calculations. The CPU is able to access memories, perform calculations, control peripherals, and execute the program in the flash memory. Interrupt handling is described in a separate section, refer to "Interrupts and Programmable Multilevel Interrupt Controller" on page 27.

# 6.3 Architectural Overview

In order to maximize performance and parallelism, the AVR CPU uses a Harvard architecture with separate memories and buses for program and data. Instructions in the program memory are executed with single-level pipelining. While one instruction is being executed, the next instruction is pre-fetched from the program memory. This enables instructions to be executed on every clock cycle. For details of all AVR instructions, refer to http://www.atmel.com/avr.

#### Figure 6-1. Block diagram of the AVR CPU architecture.

# Atmel

# 11. Power Management and Sleep Modes

## 11.1 Features

- Power management for adjusting power consumption and functions

- Five sleep modes

- Idle

- Power down

- Power save

- Standby

- Extended standby

- Power reduction register to disable clock and turn off unused peripherals in active and idle modes

# 11.2 Overview

Various sleep modes and clock gating are provided in order to tailor power consumption to application requirements. This enables the Atmel AVR XMEGA microcontroller to stop unused modules to save power.

All sleep modes are available and can be entered from active mode. In active mode, the CPU is executing application code. When the device enters sleep mode, program execution is stopped and interrupts or a reset is used to wake the device again. The application code decides which sleep mode to enter and when. Interrupts from enabled peripherals and all enabled reset sources can restore the microcontroller from sleep to active mode.

In addition, power reduction registers provide a method to stop the clock to individual peripherals from software. When this is done, the current state of the peripheral is frozen, and there is no power consumption from that peripheral. This reduces the power consumption in active mode and idle sleep modes and enables much more fine-tuned power management than sleep modes alone.

## 11.3 Sleep Modes

Sleep modes are used to shut down modules and clock domains in the microcontroller in order to save power. XMEGA microcontrollers have five different sleep modes tuned to match the typical functional stages during application execution. A dedicated sleep instruction (SLEEP) is available to enter sleep mode. Interrupts are used to wake the device from sleep, and the available interrupt wake-up sources are dependent on the configured sleep mode. When an enabled interrupt occurs, the device will wake up and execute the interrupt service routine before continuing normal program execution from the first instruction after the SLEEP instruction. If other, higher priority interrupts are pending when the wake-up occurs, their interrupt service routines will be executed according to their priority before the interrupt service routine for the wake-up interrupt is executed. After wake-up, the CPU is halted for four cycles before execution starts.

The content of the register file, SRAM and registers are kept during sleep. If a reset occurs during sleep, the device will reset, start up, and execute from the reset vector.

### 11.3.1 Idle Mode

In idle mode the CPU and nonvolatile memory are stopped (note that any ongoing programming will be completed), but all peripherals, including the interrupt controller, event system and DMA controller are kept running. Any enabled interrupt will wake the device.

### 11.3.2 Power-down Mode

In power-down mode, all clocks, including the real-time counter clock source, are stopped. This allows operation only of asynchronous modules that do not require a running clock. The only interrupts that can wake up the MCU are the twowire interface address match interrupt, asynchronous port interrupts, and the USB resume interrupt.

| Program address<br>(base address) | Source           | Interrupt description                                |

|-----------------------------------|------------------|------------------------------------------------------|

| 0x028                             | TCC1_INT_base    | Timer/counter 1 on port C interrupt base             |

| 0x030                             | SPIC_INT_vect    | SPI on port C interrupt vector                       |

| 0x032                             | USARTC0_INT_base | USART 0 on port C interrupt base                     |

| 0x038                             | USARTC1_INT_base | USART 1 on port C interrupt base                     |

| 0x03E                             | AES_INT_vect     | AES interrupt vector                                 |

| 0x040                             | NVM_INT_base     | Nonvolatile memory interrupt base                    |

| 0x044                             | PORTB_INT_base   | Port B interrupt base                                |

| 0x048                             | ACB_INT_base     | Analog comparator on port B interrupt base           |

| 0x04E                             | ADCB_INT_base    | Analog to digital converter on port B interrupt base |

| 0x056                             | PORTE_INT_base   | Port E interrupt base                                |

| 0x05A                             | TWIE_INT_base    | Two-Wire interface on port E interrupt base          |

| 0x05E                             | TCE0_INT_base    | Timer/counter 0 on port E interrupt base             |

| 0x06A                             | TCE1_INT_base    | Timer/counter 1 on port E interrupt base             |

| 0x072                             | SPIE_INT_vect    | SPI on port E interrupt vector                       |

| 0x074                             | USARTE0_INT_base | USART 0 on port E interrupt base                     |

| 0x07A                             | USARTE1_INT_base | USART 1 on port E interrupt base                     |

| 0x080                             | PORTD_INT_base   | Port D interrupt base                                |

| 0x084                             | PORTA_INT_base   | Port A interrupt base                                |

| 0x088                             | ACA_INT_base     | Analog comparator on Port A interrupt base           |

| 0x08E                             | ADCA_INT_base    | Analog to digital converter on Port A interrupt base |

| 0x096                             | TWID_INT_base    | Two-Wire Interface on port D interrupt base          |

| 0x09A                             | TCD0_INT_base    | Timer/counter 0 on port D interrupt base             |

| 0x0A6                             | TCD1_INT_base    | Timer/counter 1 on port D interrupt base             |

| 0x0AE                             | SPID_INT_vector  | SPI on port D interrupt vector                       |

| 0x0B0                             | USARTD0_INT_base | USART 0 on port D interrupt base                     |

| 0x0B6                             | USARTD1_INT_base | USART 1 on port D interrupt base                     |

| 0x0BC                             | PORTQ_INT_base   | Port Q INT base                                      |

| 0x0C0                             | PORTH_INT_base   | Port H INT base                                      |

| 0x0C4                             | PORTJ_INT_base   | Port J INT base                                      |

| 0x0C8                             | PORTK_INT_base   | Port K INT base                                      |

| 0x0D0                             | PORTF_INT_base   | Port F INT base                                      |

| 0x0D4                             | TWIF_INT_base    | Two-Wire interface on Port F INT base                |

| 0x0D8                             | TCF0_INT_base    | Timer/counter 0 on port F interrupt base             |

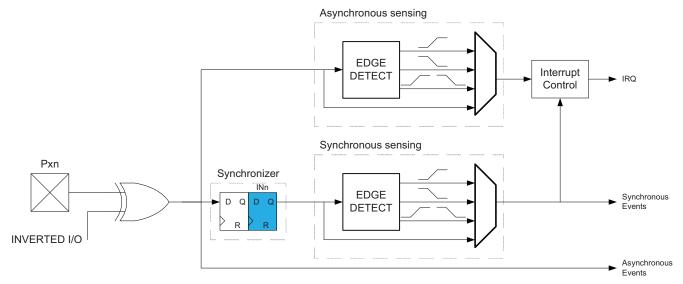

# 15.4 Input sensing

Input sensing is synchronous or asynchronous depending on the enabled clock for the ports, and the configuration is shown in Figure 15-7 on page 33.

When a pin is configured with inverted I/O, the pin value is inverted before the input sensing.

## 15.5 Alternate Port Functions

Most port pins have alternate pin functions in addition to being a general purpose I/O pin. When an alternate function is enabled, it might override the normal port pin function or pin value. This happens when other peripherals that require pins are enabled or configured to use pins. If and how a peripheral will override and use pins is described in the section for that peripheral. "Pinout and Pin Functions" on page 56 shows which modules on peripherals that enable alternate functions on a pin, and what alternate functions that are available on a pin.

# 28. EBI – External Bus Interface

## 28.1 Features

- Supports SRAM up to:

- 512KB using 2- or 3-port EBI configuration

- 16MB using 3- or 4-port EBI configuration

- Supports SDRAM up to:

- 128Mb using 3- or 4-port EBI configuration

- 4-bit SDRAM with 3-port EBI configuration

- 4- or 8-bit SDRAM with 4-port EBI configuration

- Four software configurable chip selects

- Software configurable wait state insertion

- Can run from the 2x peripheral clock frequency for fast access

- Simultaneous SRAM and SDRAM support with 4-port EBI configuration

# 28.2 Overview

The External Bus Interface (EBI) is used to connect external peripherals and memory for accessthrough the data memory space. When the EBI is enabled, data address space outside the internal SRAM becomes available using dedicated EBI pins.

The EBI can interface external SRAM, SDRAM, and peripherals, such as LCD displays and other memory mapped devices.

The address space for the external memory is selectable from 256 bytes (8-bit) up to 16MB (24-bit). Various multiplexing modes for address and data lines can be selected for optimal use of pins when more or fewer pins are available for the EBI. The complete memory will be mapped into one linear data address space continuing from the end of the internal SRAM.

The EBI has four chip selects, each with separate configuration. Each can be configured for SRAM, SRAM low pin count (LPC), or SDRAM.

The EBI is clocked from the fast, 2x peripheral clock, running up to two times faster than the CPU.

Four-bit and eight-bit SDRAM are supported, and SDRAM configurations, such as CAS latency and refresh rate, are configurable in software.

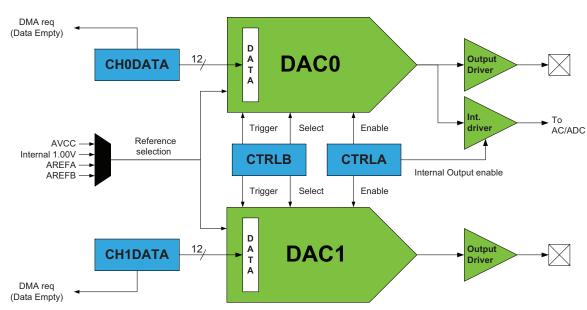

# 30. DAC – 12-bit Digital to Analog Converter

# 30.1 Features

- Two digital to analog converters (DACs)

- 12-bit resolution

- Two independent, continuous-drive output channels

- Up to one million samples per second conversion rate per DAC channel

- Built-in calibration that removes:

- Offset error

- Gain error

- Multiple conversion trigger sources

- On new available data

- Events from the event system

- High drive capabilities and support for

- Resistive loads

- Capacitive loads

- Combined resistive and capacitive loads

- Internal and external reference options

- DAC output available as input to analog comparator and ADC

- Low-power mode, with reduced drive strength

- Optional DMA transfer of data

# 30.2 Overview

The digital-to-analog converter (DAC) converts digital values to voltages. The DAC has two channels, each with12-bit resolution, and is capable of converting up to one million samples per second (msps) on each channel. The built-in calibration system can remove offset and gain error when loaded with calibration values from software.

### Figure 30-1. DAC overview.

| PORT E | PIN # | INTERRUPT  | TCE0 | AWEXE  | TCE1 | USARTE0 | USARTE1 | SPIE | TWIE | CLOCKOUT           | EVENTOUT |

|--------|-------|------------|------|--------|------|---------|---------|------|------|--------------------|----------|

| PE2    | 37    | SYNC/ASYNC | OC0C | OC0BLS |      | RXD0    |         |      |      |                    |          |

| PE3    | 38    | SYNC       | OC0D | OC0BHS |      | TXD0    |         |      |      |                    |          |

| PE4    | 39    | SYNC       |      | OCOCLS | OC1A |         |         | SS   |      |                    |          |

| PE5    | 40    | SYNC       |      | OC0CHS | OC1B |         | XCK1    | MOSI |      |                    |          |

| PE6    | 41    | SYNC       |      | OC0DLS |      |         | RXD1    | MISO |      |                    |          |

| PE7    | 42    | SYNC       |      | OC0DHS |      |         | TXD1    | SCK  |      | clk <sub>PER</sub> | EVOUT    |

Notes:

1. All pins on the port can optionally be used for EBI chip select or address lines. Refer to the EBIOUT register description in the XMEGA AU Manual.

#### Table 33-6. Port F - alternate functions.

| PORT F | PIN # | INTERRUPT  | TCF0 | TCF1 | USARTF0 | USARTF1 | SPIF | TWIF |

|--------|-------|------------|------|------|---------|---------|------|------|

| GND    | 43    |            |      |      |         |         |      |      |

| vcc    | 44    |            |      |      |         |         |      |      |

| PF0    | 45    | SYNC       | OC0A |      |         |         |      | SDA  |

| PF1    | 46    | SYNC       | OC0B |      | XCK0    |         |      | SCL  |

| PF2    | 47    | SYNC/ASYNC | OC0C |      | RXD0    |         |      |      |

| PF3    | 48    | SYNC       | OC0D |      | TXD0    |         |      |      |

| PF4    | 49    | SYNC       |      | OC1A |         |         | SS   |      |

| PF5    | 50    | SYNC       |      | OC1B |         | XCK1    | MOSI |      |

| PF6    | 51    | SYNC       |      |      |         | RXD1    | MISO |      |

| PF7    | 52    | SYNC       |      |      |         | TXD1    | SCK  |      |

Note: 1. All pins on the port can optionally be used for EBI chip select or address lines. Refer to the EBIOUT register description in the XMEGA AU Manual.

#### Table 33-7. Port H - alternate functions.

| PORT H | PIN # | INTERRUPT  | SDRAM 3P | SRAM ALE1 | SRAM ALE12 | LPC3 ALE1 | LPC2 ALE1 | LPC2 ALE12 |

|--------|-------|------------|----------|-----------|------------|-----------|-----------|------------|

| GND    | 53    |            |          |           |            |           |           |            |

| VCC    | 54    |            |          |           |            |           |           |            |

| PH0    | 55    | SYNC       | WE       | WE        | WE         | WE        | WE        | WE         |

| PH1    | 56    | SYNC       | CAS      | RE        | RE         | RE        | RE        | RE         |

| PH2    | 57    | SYNC/ASYNC | RAS      | ALE1      | ALE1       | ALE1      | ALE1      | ALE1       |

| PH3    | 58    | SYNC       | DQM      |           | ALE2       |           |           | ALE2       |

| PH4    | 59    | SYNC       | BA0      | CS0/A16   | CS0        | CS0/A16   | CS0       | CS0/A16    |

| PH5    | 60    | SYNC       | BA1      | CS1/A17   | CS1        | CS1/A17   | CS1       | CS1/A17    |

| PH6    | 61    | SYNC       | CKE      | CS2/A18   | CS2        | CS2/A18   | CS2       | CS2/A18    |

| PH7    | 62    | SYNC       | CLK      | CS3/A19   | CS3        | CS3/A19   | CS3       | CS3/A19    |

Notes: 1. CS0 - CS3 can optionally be moved to Port E or F

2. A16-A23 can optionally be moved to Port E or F when EBI configured in 4PORT mode. Refer to the EBIOUT register description in the XMEGA AU Manual.

| Mnemonics | Operands | Description                     | Operation                       | Flags | #Clocks |

|-----------|----------|---------------------------------|---------------------------------|-------|---------|

| SEV       |          | Set Two's Complement Overflow   | V ← 1                           | V     | 1       |

| CLV       |          | Clear Two's Complement Overflow | V ← 0                           | V     | 1       |

| SET       |          | Set T in SREG                   | T ← 1                           | т     | 1       |

| CLT       |          | Clear T in SREG                 | T ← 0                           | т     | 1       |

| SEH       |          | Set Half Carry Flag in SREG     | H ← 1                           | н     | 1       |

| CLH       |          | Clear Half Carry Flag in SREG   | H ← 0                           | н     | 1       |

|           |          | MCU o                           | control instructions            |       |         |

| BREAK     |          | Break                           | (See specific descr. for BREAK) | None  | 1       |

| NOP       |          | No Operation                    |                                 | None  | 1       |

| SLEEP     |          | Sleep                           | (see specific descr. for Sleep) | None  | 1       |

| WDR       |          | Watchdog Reset                  | (see specific descr. for WDR)   | None  | 1       |

Notes: 1. Cycle times for Data memory accesses assume internal memory accesses, and are not valid for accesses via the external RAM interface.

2. One extra cycle must be added when accessing Internal SRAM.

# Atmel

# 37. Electrical Characteristics

All typical values are measured at  $T = 25^{\circ}C$  unless other temperature condition is given. All minimum and maximum values are valid across operating temperature and voltage unless other conditions are given.

Note: For devices that are not available yet, preliminary values in this datasheet are based on simulations, and/or characterization of similar AVR XMEGA microcontrollers. After the device is characterized the final values will be available, hence existing values can change. Missing minimum and maximum values will be available after the device is characterized.

## 37.1 ATxmega64A1U

#### 37.1.1 Absolute Maximum Ratings

Stresses beyond those listed in Table 37-1 on page 74 under may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Table 37-1. Absolute maximum ratings.

| Symbol           | Parameter                                                      | Condition | Min. | Тур. | Max.                 | Units |

|------------------|----------------------------------------------------------------|-----------|------|------|----------------------|-------|

| V <sub>CC</sub>  | Power supply voltage                                           |           | -0.3 |      | 4                    | V     |

| I <sub>VCC</sub> | Current into a $V_{CC}$ pin                                    |           |      |      | 200                  | mA    |

| I <sub>GND</sub> | Current out of a Gnd pin                                       |           |      |      | 200                  | ША    |

| V <sub>PIN</sub> | Pin voltage with respect to Gnd and $\mathrm{V}_{\mathrm{CC}}$ |           | -0.5 |      | V <sub>CC</sub> +0.5 | V     |

| I <sub>PIN</sub> | I/O pin sink/source current                                    |           | -25  |      | 25                   | mA    |

| T <sub>A</sub>   | Storage temperature                                            |           | -65  |      | 150                  | °C    |

| Tj               | Junction temperature                                           |           |      |      | 150                  | C     |

### 37.1.2 General Operating Ratings

The device must operate within the ratings listed in Table 37-2 in order for all other electrical characteristics and typical characteristics of the device to be valid.

#### Table 37-2. General operating conditions.

| Symbol           | Parameter             | Condition | Min. | Тур. | Max. | Units |

|------------------|-----------------------|-----------|------|------|------|-------|

| V <sub>CC</sub>  | Power supply voltage  |           | 1.60 |      | 3.6  | V     |

| AV <sub>CC</sub> | Analog supply voltage |           | 1.60 |      | 3.6  | v     |

| T <sub>A</sub>   | Temperature range     |           | -40  |      | 85   | °C    |

| Tj               | Junction temperature  |           | -40  |      | 105  | C     |

#### 37.1.14.3 Calibrated and tunable 32MHz internal oscillator characteristics

#### Table 37-24. 32MHz internal oscillator characteristics.

| Symbol | Parameter                    | Condition                                                    | Min. | Тур. | Max. | Units |

|--------|------------------------------|--------------------------------------------------------------|------|------|------|-------|

|        | Tunable frequency range      | DFLL can tune to this frequency over voltage and temperature | 30   |      | 35   | MHz   |

|        | Factory calibrated frequency |                                                              |      | 32   |      |       |

|        | Factory calibration accuracy | T = 85°C, V <sub>CC</sub> = 3.0V                             | -1.5 |      | 1.5  | %     |

|        | DFLL calibration step size   |                                                              |      | 0.24 |      | 70    |

#### 37.1.14.4 32kHz Internal ULP Oscillator characteristics

#### Table 37-25. 32kHz internal ULP oscillator characteristics.

| Symbol | Parameter        | Condition | Min. | Тур. | Max. | Units |

|--------|------------------|-----------|------|------|------|-------|

|        | Output frequency |           |      | 32   |      | kHz   |

|        | Accuracy         |           | -30  |      | 30   | %     |

#### 37.1.14.5 Internal Phase Locked Loop (PLL) characteristics

### Table 37-26. Internal PLL characteristics.

| Symbol           | Parameter                       | Condition                                                   | Min. | Тур. | Max. | Units  |

|------------------|---------------------------------|-------------------------------------------------------------|------|------|------|--------|

| f <sub>IN</sub>  | Input frequency                 | Output frequency must be within $\mathbf{f}_{\text{OUT}}$   | 0.4  |      | 64   |        |

|                  |                                 | V <sub>CC</sub> = 1.6V                                      | 20   |      | 32   | MHz    |

| f <sub>OUT</sub> | Output frequency <sup>(1)</sup> | V <sub>CC</sub> = 2.7V                                      | 20   |      | 96   | INITIZ |

|                  |                                 | V <sub>CC</sub> = 3.6V                                      | 20   |      | 128  |        |

|                  | Duty cycle                      |                                                             |      | 50   |      | %      |

|                  | Start-up lock time              | f <sub>OUT</sub> = 48MHz                                    |      | 18   |      |        |

|                  | Re-lock time                    | f <sub>OUT-init</sub> = 10MHz, f <sub>OUT-end</sub> = 64MHz |      | 17   |      | μs     |

Note: 1. The maximum output frequency vs. supply voltage is linear between 1.8V and 2.7V, and can never be higher than four times the maximum CPU frequency.

| Symbol             | Parameter                  | Condition                       | Min.      | Тур. | Max. | Units |     |  |

|--------------------|----------------------------|---------------------------------|-----------|------|------|-------|-----|--|

|                    |                            | V <sub>CC</sub> = 3.0V, T= 85°C | mode = HS |      | 60   | 90    |     |  |

| t <sub>delay</sub> | Propagation delay          | mode = HS                       |           |      | 60   |       | ns  |  |

|                    |                            | V <sub>CC</sub> = 3.0V, T= 85°C | mode = LP |      | 130  |       |     |  |

|                    | Current source calibration | Single mode                     |           | 2    |      | 8     |     |  |

|                    | range                      | Double mode                     |           | 4    |      | 16    | μs  |  |

|                    | 64-Level Voltage Scaler    | Integral non-linearity (INL)    |           |      | 0.3  | 0.5   | lsb |  |

# 37.2.9 Bandgap and Internal 1.0V Reference Characteristics

### Table 37-50. Bandgap and Internal 1.0V reference characteristics.

| Symbol | Parameter                                | Condition                            | Min.                         | Тур. | Max. | Units |

|--------|------------------------------------------|--------------------------------------|------------------------------|------|------|-------|

|        | Startup time                             | As reference for ADC or DAC          | 1 Clk <sub>PER</sub> + 2.5µs |      |      |       |

|        |                                          | As input voltage to ADC and AC       |                              | 1.5  |      | μs    |

|        | Bandgap voltage                          |                                      |                              | 1.1  |      | V     |

| INT1V  | Internal 1.00V reference for ADC and DAC | T= 85°C, after calibration           | 0.99                         | 1    | 1.01 | V     |

|        | Variation over voltage and temperature   | Relative to T= 85°C, $V_{CC}$ = 3.0V |                              | ±1.0 |      | %     |

## **37.2.10 Brownout Detection Characteristics**

#### Table 37-51. Brownout detection characteristics.

| Symbol            | Parameter                           | Condition       | Min. | Тур. | Max. | Units |

|-------------------|-------------------------------------|-----------------|------|------|------|-------|

| V <sub>BOT</sub>  | BOD level 0 falling V <sub>CC</sub> |                 | 1.60 | 1.62 | 1.72 | V     |

|                   | BOD level 1 falling V <sub>CC</sub> |                 |      | 1.8  |      |       |

|                   | BOD level 2 falling V <sub>CC</sub> |                 |      | 2.0  |      |       |

|                   | BOD level 3 falling $V_{CC}$        |                 |      | 2.2  |      |       |

|                   | BOD level 4 falling V <sub>CC</sub> |                 |      | 2.4  |      |       |

|                   | BOD level 5 falling V <sub>CC</sub> |                 |      | 2.6  |      |       |

|                   | BOD level 6 falling V <sub>CC</sub> |                 |      | 2.8  |      |       |

|                   | BOD level 7 falling V <sub>CC</sub> |                 |      | 3.0  |      |       |

| t <sub>BOD</sub>  | Detection time                      | Continuous mode |      | 0.4  |      | μs    |

|                   |                                     | Sampled mode    |      | 1000 |      |       |

| V <sub>HYST</sub> | Hysteresis                          |                 |      | 1.4  |      | %     |

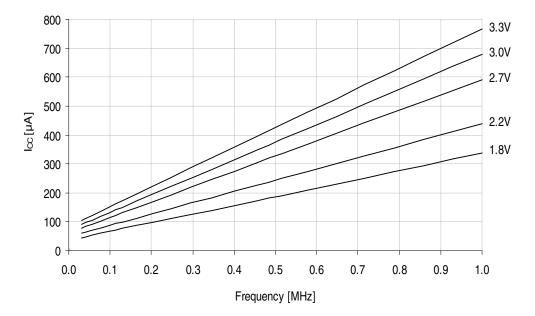

# 38. Typical Characteristics

# 38.1 ATxmega64A1U

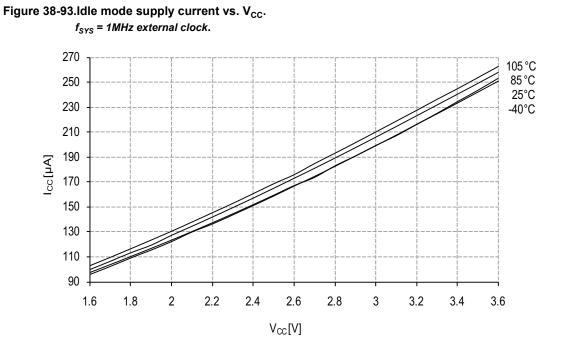

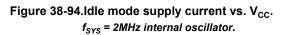

#### 38.1.1 Current consumption

38.1.1.1 Active mode supply current

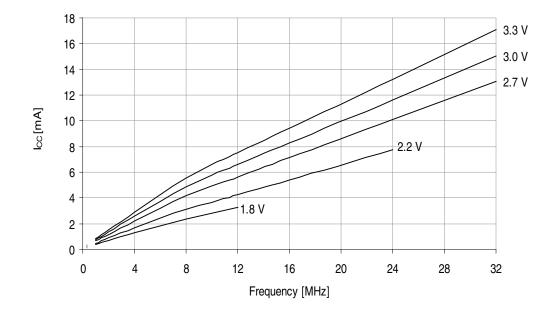

Figure 38-2. Active supply current vs. frequency.  $f_{SYS} = 1 - 32MHz \text{ external clock, } T = 25^{\circ}C.$

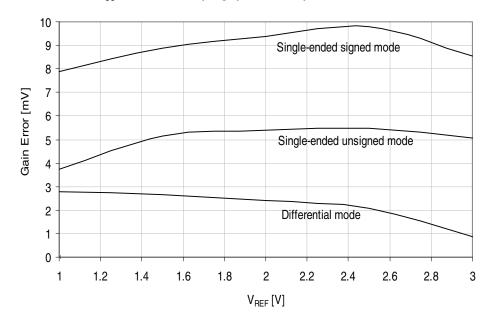

#### Figure 38-41.Gain error vs. V<sub>REF</sub>.

$T = 25 \,$ °C,  $V_{CC} = 3.6V$ , ADC sampling speed = 500ksps.

```

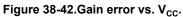

T = 25 \,°C, V_{REF} = external 1.0V, ADC sampling speed = 500ksps.

```

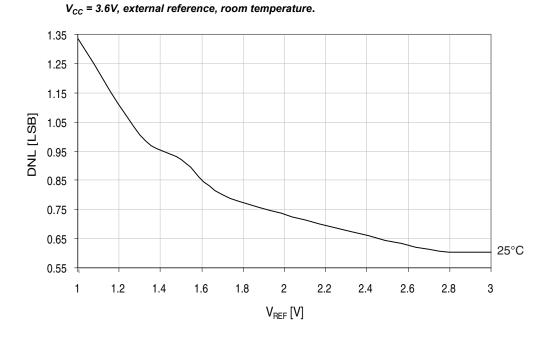

Figure 38-49.DAC DNL error vs. V<sub>REF</sub>.

**Atmel**

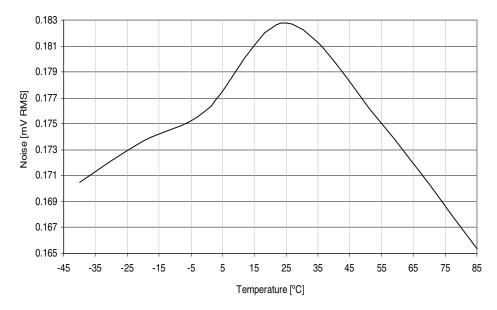

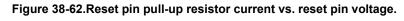

Figure 38-61.Minimum Reset pin pulse width vs. V<sub>cc</sub>.

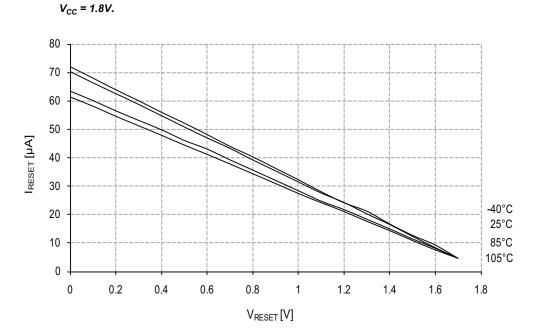

Figure 38-75. 32MHz internal oscillator frequency vs. temperature. *DFLL disabled*.

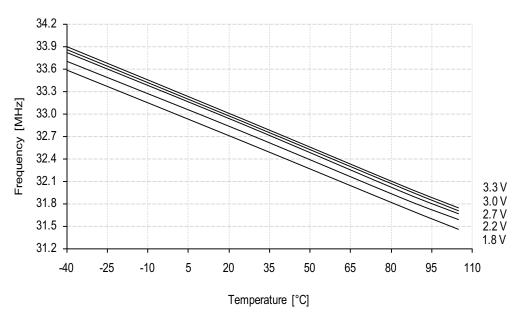

Figure 38-76. 32MHz internal oscillator frequency vs. temperature. DFLL enabled, from the 32.768kHz internal oscillator.

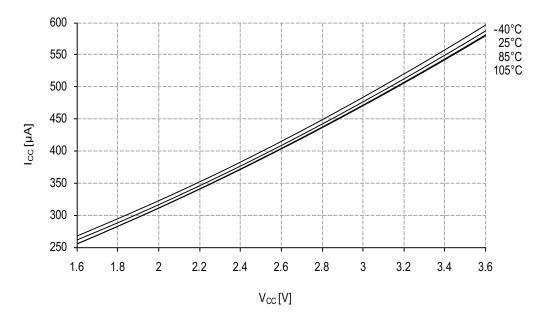

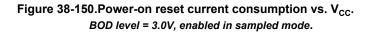

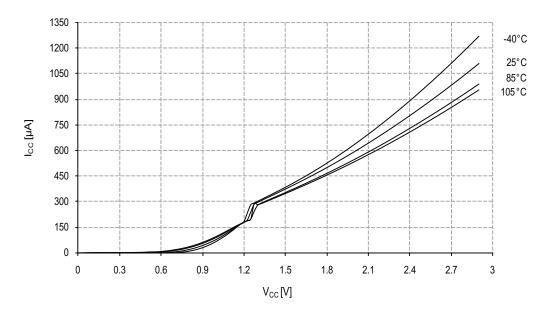

Figure 38-149.Power-on reset current consumption vs.  $V_{CC}$ . BOD level = 3.0V, enabled in continuous mode.

#### Problem fix/Workaround

Use the ADC in single ended signed mode.

#### 15. ADC has increased linearity error when using the gain stage above 500ksps

The INL error for gain stage is increased to above 20LSB for sampling speed exceeding 500 ksps.

#### Problem fix/Workaround

None.

#### 16. DAC Offset calibration range too small when using AVCC as reference

If using AVCC as reference, the DAC offset calibration will not totally remove the offset error. Offset could be up to 100LSB after calibration.

#### Problem fix/Workaround

Offset adjustment must be partly handled in software.

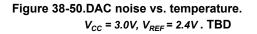

### 17. DAC clock noise

The system clock is visible as clock noise on the output of the DAC. Peak to peak noise is in the range 0.7mV - 1.6mV at 2MHz and 0.05mV to 0.1mV at 32MHz. If external clock is used as system clock, the noise is up to three times higher.

#### Problem fix/Workaround

Add external low-pass filter to remove the noise.

#### 18. Internal 1V reference has noise at low temperature

The internal 1.0V reference for the ADC and DAC has increased noise at low temperatures. The noise can result in INL numbers up to +/- 20 LSB at temperatures below 0C.

#### Problem fix/Workaround

For the ADC, use oversampling to reduce noise. For the DAC use external filter to reduce the noise.

#### 39.1.2 Rev. A - K

Not sampled.

- 7. Added electrical characterization for "ATxmega64A1U" on page 74.

- 8. Updated Table 37-29 on page 89 and Table 37-63 on page 112. Added ESR and start-up time parameters.

- 9. Added typical characteristics for "ATxmega64A1U" on page 120.

## 40.6 8385D - 07/2012

1. Updated Table 7-2 on page 15. Devices are respectively ATxmega64A1U and ATxmega128A1U.

## 40.7 8385C - 07/2012

- 1. Updated Table 7-1 on page 13. Device ID for ATxmega128A1U is 4C97. Device ID for ATxmega64A1U is 4E96.

- 2. Updated the package "100C2" on page 73. The ball rows are A-K (without I).

- 3. Updated the whole datasheet using the Atmel new updated datasheet template that includes Atmel new logo and new registered TM.

## 40.8 8385B - 03/2012

- 1. Added "Electrical Characteristics" on page 74.

- 2. Added "Typical Characteristics" on page 120.

- 3. Updated "Errata" on page 202.

- 4. Used Atmel new datasheet template that includes Atmel new addresses on the last page.

## 40.9 8385A - 11/2011

1. Initial revision.