Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | AVR                                                                        |

| Core Size                  | 8/16-Bit                                                                   |

| Speed                      | 32MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                      |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 78                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                                |

| Data Converters            | A/D 16x12b; D/A 4x12b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-TFBGA                                                                  |

| Supplier Device Package    | 100-CBGA (9x9)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega128a1u-cu |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Ordering Information

| Ordering code                     | Flash (bytes) | EEPROM<br>(bytes) | SRAM<br>(bytes) | Speed (MHz) | Power<br>supply | Package<br>(1)(2)(3) | Temp.         |

|-----------------------------------|---------------|-------------------|-----------------|-------------|-----------------|----------------------|---------------|

| ATxmega128A1U-AU                  | 128K + 8K     | 2K                | 8K              |             |                 |                      |               |

| ATxmega128A1U-AUR <sup>(4)</sup>  | 128K + 8K     | 2K                | 8K              |             |                 | 100A                 |               |

| ATxmega64A1U-AU                   | 64K + 4K      | 2K                | 4K              | _           |                 |                      |               |

| ATxmega64A1U-AUR <sup>(4)</sup>   | 64K + 4K      | 2K                | 4K              |             |                 |                      |               |

| ATxmega128A1U-CU                  | 128K + 8K     | 2K                | 8K              | _           |                 | 100C1<br>100C2       | -40°C - 85°C  |

| ATxmega128A1U-CUR <sup>(4)</sup>  | 128K + 8K     | 2K                | 8K              |             |                 |                      |               |

| ATxmega64A1U-CU                   | 64K + 4K      | 2K                | 4K              | -           |                 |                      |               |

| ATxmega64A1U-CUR <sup>(4)</sup>   | 64K + 4K      | 2K                | 4K              | 32          | 1.6 - 3.6V      |                      |               |

| ATxmega128A1U-C7U                 | 128K + 8K     | 2K                | 8K              | - 32        |                 |                      |               |

| ATxmega128A1U-C7UR <sup>(4)</sup> | 128K + 8K     | 2K                | 8K              |             |                 |                      |               |

| ATxmega64A1U-C7U                  | 64K + 4K      | 2K                | 4K              | _           |                 |                      |               |

| ATxmega64A1U-C7UR <sup>(4)</sup>  | 64K + 4K      | 2K                | 4K              |             |                 |                      |               |

| ATxmega128A1U-AN                  | 128K + 8K     | 2K                | 8K              |             |                 | 100A                 |               |

| ATxmega128A1U-ANR <sup>(4)</sup>  | 128K + 8K     | 2K                | 8K              |             |                 |                      | -40°C - 105°C |

| ATxmega64A1U-AN                   | 64K + 4K      | 2K                | 4K              |             |                 |                      | -40°C - 105°C |

| ATxmega64A1U-ANR <sup>(4)</sup>   | 64K + 4K      | 2K                | 4K              |             |                 |                      |               |

1. This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering information.

2. Pb-free packaging, complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). Also Halide free and fully Green.

3. For packaging information, see "Packaging information" on page 71.

4. Tape and Reel.

Notes:

|       | Package Type                                                                                  |

|-------|-----------------------------------------------------------------------------------------------|

| 100A  | 100-lead, 14 x 14 x 1.0mm, 0.5mm lead pitch, thin profile plastic quad flat package (TQFP)    |

| 100C1 | 100-ball, 9 x 9 x 1.2mm body, ball pitch 0.80mm, chip ball grid array (CBGA)                  |

| 100C2 | 100-ball, 7 x 7 x 1.0mm body, ball pitch 0.65mm, very thin fine-pitch ball grid array (VFBGA) |

# **Typical Applications**

| Industrial control | Climate control            | Low power battery applications |

|--------------------|----------------------------|--------------------------------|

| Factory automation | RF and ZigBee <sup>®</sup> | Power tools                    |

| Building control   | USB connectivity           | HVAC                           |

| Board control      | Sensor control             | Utility metering               |

| White goods        | Optical                    | Medical applications           |

# 10. System Clock and Clock options

## 10.1 Features

- Fast start-up time

- Safe run-time clock switching

- Internal oscillators:

- 32MHz run-time calibrated and tunable oscillator

- 2MHz run-time calibrated oscillator

- 32.768kHz calibrated oscillator

- 32kHz ultra low power (ULP) oscillator with 1kHz output

- External clock options

- 0.4MHz 16MHz crystal oscillator

- 32.768kHz crystal oscillator

- External clock

- PLL with 20MHz 128MHz output frequency

- Internal and external clock options and 1x to 31x multiplication

- Lock detector

- Clock prescalers with 1x to 2048x division

- Fast peripheral clocks running at two and four times the CPU clock

- Automatic run-time calibration of internal oscillators

- External oscillator and PLL lock failure detection with optional non-maskable interrupt

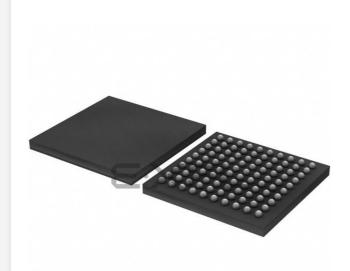

### 10.2 Overview

Atmel AVR XMEGA devices have a flexible clock system supporting a large number of clock sources. It incorporates both accurate internal oscillators and external crystal oscillator and resonator support. A high-frequency phase locked loop (PLL) and clock prescalers can be used to generate a wide range of clock frequencies. A calibration feature (DFLL) is available, and can be used for automatic run-time calibration of the internal oscillators to remove frequency drift over voltage and temperature. An oscillator failure monitor can be enabled to issue a non-maskable interrupt and switch to the internal oscillator if the external oscillator or PLL fails.

When a reset occurs, all clock sources except the 32kHz ultra low power oscillator are disabled. After reset, the device will always start up running from the 2MHz internal oscillator. During normal operation, the system clock source and prescalers can be changed from software at any time.

Figure 10-1 on page 20 presents the principal clock system in the XMEGA A1U family devices. Not all of the clocks need to be active at a given time. The clocks for the CPU and peripherals can be stopped using sleep modes and power reduction registers as described in "Power Management and Sleep Modes" on page 22.

Figure 10-1. The clock system, clock sources, and clock distribution.

#### 10.3 Clock Sources

The clock sources are divided in two main groups: internal oscillators and external clock sources. Most of the clock sources can be directly enabled and disabled from software, while others are automatically enabled or disabled, depending on peripheral settings. After reset, the device starts up running from the 2MHz internal oscillator. The other clock sources, DFLLs and PLL, are turned off by default.

The internal oscillators do not require any external components to run. For details on characteristics and accuracy of the internal oscillators, refer to the device datasheet.

#### 10.3.1 32kHz Ultra Low Power Internal Oscillator

This oscillator provides an approximate 32kHz clock. The 32kHz ultra low power (ULP) internal oscillator is a very low power clock source, and it is not designed for high accuracy. The oscillator employs a built-in prescaler that provides a

| Program address<br>(base address) | Source           | Interrupt description                    |

|-----------------------------------|------------------|------------------------------------------|

| 0x0E4                             | TCF1_INT_base    | Timer/counter 1 on port F interrupt base |

| 0x0EC                             | SPIF_INT_vector  | SPI ion port F interrupt base            |

| 0x0EE                             | USARTF0_INT_base | USART 0 on port F interrupt base         |

| 0x0F4                             | USARTF1_INT_base | USART 1 on port F interrupt base         |

| 0x0FA                             | USB_INT_base     | USB on port D interrupt base             |

# 21. USB – Universal Serial Bus Interface

## 21.1 Features

- One USB 2.0 full speed (12Mbps) and low speed (1.5Mbps) device compliant interface

- Integrated on-chip USB transceiver, no external components needed

- 16 endpoint addresses with full endpoint flexibility for up to 31 endpoints

- One input endpoint per endpoint address

- One output endpoint per endpoint address

- Endpoint address transfer type selectable to

- Control transfers

- Interrupt transfers

- Bulk transfers

- Isochronous transfers

- Configurable data payload size per endpoint, up to 1023 bytes

- Endpoint configuration and data buffers located in internal SRAM

- Configurable location for endpoint configuration data

- Configurable location for each endpoint's data buffer

- Built-in direct memory access (DMA) to internal SRAM for:

- Endpoint configurations

- Reading and writing endpoint data

- Ping-pong operation for higher throughput and double buffered operation

- Input and output endpoint data buffers used in a single direction

- CPU/DMA controller can update data buffer during transfer

- Multi packet transfer for reduced interrupt load and software intervention

- Data payload exceeding maximum packet size is transferred in one continuous transfer

- No interrupts or software interaction on packet transaction level

- Transaction complete FIFO for workflow management when using multiple endpoints

- Tracks all completed transactions in a first-come, first-served work queue

- Clock selection independent of system clock source and selection

- Minimum 1.5MHz CPU clock required for low speed USB operation

- Minimum 12MHz CPU clock required for full speed operation

- Connection to event system

- On chip debug possibilities during USB transactions

## 21.2 Overview

The USB module is a USB 2.0 full speed (12Mbps) and low speed (1.5Mbps) device compliant interface.

The USB supports 16 endpoint addresses. All endpoint addresses have one input and one output endpoint, for a total of 31 configurable endpoints and one control endpoint. Each endpoint address is fully configurable and can be configured for any of the four transfer types; control, interrupt, bulk, or isochronous. The data payload size is also selectable, and it supports data payloads up to 1023 bytes.

No dedicated memory is allocated for or included in the USB module. Internal SRAM is used to keep the configuration for each endpoint address and the data buffer for each endpoint. The memory locations used for endpoint configurations and data buffers are fully configurable. The amount of memory allocated is fully dynamic, according to the number of endpoints in use and the configuration of these. The USB module has built-in direct memory access (DMA), and will read/write data from/to the SRAM when a USB transaction takes place.

To maximize throughput, an endpoint address can be configured for ping-pong operation. When done, the input and output endpoints are both used in the same direction. The CPU or DMA controller can then read/write one data buffer while the USB module writes/reads the others, and vice versa. This gives double buffered communication.

A DAC conversion is automatically started when new data to be converted are available. Events from the event system can also be used to trigger a conversion, and this enables synchronized and timed conversions between the DAC and other peripherals, such as a timer/counter. The DMA controller can be used to transfer data to the DAC.

The DAC has high drive strength, and is capable of driving both resistive and capacitive loads, aswell as loads which combine both. A low-power mode is available, which will reduce the drive strength of the output.

Internal and external voltage references can be used. The DAC output is also internally available for use as input to the analog comparator or ADC.

PORTA and PORTB each has one DAC. Notation of these peripherals are DACA and DACB, respectively.

# 33. Pinout and Pin Functions

The device pinout is shown in "Pinout/Block Diagram" on page 3. In addition to general purpose I/O functionality, each pin can have several alternate functions. This will depend on which peripheral is enabled and connected to the actual pin. Only one of the pin functions can be used at time.

## 33.1 Alternate Pin Function Description

The tables below show the notation for all pin functions available and describe its function.

#### 33.1.1 Operation/ Power Supply

| V <sub>CC</sub>  | Digital supply voltage |

|------------------|------------------------|

| AV <sub>CC</sub> | Analog supply voltage  |

| GND              | Ground                 |

#### 33.1.2 Port Interrupt functions

| SYNC  | Port pin with full synchronous and limited asynchronous interrupt function |

|-------|----------------------------------------------------------------------------|

| ASYNC | Port pin with full synchronous and full asynchronous interrupt function    |

#### 33.1.3 Analog functions

| ACn              | Analog Comparator input pin n            |

|------------------|------------------------------------------|

| ACnOUT           | Analog Comparator n Output               |

| ADCn             | Analog to Digital Converter input pin n  |

| DACn             | Digital to Analog Converter output pin n |

| A <sub>REF</sub> | Analog Reference input pin               |

### 33.1.4 External Bus Interface functions

| An   | Address line n                 |               |

|------|--------------------------------|---------------|

| Dn   | Data line n                    |               |

| CSn  | Chip Select n                  |               |

| ALEn | Address Latch Enable pin n     | (SRAM)        |

| RE   | Read Enable                    | (SRAM)        |

| WE   | External Data Memory Write     | (SRAM /SDRAM) |

| BAn  | Bank Address                   | (SDRAM)       |

| CAS  | Column Access Strobe           | (SDRAM)       |

| CKE  | SDRAM Clock Enable             | (SDRAM)       |

| CLK  | SDRAM Clock                    | (SDRAM)       |

| DQM  | Data Mask Signal/Output Enable | (SDRAM)       |

| RAS  | Row Access Strobe              | (SDRAM)       |

#### Table 33-11. Port R - alternate functions.

| PORT R | PIN # | INTERRUPT | PDI       | XTAL  |

|--------|-------|-----------|-----------|-------|

| PDI    | 89    |           | PDI_DATA  |       |

| RESET  | 90    |           | PDI_CLOCK |       |

| PRO    | 91    | SYNC      |           | XTAL2 |

| PR1    | 92    | SYNC      |           | XTAL1 |

| Mnemonics | Operands | Description                         | Oper                         | ation  |             | Flags       | #Clocks              |

|-----------|----------|-------------------------------------|------------------------------|--------|-------------|-------------|----------------------|

| ICALL     |          | Indirect Call to (Z)                | PC(15:0)<br>PC(21:16)        | ←<br>← | Z,<br>0     | None        | 2 / 3 <sup>(1)</sup> |

| EICALL    |          | Extended Indirect Call to (Z)       | PC(15:0)<br>PC(21:16)        | ←<br>← | Z,<br>EIND  | None        | 3 (1)                |

| CALL      | k        | call Subroutine                     | PC                           | ←      | k           | None        | 3 / 4 <sup>(1)</sup> |

| RET       |          | Subroutine Return                   | PC                           | ~      | STACK       | None        | 4 / 5 <sup>(1)</sup> |

| RETI      |          | Interrupt Return                    | PC                           | ←      | STACK       | 1           | 4 / 5 <sup>(1)</sup> |

| CPSE      | Rd,Rr    | Compare, Skip if Equal              | if (Rd = Rr) PC              | ~      | PC + 2 or 3 | None        | 1/2/3                |

| СР        | Rd,Rr    | Compare                             | Rd - Rr                      |        |             | Z,C,N,V,S,H | 1                    |

| CPC       | Rd,Rr    | Compare with Carry                  | Rd - Rr - C                  |        |             | Z,C,N,V,S,H | 1                    |

| CPI       | Rd,K     | Compare with Immediate              | Rd - K                       |        |             | Z,C,N,V,S,H | 1                    |

| SBRC      | Rr, b    | Skip if Bit in Register Cleared     | if (Rr(b) = 0) PC            | ~      | PC + 2 or 3 | None        | 1/2/3                |

| SBRS      | Rr, b    | Skip if Bit in Register Set         | if (Rr(b) = 1) PC            | ~      | PC + 2 or 3 | None        | 1/2/3                |

| SBIC      | A, b     | Skip if Bit in I/O Register Cleared | if (I/O(A,b) = 0) PC         | ←      | PC + 2 or 3 | None        | 2/3/4                |

| SBIS      | A, b     | Skip if Bit in I/O Register Set     | If (I/O(A,b) =1) PC          | ←      | PC + 2 or 3 | None        | 2/3/4                |

| BRBS      | s, k     | Branch if Status Flag Set           | if (SREG(s) = 1) then PC     | ~      | PC + k + 1  | None        | 1/2                  |

| BRBC      | s, k     | Branch if Status Flag Cleared       | if (SREG(s) = 0) then PC     | ~      | PC + k + 1  | None        | 1/2                  |

| BREQ      | k        | Branch if Equal                     | if (Z = 1) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRNE      | k        | Branch if Not Equal                 | if (Z = 0) then PC           | ~      | PC + k + 1  | None        | 1/2                  |

| BRCS      | k        | Branch if Carry Set                 | if (C = 1) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRCC      | k        | Branch if Carry Cleared             | if (C = 0) then PC           | ~      | PC + k + 1  | None        | 1/2                  |

| BRSH      | k        | Branch if Same or Higher            | if (C = 0) then PC           | ~      | PC + k + 1  | None        | 1/2                  |

| BRLO      | k        | Branch if Lower                     | if (C = 1) then PC           | ~      | PC + k + 1  | None        | 1/2                  |

| BRMI      | k        | Branch if Minus                     | if (N = 1) then PC           | ~      | PC + k + 1  | None        | 1/2                  |

| BRPL      | k        | Branch if Plus                      | if (N = 0) then PC           | ~      | PC + k + 1  | None        | 1/2                  |

| BRGE      | k        | Branch if Greater or Equal, Signed  | if (N $\oplus$ V= 0) then PC | ←      | PC + k + 1  | None        | 1/2                  |

| BRLT      | k        | Branch if Less Than, Signed         | if (N $\oplus$ V= 1) then PC | ~      | PC + k + 1  | None        | 1/2                  |

| BRHS      | k        | Branch if Half Carry Flag Set       | if (H = 1) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRHC      | k        | Branch if Half Carry Flag Cleared   | if (H = 0) then PC           | ~      | PC + k + 1  | None        | 1/2                  |

| BRTS      | k        | Branch if T Flag Set                | if (T = 1) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRTC      | k        | Branch if T Flag Cleared            | if (T = 0) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRVS      | k        | Branch if Overflow Flag is Set      | if (V = 1) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRVC      | k        | Branch if Overflow Flag is Cleared  | if (V = 0) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRIE      | k        | Branch if Interrupt Enabled         | if (I = 1) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRID      | k        | Branch if Interrupt Disabled        | if (I = 0) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

|           |          | Data tr                             | ransfer instructions         |        |             |             |                      |

| MOV       | Rd, Rr   | Copy Register                       | Rd                           | ←      | Rr          | None        | 1                    |

| MOVW      | Rd, Rr   | Copy Register Pair                  | Rd+1:Rd                      | ←      | Rr+1:Rr     | None        | 1                    |

| LDI       | Rd, K    | Load Immediate                      | Rd                           | ←      | к           | None        | 1                    |

#### Table 37-14. Accuracy characteristics.

| Symbol             | Parameter                    | Condition                          |                        | Min. | Тур. | Max. | Units |

|--------------------|------------------------------|------------------------------------|------------------------|------|------|------|-------|

| RES                | Input resolution             |                                    |                        |      |      | 12   | Bits  |

|                    |                              |                                    | V <sub>CC</sub> = 1.6V |      | ±2.0 | ±3   |       |

|                    |                              | V <sub>REF</sub> = Ext 1.0V        | V <sub>CC</sub> = 3.6V |      | ±1.5 | ±2.5 |       |

| INL <sup>(1)</sup> | Integral non-linearity       |                                    | V <sub>CC</sub> = 1.6V |      | ±2.0 | ±4   | _     |

|                    | integral non-intearity       | V <sub>REF</sub> =AV <sub>CC</sub> | V <sub>CC</sub> = 3.6V |      | ±1.5 | ±4   |       |

|                    |                              | \/ -INIT1\/                        | V <sub>CC</sub> = 1.6V |      | ±5.0 |      |       |

|                    |                              | V <sub>REF</sub> =INT1V            | V <sub>CC</sub> = 3.6V |      | ±5.0 |      |       |

|                    | Differential non-linearity   | V <sub>REF</sub> =Ext 1.0V         | V <sub>CC</sub> = 1.6V |      | ±1.5 | 3.0  | lab   |

|                    |                              |                                    | V <sub>CC</sub> = 3.6V |      | ±0.6 | 1.5  | lsb   |

| DNL <sup>(1)</sup> |                              | V <sub>REF</sub> =AV <sub>CC</sub> | V <sub>CC</sub> = 1.6V |      | ±1.0 | 3.5  |       |

| DINL               |                              |                                    | V <sub>CC</sub> = 3.6V |      | ±0.6 | 1.5  |       |

|                    |                              | V <sub>REF</sub> =INT1V            | V <sub>CC</sub> = 1.6V |      | ±4.5 |      |       |

|                    |                              |                                    | V <sub>CC</sub> = 3.6V |      | ±4.5 |      | -     |

|                    | Gain error                   | After calibration                  |                        |      | <4.0 |      | -     |

|                    | Gain calibration step size   |                                    |                        |      | 4.0  |      |       |

|                    | Gain calibration drift       | V <sub>REF</sub> = Ext 1.0V        |                        |      | <0.2 |      | mV/K  |

|                    | Offset error                 | After calibration                  |                        |      | <1.0 |      | lsb   |

|                    | Offset calibration step size |                                    |                        |      | 1.0  |      |       |

Note: 1. Maximum numbers are based on characterisation and not tested in production, and valid for 5% to 95% output voltage range.

#### 37.1.8 Analog Comparator Characteristics

#### Table 37-15. Analog Comparator characteristics.

| Symbol            | Parameter             | Condition              | Min. | Тур. | Max.                  | Units |

|-------------------|-----------------------|------------------------|------|------|-----------------------|-------|

| V <sub>off</sub>  | Input offset voltage  |                        |      | <±10 |                       | mV    |

| l <sub>lk</sub>   | Input leakage current |                        |      | <1   |                       | nA    |

|                   | Input voltage range   |                        | -0.1 |      | AV <sub>CC</sub> +0.1 | V     |

| V <sub>hys1</sub> | Hysteresis, none      |                        |      | 0    |                       |       |

| V <sub>hys2</sub> | Hysteresis, small     | mode = High Speed (HS) |      | 22   |                       |       |

|                   |                       | mode = Low Power (LP)  |      | 30   |                       | mV    |

| V <sub>hys3</sub> | Hysteresis, large     | mode = HS              |      | 43   |                       |       |

|                   |                       | mode = LP              |      | 60   |                       |       |

#### Table 37-44. Accuracy characteristics.

| Symbol             | Parameter                  | Condition <sup>(2)</sup>                   |                                                         | Min.  | Тур.  | Max.      | Units |

|--------------------|----------------------------|--------------------------------------------|---------------------------------------------------------|-------|-------|-----------|-------|

| RES                | Resolution                 | Programmable to 12-bit                     |                                                         | 11    | 11.5  | 12        | Bits  |

| INL <sup>(1)</sup> | Integral non-linearity     | 500ksps,<br>differential<br>mode           | $V_{\rm CC}$ -1.0V < $V_{\rm REF}$ < $V_{\rm CC}$ -0.6V |       | ±1.2  | ±2        | lsb   |

|                    |                            |                                            | All V <sub>REF</sub>                                    |       | ±1.5  | ±3        |       |

|                    |                            | 2000ksps,<br>differential<br>mode          | $V_{\rm CC}$ -1.0V < $V_{\rm REF}$ < $V_{\rm CC}$ -0.6V |       | ±1.0  | ±2        |       |

|                    |                            |                                            | All V <sub>REF</sub>                                    |       | ±1.5  | ±3        |       |

|                    |                            | single ended mode                          |                                                         |       | ±1.5  | ±4        |       |

| DNL <sup>(1)</sup> | Differential non-linearity | guaranteed n                               |                                                         | <±0.5 | <±1   |           |       |

|                    | Offset Error               |                                            |                                                         |       | -1    |           | mV    |

|                    |                            | Temperature drift                          |                                                         |       | <0.01 |           | mV/K  |

|                    |                            | Operating voltage drift                    |                                                         |       | <0.6  |           | mV/V  |

|                    | Gain Error                 | Differential<br>mode                       | External reference                                      |       | -1    |           | mV    |

|                    |                            |                                            | AV <sub>CC</sub> /1.6                                   |       | 10    |           |       |

|                    |                            |                                            | AV <sub>CC</sub> /2.0                                   |       | 8     |           |       |

|                    |                            |                                            | Bandgap                                                 |       | ±5    |           |       |

|                    |                            | Temperature drift                          |                                                         |       | <0.02 |           | mV/K  |

|                    |                            | Operating voltage drift                    |                                                         |       | <0.5  |           | mV/V  |

|                    | Noise                      | Differential m<br>2msps, V <sub>CC</sub> = |                                                         | 0.4   |       | mV<br>rms |       |

Notes: 1. Maximum numbers are based on characterisation and not tested in production, and valid for 5% to 95% input voltage range.

2. Unless otherwise noted all linearity, offset and gain error numbers are valid under the condition that external V<sub>REF</sub> is used.

#### Table 37-45. Gain stage characteristics.

| Symbol              | Parameter              | Condition               | Min.              | Тур. | Max.                  | Units                        |     |

|---------------------|------------------------|-------------------------|-------------------|------|-----------------------|------------------------------|-----|

| R <sub>in</sub>     | Input resistance       | Switched in normal mode |                   | 4.0  |                       | kΩ                           |     |

| C <sub>sample</sub> | Input capacitance      | Switched in normal mode |                   | 4.4  |                       | pF                           |     |

|                     | Signal range           | Gain stage output       | 0                 |      | V <sub>CC</sub> - 0.6 | V                            |     |

|                     | Propagation delay      | ADC conversion rate     |                   | 1    |                       | Clk <sub>ADC</sub><br>cycles |     |

|                     | Sample rate            | Same as ADC             |                   | 100  |                       | 1000                         | kHz |

| INL <sup>(1)</sup>  | Integral Non-Linearity | 500ksps                 | All gain settings |      | ±1.5                  | ±3                           | lsb |

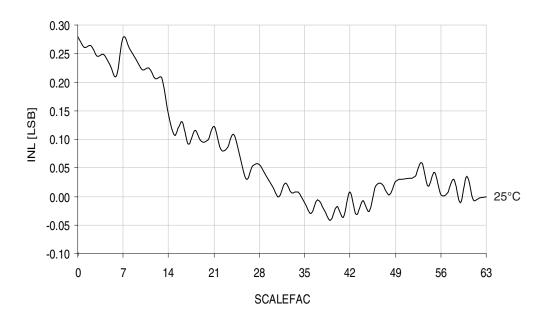

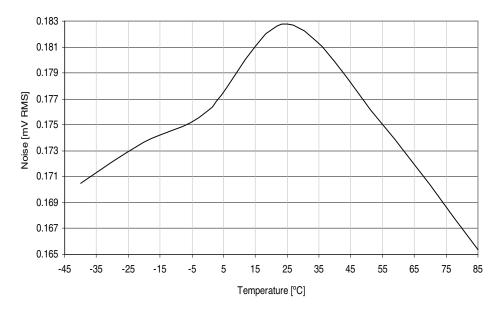

Figure 38-57.Voltage scaler INL vs. SCALEFAC.  $T = 25 \,^{\circ}C$ ,  $V_{cc} = 3.0V$ .

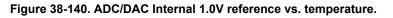

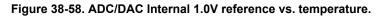

### 38.1.6 Internal 1.0V reference Characteristics

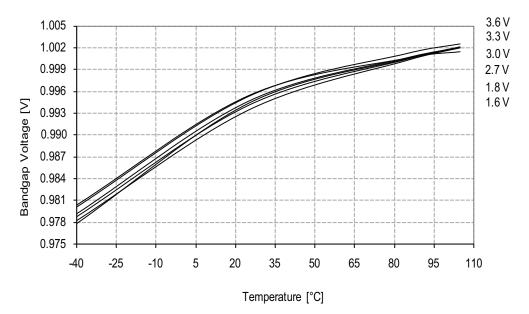

Figure 38-71. 32.768kHz internal oscillator frequency vs. calibration value.  $V_{cc} = 3.0V$ ,  $T = 25^{\circ}C$ .

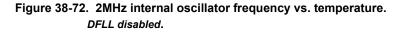

38.1.10.3 2MHz Internal Oscillator

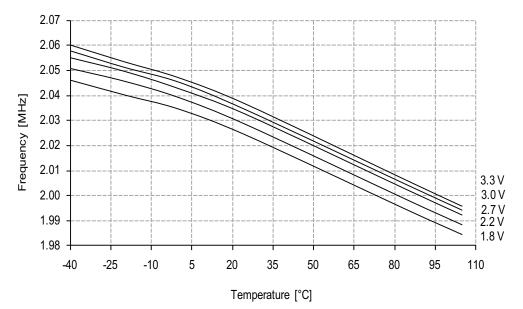

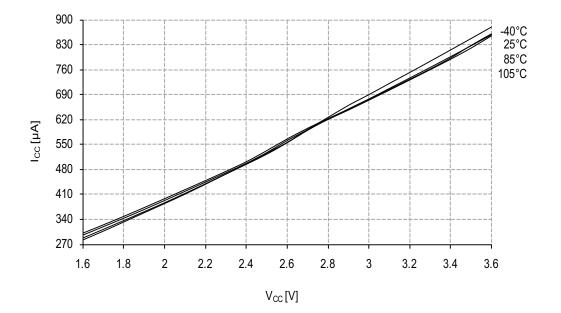

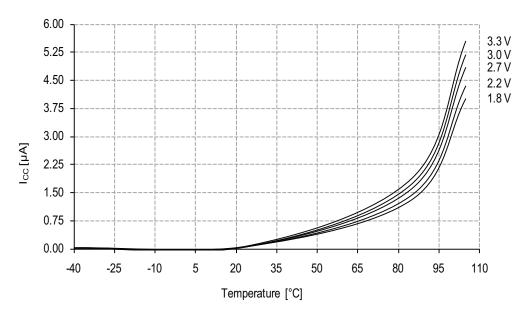

#### 38.2.1.3 Power-down mode supply current

Figure 38-97.Power-down mode supply current vs. Temperature. *All functions disabled*.

Figure 38-98.Power-down mode supply current vs. Temperature. Sampled BOD with Watchdog Timer running on ULP oscillator.

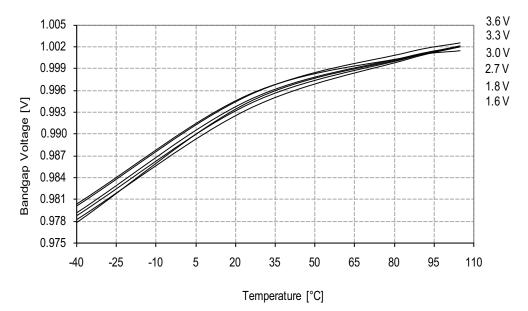

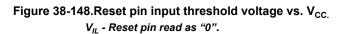

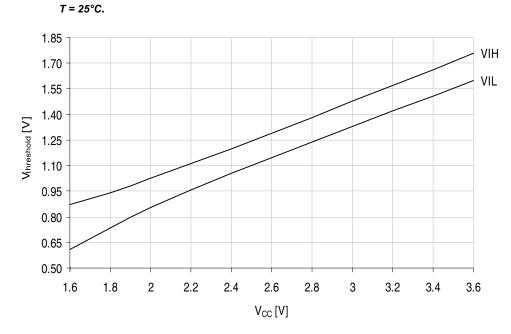

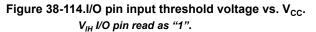

Figure 38-113.I/O pin input threshold voltage vs.  $V_{CC}$ .

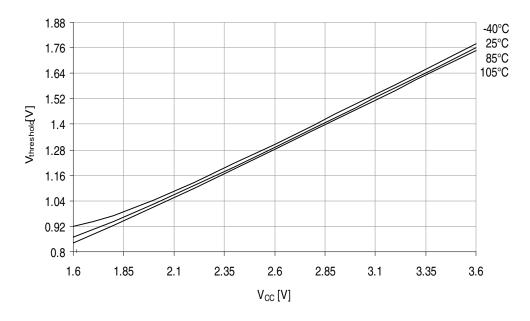

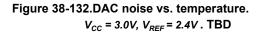

Figure 38-131.DAC DNL error vs. V<sub>REF</sub>.

Figure 38-139.Voltage scaler INL vs. SCALEFAC.  $T = 25 \mathcal{C}, V_{cc} = 3.0V.$

### 38.2.6 Internal 1.0V reference Characteristics