#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | AVR                                                                       |

| Core Size                  | 8/16-Bit                                                                  |

| Speed                      | 32MHz                                                                     |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 78                                                                        |

| Program Memory Size        | 64KB (32K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 4K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b; D/A 4x12b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 100-TQFP                                                                  |

| Supplier Device Package    | 100-TQFP (14x14)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega64a1u-au |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 6. AVR CPU

## 6.1 Features

- 8/16-bit, high-performance Atmel AVR RISC CPU

- 142 instructions

- Hardware multiplier

- 32x8-bit registers directly connected to the ALU

- Stack in RAM

- Stack pointer accessible in I/O memory space

- Direct addressing of up to 16MB of program memory and 16MB of data memory

- True 16/24-bit access to 16/24-bit I/O registers

- Efficient support for 8-, 16-, and 32-bit arithmetic

- Configuration change protection of system-critical features

### 6.2 Overview

All Atmel AVR XMEGA devices use the 8/16-bit AVR CPU. The main function of the CPU is to execute the code and perform all calculations. The CPU is able to access memories, perform calculations, control peripherals, and execute the program in the flash memory. Interrupt handling is described in a separate section, refer to "Interrupts and Programmable Multilevel Interrupt Controller" on page 27.

## 6.3 Architectural Overview

In order to maximize performance and parallelism, the AVR CPU uses a Harvard architecture with separate memories and buses for program and data. Instructions in the program memory are executed with single-level pipelining. While one instruction is being executed, the next instruction is pre-fetched from the program memory. This enables instructions to be executed on every clock cycle. For details of all AVR instructions, refer to http://www.atmel.com/avr.

#### Figure 6-1. Block diagram of the AVR CPU architecture.

## 7.10 Memory Timing

Read and write access to the I/O memory takes one CPU clock cycle. A write to SRAM takes one cycle, and a read from SRAM takes two cycles. For burst read (DMA), new data are available every cycle. EEPROM page load (write) takes one cycle, and three cycles are required for read. For burst read, new data are available every second cycle. External memory has multi-cycle read and write. The number of cycles depends on the type of memory and configuration of the external bus interface. Refer to the instruction summary for more details on instructions and instruction timing.

### 7.11 Device ID and Revision

Each device has a three-byte device ID. This ID identifies Atmel as the manufacturer of the device and the device type. A separate register contains the revision number of the device.

## 7.12 I/O Memory Protection

Some features in the device are regarded as critical for safety in some applications. Due to this, it is possible to lock the I/O register related to the clock system, the event system, and the advanced waveform extensions. As long as the lock is enabled, all related I/O registers are locked and they can not be written from the application software. The lock registers themselves are protected by the configuration change protection mechanism.

### 7.13 JTAG Disable

It is possible to disable the JTAG interface from the application software. This will prevent all external JTAG access to the device until the next device reset or until JTAG is enabled again from the application software. As long as JTAG is disabled, the I/O pins required for JTAG can be used as normal I/O pins.

## 7.14 Flash and EEPROM Page Size

The flash program memory and EEPROM data memory are organized in pages. The pages are word accessible for the flash and byte accessible for the EEPROM.

Table 7-2 on page 15 shows the Flash Program Memory organization. Flash write and erase operations are performed on one page at a time, while reading the Flash is done one byte at a time. For Flash access the Z-pointer (Z[m:n]) is used for addressing. The most significant bits in the address (FPAGE) gives the page number and the least significant address bits (FWORD) gives the word in the page.

#### Table 7-2. Number of words and Pages in the Flash.

| Devices       | PC size | Flash     | Page Size | FWORD  | FPAGE   | App  | Application Boot |      | Boot        |

|---------------|---------|-----------|-----------|--------|---------|------|------------------|------|-------------|

|               | bits    | bytes     | words     |        |         | Size | No of pages      | Size | No of pages |

| ATxmega64A1U  | 16      | 64K + 4K  | 128       | Z[7:1] | Z[16:8] | 64K  | 256              | 4K   | 16          |

| ATxmega128A1U | 17      | 128K + 8K | 256       | Z[8:1] | Z[17:9] | 128K | 256              | 8K   | 16          |

Table 7-3 on page 16 shows EEPROM memory organization for the Atmel AVR XMEGA A1U devices. EEPROM write and erase operations can be performed one page or one byte at a time, while reading the EEPROM is done one byte at a time. For EEPROM access the NVM Address Register (ADDR[m:n]) is used for addressing. The most significant bits in the address (E2PAGE) give the page number and the least significant address bits (E2BYTE) give the byte in the page.

| Program address<br>(base address) | Source           | Interrupt description                                |

|-----------------------------------|------------------|------------------------------------------------------|

| 0x028                             | TCC1_INT_base    | Timer/counter 1 on port C interrupt base             |

| 0x030                             | SPIC_INT_vect    | SPI on port C interrupt vector                       |

| 0x032                             | USARTC0_INT_base | USART 0 on port C interrupt base                     |

| 0x038                             | USARTC1_INT_base | USART 1 on port C interrupt base                     |

| 0x03E                             | AES_INT_vect     | AES interrupt vector                                 |

| 0x040                             | NVM_INT_base     | Nonvolatile memory interrupt base                    |

| 0x044                             | PORTB_INT_base   | Port B interrupt base                                |

| 0x048                             | ACB_INT_base     | Analog comparator on port B interrupt base           |

| 0x04E                             | ADCB_INT_base    | Analog to digital converter on port B interrupt base |

| 0x056                             | PORTE_INT_base   | Port E interrupt base                                |

| 0x05A                             | TWIE_INT_base    | Two-Wire interface on port E interrupt base          |

| 0x05E                             | TCE0_INT_base    | Timer/counter 0 on port E interrupt base             |

| 0x06A                             | TCE1_INT_base    | Timer/counter 1 on port E interrupt base             |

| 0x072                             | SPIE_INT_vect    | SPI on port E interrupt vector                       |

| 0x074                             | USARTE0_INT_base | USART 0 on port E interrupt base                     |

| 0x07A                             | USARTE1_INT_base | USART 1 on port E interrupt base                     |

| 0x080                             | PORTD_INT_base   | Port D interrupt base                                |

| 0x084                             | PORTA_INT_base   | Port A interrupt base                                |

| 0x088                             | ACA_INT_base     | Analog comparator on Port A interrupt base           |

| 0x08E                             | ADCA_INT_base    | Analog to digital converter on Port A interrupt base |

| 0x096                             | TWID_INT_base    | Two-Wire Interface on port D interrupt base          |

| 0x09A                             | TCD0_INT_base    | Timer/counter 0 on port D interrupt base             |

| 0x0A6                             | TCD1_INT_base    | Timer/counter 1 on port D interrupt base             |

| 0x0AE                             | SPID_INT_vector  | SPI on port D interrupt vector                       |

| 0x0B0                             | USARTD0_INT_base | USART 0 on port D interrupt base                     |

| 0x0B6                             | USARTD1_INT_base | USART 1 on port D interrupt base                     |

| 0x0BC                             | PORTQ_INT_base   | Port Q INT base                                      |

| 0x0C0                             | PORTH_INT_base   | Port H INT base                                      |

| 0x0C4                             | PORTJ_INT_base   | Port J INT base                                      |

| 0x0C8                             | PORTK_INT_base   | Port K INT base                                      |

| 0x0D0                             | PORTF_INT_base   | Port F INT base                                      |

| 0x0D4                             | TWIF_INT_base    | Two-Wire interface on Port F INT base                |

| 0x0D8                             | TCF0_INT_base    | Timer/counter 0 on port F interrupt base             |

# 17. TC2 – Time/Counter Type 2

## 17.1 Features

- Eight eight-bit timer/counters

- Four Low-byte timer/counters

- Four High-byte timer/counters

- Up to eight compare channels in each timer/counter 2

- Four compare channels for the low-byte timer/counter

- Four compare channels for the high-byte timer/counter

- Waveform generation

- Single slope pulse width modulation

- Timer underflow interrupts/events

- One compare match interrupt/event per compare channel for the low-byte timer/counter

- Can be used with the event system for count control

- Can be used to trigger DMA transactions

## 17.2 Overview

There are four Timer/counter 2. These are realized when a Timer/counter 0 is set in split mode. It is then a system of two eight-bit timer/counters, each with four compare channels. This results in eight configurable pulse width modulation (PWM) channels with individually controlled duty cycles, and is intended for applications that require a high number of PWM channels.

The two eight-bit timer/counters in this system are referred to as the low-byte timer/counter and high-byte timer/counter, respectively. The difference between them is that only the low-byte timer/counter can be used to generate compare match interrupts, events and DMA triggers.

The two eight-bit timer/counters have a shared clock source and separate period and compare settings. They can be clocked and timed from the peripheral clock, with optional prescaling, or from the event system. The counters are always counting down.

PORTC, PORTD, PORTE and PORTF each has one Timer/Counter 2. Notation of these are TCC2 (Time/Counter C2), TCD2, TCE2 and TCF2, respectively.

# 19. Hi-Res – High Resolution Extension

## 19.1 Features

- Increases waveform generator resolution up to 8x (three bits)

- Supports frequency, single-slope PWM and dual-slope PWM generation

- Supports the AWeX when this is used for the same timer/counter

## 19.2 Overview

The high-resolution (hi-res) extension can be used to increase the resolution of the waveform generation output from a timer/counter by four or eight. It can be used for a timer/counter doing frequency, single-slope PWM, or dual-slope PWM generation. It can also be used with the AWeX if this is used for the same timer/counter.

The hi-res extension uses the peripheral 4x clock ( $Clk_{PER4}$ ). The system clock prescalers must be configured so the peripheral 4x clock frequency is four times higher than the peripheral and CPU clock frequency when the hi-res extension is enabled.

There are four hi-res extensions that each can be enabled for each timer/counters pair on PORTC, PORTD, PORTE and PORTF. The notation of these peripherals are HIRESC, HIRESD, HIRESE and HIRESF, respectively.

# 26. AES and DES Crypto Engine

## 26.1 Features

- Data Encryption Standard (DES) CPU instruction

- Advanced Encryption Standard (AES) crypto module

- DES Instruction

- Encryption and decryption

- DES supported

- Encryption/decryption in 16 CPU clock cycles per 8-byte block

- AES crypto module

- Encryption and decryption

- Supports 128-bit keys

- Supports XOR data load mode to the state memory

- Encryption/decryption in 375 clock cycles per 16-byte block

# 26.2 Overview

The Advanced Encryption Standard (AES) and Data Encryption Standard (DES) are two commonly used standards for cryptography. These are supported through an AES peripheral module and a DES CPU instruction, and the communication interfaces and the CPU can use these for fast, encrypted communication and secure data storage.

DES is supported by an instruction in the AVR CPU. The 8-byte key and 8-byte data blocks must be loaded into the register file, and then the DES instruction must be executed 16 times to encrypt/decrypt the data block.

The AES crypto module encrypts and decrypts 128-bit data blocks with the use of a 128-bit key. The key and data must be loaded into the key and state memory in the module before encryption/decryption is started. It takes 375 peripheral clock cycles before the encryption/decryption is done. The encrypted/encrypted data can then be read out, and an optional interrupt can be generated. The AES crypto module also has DMA support with transfer triggers when encryption/decryption is done and optional auto-start of encryption/decryption when the state memory is fully loaded.

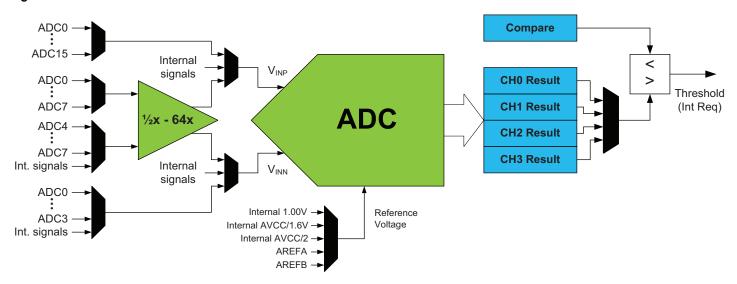

# 29. ADC – 12-bit Analog to Digital Converter

## 29.1 Features

- Two Analog to Digital Converters

- 12-bit resolution

- Up to two million samples per second

- Two inputs can be sampled simultaneously using ADC and 1x gain stage

- Four inputs can be sampled within 1.5µs

- Down to 2.5µs conversion time with 8-bit resolution

- Down to 3.5µs conversion time with 12-bit resolution

- Differential and single-ended input

- Up to 16 single-ended inputs

- 16x4 differential inputs without gain

- 8x4 differential input with gain

- Built-in differential gain stage

- 1/2x, 1x, 2x, 4x, 8x, 16x, 32x, and 64x gain options

- Single, continuous and scan conversion options

- Four internal inputs

- Internal temperature sensor

- DAC output

- $AV_{CC}$  voltage divided by 10

- 1.1V bandgap voltage

- Four conversion channels with individual input control and result registers

- Enable four parallel configurations and results

- Internal and external reference options

- Compare function for accurate monitoring of user defined thresholds

- Optional event triggered conversion for accurate timing

- Optional DMA transfer of conversion results

- Optional interrupt/event on compare result

# 29.2 Overview

The ADC converts analog signals to digital values. There are two Analog to Digital Converters (ADCs) modules that can be operated simultaneously, individually or synchronized.

The ADC has 12-bit resolution and is capable of converting up to two million samples per second (msps). The input selection is flexible, and both single-ended and differential measurements can be done. For differential measurements, an optional gain stage is available to increase the dynamic range. In addition, several internal signal inputs are available. The ADC can provide both signed and unsigned results.

This is a pipelined ADC that consists of several consecutive stages. The pipelined design allows a high sample rate at a low system clock frequency. It also means that a new input can be sampled and a new ADC conversion started while other ADC conversions are still ongoing. This removes dependencies between sample rate and propagation delay.

The ADC has four conversion channels (0-3) with individual input selection, result registers, and conversion start control. The ADC can then keep and use four parallel configurations and results, and this will ease use for applications with high data throughput or for multiple modules using the ADC independently. It is possible to use DMA to move ADC results directly to memory or peripherals when conversions are done.

Both internal and external reference voltages can be used. An integrated temperature sensor is available for use with the ADC. The output from the DAC,  $AV_{CC}/10$  and the bandgap voltage can also be measured by the ADC.

The ADC has a compare function for accurate monitoring of user defined thresholds with minimum software intervention required.

Figure 29-1. ADC overview.

Two inputs can be sampled simultaneously as both the ADC and the gain stage include sample and hold circuits, and the gain stage has 1x gain setting.

Four inputs can be sampled within 1.5µs without any intervention by the application.

The ADC may be configured for 8- or 12-bit result, reducing the minimum conversion time (propagation delay) from 3.5µs for 12-bit to 2.5µs for 8-bit result.

ADC conversion results are provided left- or right adjusted with optional '1' or '0' padding. This eases calculation when the result is represented as a signed integer (signed 16-bit number).

PORTA and PORTB each has one ADC. Notation of these peripherals are ADCA and ADCB, respectively.

#### Table 37-39. Current consumption for modules and peripherals.

| Symbol          | Parameter                 | Condition <sup>(1)</sup>              |                                  | Min. | Тур. | Max. | Units |

|-----------------|---------------------------|---------------------------------------|----------------------------------|------|------|------|-------|

|                 | ULP oscillator            |                                       |                                  |      | 1.0  |      |       |

|                 | 32.768kHz int. oscillator |                                       |                                  |      | 27   |      |       |

|                 | 2MHz int. oscillator      |                                       |                                  |      |      |      |       |

|                 |                           | DFLL enabled with                     | 32.768kHz int. osc. as reference |      | 120  |      |       |

|                 | 32MHz int. oscillator     |                                       |                                  |      | 310  |      |       |

|                 |                           | DFLL enabled with                     | 32.768kHz int. osc. as reference |      | 560  |      | μA    |

|                 | Watchdog timer            |                                       |                                  |      | 1.0  |      |       |

|                 | BOD                       | Continuous mode                       |                                  |      | 126  |      |       |

|                 | BOD                       | Sampled mode, inc                     | cludes ULP oscillator            |      | 1.2  |      |       |

|                 | Internal 1.0V reference   |                                       |                                  |      | 89   |      |       |

|                 | Temperature sensor        |                                       |                                  |      | 83   |      |       |

| I <sub>CC</sub> |                           | 250ksps<br>V <sub>REF</sub> = Ext ref |                                  |      | 3.0  |      |       |

|                 | ADC                       |                                       | CURRLIMIT = LOW                  |      | 2.6  |      | mA    |

|                 | ADC                       |                                       | CURRLIMIT = MEDIUM               |      | 2.1  |      |       |

|                 |                           |                                       | CURRLIMIT = HIGH                 |      | 1.6  |      |       |

|                 | DAC                       | 250ksps                               | Normal mode                      |      | 1.9  |      |       |

|                 | DAC                       | V <sub>REF</sub> = Ext ref<br>No load | Low Power mode                   |      | 1.1  |      |       |

|                 | AC                        | High speed mode                       |                                  |      | 324  |      |       |

|                 | AC                        | Low power mode                        |                                  |      | 122  |      |       |

|                 | DMA                       | 615KBps between                       | I/O registers and SRAM           |      | 140  |      | μA    |

|                 | Timer/counter             |                                       |                                  |      | 20   |      |       |

|                 | USART                     | Rx and Tx enabled                     | I, 9600 BAUD                     |      | 4    |      |       |

|                 | Flash memory and EEPRO    | M programming                         |                                  |      | 4    |      | mA    |

Note: 1. All parameters measured as the difference in current consumption between module enabled and disabled. All data at V<sub>CC</sub> = 3.0V, Clk<sub>SYS</sub> = 1MHz external clock without prescaling, T = 25°C unless other conditions are given.

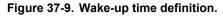

#### 37.2.4 Wake-up time from sleep modes

| Symbol              | Parameter                          | Condition                     | Min. | Typ. <sup>(1)</sup> | Max. | Units |

|---------------------|------------------------------------|-------------------------------|------|---------------------|------|-------|

|                     |                                    | External 2MHz clock           |      | 2.0                 |      |       |

|                     | Wake-up time from idle,            | 32.768kHz internal oscillator |      | 120                 |      |       |

|                     | standby, and extended standby mode | 2MHz internal oscillator      |      | 2.0                 |      |       |

| +                   |                                    | 32MHz internal oscillator     |      | 0.2                 |      | 110   |

| <sup>L</sup> wakeup |                                    | External 2MHz clock           |      | 4.5                 |      | μs    |

|                     | Wake-up time from Power-save       | 32.768kHz internal oscillator |      | 320                 |      |       |

|                     | and Power-down mode                | 2MHz internal oscillator      |      | 10                  |      |       |

|                     |                                    | 32MHz internal oscillator     |      | 5.5                 |      |       |

# Note: 1. The wake-up time is the time from the wake-up request is given until the peripheral clock is available on pin, see Figure 37-9. All peripherals and modules start execution from the first clock cycle, expect the CPU that is halted for four clock cycles before program execution starts.

### 37.2.6 ADC characteristics

| Symbol            | Parameter                   | Condition                        | Min.                  | Тур. | Max.                   | Units |

|-------------------|-----------------------------|----------------------------------|-----------------------|------|------------------------|-------|

| AV <sub>CC</sub>  | Analog supply voltage       |                                  | V <sub>CC</sub> - 0.3 |      | V <sub>CC</sub> + 0.3  | V     |

| V <sub>REF</sub>  | Reference voltage           |                                  | 1                     |      | AV <sub>CC</sub> - 0.6 | v     |

| R <sub>in</sub>   | Input resistance            | Switched                         |                       | 5.0  |                        | kΩ    |

| C <sub>in</sub>   | Input capacitance           | Switched                         |                       | 5.0  |                        | pF    |

| R <sub>AREF</sub> | Reference input resistance  | (leakage only)                   |                       | >10  |                        | MΩ    |

| C <sub>AREF</sub> | Reference input capacitance | Static load                      |                       | 7    |                        | pF    |

| V <sub>IN</sub>   | Input range                 |                                  | -0.1                  |      | AV <sub>CC</sub> +0.1  |       |

|                   | Conversion range            | Differential mode, Vinp - Vinn   | -V <sub>REF</sub>     |      | $V_{REF}$              | V     |

| V <sub>IN</sub>   | Conversion range            | Single ended unsigned mode, Vinp | -ΔV                   |      | $V_{REF}$ - $\Delta V$ |       |

| ΔV                | Fixed offset voltage        |                                  |                       | 190  |                        | LSB   |

Table 37-42. Power supply, reference and input range.

### Table 37-43. Clock and timing.

| Symbol             | Parameter                 | Condition                                          | Min. | Тур. | Max. | Units                        |

|--------------------|---------------------------|----------------------------------------------------|------|------|------|------------------------------|

| Clk <sub>ADC</sub> | ADC Clock frequency       | Maximum is 1/4 of peripheral clock<br>frequency    | 100  |      | 2000 | kHz                          |

|                    |                           | Measuring internal signals                         | 100  |      | 125  | _                            |

|                    |                           | Current limitation (CURRLIMIT) off                 | 100  |      | 2000 |                              |

| £                  | Comple rate               | CURRLIMIT = LOW                                    | 100  |      | 1500 | kana                         |

| f <sub>ADC</sub>   | Sample rate               | CURRLIMIT = MEDIUM                                 | 100  |      | 1000 | ksps                         |

|                    |                           | CURRLIMIT = HIGH                                   | 100  |      | 500  | _                            |

|                    | Sampling time             | 1/2 Clk <sub>ADC</sub> cycle                       | 0.25 |      | 5    | μs                           |

|                    | Conversion time (latency) | (RES+2)/2+(GAIN !=0)<br>RES (Resolution) = 8 or 12 | 5    |      | 8    | Clk <sub>ADC</sub><br>cycles |

|                    | Start-up time             | ADC clock cycles                                   |      | 12   | 24   | Clk <sub>ADC</sub><br>cycles |

|                    | ADC sottling time         | After changing reference or input mode             |      | 7    | 7    | Clk <sub>ADC</sub>           |

|                    | ADC settling time         | After ADC flush                                    |      | 1    | 1    | cycles                       |

#### Table 37-48. Accuracy characteristics.

| Symbol             | Parameter                    | Condition                          |                        | Min. | Тур. | Max. | Units |

|--------------------|------------------------------|------------------------------------|------------------------|------|------|------|-------|

| RES                | Input resolution             |                                    |                        |      |      | 12   | Bits  |

|                    |                              | $\gamma = E_{\rm V} + 1.0 \gamma$  | V <sub>CC</sub> = 1.6V |      | ±2.0 | ±3   |       |

|                    |                              | V <sub>REF</sub> = Ext 1.0V        | V <sub>CC</sub> = 3.6V |      | ±1.5 | ±2.5 |       |

| INL <sup>(1)</sup> | Integral non-linearity       | V <sub>REF</sub> =AV <sub>CC</sub> | V <sub>CC</sub> = 1.6V |      | ±2.0 | ±4   |       |

|                    | Integral non-intearity       | VREF-AVCC                          | V <sub>CC</sub> = 3.6V |      | ±1.5 | ±4   |       |

|                    |                              |                                    | V <sub>CC</sub> = 1.6V |      | ±5.0 |      |       |

|                    |                              | V <sub>REF</sub> =INT1V            | V <sub>CC</sub> = 3.6V |      | ±5.0 |      |       |

|                    | Differential new linearity   | V <sub>REF</sub> =Ext 1.0V         | V <sub>CC</sub> = 1.6V |      | ±1.5 | 3.0  | lsb   |

|                    |                              |                                    | V <sub>CC</sub> = 3.6V |      | ±0.6 | 1.5  |       |

| DNL <sup>(1)</sup> |                              | V <sub>REF</sub> =AV <sub>CC</sub> | V <sub>CC</sub> = 1.6V |      | ±1.0 | 3.5  |       |

| DINL               | Differential non-linearity   |                                    | V <sub>CC</sub> = 3.6V |      | ±0.6 | 1.5  |       |

|                    |                              | V <sub>REF</sub> =INT1V            | V <sub>CC</sub> = 1.6V |      | ±4.5 |      |       |

|                    |                              | V <sub>REF</sub> -INTIV            | V <sub>CC</sub> = 3.6V |      | ±4.5 |      |       |

|                    | Gain error                   | After calibration                  |                        |      | <4   |      |       |

|                    | Gain calibration step size   |                                    |                        |      | 4    |      |       |

|                    | Gain calibration drift       | V <sub>REF</sub> = Ext 1.0V        |                        |      | <0.2 |      | mV/K  |

|                    | Offset error                 | After calibration                  |                        |      | <1   |      | lsb   |

|                    | Offset calibration step size |                                    |                        |      | 1    |      |       |

Note: 1. Maximum numbers are based on characterisation and not tested in production, and valid for 5% to 95% output voltage range.

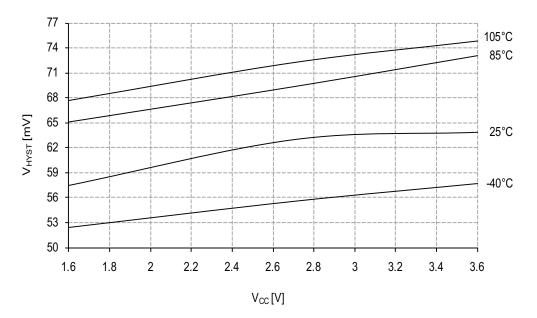

### 37.2.8 Analog Comparator Characteristics

#### Table 37-49. Analog Comparator characteristics.

| Symbol            | Parameter                | Condition              | Min. | Тур. | Max.                  | Units |

|-------------------|--------------------------|------------------------|------|------|-----------------------|-------|

| V <sub>off</sub>  | Input offset voltage     |                        |      | <±10 |                       | mV    |

| l <sub>lk</sub>   | Input leakage current    |                        |      | <1   |                       | nA    |

|                   | Input voltage range      |                        | -0.1 |      | AV <sub>CC</sub> +0.1 | V     |

| V <sub>hys1</sub> | Hysteresis, none         |                        |      | 0    |                       |       |

| M                 | Hystorasia small         | mode = High Speed (HS) |      | 22   |                       |       |

| V <sub>hys2</sub> | Hysteresis, small mode = | mode = Low Power (LP)  |      | 30   |                       | mV    |

| V                 |                          | mode = HS              |      | 43   |                       |       |

| V <sub>hys3</sub> | Hysteresis, large        | mode = LP              |      | 60   |                       |       |

| Symbol             | Parameter                            | Condition                       |           | Min. | Тур. | Max. | Units |

|--------------------|--------------------------------------|---------------------------------|-----------|------|------|------|-------|

|                    |                                      | V <sub>CC</sub> = 3.0V, T= 85°C | mode = HS |      | 60   | 90   |       |

| t <sub>delay</sub> | t <sub>delay</sub> Propagation delay | mode = HS                       |           |      | 60   |      | ns    |

|                    |                                      | V <sub>CC</sub> = 3.0V, T= 85°C | mode = LP |      | 130  |      |       |

|                    | Current source calibration           | Single mode                     |           | 2    |      | 8    |       |

|                    | range                                | Double mode                     |           | 4    |      | 16   | μs    |

|                    | 64-Level Voltage Scaler              | Integral non-linearity (INL)    |           |      | 0.3  | 0.5  | lsb   |

# 37.2.9 Bandgap and Internal 1.0V Reference Characteristics

### Table 37-50. Bandgap and Internal 1.0V reference characteristics.

| Symbol | Parameter                                | Condition                            | Min. | Тур.                     | Max. | Units |

|--------|------------------------------------------|--------------------------------------|------|--------------------------|------|-------|

|        | Startup time                             | As reference for ADC or DAC          | 1 (  | Clk <sub>PER</sub> + 2.5 | δµs  |       |

|        | Startup time                             | As input voltage to ADC and AC       |      | 1.5                      |      | μs    |

|        | Bandgap voltage                          |                                      |      | 1.1                      |      | V     |

| INT1V  | Internal 1.00V reference for ADC and DAC | T= 85°C, after calibration           | 0.99 | 1                        | 1.01 | V     |

|        | Variation over voltage and temperature   | Relative to T= 85°C, $V_{CC}$ = 3.0V |      | ±1.0                     |      | %     |

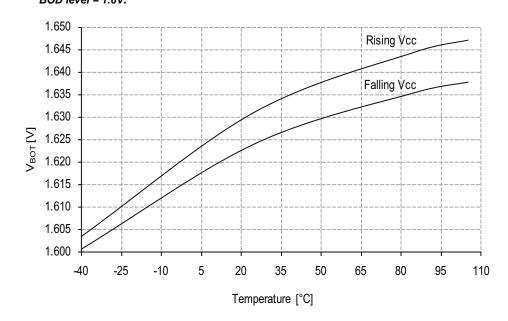

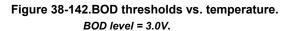

### **37.2.10 Brownout Detection Characteristics**

#### Table 37-51. Brownout detection characteristics.

| Symbol            | Parameter                           | Condition       | Min. | Тур. | Max. | Units |  |  |

|-------------------|-------------------------------------|-----------------|------|------|------|-------|--|--|

|                   | BOD level 0 falling V <sub>CC</sub> |                 | 1.60 | 1.62 | 1.72 |       |  |  |

|                   | BOD level 1 falling V <sub>CC</sub> |                 |      | 1.8  |      |       |  |  |

|                   | BOD level 2 falling V <sub>CC</sub> |                 |      | 2.0  |      | V     |  |  |

| V <sub>BOT</sub>  | BOD level 3 falling $V_{CC}$        |                 |      | 2.2  |      |       |  |  |

|                   | BOD level 4 falling V <sub>CC</sub> |                 |      | 2.4  |      |       |  |  |

|                   | BOD level 5 falling V <sub>CC</sub> |                 |      | 2.6  |      |       |  |  |

|                   | BOD level 6 falling V <sub>CC</sub> |                 |      | 2.8  |      |       |  |  |

|                   | BOD level 7 falling V <sub>CC</sub> |                 |      | 3.0  |      |       |  |  |

| t <sub>BOD</sub>  | Detection time                      | Continuous mode |      | 0.4  |      | μs    |  |  |

|                   |                                     | Sampled mode    |      | 1000 |      |       |  |  |

| V <sub>HYST</sub> | Hysteresis                          |                 |      | 1.4  |      | %     |  |  |

| Symbol             | Parameter                         | Condition                |                            | Min. | Тур. | Max.                    | Units |

|--------------------|-----------------------------------|--------------------------|----------------------------|------|------|-------------------------|-------|

| Rq                 | Negative impedance <sup>(1)</sup> | FRQRANGE=0               | 0.4MHz resonator, CL=100pF |      | 13k  |                         | Ω     |

|                    |                                   |                          | 1MHz crystal, CL=20pF      |      | 9k   |                         |       |

|                    |                                   |                          | 2MHz crystal, CL=20pF      |      | 2.2k |                         |       |

|                    |                                   | FRQRANGE=1               | 1MHz crystal, CL=20pF      |      | 2.3k |                         |       |

|                    |                                   |                          | 2MHz crystal, CL=20pF      |      | 8k   |                         |       |

|                    |                                   |                          | 9MHz crystal, CL=20pF      |      | 200  |                         |       |

|                    |                                   | FRQRANGE=2               | 8MHz crystal, CL=20pF      |      | 225  |                         |       |

|                    |                                   |                          | 9MHz crystal, CL=20pF      |      | 300  |                         |       |

|                    |                                   |                          | 12MHz crystal, CL=10pF     |      | 175  |                         |       |

|                    |                                   |                          | 8MHz crystal, CL=20pF      |      | 340  |                         |       |

|                    |                                   | FRQRANGE=3               | 9MHz crystal, CL=20pF      |      | 400  |                         |       |

|                    |                                   |                          | 12MHz crystal, CL=10pF     |      | 330  |                         |       |

|                    |                                   |                          | 12MHz crystal, CL=12pF     |      | 230  |                         |       |

|                    |                                   |                          | 16MHz crystal, CL=10pF     |      | 115  |                         |       |

|                    | ESR                               | SF = safety factor       |                            |      |      | min(R <sub>Q</sub> )/SF | kΩ    |

|                    | Start-up time                     | XOSCPWR=0,<br>FRQRANGE=0 | 0.4MHz resonator, CL=100pF |      | 1.0  |                         | ms    |

|                    |                                   | XOSCPWR=0,<br>FRQRANGE=1 | 2MHz crystal, CL=20pF      |      | 2.6  |                         |       |

|                    |                                   | XOSCPWR=0,<br>FRQRANGE=2 | 8MHz crystal, CL=20pF      |      | 0.8  |                         |       |

|                    |                                   | XOSCPWR=0,<br>FRQRANGE=3 | 12MHz crystal, CL=20pF     |      | 1.0  |                         |       |

|                    |                                   | XOSCPWR=1,<br>FRQRANGE=3 | 16MHz crystal, CL=20pF     |      | 1.4  |                         |       |

| C <sub>XTAL1</sub> | Parasitic capacitance X           | TAL1 pin                 |                            |      | 6    |                         |       |

| C <sub>XTAL2</sub> | Parasitic capacitance X           | TAL2 pin                 |                            |      | 10   |                         | pF    |

| C <sub>LOAD</sub>  | Parasitic capacitance loa         | ad                       |                            |      | 3.8  |                         |       |

Note: 1. Numbers for negative impedance are not tested in production but guaranteed from design and characterization.

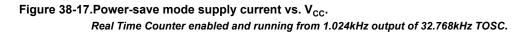

#### 38.1.1.4 Power-save mode supply current

#### 38.1.1.5 Standby mode supply current

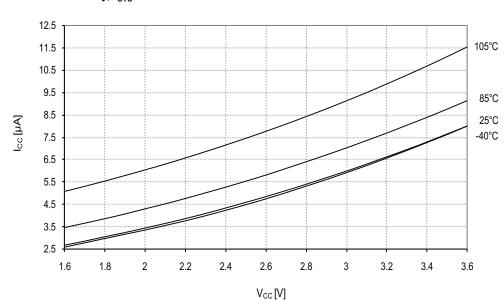

#### Figure 38-18. Standby supply current vs. $V_{CC}$ . Standby, $f_{SYS} = 1MHz$ .

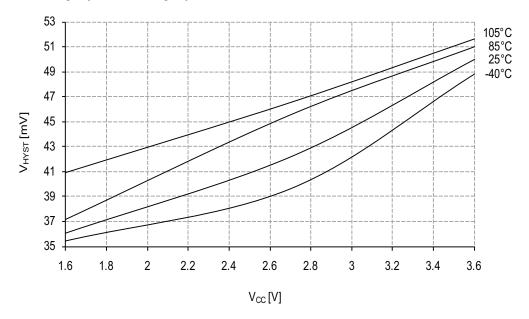

Figure 38-141.BOD thresholds vs. temperature. BOD level = 1.6V.

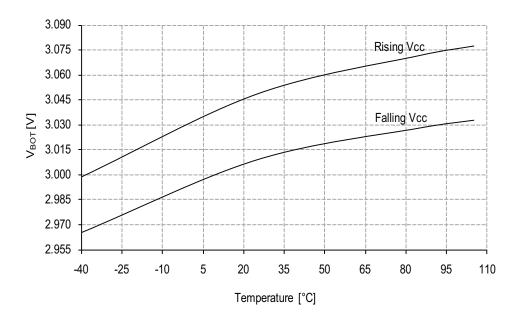

Figure 38-157. 32MHz internal oscillator frequency vs. temperature. DFLL disabled.

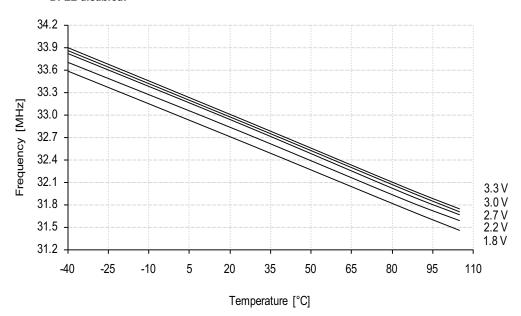

Figure 38-158. 32MHz internal oscillator frequency vs. temperature. DFLL enabled, from the 32.768kHz internal oscillator.

|     | 36.3                        | 100C2                                                                                                  |  |  |  |  |  |

|-----|-----------------------------|--------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 37. | <b>Elec</b><br>37.1<br>37.2 | trical Characteristics         74           ATxmega64A1U         74           ATxmega128A1U         97 |  |  |  |  |  |

| 38. | Турі                        | Typical Characteristics                                                                                |  |  |  |  |  |

|     | 38.1                        | ATxmega64A1U                                                                                           |  |  |  |  |  |

|     | 38.2                        | ATxmega128A1U                                                                                          |  |  |  |  |  |

| 39. | Erra                        | ta                                                                                                     |  |  |  |  |  |

|     | 39.1                        | ATxmega64A1U                                                                                           |  |  |  |  |  |

|     | 39.2                        | ATxmega128A1U                                                                                          |  |  |  |  |  |

| 40. | Data                        | sheet Revision History                                                                                 |  |  |  |  |  |

|     | 40.1                        | 8385I – 07/2014                                                                                        |  |  |  |  |  |

|     | 40.2                        | 8385H – 05/2014                                                                                        |  |  |  |  |  |

|     | 40.3                        | 8385G – 11/2013                                                                                        |  |  |  |  |  |

|     | 40.4                        | 8385F – 12/2012                                                                                        |  |  |  |  |  |

|     | 40.5                        | 8385E – 11/2012                                                                                        |  |  |  |  |  |

|     | 40.6                        | 8385D – 07/2012                                                                                        |  |  |  |  |  |

|     | 40.7                        | 8385C – 07/2012                                                                                        |  |  |  |  |  |

|     | 40.8                        | 8385B – 03/2012                                                                                        |  |  |  |  |  |

|     | 40.9                        | 8385A – 11/2011                                                                                        |  |  |  |  |  |

| Tab | le of                       | Contents                                                                                               |  |  |  |  |  |