Welcome to E-XFL.COM

Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

### Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application enacific microcontrollars are angineered to

### Details

ĿХЕ

| Details                 |                                                                             |

|-------------------------|-----------------------------------------------------------------------------|

| Product Status          | Active                                                                      |

| Applications            | USB Microcontroller                                                         |

| Core Processor          | M8C                                                                         |

| Program Memory Type     | FLASH (16kB)                                                                |

| Controller Series       | CY7C642xx                                                                   |

| RAM Size                | 1K x 8                                                                      |

| Interface               | I²C, USB                                                                    |

| Number of I/O           | 50                                                                          |

| Voltage - Supply        | 3V ~ 5.25V                                                                  |

| Operating Temperature   | -40°C ~ 85°C                                                                |

| Mounting Type           | Surface Mount                                                               |

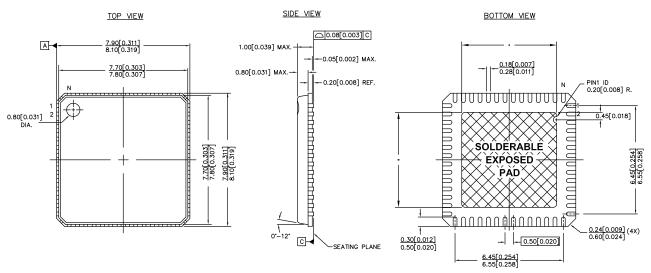

| Package / Case          | 56-VFQFN Exposed Pad                                                        |

| Supplier Device Package | 56-QFN-EP (8×8)                                                             |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/cy7c64215-56ltxi |

|                         |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

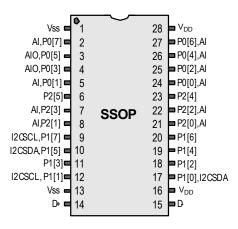

## 28-Pin Part Pinout

The CY7C64215 enCoRe III device is available in a 28-pin package which is listed and illustrated in the following table. Every port pin (labeled with a "P") is capable of digital I/O. However,  $V_{SS}$  and  $V_{DD}$  are not capable of digital I/O.

### Table 3. 28-Pin Part Pinout (SSOP)

| Pin | Ту      | pe     | Name     | Description                                |

|-----|---------|--------|----------|--------------------------------------------|

| No. | Digital | Analog | Name     | Description                                |

| 1   | Po      | wer    | GND      | Ground connection.                         |

| 2   | I/O     | I, M   | P0[7]    | Analog column mux input.                   |

| 3   | I/O     | I/O,M  | P0[5]    | Analog column mux input and column output. |

| 4   | I/O     | I/O,M  | P0[3]    | Analog column mux input and column output. |

| 5   | I/O     | I,M    | P0[1]    | Analog column mux input.                   |

| 6   | I/O     | М      | P2[5]    |                                            |

| 7   | I/O     | М      | P2[3]    | Direct switched capacitor block input.     |

| 8   | I/O     | М      | P2[1]    | Direct switched capacitor block input.     |

| 9   | I/O     | М      | P1[7]    | I <sup>2</sup> C SCL                       |

| 10  | I/O     | М      | P1[5]    | I <sup>2</sup> C SDA                       |

| 11  | I/O     | М      | P1[3]    |                                            |

| 12  | I/O     | М      | P1[1]    | I <sup>2</sup> C SCL, ISSP-SCLK.           |

| 13  | Power   |        | GND      | Ground connection.                         |

| 14  | U       | SB     | D+       |                                            |

| 15  | U       | SB     | D-       |                                            |

| 16  | Po      | wer    | $V_{DD}$ | Supply voltage.                            |

| 17  | I/O     | М      | P1[0]    | I <sup>2</sup> C SCL, ISSP-SDATA.          |

| 18  | I/O     | М      | P1[2]    |                                            |

| 19  | I/O     | М      | P1[4]    |                                            |

| 20  | I/O     | М      | P1[6]    |                                            |

| 21  | I/O     | М      | P2[0]    | Direct switched capacitor block input.     |

| 22  | I/O     | М      | P2[2]    | Direct switched capacitor block input.     |

| 23  | I/O     | М      | P2[4]    | External analog ground (AGND) input.       |

| 24  | I/O     | М      | P0[0]    | Analog column mux input.                   |

| 25  | I/O     | М      | P0[2]    | Analog column mux input and column output. |

| 26  | I/O     | М      | P0[4]    | Analog column mux input and column output. |

| 27  | I/O     | М      | P0[6]    | Analog column mux input.                   |

| 28  | Po      | wer    | $V_{DD}$ | Supply voltage.                            |

# Figure 4. CY7C64215 28-Pin enCoRe III Device

LEGEND A = Analog, I = Input, O = Output, and M = Analog Mux Input.

# Register Map Bank 1 Table: Configuration Space

| Name                                    | Addr<br>(1,Hex) | Access           | Name      | Addr<br>(1,Hex) | Access | Name                    | Addr<br>(1,Hex) | Access | Name                 | Addr<br>(1,Hex) | Access   |

|-----------------------------------------|-----------------|------------------|-----------|-----------------|--------|-------------------------|-----------------|--------|----------------------|-----------------|----------|

| PRT0DM0                                 | 00              | RW               | PMA0_WA   | 40              | RW     | ASC10CR0                | 80              | RW     | USBIO_CR2            | CO              | RW       |

| PRT0DM1                                 | 01              | RW               | PMA1_WA   | 41              | RW     | ASC10CR1                | 81              | RW     | USB_CR1              | C1              | #        |

| PRT0IC0                                 | 02              | RW               | PMA2_WA   | 42              | RW     | ASC10CR2                | 82              | RW     |                      |                 |          |

| PRT0IC1                                 | 03              | RW               | PMA3_WA   | 43              | RW     | ASC10CR3                | 83              | RW     |                      |                 | -        |

| PRT1DM0                                 | 04              | RW               | PMA4_WA   | 44              | RW     | ASD11CR0                | 84              | RW     | EP1_CR0              | C4              | #        |

| PRT1DM1                                 | 05              | RW               | PMA5_WA   | 45              | RW     | ASD11CR1                | 85              | RW     | EP2_CR0              | C5              | #        |

| PRT1IC0                                 | 06              | RW               | PMA6_WA   | 46              | RW     | ASD11CR2                | 86              | RW     | EP3_CR0              | C6              | #        |

| PRT1IC1                                 | 07              | RW               | PMA7_WA   | 47              | RW     | ASD11CR3                | 87              | RW     | EP4_CR0              | C7              | #        |

| PRT2DM0                                 | 08              | RW               | _         | 48              |        |                         | 88              | 1      |                      | C8              |          |

| PRT2DM1                                 | 09              | RW               |           | 49              |        |                         | 89              | 1      |                      | C9              |          |

| PRT2IC0                                 | 0A              | RW               |           | 4A              |        |                         | 8A              |        |                      | CA              |          |

| PRT2IC1                                 | 0B              | RW               |           | 4B              |        |                         | 8B              |        |                      | СВ              |          |

| PRT3DM0                                 | 0C              | RW               |           | 4C              |        |                         | 8C              |        |                      | CC              |          |

| PRT3DM1                                 | 0D              | RW               |           | 4D              |        |                         | 8D              |        |                      | CD              | -        |

| PRT3IC0                                 | 0E              | RW               |           | 4E              |        |                         | 8E              | 1      |                      | CE              |          |

| PRT3IC1                                 | 0F              | RW               |           | 4F              |        |                         | 8F              |        |                      | CF              | -        |

| PRT4DM0                                 | 10              | RW               | PMA0_RA   | 50              | RW     |                         | 90              | ł      | GDI_O_IN             | D0              | RW       |

| PRT4DM1                                 | 11              | RW               | PMA1 RA   | 51              | RW     | ASD20CR1                | 91              | RW     | GDI E IN             | D1              | RW       |

| PRT4IC0                                 | 12              | RW               | PMA2_RA   | 52              | RW     | ASD20CR2                | 92              | RW     | GDI_O_OU             | D2              | RW       |

| PRT4IC1                                 | 13              | RW               | PMA3_RA   | 53              | RW     | ASD20CR3                | 93              | RW     | GDI_E_OU             | D3              | RW       |

| PRT5DM0                                 | 14              | RW               | PMA4_RA   | 55              | RW     | ASC21CR0                | 94              | RW     | 552_00               | D3              | +        |

| PRT5DM0                                 | 14              | RW               | PMA5_RA   | 55              | RW     | ASC21CR1                | 95              | RW     |                      | D4<br>D5        | ───      |

| PRT5IC0                                 | 16              | RW               | PMA6_RA   | 56              | RW     | ASC21CR2                | 96              | RW     |                      | D5              | ───      |

| PRT5IC1                                 | 10              | RW               | PMA7_RA   | 57              | RW     | ASC21CR3                | 97              | RW     |                      | D7              | <u> </u> |

| 11(15)01                                | 18              | 1.00             |           | 58              | 1      | 700210103               | 98              | 1      | MUX_CR0              | D8              | RW       |

|                                         | 19              | -                |           | 59              |        |                         | 99              | -      | MUX_CR1              | D0              | RW       |

|                                         | 19<br>1A        | -                |           | 59<br>5A        |        |                         | 99<br>9A        | -      | MUX_CR2              | DA              | RW       |

|                                         | 1A<br>1B        |                  |           | 5A<br>5B        |        |                         | 9A<br>9B        |        | MUX_CR3              | DA              | RW       |

| PRT7DM0                                 |                 | RW               |           | 5D<br>5C        |        |                         | 9D<br>9C        |        | MUX_CR3              | DC              | RVV      |

|                                         | 1C              |                  |           |                 |        |                         |                 |        |                      |                 | DW/      |

| PRT7DM1                                 | 1D              | RW               |           | 5D              |        |                         | 9D              |        | OSC_GO_EN<br>OSC_CR4 | DD              | RW       |

| PRT7IC0<br>PRT7IC1                      | 1E              | RW               |           | 5E              |        |                         | 9E              |        |                      | DE              | RW       |

|                                         | 1F              | RW               |           | 5F              | DW     |                         | 9F              |        | OSC_CR3              | DF              | RW       |

| DBB00FN                                 | 20              | RW               | CLK_CR0   | 60              | RW     |                         | A0              |        | OSC_CR0<br>OSC_CR1   | E0              | RW       |

| DBB00IN                                 | 21              | RW               | CLK_CR1   | 61              | RW     |                         | A1              |        |                      | E1              | RW       |

| DBB00OU                                 | 22              | RW               | ABF_CR0   | 62              | RW     |                         | A2              |        | OSC_CR2              | E2              | RW       |

| DDDALEN                                 | 23              | DW               | AMD_CR0   | 63              | RW     |                         | A3              |        | VLT_CR               | E3              | RW       |

| DBB01FN                                 | 24              | RW               | CMP_GO_EN | 64              | RW     |                         | A4              |        | VLT_CMP              | E4              | R        |

| DBB01IN                                 | 25              | RW               | AND 004   | 65              | RW     |                         | A5              |        |                      | E5              |          |

| DBB01OU                                 | 26              | RW               | AMD_CR1   | 66              | RW     |                         | A6              |        |                      | E6              |          |

|                                         | 27              |                  | ALT_CR0   | 67              | RW     |                         | A7              |        |                      | E7              |          |

| DCB02FN                                 | 28              | RW               |           | 68              |        |                         | A8              |        | IMO_TR               | E8              | W        |

| DCB02IN                                 | 29              | RW               |           | 69              |        |                         | A9              |        | ILO_TR               | E9              | W        |

| DCB02OU                                 | 2A              | RW               |           | 6A              |        |                         | AA              |        | BDG_TR               | EA              | RW       |

| B 0 B 0 B 0 B 0 B 0 B 0 B 0 B 0 B 0 B 0 | 2B              | 514              |           | 6B              | 514    |                         | AB              |        | ECO_TR               | EB              | W        |

| DCB03FN                                 | 2C              | RW               | TMP_DR0   | 6C              | RW     | l                       | AC              |        | MUX_CR4              | EC              | RW       |

| DCB03IN                                 | 2D              | RW               | TMP_DR1   | 6D              | RW     | l                       | AD              |        | MUX_CR5              | ED              | RW       |

| DCB03OU                                 | 2E              | RW               | TMP_DR2   | 6E              | RW     |                         | AE              |        |                      | EE              |          |

|                                         | 2F              |                  | TMP_DR3   | 6F              | RW     |                         | AF              |        |                      | EF              |          |

|                                         | 30              |                  | ACB00CR3  | 70              | RW     | RDIORI                  | B0              | RW     |                      | F0              |          |

|                                         | 31              |                  | ACB00CR0  | 71              | RW     | RDI0SYN                 | B1              | RW     |                      | F1              |          |

|                                         | 32              |                  | ACB00CR1  | 72              | RW     | RDI0IS                  | B2              | RW     |                      | F2              |          |

|                                         | 33              |                  | ACB00CR2  | 73              | RW     | RDI0LT0                 | B3              | RW     |                      | F3              |          |

|                                         | 34              |                  | ACB01CR3  | 74              | RW     | RDI0LT1                 | B4              | RW     |                      | F4              |          |

|                                         | 35              |                  | ACB01CR0  | 75              | RW     | RDI0RO0                 | B5              | RW     |                      | F5              |          |

|                                         | 36              |                  | ACB01CR1  | 76              | RW     | RDI0RO1                 | B6              | RW     |                      | F6              |          |

|                                         | 37              |                  | ACB01CR2  | 77              | RW     |                         | B7              |        | CPU_F                | F7              | RL       |

|                                         | 38              |                  |           | 78              |        |                         | B8              |        |                      | F8              |          |

|                                         | 39              |                  |           | 79              |        | 1                       | B9              | İ      |                      | F9              |          |

|                                         | 3A              |                  |           | 7A              | 1      |                         | BA              | Ì      |                      | FA              | 1        |

|                                         | 3B              |                  | 1         | 7B              | 1      | 1                       | BB              | İ      |                      | FB              | 1        |

|                                         | 3C              | İ                | 1         | 7C              |        | 1                       | BC              |        |                      | FC              | 1        |

|                                         | 3D              | İ                | 1         | 7D              |        | I                       | BD              |        | DAC_CR               | FD              | RW       |

|                                         | 3E              |                  | 1         | 7E              | 1      | 1                       | BE              | 1      | <br>CPU_SCR1         | FE              | #        |

|                                         | 3F              | l                | 1         | 7F              | 1      | 1                       | BF              |        | CPU SCR0             | FF              | #        |

|                                         |                 | and should not b |           |                 | 1      | # Access is bit specifi |                 | 1      |                      | 1               | 1        |

# Absolute Maximum Ratings

## Table 5. Absolute Maximum Ratings

| Parameter             | Description                                                         | Min                     | Тур | Max                     | Unit  | Notes                                                    |

|-----------------------|---------------------------------------------------------------------|-------------------------|-----|-------------------------|-------|----------------------------------------------------------|

| T <sub>STG</sub>      | Storage temperature                                                 | -55                     | -   | +100                    | °C    | Higher storage temperatures reduces data retention time. |

| T <sub>BAKETEMP</sub> | Bake temperature                                                    | -                       | 125 | See<br>package<br>label | °C    | -                                                        |

| T <sub>BAKETIME</sub> | Bake time                                                           | See<br>package<br>label | _   | 72                      | Hours | -                                                        |

| T <sub>A</sub>        | Ambient temperature with power applied                              | 0                       | _   | +70                     | °C    | -                                                        |

| V <sub>DD</sub>       | Supply voltage on $V_{DD}$ relative to $V_{SS}$                     | -0.5                    | _   | +6.0                    | V     | -                                                        |

| V <sub>IO</sub>       | DC input voltage                                                    | V <sub>SS</sub> – 0.5   | _   | V <sub>DD</sub> + 0.5   | V     | -                                                        |

| V <sub>IO2</sub>      | DC voltage applied to tristate                                      | $V_{SS} - 0.5$          | _   | V <sub>DD</sub> + 0.5   | V     | -                                                        |

| I <sub>MIO</sub>      | Maximum current into any port pin                                   | -25                     | -   | +50                     | mA    | -                                                        |

| I <sub>MAIO</sub>     | Maximum current into any port pin<br>configured as an analog driver | -50                     | -   | +50                     | mA    | -                                                        |

| ESD                   | Electrostatic discharge voltage                                     | 2000                    | -   | -                       | V     | Human body model ESD.                                    |

| LU                    | Latch up current                                                    | _                       | _   | 200                     | mA    | -                                                        |

# **Operating Temperature**

## Table 6. Operating Temperature

| Parameter       | Description                    | Min | Тур | Max  | Unit | Notes                                                                                                                                                                                                  |

|-----------------|--------------------------------|-----|-----|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>AC</sub> | Commercial ambient temperature | 0   | -   | +70  | °C   | -                                                                                                                                                                                                      |

| T <sub>AI</sub> | Industrial ambient temperature | -40 | Ι   | +85  | °C   | USB operation requires the<br>use of an external clock<br>oscillator and the 56-pin<br>QFN package.                                                                                                    |

| Т               | Junction temperature           | -40 | _   | +100 | °C   | The temperature rise from<br>ambient to junction is<br>package specific. See<br>"Thermal Impedance" on<br>page 32. The user must limit<br>the power consumption to<br>comply with this<br>requirement. |

## DC GPIO Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.15 V to 3.5 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

### Table 8. DC GPIO Specifications

| Parameter        | Description                       | Min                   | Тур | Max  | Unit | Notes                                                                                                                                                                                                                     |

|------------------|-----------------------------------|-----------------------|-----|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R <sub>PU</sub>  | Pull-up resistor                  | 4                     | 5.6 | 8    | kΩ   | -                                                                                                                                                                                                                         |

| R <sub>PD</sub>  | Pull-down resistor                | 4                     | 5.6 | 8    | kΩ   | -                                                                                                                                                                                                                         |

| V <sub>OH</sub>  | High output level                 | V <sub>DD</sub> – 1.0 | -   | _    | V    | $I_{OH}$ = 10 mA, $V_{DD}$ = 4.75 to 5.25 V (8 total<br>loads, 4 on even port pins (for example,<br>P0[2], P1[4]), 4 on odd port pins (for<br>example, P0[3], P1[5])). 80 mA maximum<br>combined I <sub>OH</sub> budget.  |

| V <sub>OL</sub>  | Low output level                  | -                     | _   | 0.75 | V    | $I_{OL}$ = 25 mA, $V_{DD}$ = 4.75 to 5.25 V (8 total<br>loads, 4 on even port pins (for example,<br>P0[2], P1[4]), 4 on odd port pins (for<br>example, P0[3], P1[5])). 150 mA<br>maximum combined I <sub>OL</sub> budget. |

| I <sub>ОН</sub>  | High-level source current         | 10                    | _   | _    | mA   | -                                                                                                                                                                                                                         |

| I <sub>OL</sub>  | Low-level sink current            | 25                    | -   | I    | mA   | -                                                                                                                                                                                                                         |

| V <sub>IL</sub>  | Input low level                   | -                     | -   | 0.8  | V    | V <sub>DD</sub> = 3.15 to 5.25.                                                                                                                                                                                           |

| V <sub>IH</sub>  | Input high level                  | 2.1                   | -   |      | V    | V <sub>DD</sub> = 3.15 to 5.25.                                                                                                                                                                                           |

| V <sub>H</sub>   | Input hysteresis                  | -                     | 60  | -    | mV   | -                                                                                                                                                                                                                         |

| IIL              | Input leakage (absolute value)    | -                     | 1   | -    | nA   | Gross tested to 1 µA.                                                                                                                                                                                                     |

| C <sub>IN</sub>  | Capacitive load on pins as input  | -                     | 3.5 | 10   | pF   | Package and pin dependent.<br>Temp = 25 °C.                                                                                                                                                                               |

| C <sub>OUT</sub> | Capacitive load on pins as output | -                     | 3.5 | 10   | pF   | Package and pin dependent.<br>Temp = 25 °C.                                                                                                                                                                               |

## DC Full-Speed USB Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges when the IMO is selected as system clock: 4.75 V to 5.25 V and 0 °C  $\leq$  T<sub>A</sub>  $\leq$  70 °C, or 3.15 V to 3.5 V and 0 °C  $\leq$  T<sub>A</sub>  $\leq$  70 °C, respectively.

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges when an external clock is selected as the system clock: 4.75 V to 5.25 V and  $-40 \degree C \le T_A \le 85 \degree C$ , or 3.15 V to 3.5 V and  $-40 \degree C \le T_A \le 85 \degree C$ .

Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

### Table 9. DC Full Speed (12 Mbps) USB Specifications

| Parameter         | Description                          | Min | Тур | Max | Unit | Notes                                                      |

|-------------------|--------------------------------------|-----|-----|-----|------|------------------------------------------------------------|

| USB Interfa       | ace                                  |     |     |     |      |                                                            |

| V <sub>DI</sub>   | Differential input sensitivity       | 0.2 | -   | -   | V    | (D+) – (D–)                                                |

| V <sub>CM</sub>   | Differential input common mode range | 0.8 | -   | 2.5 | V    | -                                                          |

| V <sub>SE</sub>   | Single-ended receiver threshold      | 0.8 | -   | 2.0 | V    | -                                                          |

| C <sub>IN</sub>   | Transceiver capacitance              | -   | -   | 20  | pF   | -                                                          |

| I <sub>IO</sub>   | High Z state data line leakage       | -10 | -   | 10  | μA   | 0 V < V <sub>IN</sub> < 3.3 V.                             |

| R <sub>EXT</sub>  | External USB series resistor         | 23  | -   | 25  | Ω    | In series with each USB pin.                               |

| V <sub>UOH</sub>  | Static output high, driven           | 2.8 | -   | 3.6 | V    | 15 k $\Omega$ ± 5% to ground. Internal pull-up enabled.    |

| V <sub>UOHI</sub> | Static output high, idle             | 2.7 | -   | 3.6 | V    | 15 k $\Omega \pm 5\%$ to ground. Internal pull-up enabled. |

| V <sub>UOL</sub>  | Static output low                    | -   | -   | 0.3 | V    | 15 k $\Omega$ ± 5% to ground. Internal pull-up enabled.    |

| Z <sub>O</sub>    | USB driver output impedance          | 28  | -   | 44  | Ω    | Including R <sub>EXT</sub> resistor.                       |

| V <sub>CRS</sub>  | D+/D– crossover voltage              | 1.3 | -   | 2.0 | V    | -                                                          |

### DC Analog Output Buffer Specifications

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40 \text{ °C} \le T_A \le 85 \text{ °C}$ , or 3.15 V to 3.5 V and  $-40 \text{ °C} \le T_A \le 85 \text{ °C}$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

Table 10. 5 V DC Analog Output Buffer Specifications

| Parameter            | Description                                                                                        | Min                                                        | Тур        | Max                                                        | Unit     | Notes                                                                                                         |

|----------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------|------------------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------|

| CL                   | Load Capacitance                                                                                   | _                                                          | -          | 200                                                        | pF       | This specification applies to the<br>external circuit that is being<br>driven by the analog output<br>buffer. |

| V <sub>OSOB</sub>    | Input offset voltage (absolute value)                                                              | -                                                          | 3          | 12                                                         | mV       | -                                                                                                             |

| TCV <sub>OSOB</sub>  | Average input offset voltage drift                                                                 | -                                                          | +6         | -                                                          | μV/°C    | -                                                                                                             |

| V <sub>CMOB</sub>    | Common mode input voltage range                                                                    | 0.5                                                        | -          | V <sub>DD</sub> – 1.0                                      | V        | -                                                                                                             |

| R <sub>OUTOB</sub>   | Output resistance<br>Power = low<br>Power = high                                                   |                                                            | 0.6<br>0.6 |                                                            | W<br>W   | -                                                                                                             |

| V <sub>OHIGHOB</sub> | High output voltage swing<br>(Load = 32 ohms to V <sub>DD</sub> /2)<br>Power = low<br>Power = high | 0.5 × V <sub>DD</sub> + 1.1<br>0.5 × V <sub>DD</sub> + 1.1 |            |                                                            | V<br>V   | -                                                                                                             |

| V <sub>OLOWOB</sub>  | Low output voltage swing<br>(Load = 32 ohms to V <sub>DD</sub> /2)<br>Power = low<br>Power = high  |                                                            | -          | 0.5 × V <sub>DD</sub> – 1.3<br>0.5 × V <sub>DD</sub> – 1.3 | V<br>V   | -                                                                                                             |

| I <sub>SOB</sub>     | Supply current including bias cell (no load)<br>Power = low<br>Power = high                        |                                                            | 1.1<br>2.6 | 5.1<br>8.8                                                 | mA<br>mA | -                                                                                                             |

| PSRR <sub>OB</sub>   | Supply voltage rejection ratio                                                                     | 53                                                         | 64         | -                                                          | dB       | $(0.5 \times V_{DD} - 1.3) \le V_{OUT} \le (V_{DD} - 2.3).$                                                   |

## Table 11. 3.3 V DC Analog Output Buffer Specifications

| Parameter            | Description                                                                                             | Min                                                        | Тур        | Max                                                        | Unit     | Notes                                                                                                         |

|----------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------|------------------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------|

| CL                   | Load Capacitance                                                                                        | -                                                          | -          | 200                                                        | pF       | This specification applies to the<br>external circuit that is being<br>driven by the analog output<br>buffer. |

| V <sub>OSOB</sub>    | Input offset voltage (absolute value)                                                                   | -                                                          | 3          | 12                                                         | mV       | -                                                                                                             |

| TCV <sub>OSOB</sub>  | Average input offset voltage drift                                                                      | -                                                          | +6         | -                                                          | μV/°C    | -                                                                                                             |

| V <sub>CMOB</sub>    | Common mode input voltage range                                                                         | 0.5                                                        | -          | V <sub>DD</sub> – 1.0                                      | V        | -                                                                                                             |

| R <sub>OUTOB</sub>   | Output resistance<br>Power = low<br>Power = high                                                        |                                                            | 1<br>1     |                                                            | W<br>W   | -                                                                                                             |

| V <sub>OHIGHOB</sub> | High output voltage swing<br>(Load = 1 K $\Omega$ to V <sub>DD</sub> /2)<br>Power = low<br>Power = high | 0.5 × V <sub>DD</sub> + 1.0<br>0.5 × V <sub>DD</sub> + 1.0 |            |                                                            | V<br>V   | -                                                                                                             |

| V <sub>OLOWOB</sub>  | Low output voltage swing<br>(Load = 1 K $\Omega$ to V <sub>DD</sub> /2)<br>Power = low<br>Power = high  |                                                            |            | 0.5 × V <sub>DD</sub> – 1.0<br>0.5 × V <sub>DD</sub> – 1.0 | V<br>V   | -                                                                                                             |

| I <sub>SOB</sub>     | Supply current including bias cell (no<br>load)<br>Power = low<br>Power = high                          | _                                                          | 0.8<br>2.0 | 2.0<br>4.3                                                 | mA<br>mA | -                                                                                                             |

| PSRR <sub>OB</sub>   | Supply voltage rejection ratio                                                                          | 34                                                         | 64         | -                                                          | dB       | $(0.5 \times V_{DD} - 1.0) \le V_{OUT} \le (0.5 \times V_{DD} + 0.9).$                                        |

### DC Analog Reference Specifications

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40 \text{ }^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq 85 \text{ }^{\circ}\text{C}$ , or 3.15 V to 3.5 V and  $-40 \text{ }^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq 85 \text{ }^{\circ}\text{C}$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

The guaranteed specifications are measured through the analog continuous time PSoC blocks. The power levels for AGND refer to the power of the Analog Continuous Time PSoC block. The power levels for RefHi and RefLo refer to the Analog Reference Control register. The limits stated for AGND include the offset error of the AGND buffer local to the Analog Continuous Time PSoC block. Reference control power is high.

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings            | Symbol             | Reference | Description                                                | Min                        | Тур                        | Мах                        | Units |

|------------------------------|----------------------------------------|--------------------|-----------|------------------------------------------------------------|----------------------------|----------------------------|----------------------------|-------|

| 0b000                        | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap                               | V <sub>DD</sub> /2 + 1.229 | V <sub>DD</sub> /2 + 1.290 | V <sub>DD</sub> /2 + 1.346 | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | V <sub>DD</sub> /2 – 0.038 | V <sub>DD</sub> /2         | V <sub>DD</sub> /2 + 0.040 | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap                               | V <sub>DD</sub> /2 – 1.356 | V <sub>DD</sub> /2 – 1.295 | V <sub>DD</sub> /2 – 1.218 | V     |

|                              | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap                               | V <sub>DD</sub> /2 + 1.220 | V <sub>DD</sub> /2 + 1.292 | V <sub>DD</sub> /2 + 1.348 | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | V <sub>DD</sub> /2 – 0.036 | V <sub>DD</sub> /2         | $V_{DD}/2 + 0.036$         | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap                               | V <sub>DD</sub> /2 – 1.357 | V <sub>DD</sub> /2 – 1.297 | V <sub>DD</sub> /2 – 1.225 | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap                               | V <sub>DD</sub> /2 + 1.221 | V <sub>DD</sub> /2 + 1.293 | V <sub>DD</sub> /2 + 1.351 | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | V <sub>DD</sub> /2 – 0.036 | V <sub>DD</sub> /2         | $V_{DD}/2 + 0.036$         | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap                               | V <sub>DD</sub> /2 – 1.357 | V <sub>DD</sub> /2 – 1.298 | V <sub>DD</sub> /2 – 1.228 | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap                               | V <sub>DD</sub> /2 + 1.219 | V <sub>DD</sub> /2 + 1.293 | V <sub>DD</sub> /2 + 1.353 | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | V <sub>DD</sub> /2 – 0.037 | V <sub>DD</sub> /2 - 0.001 | $V_{DD}/2 + 0.036$         | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap                               | V <sub>DD</sub> /2 – 1.359 | V <sub>DD</sub> /2 – 1.299 | V <sub>DD</sub> /2 – 1.229 | V     |

| 0b001                        | RefPower = high<br>Opamp bias = high   | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 1.3 V) | P2[4] + P2[6] -<br>0.092   | P2[4]+P2[6]-<br>0.011      | P2[4]+P2[6]+<br>0.064      | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                                      | P2[4]                      | P2[4]                      | P2[4]                      | -     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 1.3 V) | P2[4] – P2[6] –<br>0.031   | P2[4]-P2[6]+<br>0.007      | P2[4]-P2[6]+<br>0.056      | V     |

|                              | RefPower = high<br>Opamp bias = low    | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 1.3 V) | P2[4] + P2[6] -<br>0.078   | P2[4]+P2[6]-<br>0.008      | P2[4]+P2[6]+<br>0.063      | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                                      | P2[4]                      | P2[4]                      | P2[4]                      | -     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 1.3 V) | P2[4] – P2[6] –<br>0.031   | P2[4]-P2[6]+<br>0.004      | P2[4]-P2[6]+<br>0.043      | V     |

|                              | RefPower = medium<br>Opamp bias = high | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 1.3 V) | P2[4] + P2[6] -<br>0.073   | P2[4]+P2[6]-<br>0.006      | P2[4]+P2[6]+<br>0.062      | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                                      | P2[4]                      | P2[4]                      | P2[4]                      | -     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 1.3 V) | P2[4] – P2[6] –<br>0.032   | P2[4]-P2[6]+<br>0.003      | P2[4]-P2[6]+<br>0.038      | V     |

|                              | RefPower = medium<br>Opamp bias = low  | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 1.3 V) | P2[4] + P2[6] -<br>0.073   | P2[4]+P2[6]-<br>0.006      | P2[4]+P2[6]+<br>0.062      | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                                      | P2[4]                      | P2[4]                      | P2[4]                      | -     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 1.3 V) | P2[4] – P2[6] –<br>0.034   | P2[4]-P2[6]+<br>0.002      | P2[4]-P2[6]+<br>0.037      | V     |

Table 12. 5-V DC Analog Reference Specifications

## Table 12. 5-V DC Analog Reference Specifications (continued)

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings            | Symbol             | Reference | Description                                     | Min             | Тур                     | Max                     | Units |

|------------------------------|----------------------------------------|--------------------|-----------|-------------------------------------------------|-----------------|-------------------------|-------------------------|-------|

| 0b101                        | RefPower = high<br>Opamp bias = high   | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.218   | P2[4] + 1.291           | P2[4] + 1.354           | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | _     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.335   | P2[4] – 1.294           | P2[4] – 1.237           | V     |

|                              | RefPower = high<br>Opamp bias = low    | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.221   | P2[4] + 1.293           | P2[4] + 1.358           | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.337   | P2[4] – 1.297           | P2[4] – 1.243           | V     |

|                              | RefPower = medium<br>Opamp bias = high | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.222   | P2[4] + 1.294           | P2[4] + 1.360           | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.338   | P2[4] – 1.298           | P2[4] – 1.245           | V     |

|                              | RefPower = medium<br>Opamp bias = low  | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.221   | P2[4] + 1.294           | P2[4] + 1.362           | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.340   | P2[4] – 1.298           | P2[4] – 1.245           | V     |

| 0b110                        | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.513           | 2.593                   | 2.672                   | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.264           | 1.302                   | 1.340                   | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.008 | V <sub>SS</sub> + 0.038 | V     |

|                              | RefPower = high<br>Opamp bias = low    | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.514           | 2.593                   | 2.674                   | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.264           | 1.301                   | 1.340                   | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.005 | V <sub>SS</sub> + 0.028 | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.514           | 2.593                   | 2.676                   | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.264           | 1.301                   | 1.340                   | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.004 | V <sub>SS</sub> + 0.024 | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.514           | 2.593                   | 2.677                   | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.264           | 1.300                   | 1.340                   | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.003 | V <sub>SS</sub> + 0.021 | V     |

| 0b111                        | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap                                   | 4.028           | 4.144                   | 4.242                   | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap                                   | 2.028           | 2.076                   | 2.125                   | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.008 | V <sub>SS</sub> + 0.034 | V     |

|                              | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap                                   | 4.032           | 4.142                   | 4.245                   | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap                                   | 2.029           | 2.076                   | 2.126                   | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.005 | V <sub>SS</sub> + 0.025 | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap                                   | 4.034           | 4.143                   | 4.247                   | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap                                   | 2.029           | 2.076                   | 2.126                   | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.004 | V <sub>SS</sub> + 0.021 | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap                                   | 4.036           | 4.144                   | 4.249                   | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap                                   | 2.029           | 2.076                   | 2.126                   | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.003 | V <sub>SS</sub> + 0.019 | V     |

## DC Programming Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40 \degree C \le T_A \le 85 \degree C$ , or 3.15 V to 3.5 V and  $-40 \degree C \le T_A \le 85 \degree C$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

### Table 16. DC Programming Specifications

| Parameter             | Description                                                                        | Min                   | Тур | Max                   | Unit  | Notes                                                                                        |

|-----------------------|------------------------------------------------------------------------------------|-----------------------|-----|-----------------------|-------|----------------------------------------------------------------------------------------------|

| V <sub>DDP</sub>      | $V_{DD}$ for programming and erase                                                 | 4.5                   | 5.0 | 5.5                   | V     | This specification applies to the<br>functional requirements of external<br>programmer tools |

| V <sub>DDLV</sub>     | Low V <sub>DD</sub> for verify                                                     | 3.0                   | 3.1 | 3.2                   | V     | This specification applies to the<br>functional requirements of external<br>programmer tools |

| V <sub>DDHV</sub>     | High $V_{DD}$ for verify                                                           | 5.1                   | 5.2 | 5.3                   | V     | This specification applies to the<br>functional requirements of external<br>programmer tools |

| V <sub>DDIWRITE</sub> | Supply voltage for flash write operation                                           | 3.15                  | _   | 5.25                  | V     | This specification applies to this device when it is executing internal flash writes         |

| I <sub>DDP</sub>      | Supply current during programming or verify                                        | -                     | 15  | 30                    | mA    | -                                                                                            |

| V <sub>ILP</sub>      | Input low voltage during programming or verify                                     | -                     | -   | 0.8                   | V     | -                                                                                            |

| V <sub>IHP</sub>      | Input high voltage during programming or Verify                                    | 2.1                   | -   | -                     | V     | _                                                                                            |

| I <sub>ILP</sub>      | Input current when applying Vilp to P1[0] or<br>P1[1] during programming or verify | -                     | -   | 0.2                   | mA    | Driving internal pull-down resistor.                                                         |

| I <sub>IHP</sub>      | Input current when applying Vihp to P1[0] or P1[1] during programming or verify    | -                     | _   | 1.5                   | mA    | Driving internal pull-down resistor.                                                         |

| V <sub>OLV</sub>      | Output low voltage during programming or verify                                    | -                     | _   | V <sub>SS</sub> +0.75 | V     | -                                                                                            |

| V <sub>OHV</sub>      | Output high voltage during programming or verify                                   | V <sub>DD</sub> – 1.0 | _   | V <sub>DD</sub>       | V     | -                                                                                            |

| Flash <sub>ENPB</sub> | Flash endurance (per block)                                                        | 50,000 <sup>[8]</sup> | _   | _                     | _     | Erase/write cycles per block.                                                                |

| Flash <sub>ENT</sub>  | Flash endurance (total) <sup>[9]</sup>                                             | 1,800,000             | -   | _                     | _     | Erase/write cycles.                                                                          |

| Flash <sub>DR</sub>   | Flash data retention                                                               | 10                    | _   | _                     | Years | -                                                                                            |

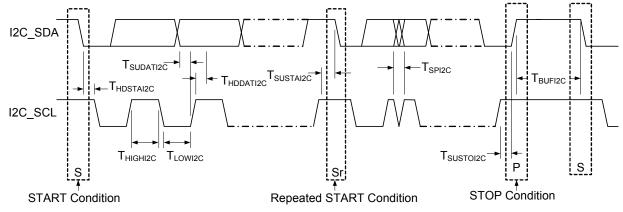

## DC I<sup>2</sup>C Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.15 V to 3.5 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

### Table 17. DC I<sup>2</sup>C Specifications <sup>[10]</sup>

| Symbol             | Description      | Min                 | Тур | Max                  | Units | Notes                            |

|--------------------|------------------|---------------------|-----|----------------------|-------|----------------------------------|

| V <sub>ILI2C</sub> | Input low level  | -                   | -   | $0.3 \times V_{DD}$  | V     | $3.15~V \leq V_{DD} \leq 3.6~V$  |

|                    |                  | -                   | -   | $0.25 \times V_{DD}$ | V     | $4.75~V \leq V_{DD} \leq 5.25~V$ |

| V <sub>IHI2C</sub> | Input high level | $0.7 \times V_{DD}$ | -   | -                    | V     | $3.15~V \leq V_{DD} \leq 5.25~V$ |

#### Notes

- 8. The 50,000 cycle Flash endurance per block will only be guaranteed if the Flash is operating within one voltage range. Voltage ranges are 3.0V to 3.6V and 4.75V to 5.25V.

- 9. A maximum of 36 x 50,000 block endurance cycles is allowed. This may be balanced between operations on 36x1 blocks of 50,000 maximum cycles each, 36x2 blocks of 25,000 maximum cycles each, or 36x4 blocks of 12,500 maximum cycles each (to limit the total number of cycles to 36x50,000 and that no single block ever sees more than 50,000 cycles).

ever sees more than 50,000 cycles). For the full industrial range, the user must employ a temperature sensor user module (FlashTemp) and feed the result to the temperature argument before writing. Refer to the Flash APIs application note AN2015 for more information.

10. All GPIOs meet the DC GPIO  $V_{IL}$  and  $V_{IH}$  specifications found in the DC GPIO Specifications sections. The I<sup>2</sup>C GPIO pins also meet the mentioned specifications.

## **AC Electrical Characteristics**

## AC Chip-Level Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.15 V to 3.5 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

### Table 18. AC Chip-Level Specifications

| Parameter                            | Description                                                                 | Min   | Тур  | Max                         | Unit | Notes                                                                                                                                                                                |

|--------------------------------------|-----------------------------------------------------------------------------|-------|------|-----------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F <sub>IMO245V</sub>                 | IMO frequency for 24 MHz (5 V)                                              | 23.04 | 24   | 24.96 <sup>[11, 12]</sup>   | MHz  | Trimmed for 5 V operation using factory trim values.                                                                                                                                 |

| F <sub>IMO243V</sub>                 | IMO frequency for 24 MHz (3.3 V)                                            | 22.08 | 24   | 25.92 <sup>[11,13]</sup>    | MHz  | Trimmed for 3.3 V operation using factory trim values.                                                                                                                               |

| F <sub>IMOUSB</sub>                  | IMO frequency with USB frequency locking<br>enabled and USB traffic present | 23.94 | 24   | 24.06 <sup>[12]</sup>       | MHz  | USB operation for system clock source from the IMO is limited to $0^{\circ}C \leq T_A \leq 70^{\circ}C$ .                                                                            |

| F <sub>CPU1</sub>                    | CPU frequency (5 V nominal)                                                 | 0.090 | 24   | 24.96 <sup>[11,12]</sup>    | MHz  | SLIMO mode = 0.                                                                                                                                                                      |

| F <sub>CPU2</sub>                    | CPU frequency (3.3 V nominal)                                               | 0.086 | 12   | 12.96 <sup>[12,13]</sup>    | MHz  | SLIMO mode = 0.                                                                                                                                                                      |

| F <sub>BLK5</sub>                    | Digital PSoC block frequency<br>(5 V nominal)                               | 0     | 48   | 49.92 <sup>[11,12,14]</sup> | MHz  | Refer to the AC Digital Block Specifica-<br>tions on page 26.                                                                                                                        |

| F <sub>BLK3</sub>                    | Digital PSoC block frequency (3.3 V nominal)                                | 0     | 24   | 25.92 <sup>[12,14]</sup>    | MHz  | _                                                                                                                                                                                    |

| F <sub>32K1</sub>                    | ILO frequency                                                               | 15    | 32   | 64                          | kHz  | _                                                                                                                                                                                    |

| F <sub>32K_U</sub>                   | ILO untrimmed frequency                                                     | 5     | _    | 100                         | kHz  | After a reset and before the M8C<br>starts to run, the ILO is not trimmed.<br>See the System Resets section of<br>the PSoC Technical Reference<br>Manual for details on this timing. |

| DC <sub>ILO</sub>                    | ILO duty cycle                                                              | 20    | 50   | 80                          | %    | _                                                                                                                                                                                    |

| DC <sub>24M</sub>                    | 24-MHz duty cycle                                                           | 40    | 50   | 60                          | %    |                                                                                                                                                                                      |

| Step24M                              | 24-MH trim step size                                                        | _     | 50   | _                           | kHz  | _                                                                                                                                                                                    |

| Fout48M                              | 48-MHz output frequency                                                     | 46.08 | 48.0 | 49.92 <sup>[11,13]</sup>    | MHz  | Trimmed. Utilizing factory trim values.                                                                                                                                              |

| F <sub>MAX</sub>                     | Maximum frequency of signal on row input or row output                      | -     | -    | 12.96                       | MHz  | _                                                                                                                                                                                    |

| SR <sub>POWER_UP</sub>               | Power supply slew rate                                                      | -     | _    | 250                         | V/ms | _                                                                                                                                                                                    |

| T <sub>POWERUP</sub>                 | Time from end of POR to CPU executing code                                  | -     | 16   | 100                         | ms   | _                                                                                                                                                                                    |

| T <sub>jit_IMO</sub> <sup>[15]</sup> | 24 MHz IMO cycle-to-cycle jitter (RMS)                                      | -     | 200  | 1200                        | ps   |                                                                                                                                                                                      |

|                                      | 24 MHz IMO long term N cycle-to-cycle jitter (RMS)                          | _     | 900  | 6000                        | ps   | N = 32.                                                                                                                                                                              |

|                                      | 24 MHz IMO period jitter (RMS)                                              | -     | 200  | 900                         | ps   |                                                                                                                                                                                      |

#### Notes

11. 4.75 V < V<sub>DD</sub> < 5.25 V.</li>

12. Accuracy derived from Internal Main Oscillator with appropriate trim for V<sub>DD</sub> range.

13. 3.0 V < V<sub>DD</sub> < 3.6 V. See application note AN2012 "Adjusting PSoC Microcontroller Trims for Dual Voltage-Range Operation" for information on trimming for operation at 3.3 V.</li>

14. See the individual user module data sheets for information on maximum frequencies for user modules.

15. Refer to Cypress Jitter Specifications application note, Understanding Datasheet Jitter Specifications for Cypress Timing Products – AN5054 for more information.

## AC External Clock Specifications

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.15 V to 3.5 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

### Table 22. AC External Clock Specifications

| Parameter           | Description                    | Min   | Тур | Max   | Unit | Notes                                                                                                                                                                               |

|---------------------|--------------------------------|-------|-----|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F <sub>OSCEXT</sub> | Frequency for USB applications | 23.94 | 24  | 24.06 |      | USB operation in the extended Industrial temperature range (–40 °C $\leq$ T <sub>A</sub> $\leq$ 85 °C) requires that the system clock is sourced from an external clock oscillator. |

| -                   | Duty cycle                     | 47    | 50  | 53    | %    | -                                                                                                                                                                                   |

| _                   | Power-up to IMO switch         | 150   | -   | -     | μS   | -                                                                                                                                                                                   |

### AC Analog Output Buffer Specifications

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40 \degree C \le T_A \le 85 \degree C$ , or 3.15 V to 3.5 V and  $-40 \degree C \le T_A \le 85 \degree C$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

### Table 23. 5 V AC Analog Output Buffer Specifications

| Parameter          | Description                                                                                       | Min          | Тур | Max        | Unit         | Notes |

|--------------------|---------------------------------------------------------------------------------------------------|--------------|-----|------------|--------------|-------|

| T <sub>ROB</sub>   | Rising settling time to 0.1%, 1 V Step, 100-pF load<br>Power = low<br>Power = high                |              |     | 2.5<br>2.5 | μS<br>μS     | -     |

| T <sub>SOB</sub>   | Falling settling time to 0.1%, 1 V Step, 100-pF load<br>Power = low<br>Power = high               |              |     | 2.2<br>2.2 | μs<br>μs     | -     |

| SR <sub>ROB</sub>  | Rising slew rate (20% to 80%), 1 V Step, 100-pF load<br>Power = low<br>Power = high               | 0.65<br>0.65 |     |            | V/μs<br>V/μs | -     |

| SR <sub>FOB</sub>  | Falling slew rate (80% to 20%), 1 V Step, 100-pF load<br>Power = low<br>Power = high              | 0.65<br>0.65 |     |            | V/μs<br>V/μs | -     |

| BW <sub>OBSS</sub> | Small signal bandwidth, 20 mV <sub>pp</sub> , 3-dB BW, 100-pF load<br>Power = low<br>Power = high | 0.8<br>0.8   |     |            | MHz<br>MHz   | -     |

| BW <sub>OBLS</sub> | Large signal bandwidth, 1 V <sub>pp</sub> , 3-dB BW, 100-pF load<br>Power = low<br>Power = high   | 300<br>300   |     | _<br>_     | kHz<br>kHz   | -     |

Table 24. 3.3 V AC Analog Output Buffer Specifications