# E·XFL

# Zilog - Z8F1601AN020EC00TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | I²C, IrDA, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                    |

| Number of I/O              | 31                                                            |

| Program Memory Size        | 16KB (16K x 8)                                                |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 2K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                     |

| Data Converters            | A/D 8x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 44-LQFP                                                       |

| Supplier Device Package    | 44-LQFP (10x10)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1601an020ec00tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| External Pin Reset 29                                  | ) |

|--------------------------------------------------------|---|

| Stop Mode Recovery                                     |   |

| Stop Mode Recovery Using Watch-Dog Timer Time-Out 29   | ) |

| Stop Mode Recovery Using a GPIO Port Pin Transition 30 | ) |

| Low-Power Modes                                        | L |

| Overview                                               | l |

| Stop Mode                                              | l |

| Halt Mode                                              | L |

| General-Purpose I/O 33                                 | 3 |

| Overview                                               | 3 |

| GPIO Port Availability By Device                       | 3 |

| Architecture                                           | 1 |

| GPIO Alternate Functions 34                            | ł |

| GPIO Interrupts                                        | 5 |

| GPIO Control Register Definitions                      | 5 |

| Port A-H Address Registers                             |   |

| Port A-H Control Registers                             |   |

| Port A-H Input Data Registers                          | 2 |

| Port A-H Output Data Register 43                       | 3 |

| Interrupt Controller                                   | l |

| Overview                                               | 1 |

| Interrupt Vector Listing                               | ł |

| Architecture                                           |   |

| Operation                                              |   |

| Master Interrupt Enable 46                             | 5 |

| Interrupt Vectors and Priority 47                      |   |

| Interrupt Assertion Types 47                           |   |

| Interrupt Control Register Definitions                 |   |

| Interrupt Request 0 Register                           |   |

| Interrupt Request 1 Register 49                        |   |

| Interrupt Request 2 Register 50                        |   |

| IRQ0 Enable High and Low Bit Registers                 |   |

| IRQ1 Enable High and Low Bit Registers                 |   |

| IRQ2 Enable High and Low Bit Registers                 |   |

| Interrupt Edge Select Register54                       |   |

| Interrupt Port Select Register 55                      |   |

| Interrupt Control Register 56                          |   |

| Timers                                                 |   |

| Overview                                               |   |

| Architecture                                           |   |

| Operation                                              | 3 |

## **Use of All Uppercase Letters**

The use of all uppercase letters designates the names of states and commands.

- Example 1: The bus is considered BUSY after the Start condition.

- Example 2: A START command triggers the processing of the initialization sequence.

## **Bit Numbering**

Bits are numbered from 0 to n-1 where n indicates the total number of bits. For example, the 8 bits of a register are numbered from 0 to 7.

## Safeguards

It is important that all users understand the following safety terms, which are defined here.

Indicates a procedure or file may become corrupted if the user does not follow directions.

## Trademarks

ZiLOG, eZ8, Z8 Encore!, and Z8 are trademarks of <u>ZiLOG, Inc.</u> in the U.S.A. and other countries. All other trademarks are the property of their respective corporations.

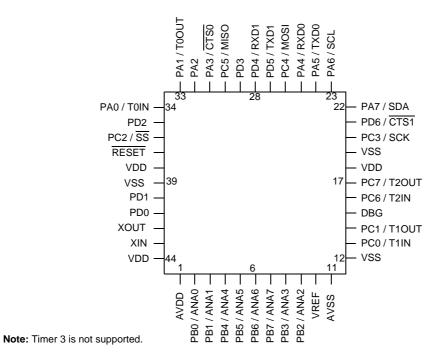

Figure 58. Z8Fxx01 in 44-Pin Low-Profile Quad Flat Package (LQFP)

# **Signal Descriptions**

Table 2 describes the Z8F640x family signals. Refer to the section **Pin Configurations on page 7** to determine the signals available for the specific package styles.

| Signal Mnemonic               | I/O | Description                                                                                                                                                                                                                                                                           |  |  |  |  |

|-------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| General-Purpose I/O Ports A-H |     |                                                                                                                                                                                                                                                                                       |  |  |  |  |

| PA[7:0]                       | I/O | Port A[7:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                             |  |  |  |  |

| PB[7:0]                       | I/O | Port B[7:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                             |  |  |  |  |

| PC[7:0]                       | I/O | Port C[7:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                             |  |  |  |  |

| PD[7:0]                       | I/O | Port D[7:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                             |  |  |  |  |

| PE[7:0]                       | I/O | Port E[7:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                             |  |  |  |  |

| PF[7:0]                       | I/O | Port F[7:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                             |  |  |  |  |

| PG[7:0]                       | I/O | Port G[7:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                             |  |  |  |  |

| PH[3:0]                       | I/O | Port H[3:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                             |  |  |  |  |

| I <sup>2</sup> C Controller   |     |                                                                                                                                                                                                                                                                                       |  |  |  |  |

| SCL                           | 0   | Serial Clock. This is the output clock for the I <sup>2</sup> C. This pin is multiplexed with a general-purpose I/O pin. When the general-purpose I/O pin is configured for alternate function to enable the SCL function, this pin is open-drain.                                    |  |  |  |  |

| SDA                           | I/O | Serial Data. This open-drain pin is used to transfer data between the I <sup>2</sup> C and a slave. This pin is multiplexed with a general-purpose I/O pin. When the general-purpose I/O pin is configured for alternate function to enable the SDA function, this pin is open-drain. |  |  |  |  |

| SPI Controller                |     |                                                                                                                                                                                                                                                                                       |  |  |  |  |

| SS                            | I/O | Slave Select. This signal can be an output or an input. If the Z8 Encore! is the SPI master, this pin may be configured as the Slave Select output. If the Z8 Encore! is the SPI slave, this pin is the input slave select. It is multiplexed with a general-purpose I/O pin.         |  |  |  |  |

| SCK                           | I/O | SPI Serial Clock. The SPI master supplies this pin. If the Z8 Encore! is the SPI master, this pin is an output. If the Z8 Encore! is the SPI slave, this pin is an input. It is multiplexed with a general-purpose I/O pin.                                                           |  |  |  |  |

| MOSI                          | I/O | Master Out Slave In. This signal is the data output from the SPI master device and the data input to the SPI slave device. It is multiplexed with a general-purpose I/O pin.                                                                                                          |  |  |  |  |

| MISO                          | I/O | Master In Slave Out. This pin is the data input to the SPI master device and the data output from the SPI slave device. It is multiplexed with a general-purpose I/O pin.                                                                                                             |  |  |  |  |

Table 2. Signal Descriptions

| Address (Hex)    | Register Description                  | Mnemonic | Reset (Hex) | Page # |

|------------------|---------------------------------------|----------|-------------|--------|

| Timer 3 (not av  | ailable in 40- and 44- Pin Packages)  |          |             |        |

| F18              | Timer 3 High Byte                     | ТЗН      | 00          | 66     |

| F19              | Timer 3 Low Byte                      | T3L      | 01          | 66     |

| F1A              | Timer 3 Reload High Byte              | T3RH     | FF          | 67     |

| F1B              | Timer 3 Reload Low Byte               | T3RL     | FF          | 67     |

| F1C              | Timer 3 PWM High Byte                 | T3PWMH   | 00          | 69     |

| F1D              | Timer 3 PWM Low Byte                  | T3PWML   | 00          | 69     |

| F1E              | Reserved                              | _        | XX          |        |

| F1F              | Timer 3 Control                       | T3CTL    | 00          | 70     |

| F20-F3F          | Reserved                              | _        | XX          |        |

| UART 0           |                                       |          |             |        |

| F40              | UART0 Transmit Data                   | U0TXD    | XX          | 86     |

|                  | UART0 Receive Data                    | U0RXD    | XX          | 87     |

| F41              | UART0 Status 0                        | U0STAT0  | 0000011Xb   | 87     |

| F42              | UART0 Control 0                       | U0CTL0   | 00          | 89     |

| F43              | UART0 Control 1                       | U0CTL1   | 00          | 89     |

| F44              | UART0 Status 1                        | U0STAT1  | 00          | 87     |

| F45              | Reserved                              | _        | XX          |        |

| F46              | UART0 Baud Rate High Byte             | U0BRH    | FF          | 91     |

| F47              | UARTO Baud Rate Low Byte              | U0BRL    | FF          | 91     |

| UART 1           | · · · · · · · · · · · · · · · · · · · |          |             |        |

| F48              | UART1 Transmit Data                   | UITXD    | XX          | 86     |

|                  | UART1 Receive Data                    | U1RXD    | XX          | 87     |

| F49              | UART1 Status 0                        | U1STAT0  | 0000011Xb   | 87     |

| F4A              | UART1 Control 0                       | U1CTL0   | 00          | 89     |

| F4B              | UART1 Control 1                       | U1CTL1   | 00          | 89     |

| F4C              | UART1 Status 1                        | U1STAT1  | 00          | 87     |

| F4D              | Reserved                              | _        | XX          |        |

| F4E              | UART1 Baud Rate High Byte             | U1BRH    | FF          | 91     |

| F4F              | UART1 Baud Rate Low Byte              | U1BRL    | FF          | 91     |

| I <sup>2</sup> C |                                       |          |             |        |

| F50              | I <sup>2</sup> C Data                 | I2CDATA  | 00          | 118    |

| F51              | I <sup>2</sup> C Status               | I2CSTAT  | 80          | 118    |

| F52              | I <sup>2</sup> C Control              | I2CCTL   | 00          | 119    |

| F53              | I <sup>2</sup> C Baud Rate High Byte  | I2CBRH   | FF          | 121    |

| F54              | I <sup>2</sup> C Baud Rate Low Byte   | I2CBRL   | FF          | 121    |

| F55-F5F          | Reserved                              | _        | XX          |        |

|                  | al Interface (SPI)                    |          |             |        |

| F60              | SPI Data                              | SPIDATA  | XX          | 106    |

|                  |                                       |          |             |        |

Table 6. Register File Address Map (Continued)

## System and Short Resets

During a System Reset, the Z8F640x family device is held in Reset for 514 cycles of the Watch-Dog Timer oscillator followed by 16 cycles of the system clock (crystal oscillator). A Short Reset differs from a System Reset only in the number of Watch-Dog Timer oscillator cycles required to exit Reset. A Short Reset requires only 66 Watch-Dog Timer oscillator cycles. Unless specifically stated otherwise, System Reset and Short Reset are referred to collectively as Reset.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watch-Dog Timer oscillator continue to run. The system clock begins operating following the Watch-Dog Timer oscillator cycle count. The eZ8 CPU and on-chip peripherals remain idle through the 16 cycles of the system clock.

Upon Reset, control registers within the Register File that have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer, and Flags) and general-purpose RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

## **Reset Sources**

Table 8 lists the reset sources and type of Reset as a function of the Z8F640x family device operating mode. The text following provides more detailed information on the individual Reset sources. Please note that Power-On Reset / Voltage Brown-Out events always have priority over all other possible reset sources to insure a full system reset occurs.

| <b>Operating Mode</b> | Reset Source                                             | Reset Type                                                          |

|-----------------------|----------------------------------------------------------|---------------------------------------------------------------------|

| Normal or Halt modes  | Power-On Reset / Voltage Brown-Out                       | System Reset                                                        |

|                       | Watch-Dog Timer time-out<br>when configured for Reset    | Short Reset                                                         |

|                       | RESET pin assertion                                      | Short Reset                                                         |

|                       | On-Chip Debugger initiated Reset<br>(OCDCTL[1] set to 1) | System Reset except the On-Chip Debugger is unaffected by the reset |

| Stop mode             | Power-On Reset / Voltage Brown-Out                       | System Reset                                                        |

|                       | RESET pin assertion                                      | System Reset                                                        |

|                       | DBG pin driven Low                                       | System Reset                                                        |

Table 8. Reset Sources and Resulting Reset Type

## Architecture

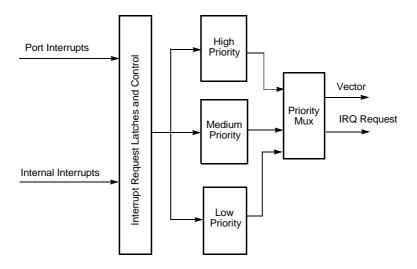

Figure 65 illustrates a block diagram of the interrupt controller.

Figure 65. Interrupt Controller Block Diagram

# Operation

## **Master Interrupt Enable**

The master interrupt enable bit (IRQE) in the Interrupt Control register globally enables and disables interrupts.

Interrupts are globally enabled by any of the following actions:

- Execution of an EI (Enable Interrupt) instruction

- Execution of an IRET (Return from Interrupt) instruction

- Writing a 1 to the IRQE bit in the Interrupt Control register

Interrupts are globally disabled by any of the following actions:

- Execution of a DI (Disable Interrupt) instruction

- eZ8 CPU acknowledgement of an interrupt service request from the interrupt controller

- Writing a 0 to the IRQE bit in the Interrupt Control register

- Reset

## **IRQ0 Enable High and Low Bit Registers**

The IRQ0 Enable High and Low Bit registers (Tables 27 and 28) form a priority encoded enabling for interrupts in the Interrupt Request 0 register. Priority is generated by setting bits in each register. Table 26 describes the priority control for IRQ0.

| IRQ0ENH[x] | IRQ0ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

| 1          | 1          | Level 3  | High        |

Table 26. IRQ0 Enable and Priority Encoding

where *x* indicates the register bits from 0 through 7.

Table 27. IRQ0 Enable High Bit Register (IRQ0ENH)

| BITS  | 7     | 6     | 5            | 4             | 3      | 2      | 1      | 0      |

|-------|-------|-------|--------------|---------------|--------|--------|--------|--------|

| FIELD | T2ENH | T1ENH | <b>T0ENH</b> | <b>UORENH</b> | U0TENH | I2CENH | SPIENH | ADCENH |

| RESET | 0     | 0     | 0            | 0             | 0      | 0      | 0      | 0      |

| R/W   | R/W   | R/W   | R/W          | R/W           | R/W    | R/W    | R/W    | R/W    |

| ADDR  | FC1H  |       |              |               |        |        |        |        |

T2ENH—Timer 2 Interrupt Request Enable High Bit T1ENH—Timer 1 Interrupt Request Enable High Bit T0ENH—Timer 0 Interrupt Request Enable High Bit U0RENH—UART 0 Receive Interrupt Request Enable High Bit U0TENH—UART 0 Transmit Interrupt Request Enable High Bit I2CENH—I<sup>2</sup>C Interrupt Request Enable High Bit SPIENH—SPI Interrupt Request Enable High Bit ADCENH—ADC Interrupt Request Enable High Bit

#### **Capture mode**

0 = Count is captured on the rising edge of the Timer Input signal.

1 = Count is captured on the falling edge of the Timer Input signal.

#### **Compare mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### Gated mode

0 = Timer counts when the Timer Input signal is High (1) and interrupts are generated on the falling edge of the Timer Input.

1 = Timer counts when the Timer Input signal is Low (0) and interrupts are generated on the rising edge of the Timer Input.

#### Capture/Compare mode

0 = Counting is started on the first rising edge of the Timer Input signal. The current count is captured on subsequent rising edges of the Timer Input signal.

1 = Counting is started on the first falling edge of the Timer Input signal. The current count is captured on subsequent falling edges of the Timer Input signal.

#### PRES—Prescale value.

The timer input clock is divided by 2<sup>PRES</sup>, where PRES can be set from 0 to 7. The prescaler is reset each time the Timer is disabled. This insures proper clock division each time the Timer is restarted.

- 000 = Divide by 1

- 001 = Divide by 2

- 010 = Divide by 4

- 011 = Divide by 8

- 100 = Divide by 16

- 101 = Divide by 32

- 110 = Divide by 64

- 111 = Divide by 128

TMODE—Timer mode

- 000 =One-Shot mode

- 001 = Continuous mode

- 010 =Counter mode

- 011 = PWM mode

- 100 = Capture mode

- 101 = Compare mode

- 110 = Gated mode

- 111 = Capture/Compare mode

0 = No parity error has occurred.

1 = A parity error has occurred.

#### OE—Overrun Error

This bit indicates that an overrun error has occurred. An overrun occurs when new data is received and the UART Receive Data register has not been read. If the RDA bit is reset to 0, then reading the UART Receive Data register clears this bit.

0 = No overrun error occurred.

1 = An overrun error occurred.

FE—Framing Error

This bit indicates that a framing error (no Stop bit following data reception) was detected. Reading the UART Receive Data register clears this bit.

0 = No framing error occurred.

1 = A framing error occurred.

#### BRKD—Break Detect

This bit indicates that a break occurred. If the data bits, parity/multiprocessor bit, and Stop bit(s) are all zeros then this bit is set to 1. Reading the UART Receive Data register clears this bit.

0 = No break occurred.

1 = A break occurred.

#### TDRE—Transmitter Data Register Empty

This bit indicates that the UART Transmit Data register is empty and ready for additional data. Writing to the UART Transmit Data register resets this bit.

0 = Do not write to the UART Transmit Data register.

1 = The UART Transmit Data register is ready to receive an additional byte to be transmitted.

#### TXE—Transmitter Empty

This bit indicates that the transmit shift register is empty and character transmission is finished.

0 = Data is currently transmitting.

1 = Transmission is complete.

CTS—CTS signal

When this bit is read it returns the level of the  $\overline{\text{CTS}}$  signal.

mitter and receiver sections, a Baud Rate (clock) Generator and a control unit. The transmitter and receiver sections use the same clock.

During an SPI transfer, data is sent and received simultaneously by both the Master and the Slave SPI devices. Separate signals are required for data and the serial clock. When an SPI transfer occurs, a multi-bit (typically 8-bit) character is shifted out one data pin and an multi-bit character is simultaneously shifted in on a second data pin. An 8-bit shift register in the Master and another 8-bit shift register in the Slave are connected as a circular buffer. The SPI shift register is single-buffered in the transmit and receive directions. New data to be transmitted cannot be written into the shift register until the previous transmission is complete and receive data (if valid) has been read.

#### SPI Signals

The four basic SPI signals are:

- MISO (Master-In, Slave-Out)

- MOSI (Master-Out, Slave-In)

- SCK (SPI Serial Clock)

- $\overline{SS}$  (Slave Select)

The following paragraphs discuss these SPI signals. Each signal is described in both Master and Slave modes.

#### Master-In, Slave-Out

The Master-In, Slave-Out (MISO) pin is configured as an input in a Master device and as an output in a Slave device. It is one of the two lines that transfer serial data, with the most significant bit sent first. The MISO pin of a Slave device is placed in a high-impedance state if the Slave is not selected. When the SPI is not enabled, this signal is in a highimpedance state.

#### Master-Out, Slave-In

The Master-Out, Slave-In (MOSI) pin is configured as an output in a Master device and as an input in a Slave device. It is one of the two lines that transfer serial data, with the most significant bit sent first. When the SPI is not enabled, this signal is in a high-impedance state.

#### Serial Clock

The Serial Clock (SCK) is used to synchronize data movement both in and out of the device through its MOSI and MISO pins. In Master mode, the SPI's Baud Rate Generator creates the serial clock. The Master drives the serial clock out its own SCK pin to the Slave's SCK pin. When the SPI is configured as a Slave, the SCK pin is an input and the clock signal from the Master synchronizes the data transfer between the Master and Slave devices. Slave devices ignore the SCK signal, unless the  $\overline{SS}$  pin is asserted.

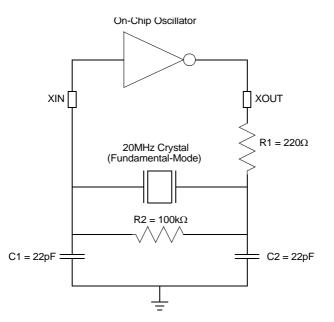

Figure 90. Recommended Crystal Oscillator Configuration (20MHz operation)

| Parameter                           | Value       | Units | Comments |

|-------------------------------------|-------------|-------|----------|

| Frequency                           | 20          | MHz   |          |

| Resonance                           | Parallel    |       |          |

| Mode                                | Fundamental |       |          |

| Series Resistance (R <sub>S</sub> ) | 25          | Ω     | Maximum  |

| Load Capacitance (CL)               | 20          | pF    | Maximum  |

| Shunt Capacitance (C <sub>0</sub> ) | 7           | pF    | Maximum  |

| Drive Level                         | 1           | mW    | Maximum  |

Table 99. Recommended Crystal Oscillator Specifications (20MHz Operation)

|                  |                                | V <sub>I</sub><br>T <sub>A</sub> = | $D_D = 3.0 - 3.0 - 3.0 - 40^{\circ}$ C to 1 | .6V<br>05 <sup>0</sup> C |        |                                                                                                                               |

|------------------|--------------------------------|------------------------------------|---------------------------------------------|--------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------|

| Symbol           | Parameter                      | Minimum                            | Typical                                     | Maximum                  | Units  | Conditions                                                                                                                    |

|                  | DC Offset Error                | -50                                | _                                           | 25                       | mV     | 40-pin PDIP, 44-pin LQFP,<br>44-pin PLCC, and 68-pin<br>PLCC packages.                                                        |

| V <sub>REF</sub> | Internal Reference Voltage     | -                                  | 2.0                                         | _                        | V      |                                                                                                                               |

|                  | Single-Shot Conversion<br>Time | _                                  | 5129                                        | -                        | cycles | System clock cycles                                                                                                           |

|                  | Continuous Conversion Time     | _                                  | 256                                         | _                        | cycles | System clock cycles                                                                                                           |

|                  | Sampling Rate                  | System Clock / 256                 |                                             | Hz                       |        |                                                                                                                               |

|                  | Signal Input Bandwidth         | -                                  | -                                           | 3.5                      | kHz    |                                                                                                                               |

| R <sub>S</sub>   | Analog Source Impedance        | -                                  | -                                           | 10 <sup>1</sup>          | kΩ     |                                                                                                                               |

| Zin              | Input Impedance                |                                    | 150                                         |                          | kΩ     | 20MHz system clock. Input<br>impedance increases with<br>lower system clock<br>frequency.                                     |

| V <sub>REF</sub> | External Reference Voltage     |                                    |                                             | AVDD                     | V      | AVDD <= VDD. When using<br>an external reference voltage,<br>decoupling capacitance<br>should be placed from VREF<br>to AVSS. |

#### Table 106. Analog-to-Digital Converter Electrical Characteristics and Timing (Continued)

<sup>1</sup> Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

# General Purpose I/O Port Output Timing

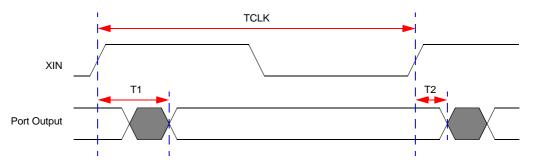

Figure 94 and Table 108 provide timing information for GPIO Port pins.

Figure 94. GPIO Port Output Timing

Table 108. GPIO Port Output Timing

|                |                                     | Delay (ns) |         |

|----------------|-------------------------------------|------------|---------|

| Parameter      | Abbreviation                        | Minimum    | Maximum |

| T <sub>1</sub> | XIN Rise to Port Output Valid Delay | _          | 15      |

| T <sub>2</sub> | XIN Rise to Port Output Hold Time   | 2          | -       |

## **SPI Master Mode Timing**

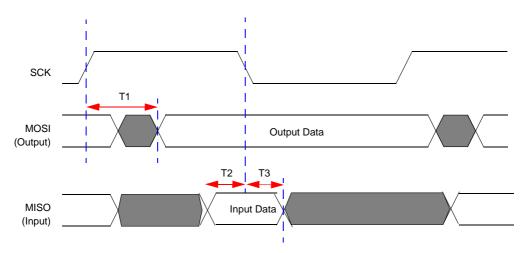

Figure 96 and Table 110 provide timing information for SPI Master mode pins. Timing is shown with SCK rising edge used to source MOSI output data, SCK falling edge used to sample MISO input data. Timing on the SS output pin(s) is controlled by software.

Figure 96. SPI Master Mode Timing

| Table | 110. | SPI | Master | Mode | Timing |

|-------|------|-----|--------|------|--------|

|-------|------|-----|--------|------|--------|

|                |                                             | Dela    | y (ns)  |

|----------------|---------------------------------------------|---------|---------|

| Parameter      | Abbreviation                                | Minimum | Maximum |

| T <sub>1</sub> | SCK Rise to MOSI output Valid Delay         | -5      | +5      |

| T <sub>2</sub> | MISO input to SCK (receive edge) Setup Time | 20      |         |

| T <sub>3</sub> | MISO input to SCK (receive edge) Hold Time  | 0       |         |

| Notation | Description                    | Operand | Range                                                                                                                     |  |  |  |  |  |  |  |

|----------|--------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| b        | Bit                            | b       | b represents a value from 0 to 7 (000B to 111B).                                                                          |  |  |  |  |  |  |  |

| сс       | Condition Code                 | _       | See Condition Codes overview in the eZ8 CPU Use Manual.                                                                   |  |  |  |  |  |  |  |

| DA       | Direct Address                 | Addrs   | Addrs. represents a number in the range of 0000H to FFFFH                                                                 |  |  |  |  |  |  |  |

| ER       | Extended Addressing Register   | Reg     | Reg. represents a number in the range of 000H to FFFH                                                                     |  |  |  |  |  |  |  |

| IM       | Immediate Data                 | #Data   | Data is a number between 00H to FFH                                                                                       |  |  |  |  |  |  |  |

| Ir       | Indirect Working Register      | @Rn     | n = 0 - 15                                                                                                                |  |  |  |  |  |  |  |

| IR       | Indirect Register              | @Reg    | Reg. represents a number in the range of 00H to FFH                                                                       |  |  |  |  |  |  |  |

| Irr      | Indirect Working Register Pair | @RRp    | p = 0, 2, 4, 6, 8, 10, 12, or 14                                                                                          |  |  |  |  |  |  |  |

| IRR      | Indirect Register Pair         | @Reg    | Reg. represents an even number in the range 00H to FEH                                                                    |  |  |  |  |  |  |  |

| р        | Polarity                       | р       | Polarity is a single bit binary value of either 0B or 1B.                                                                 |  |  |  |  |  |  |  |

| r        | Working Register               | Rn      | n = 0 - 15                                                                                                                |  |  |  |  |  |  |  |

| R        | Register                       | Reg     | Reg. represents a number in the range of 00H to FFH                                                                       |  |  |  |  |  |  |  |

| RA       | Relative Address               | Х       | X represents an index in the range of $+127$ to $-128$ which is an offset relative to the address of the next instruction |  |  |  |  |  |  |  |

| rr       | Working Register Pair          | RRp     | p = 0, 2, 4, 6, 8, 10, 12, or 14                                                                                          |  |  |  |  |  |  |  |

| RR       | Register Pair                  | Reg     | Reg. represents an even number in the range of 00H to FEH                                                                 |  |  |  |  |  |  |  |

| Vector   | Vector Address                 | Vector  | Vector represents a number in the range of 00H to FFH                                                                     |  |  |  |  |  |  |  |

| X        | Indexed                        | #Index  | The register or register pair to be indexed is offset by the signed Index value (#Index) in a +127 to -128 range.         |  |  |  |  |  |  |  |

#### Table 115. Notational Shorthand

Table 116 contains additional symbols that are used throughout the Instruction Summary and Instruction Set Description sections.

| Mnemonic | Operands | Instruction             |  |  |  |  |  |  |  |

|----------|----------|-------------------------|--|--|--|--|--|--|--|

| CCF      | _        | Complement Carry Flag   |  |  |  |  |  |  |  |

| DI       | —        | Disable Interrupts      |  |  |  |  |  |  |  |

| EI       | _        | Enable Interrupts       |  |  |  |  |  |  |  |

| HALT     | _        | Halt Mode               |  |  |  |  |  |  |  |

| NOP      | _        | No Operation            |  |  |  |  |  |  |  |

| RCF      | —        | Reset Carry Flag        |  |  |  |  |  |  |  |

| SCF      | _        | Set Carry Flag          |  |  |  |  |  |  |  |

| SRP      | src      | Set Register Pointer    |  |  |  |  |  |  |  |

| STOP     | —        | Stop Mode               |  |  |  |  |  |  |  |

| WDT      | _        | Watch-Dog Timer Refresh |  |  |  |  |  |  |  |

#### **Table 121. CPU Control Instructions**

## Table 122. Load Instructions

| Mnemonic | Operands    | Instruction                                                            |

|----------|-------------|------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                  |

| LD       | dst, src    | Load                                                                   |

| LDC      | dst, src    | Load Constant to/from Program Memory                                   |

| LDCI     | dst, src    | Load Constant to/from Program Memory and Auto-Increment<br>Addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                 |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-Increment<br>Addresses |

| LDX      | dst, src    | Load using Extended Addressing                                         |

| LEA      | dst, X(src) | Load Effective Address                                                 |

| POP      | dst         | Рор                                                                    |

| POPX     | dst         | Pop using Extended Addressing                                          |

| PUSH     | src         | Push                                                                   |

| PUSHX    | src         | Push using Extended Addressing                                         |

| Assembly        |                                                                                                                            | Address Mode |     | Opcode(s) | Flags                           |   |   |   |   |   | Fotob | Instr. |

|-----------------|----------------------------------------------------------------------------------------------------------------------------|--------------|-----|-----------|---------------------------------|---|---|---|---|---|-------|--------|

| Mnemonic        | Symbolic Operation                                                                                                         | dst          | src | (Hex)     | С                               | Z | S | V | D | Н |       | Cycles |

| POP dst         | $dst \leftarrow @SP$ $SP \leftarrow SP + 1$                                                                                | R            |     | 50        | -                               | - | - | - | - | - | 2     | 2      |

|                 |                                                                                                                            | IR           |     | 51        | -                               |   |   |   |   |   | 2     | 3      |

| POPX dst        | $dst \leftarrow @SP \\ SP \leftarrow SP + 1$                                                                               | ER           |     | D8        | -                               | - | - | - | - | - | 3     | 2      |

| PUSH src        | $SP \leftarrow SP - 1$                                                                                                     | R            |     | 70        | -                               | - | - | - | - | - | 2     | 2      |

|                 | $@SP \leftarrow src$                                                                                                       | IR           |     | 71        | -                               |   |   |   |   |   | 2     | 3      |

| PUSHX src       | $SP \leftarrow SP - 1$<br>@SP \leftarrow src                                                                               | ER           |     | C8        | -                               | - | - | - | - | - | 3     | 2      |

| RCF             | C ← 0                                                                                                                      |              |     | CF        | 0                               | - | - | - | - | - | 1     | 2      |

| RET             | $\begin{array}{l} PC \leftarrow @SP \\ SP \leftarrow SP + 2 \end{array}$                                                   |              |     | AF        | -                               | - | - | - | - | - | 1     | 4      |

| RL dst          | C                                                                                                                          | R            |     | 90        | *                               | * | * | * | - | - | 2     | 2      |

|                 |                                                                                                                            | IR           |     | 91        | -                               |   |   |   |   |   | 2     | 3      |

| RLC dst         | C                                                                                                                          | R            |     | 10        | *                               | * | * | * | - | - | 2     | 2      |

|                 |                                                                                                                            | IR           |     | 11        |                                 |   |   |   |   |   | 2     | 3      |

| RR dst          |                                                                                                                            | R            |     | E0        | *                               | * | * | * | - | - | 2     | 2      |

|                 | ► D7 D6 D5 D4 D3 D2 D1 D0<br>dst                                                                                           | IR           |     | E1        | -                               |   |   |   |   |   | 2     | 3      |

| RRC dst         | ► D7D6D5D4D3D2D1D0 ► C                                                                                                     | R            |     | C0        | *                               | * | * | * | - | - | 2     | 2      |

|                 |                                                                                                                            | IR           |     | C1        | -                               |   |   |   |   |   | 2     | 3      |

| Flags Notation: | <ul> <li>* = Value is a function of the result of the operation.</li> <li>- = Unaffected</li> <li>X = Undefined</li> </ul> |              |     |           | 0 = Reset to  0 $1 = Set to  1$ |   |   |   |   |   |       |        |

## Table 126. eZ8 CPU Instruction Summary (Continued)

## Z8F640x/Z8F480x/Z8F320x/Z8F240x/Z8F160x Z8 Encore!®

205

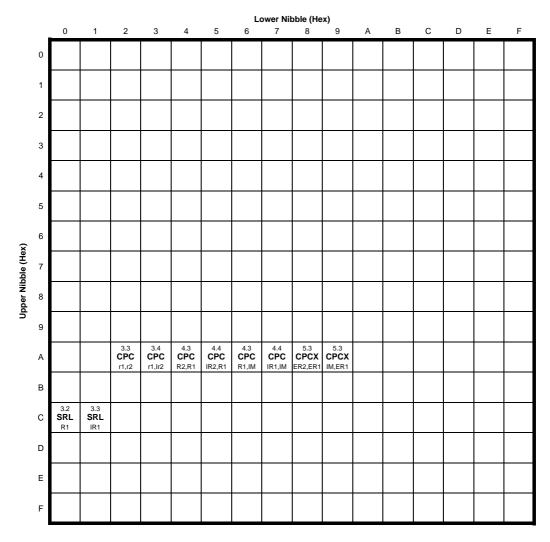

Figure 102. Second Opcode Map after 1FH

# **Problem Description or Suggestion**

Provide a complete description of the problem or your suggestion. If you are reporting a specific problem, include all steps leading up to the occurrence of the problem. Attach additional pages as necessary.