# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I²C, IrDA, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 31                                                        |

| Program Memory Size        | 16KB (16K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 2K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 44-LQFP                                                   |

| Supplier Device Package    | 44-LQFP (10x10)                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1601an020sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Signal and Pin Descriptions

# **Overview**

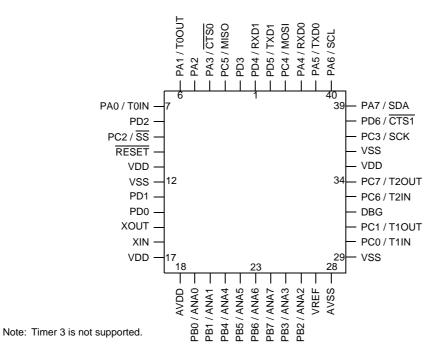

The Z8F640x family products are available in a variety of packages styles and pin configurations. This chapter describes the signals and available pin configurations for each of the package styles. For information regarding the physical package specifications, please refer to the chapter Packaging on page 206.

# **Available Packages**

Table 2 identifies the package styles that are available for each device within the Z8F640x family product line.

|             | -              |                |                |                |                |               |

|-------------|----------------|----------------|----------------|----------------|----------------|---------------|

| Part Number | 40-pin<br>PDIP | 44-pin<br>LQFP | 44-pin<br>PLCC | 64-pin<br>LQFP | 68-pin<br>PLCC | 80-pin<br>QFP |

| Z8F1601     | Х              | Х              | Х              |                |                |               |

| Z8F1602     |                |                |                | Х              | Х              |               |

| Z8F2401     | Х              | Х              | Х              |                |                |               |

| Z8F2402     |                |                |                | Х              | Х              |               |

| Z8F3201     | Х              | Х              | Х              |                |                |               |

| Z8F3202     |                |                |                | Х              | Х              |               |

| Z8F4801     | Х              | Х              | Х              |                |                |               |

| Z8F4802     |                |                |                | Х              | Х              |               |

| Z8F4803     |                |                |                |                |                | Х             |

| Z8F6401     | Х              | Х              | Х              |                |                |               |

| Z8F6402     |                |                |                | Х              | Х              |               |

| Z8F6403     |                |                |                |                |                | Х             |

|             |                |                |                |                |                |               |

Table 2.Z8F640x family Package Options

Figure 57. Z8Fxx01 in 44-Pin Plastic Leaded Chip Carrier (PLCC)

8

| Signal Mnemonic | I/O | Description                                          |

|-----------------|-----|------------------------------------------------------|

| Reset           |     |                                                      |

| RESET           | I   | RESET. Generates a Reset when asserted (driven Low). |

| Power Supply    |     |                                                      |

| VDD             | Ι   | Power Supply.                                        |

| AVDD            | Ι   | Analog Power Supply.                                 |

| VSS             | I   | Ground.                                              |

| AVSS            | I   | Analog Ground.                                       |

#### Table 2. Signal Descriptions (Continued)

# **Pin Characteristics**

Table 3 provides detailed information on the **acter** ristics for each pin available on the Z8F640x family products. Data in Table 3 is sorted alphabetically by the pin symbol mnemonic.

Table 3. Pin Characteristics of the **Z8F640x family**

| Symbol<br>Mnemonic | Direction    | Reset<br>Direction | Active Low<br>or<br>Active High | Tri-State<br>Output | Internal<br>Pull-up or<br>Pull-down | Schmitt<br>Trigger<br>Input | Open Drain<br>Output                                                                                              |  |  |  |  |  |  |  |  |  |

|--------------------|--------------|--------------------|---------------------------------|---------------------|-------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| AVSS               | N/A          | N/A                | N/A                             | N/A                 | No                                  | No                          | N/A                                                                                                               |  |  |  |  |  |  |  |  |  |

| AVDD               | N/A          | N/A                | N/A                             | N/A                 | No                                  | No                          | N/A                                                                                                               |  |  |  |  |  |  |  |  |  |

| DBG                | I/O          | I                  | N/A                             | Yes                 | No                                  | Yes                         | Yes                                                                                                               |  |  |  |  |  |  |  |  |  |

| VSS                | N/A          | N/A                | N/A                             | N/A                 | No                                  | No                          | N/A                                                                                                               |  |  |  |  |  |  |  |  |  |

| PA[7:0]            | I/O          | I                  | N/A                             | Yes                 | No                                  | Yes                         | Yes,<br>Programmable                                                                                              |  |  |  |  |  |  |  |  |  |

| PB[7:0]            | I/O          | Ι                  | N/A                             | Yes                 | No                                  | Yes                         | Yes,<br>Programmable                                                                                              |  |  |  |  |  |  |  |  |  |

| PC[7:0]            | I/O          | I                  | N/A                             | Yes                 | No                                  | Yes                         | Yes,<br>Programmable                                                                                              |  |  |  |  |  |  |  |  |  |

| PD[7:0]            | I/O          | Ι                  | N/A                             | Yes                 | No                                  | Yes                         | Yes,<br>Programmable                                                                                              |  |  |  |  |  |  |  |  |  |

| PE7:0]             | I/O          | I                  | N/A                             | Yes                 | No                                  | Yes                         | Yes,<br>Programmable                                                                                              |  |  |  |  |  |  |  |  |  |

| x represents i     | nteger 0, 1, | to indicate        | multiple pins v                 | vith symbol         | mnemonics                           | that differ o               | <i>x</i> represents integer 0, 1, to indicate multiple pins with symbol mnemonics that differ only by the integer |  |  |  |  |  |  |  |  |  |

# General-Purpose I/O

# Overview

The Z8F640x family products support a maximuf seven 8-bit ports (Ports A-G) and one 4-bit port (Port H) for general-purposeuit/output (I/O) operations. Each port contains control and data registers. The GPIOtcod registers are used to determine data direction, open-drain, outputrive current and alternate pin functions. Each port pin is individually programmable.

# GPIO Port Availability By Device

Not all Z8F640x family products support all 8 ports (A-H). Table 10 lists the port pins available with each device and package type.

| Device  | Packages       | Port A | Port B | Port C | Port D     | Port E | Port F | Port G | Port H |

|---------|----------------|--------|--------|--------|------------|--------|--------|--------|--------|

| Z8F1601 | 40-pin         | [7:0]  | [7:0]  | [6:0]  | [6:3, 1:0] | -      | -      | -      | -      |

| Z8F1601 | 44-pin         | [7:0]  | [7:0]  | [7:0]  | [6:0]      |        |        |        |        |

| Z8F1602 | 64- and 68-pin | [7:0]  | [7:0]  | [7:0]  | [7:0]      | [7:0]  | [7]    | [3]    | [3:0]  |

| Z8F2401 | 40-pin         | [7:0]  | [7:0]  | [6:0]  | [6:3, 1:0] | -      | -      | -      | -      |

| Z8F2401 | 44-pin         | [7:0]  | [7:0]  | [7:0]  | [6:0]      | -      | -      | -      | -      |

| Z8F2402 | 64- and 68-pin | [7:0]  | [7:0]  | [7:0]  | [7:0]      | [7:0]  | [7]    | [3]    | [3:0]  |

| Z8F3201 | 40-pin         | [7:0]  | [7:0]  | [6:0]  | [6:3, 1:0] | -      | -      | -      | -      |

| Z8F3201 | 44-pin         | [7:0]  | [7:0]  | [7:0]  | [6:0]      | -      | -      | -      | -      |

| Z8F3202 | 64- and 68-pin | [7:0]  | [7:0]  | [7:0]  | [7:0]      | [7:0]  | [7]    | [3]    | [3:0]  |

| Z8F4801 | 40-pin         | [7:0]  | [7:0]  | [6:0]  | [6:3, 1:0] | -      | -      | -      | -      |

| Z8F4801 | 44-pin         | [7:0]  | [7:0]  | [7:0]  | [6:0]      | -      | -      | -      | -      |

| Z8F4802 | 64- and 68-pin | [7:0]  | [7:0]  | [7:0]  | [7:0]      | [7:0]  | [7]    | [3]    | [3:0]  |

| Z8F4803 | 80-pin         | [7:0]  | [7:0]  | [7:0]  | [7:0]      | [7:0]  | [7:0]  | [7:0]  | [3:0]  |

| Z8F6401 | 40-pin         | [7:0]  | [7:0]  | [6:0]  | [6:3, 1:0] | -      | -      | -      | -      |

Port A-H Data Direction Sub-Registers

The Port A-H Data Direction sub-registeraiscessed through the Port A-H Control register by writing 01H to the Port A+ Address register (Table 15).

Table 15. Port A-H Data Direction Sub-Registers

| BITS  | 7   | 6                                                                             | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-------|-----|-------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|--|--|

| FIELD | DD7 | DD6                                                                           | DD5 | DD4 | DD3 | DD2 | DD1 | DD0 |  |  |

| RESET | 1   | 1                                                                             | 1   | 1   | 1   | 1   | 1   | 1   |  |  |

| R/W   | R/W | R/W                                                                           | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| ADDR  |     | If 01H in Port A-H Address Register, accessible via Port A-H Control Register |     |     |     |     |     |     |  |  |

#### DD[7:0]—Data Direction

These bits control the direction of the asatecial port pin. Port Alternate Function operation overrides the Data Direction register setting.

0 = Output. Data in the Port A-H Output **ta** egister is driven onto the port pin.

1 = Input. The port pin is sampled and the value written into the Port A-H Input Data Register. The output driver is tri-stated.

Port A-H Alternate Function Sub-Registers

The Port A-H Alternate Function sub-register (Table 16) is accessed through the Port A-H Control register by writing 2H to the Port A-H Address register. The Port A-H Alternate Function sub-registers select the alternate functions for the selected pins. Refer to the **GPIO Alternate Functions** section to determine the alternate function associated with each port pin.

Caution: Do not enable alternate function **GPIO** port pins which do not have an associated alternate function. Failur**édto**w this guideline may result in unpredictable operation.

| BITS  | 7   | 6                                                                             | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-------|-----|-------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|--|--|

| FIELD | AF7 | AF6                                                                           | AF5 | AF4 | AF3 | AF2 | AF1 | AF0 |  |  |

| RESET | 0   | 0                                                                             | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

| R/W   | R/W | R/W                                                                           | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| ADDR  |     | If 02H in Port A-H Address Register, accessible via Port A-H Control Register |     |     |     |     |     |     |  |  |

Table 16. Port A-H Alternate Function Sub-Registers

57

# **Timers**

# Overview

The Z8F640x family products contain three douf 16-bit reloadable timers that can be used for timing, event counting, or generation pulse-width modulated (PWM) signals. The timers' features include:

- 16-bit reload counter

- Programmable prescaler with prescale values from 1 to 128

- PWM output generation

- Capture and compare capability

- External input pin for timer input, clock tigag, or capture signal. External input pin signal frequency is limited to a maximum fone-fourth the system clock frequency.

- Timer output pin

- Timer interrupt

In addition to the timers described in tbhapter, the Baud RaGenerators for any unused UART, SPI,  $o^2 \mathbb{C}$  peripherals may also be used to provide basic timing functionality. Refer to the respective serial communication peripheral chapters for information on using the Baud Rate Generators as timers. Timer 3 is unavailable in the 40- and 44-pin packages.

# Architecture

Figure 66 illustrates the architecture of the timers.

out, first set the POL bit in the Timer Control Register to the start value before beginning One-Shot mode. Then, after starting the timer **set** to the opposite bit value.

The steps for configuring a timer for One-Shoulde and initiating the count are as follows:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for One-Shot mode.

- Set the prescale value.

- If using the Timer Output alternate functioset the initial output level (High or Low).

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If desired, enable the timer interrupt **ared** the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, cogfire the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer and initiate counting.

In One-Shot mode, the system clock always vides the timer input. The timer period is given by the following equation:

# One-Shot Mode Time-Out Period (s) = (Reload Value – Start Value) × Prescale System Clock Frequency (Hz)

### Continuous Mode

In Continuous mode, the timer counts up **to 16**-bit Reload value stored in the Timer Reload High and Low Byte registers. The **time**put is the system clock. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset **to 1H** and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) upon timer Reload.

The steps for configuring a timer for Continuous de and initiating the count are as follows:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for Continuous mode.

- Set the prescale value.

set to 2-byte transfers, the temporary holdingister for the Timer Reload High Byte is not bypassed.

| BITS  | 7   | 6                      | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-------|-----|------------------------|-----|-----|-----|-----|-----|-----|--|--|

| FIELD | TRH |                        |     |     |     |     |     |     |  |  |

| RESET | 1   | 1                      | 1   | 1   | 1   | 1   | 1   | 1   |  |  |

| R/W   | R/W | R/W                    | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| ADDR  |     | F02H, F0AH, F12H, F1AH |     |     |     |     |     |     |  |  |

Table 40. Timer 0-3 Reload High Byte Register (TxRH)

#### Table 41. Timer 0-3 Reload Low Byte Register (TxRL)

| BITS  | 7   | 6                      | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-------|-----|------------------------|-----|-----|-----|-----|-----|-----|--|--|

| FIELD | TRL |                        |     |     |     |     |     |     |  |  |

| RESET | 1   | 1                      | 1   | 1   | 1   | 1   | 1   | 1   |  |  |

| R/W   | R/W | R/W                    | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| ADDR  |     | F03H, F0BH, F13H, F1BH |     |     |     |     |     |     |  |  |

TRH and TRL—Timer Reload Register High and Low

These two bytes form the 16-bit Reload val(TeRH[7:0], TRL[7:0]}. This value is used to set the maximum count value which initiates a timer reload to H. In Compare mode, these two byte form the 16-bit Compare value.

86

3. Enable the Baud Rate Generator timer **fionc** and associated interrupt by setting the BIRQ bit in the UART Control 1 register to 1.

# **UART** Control Register Definitions

The UART control registers support both the RWs and the associated Infrared Encoder/ Decoders. For more information on the infrared operation, refer **Infrared Encoder**/ **Decoder** chapter on page 95.

### UART x Transmit Data Register

Data bytes written to the UARTTransmit Data register (Table 50) are shifted out on the TXDx pin. The Write-only UART Transmit Data register shares a Register File address with the Read-only UART Receive Data register.

| BITS  | 7   | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|-----|---------------|---|---|---|---|---|---|--|--|

| FIELD | TXD |               |   |   |   |   |   |   |  |  |

| RESET | х   | х             | х | х | Х | х | х | х |  |  |

| R/W   | W   | W             | W | W | W | W | W | W |  |  |

| ADDR  |     | F40H and F48H |   |   |   |   |   |   |  |  |

Table 50. UARTx Transmit Data Register (UxTXD)

TXD—Transmit Data

UART transmitter data byte to be shifted out through the **T** XID.

89

| BITS  | 7 | 6        | 5 | 4      | 3       | 2 | 1 | 0 |  |  |

|-------|---|----------|---|--------|---------|---|---|---|--|--|

| FIELD |   | Reserved |   |        |         |   |   |   |  |  |

| RESET | 0 | 0        | 0 | 0      | 0       | 0 | 0 | 0 |  |  |

| R/W   | R | R        | R | R      | R       | R | R | R |  |  |

| ADDR  |   |          |   | F44H a | nd F4CH |   |   |   |  |  |

#### Table 53. UARTx Status 1 Register (UxSTAT1)

#### Reserved

These bits are reserved and must be 0.

#### MPRX—Multiprocessor Receive

This status bit is for the receiver and reflectes actual status of the last multiprocessor bit received. Reading from the UART Dategister resets this bit to 0.

# UART x Control 0 and Control 1 Registers

The UARTx Control 0 and Control 1 registers (Test 54 and 55) configure the properties of the UART's transmit and receive operation be UART Control registers must ben be written while the UART is enabled.

| BITS  | 7             | 6   | 5    | 4   | 3    | 2    | 1    | 0    |

|-------|---------------|-----|------|-----|------|------|------|------|

| FIELD | TEN           | REN | CTSE | PEN | PSEL | SBRK | STOP | LBEN |

| RESET | 0             | 0   | 0    | 0   | 0    | 0    | 0    | 0    |

| R/W   | R/W           | R/W | R/W  | R/W | R/W  | R/W  | R/W  | R/W  |

| ADDR  | F42H and F4AH |     |      |     |      |      |      |      |

Table 54. UARTx Control 0 Register (UxCTL0)

**TEN**—Transmit Enable

This bit enables or disables the transmittee enable is also controlled by the Cational and the CTSE bit. If the CTS signal is low and the TSE bit is 1, the transmitter is enabled.

0 = Transmitter disabled.

1 = Transmitter enabled.

REN—Receive Enable

This bit enables or disables the receiver.

- 0 = Receiver disabled.

- 1 = Receiver enabled.

#### **Table 58. UART Baud Rates**

#### 20.0 MHz System Clock

| Desired Rate | Desired Rate BRG Divisor |        | Error |

|--------------|--------------------------|--------|-------|

| (kHz)        | (Decimal)                | (kHz)  | (%)   |

| 1250.0       | 1                        | 1250.0 | 0.00  |

| 625.0        | 2                        | 625.0  | 0.00  |

| 250.0        | 5                        | 250.0  | 0.00  |

| 115.2        | 11                       | 113.6  | -1.36 |

| 57.6         | 22                       | 56.8   | -1.36 |

| 38.4         | 33                       | 37.9   | -1.36 |

| 19.2         | 65                       | 19.2   | 0.16  |

| 9.60         | 130                      | 9.62   | 0.16  |

| 4.80         | 260                      | 4.81   | 0.16  |

| 2.40         | 521                      | 2.40   | -0.03 |

| 1.20         | 1042                     | 1.20   | -0.03 |

| 0.60         | 2083                     | 0.60   | 0.02  |

| 0.30         | 4167                     | 0.30   | -0.01 |

|              |                          |        |       |

| Desired Rate | BRG Divisor | Actual Rate | Error  |  |  |

|--------------|-------------|-------------|--------|--|--|

| (kHz)        | (Decimal)   | (kHz)       | (%)    |  |  |

| 1250.0       | 1           | 1152.0      | -7.84% |  |  |

| 625.0        | 2           | 576.0       | -7.84% |  |  |

| 250.0        | 5           | 230.4       | -7.84% |  |  |

| 115.2        | 10          | 115.2       | 0.00   |  |  |

| 57.6         | 20          | 57.6        | 0.00   |  |  |

| 38.4         | 30          | 38.4        | 0.00   |  |  |

| 19.2         | 60          | 19.2        | 0.00   |  |  |

| 9.60         | 120         | 9.60        | 0.00   |  |  |

| 4.80         | 240         | 4.80        | 0.00   |  |  |

| 2.40         | 480         | 2.40        | 0.00   |  |  |

| 1.20         | 960         | 1.20        | 0.00   |  |  |

| 0.60         | 1920        | 0.60        | 0.00   |  |  |

| 0.30         | 3840        | 0.30        | 0.00   |  |  |

|              |             |             |        |  |  |

18.432 MHz System Clock

11.0592 MHz System Clock

#### 16.667 MHz System Clock

| Desired Rate | BRG Divisor | Actual Rate | Error  | Desired Rate | BRG Divisor | Actual Rate | Error |

|--------------|-------------|-------------|--------|--------------|-------------|-------------|-------|

| (kHz)        | (Decimal)   | (kHz)       | (%)    | (kHz)        | (Decimal)   | (kHz)       | (%)   |

| 1250.0       | 1           | 1041.69     | -16.67 | 1250.0       | N/A         | N/A         | N/A   |

| 625.0        | 2           | 520.8       | -16.67 | 625.0        | 1           | 691.2       | 10.59 |

| 250.0        | 4           | 260.4       | 4.17   | 250.0        | 3           | 230.4       | -7.84 |

| 115.2        | 9           | 115.7       | 0.47   | 115.2        | 6           | 115.2       | 0.00  |

| 57.6         | 18          | 57.87       | 0.47   | 57.6         | 12          | 57.6        | 0.00  |

| 38.4         | 27          | 38.6        | 0.47   | 38.4         | 18          | 38.4        | 0.00  |

| 19.2         | 54          | 19.3        | 0.47   | 19.2         | 36          | 19.2        | 0.00  |

| 9.60         | 109         | 9.56        | -0.45  | 9.60         | 72          | 9.60        | 0.00  |

| 4.80         | 217         | 4.80        | -0.83  | 4.80         | 144         | 4.80        | 0.00  |

| 2.40         | 434         | 2.40        | 0.01   | 2.40         | 288         | 2.40        | 0.00  |

| 1.20         | 868         | 1.20        | 0.01   | 1.20         | 576         | 1.20        | 0.00  |

| 0.60         | 1736        | 0.60        | 0.01   | 0.60         | 1152        | 0.60        | 0.00  |

| 0.30         | 3472        | 0.30        | 0.01   | 0.30         | 2304        | 0.30        | 0.00  |

|              |             |             |        |              |             |             |       |

If the current ADC Analog Input is not theighest numbered input to be converted, DMA\_ADC initiates data conversion in the thigher numbered ADC Analog Input.

Configuring DMA\_ADC for Data Transfer

Follow these steps to configure and enable DMA\_ADC:

- 1. Write the DMA\_ADC Address register with the 7 most-significant bits of the Register File address for data transfers.

- 2. Write to the DMA\_ADC Control register to complete the following:

- Enable the DMA\_ADC interrupt request, if desired

- Select the number of ADC Analog Inputs to convert

- Enable the DMA\_ADC channel

- Caution:

When using the DMA\_ADC to perform conversions on multiple ADC inputs and the DC\_IN field in the DMA\_ADC Control Register is greater than 000b, the Analog-to-Digital Converter must be configured for Single-Shot mode.

Continuous mode operation of the ADC **carly** be used in conjunction with DMA\_ADC if the ADC\_IN field in the DMA\_ADC Control Register is reset to 000b to enable conversion on ADC Analog Input 0 only.

# **DMA Control Register Definitions**

### DMA x Control Register

The DMAx Control register is used to enabled select the mode of operation for DMA

| BITS  | 7          | 6   | 5    | 4     | 3    | 2   | 1   | 0   |

|-------|------------|-----|------|-------|------|-----|-----|-----|

| FIELD | DEN        | DLE | DDIR | IRQEN | WSEL |     | RSS |     |

| RESET | 0          | 0   | 0    | 0     | 0    | 0   | 0   | 0   |

| R/W   | R/W        | R/W | R/W  | R/W   | R/W  | R/W | R/W | R/W |

| ADDR  | FB0H, FB8H |     |      |       |      |     |     |     |

Table 71. DMAx Control Register (DMAxCTL)

DEN—DMAx Enable

0 = DMAx is disabled and data traffer requests are disregarded.

# Analog-to-Digital Converter

# Overview

The Analog-to-Digital Converter (ADC) converts an analog input signal to a 10-bit binary number. The features of the sigma-delta ADC include:

- 12 analog input sources are multiplexed with general-purpose I/O ports

- Interrupt upon conversion complete

- Internal voltage reference generator

- Direct Memory Access (DMA) controller pæutomatically initiate data conversion and transfer of the data from 1 to 12 of the analog inputs.

# Architecture

Figure 83 illustrates the three major function blacks (converter, analog multiplexer, and voltage reference generator) of the ADC. THEC converts an analog input signal to its digital representation. The 12-input analog multiplexer selects one of the 12 analog input sources. The ADC requires an input reference for the conversion. The voltage reference for the conversion may be input throthe external VREF pin or generated internally by the voltage reference generator.

| Debug Command          | Command Byte | Enabled when NOT in Debug mode? | Disabled by<br>Read Protect Option Bit |

|------------------------|--------------|---------------------------------|----------------------------------------|

| Write Program Memory   | 0AH          | -                               | Disabled                               |

| Read Program Memory    | 0BH          | -                               | Disabled                               |

| Write Data Memory      | 0CH          | -                               | Yes                                    |

| Read Data Memory       | 0DH          | -                               | -                                      |

| Read Program Memory CR | C 0EH        | -                               | -                                      |

| Reserved               | 0FH          | -                               | -                                      |

| Step Instruction       | 10H          | -                               | Disabled                               |

| Stuff Instruction      | 11H          | -                               | Disabled                               |

| Execute Instruction    | 12H          | -                               | Disabled                               |

| Reserved               | 13H - 1FH    | -                               | -                                      |

| Write Watchpoint       | 20H          | -                               | Disabled                               |

| Read Watchpoint        | 21H          | -                               | -                                      |

| Reserved               | 22H - FFH    | -                               | -                                      |

#### Table 93. On-Chip Debugger Commands

In the following bulleted list of OCD Commands and commands sent from the host to the On-Chip Debugger are identified by G <-- Command/Data'. Data sent from the On-Chip Debugger back to the host is identified by C'--> Data'

• Read OCD Revision (00H)—The Read OCD Revisiorommand is used to determine the version of the On-Clopebugger. If OCD commands are added, removed, or changed, this vision number changes.

```

DEG <-- 00H

DEG --> OCDREV[15:8] (Major revision number)

DEG --> OCDREV[7:0] (Minor revision number)

```

• **Read OCD Status Register (02H)**—The Read OCD Status Register command is used to read the OCDSTAT register.

```

DBG <-- 02H

DBG --> OCDSTAT[7:0]

```

• Read Runtime Counter (03H)—The Runtime Counter is used to count Z8 Encore! system clock cycles in between Breakpoints. The 16-bit Runtime Counter counts up from 0000H and stops at the maximum counteofFH. The Runtime Counter is overwritten during the Write Memory, Readtemory, Write Register, Read Register, Read Memory CRC, Step InstructionufSInstruction, and Execute Instruction commands.

| Parameter                                                                                          | Minimum | Maximum | Units | Notes |

|----------------------------------------------------------------------------------------------------|---------|---------|-------|-------|

| 68-Pin PLCC Maximum Ratings at 70 <sup>0</sup> C to 105 <sup>0</sup> C                             |         |         |       |       |

| Total power dissipation                                                                            |         | 500     | mW    |       |

| Maximum current into $ ot\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |         | 140     | mA    |       |

| 64-Pin LQFP Maximum Ratings at -40°C to 70°C                                                       |         |         |       |       |

| Total power dissipation                                                                            |         | 1000    | mW    |       |

| Maximum current into $ ot\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |         | 275     | mA    |       |

| 64-Pin LQFP Maximum Ratings at 70 <sup>0</sup> C to 105 <sup>0</sup> C                             |         |         |       |       |

| Total power dissipation                                                                            |         | 540     | mW    |       |

| Maximum current into                                                                               |         | 150     | mA    |       |

| 44-Pin PLCC Maximum Ratings at -40°C to 70°C                                                       |         |         |       |       |

| Total power dissipation                                                                            |         | 750     | mW    |       |

| Maximum current into $ ot\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |         | 200     | mA    |       |

| 44-Pin PLCC Maximum Ratings at 70 <sup>0</sup> C to 105 <sup>0</sup> C                             |         |         |       |       |

| Total power dissipation                                                                            |         | 295     | mW    |       |

| Maximum current into $\mathcal{Y}_D$ or out of $V_{SS}$                                            |         | 83      | mA    |       |

| 44-pin LQFP Maximum Ratings at -40°C to 70°C                                                       |         |         |       |       |

| Total power dissipation                                                                            |         | 750     | mW    |       |

| Maximum current into $\mathcal{Y}_D$ or out of $V_{SS}$                                            |         | 200     | mA    |       |

| 44-pin LQFP Maximum Ratings at 70 <sup>0</sup> C to 105 <sup>0</sup> C                             |         |         |       |       |

| Total power dissipation                                                                            |         | 410     | mW    |       |

| Maximum current into $\mathcal{Y}_D$ or out of $V_{SS}$                                            |         | 114     | mA    |       |

| 40-Pin PDIP Maximum Ratings at -40°C to 70°C                                                       |         |         |       |       |

| Total power dissipation                                                                            |         | 1000    | mW    |       |

| Maximum current into $ ot\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |         | 275     | mA    |       |

| 40-Pin PDIP Maximum Ratings at 70°C to 105°C                                                       |         |         |       |       |

| Total power dissipation                                                                            |         | 540     | mW    |       |

| Maximum current into                                                                               |         | 150     | mA    |       |

| Natao                                                                                              |         |         |       |       |

Notes:

This voltage applies to all pins except the following: V<sub>DD</sub>, AV<sub>DD</sub>, pins supporting analog input (Port B and Port H), RESET, and where noted otherwise. 168

# AC Characteristics

The section provides information on th€ characteristics and timing of the Z8 Encore!™. All AC timing information assumes a standard load of 50pF on all outputs.

# Table 102. AC Characteristics

|                     |                              | $V_{DD} = 3$ $T_A = -40^{\circ}$ | $V_{DD} = 3.0 - 3.6V$<br>$T_A = -40^{\circ}C$ to $105^{\circ}C$ |       |                                                                                                 |

|---------------------|------------------------------|----------------------------------|-----------------------------------------------------------------|-------|-------------------------------------------------------------------------------------------------|

| Symbol              | Parameter                    | Minimum                          | Maximum                                                         | Units | Conditions                                                                                      |

| F <sub>syscik</sub> | System Clock Frequency       | -                                | 20.0                                                            | MHz   | Read-only from Flash memory.                                                                    |

|                     |                              | 0.032768                         | 20.0                                                            | MHz   | Program or erasure of the Flash memory.                                                         |

| F <sub>XTAL</sub>   | Crystal Oscillator Frequency | 1.0                              | 20.0                                                            | MHz   | System clock frequencies below the crystal oscillator minimum require an external clock driver. |

| T <sub>XIN</sub>    | System Clock Period          | 50                               | -                                                               | ns    | T <sub>CLK</sub> = 1/F <sub>sysclk</sub>                                                        |

| T <sub>XINH</sub>   | System Clock High Time       | 20                               | 30                                                              | ns    | T <sub>CLK</sub> = 50ns                                                                         |

| T <sub>XINL</sub>   | System Clock Low Time        | 20                               | 30                                                              | ns    | T <sub>CLK</sub> = 50ns                                                                         |

| T <sub>XINR</sub>   | System Clock Rise Time       | -                                | 3                                                               | ns    | T <sub>CLK</sub> = 50ns                                                                         |

| T <sub>XINF</sub>   | System Clock Fall Time       | -                                | 3                                                               | ns    | T <sub>CLK</sub> = 50ns                                                                         |

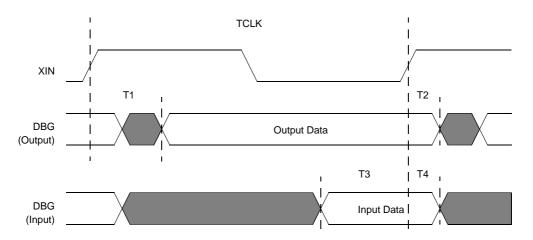

# **On-Chip Debugger Timing**

Figure 95 and Table 109 provide timing information for DBG pins. The timing specifications presume a rise and fall time on DBG of less that 4

Figure 95. On-Chip Debugger Timing

|                |                                  | Delay (ns) |                     |  |  |

|----------------|----------------------------------|------------|---------------------|--|--|

| Parameter      | Abbreviation                     | Minimum    | Maximum             |  |  |

| DBG            |                                  |            |                     |  |  |

| T <sub>1</sub> | XIN Rise to DBG Valid Delay      | -          | 15                  |  |  |

| T <sub>2</sub> | XIN Rise to DBG Output Hold Time | 2          | -                   |  |  |

| T <sub>3</sub> | DBG to XIN Rise Input Setup Time | 10         | _                   |  |  |

| T <sub>4</sub> | DBG to XIN Rise Input Hold Time  | 5          | _                   |  |  |

|                | DBG frequency                    |            | System<br>Clock / 4 |  |  |

| Table | 109. | <b>On-Chip</b> | Debugger  | Timing |

|-------|------|----------------|-----------|--------|

|       |      | on omp         | 200000000 |        |

| Mnemonic | Operands | Instruction                |

|----------|----------|----------------------------|

| BSWAP    | dst      | Bit Swap                   |

| RL       | dst      | Rotate Left                |

| RLC      | dst      | Rotate Left through Carry  |

| RR       | dst      | Rotate Right               |

| RRC      | dst      | Rotate Right through Carry |

| SRA      | dst      | Shift Right Arithmetic     |

| SRL      | dst      | Shift Right Logical        |

| SWAP     | dst      | Swap Nibbles               |

Table 125. Rotate and Shift Instructions

# eZ8 CPU Instruction Summary

Table 126 summarizes the eZ8 CPU instructions. The table identifies the addressing modes employed by the instruction, the effect upon the Flags register, the number of CPU clock cycles required for the instructiont de, and the number of CPU clock cycles required for the instruction.

| Assembly<br>Mnemonic | Symbolic Operation                                         | Address Mode |          | <b>Opcode</b> (s) | Flags |   |   |   |    |           | - Fetch | Instr    |   |

|----------------------|------------------------------------------------------------|--------------|----------|-------------------|-------|---|---|---|----|-----------|---------|----------|---|

|                      |                                                            | dst          | src      | (Hex)             | С     | Z | ł | S | v  | D         | Н       | I Cycles |   |

| ADC dst, src         | dst– dst + src + C                                         | r            | r        | 12                | *     |   | ۲ | * | *  | 0         | *       | 2        | 3 |

|                      |                                                            | r            | lr       | 13                | •     |   |   |   |    |           |         | 2        | 4 |

|                      |                                                            | R            | R        | 14                | •     |   |   |   |    |           |         | 3        | 3 |

|                      |                                                            | R            | IR       | 15                | •     |   |   |   |    |           |         | 3        | 4 |

|                      |                                                            | R            | IM       | 16                | •     |   |   |   |    |           |         | 3        | 3 |

|                      |                                                            | IR           | IM       | 17                | •     |   |   |   |    |           |         | 3        | 4 |

| ADCX dst, src        | dst– dst + src + C                                         | ER           | ER       | 18                | ,     | * | * | * | *  | 0         | *       | 4        | 3 |

|                      |                                                            | ER           | IM       | 19                | •     |   |   |   |    |           |         | 4        | 3 |

| Flags Notation:      | * = Value is a function<br>- = Unaffected<br>X = Undefined | n of the re  | esult of | the operatio      | n.    | - |   |   | to | :o 0<br>1 |         |          |   |

Table 126. eZ8 CPU Instruction Summary

| Part                                                          | Flash<br>KB (Bytes) | RAM<br>KB (Bytes) | Max. Speed<br>(MHz) | Temp<br>( <sup>0</sup> C) | Voltage<br>(V) | Package | Part Number    |  |  |  |  |  |

|---------------------------------------------------------------|---------------------|-------------------|---------------------|---------------------------|----------------|---------|----------------|--|--|--|--|--|

| Z8 Encore! <sup>®</sup> with 48KB Flash, Extended Temperature |                     |                   |                     |                           |                |         |                |  |  |  |  |  |

| Z8 Encore®                                                    | 48 (49,152)         | 4 (4096)          | 20                  | -40 to +105               | 3.0 - 3.6      | PDIP-40 | Z8F4801PM020EC |  |  |  |  |  |

| Z8 Encore®                                                    | 48 (49,152)         | 4 (4096)          | 20                  | -40 to +105               | 3.0 - 3.6      | LQFP-44 | Z8F4801AN020EC |  |  |  |  |  |

| Z8 Encore®                                                    | 48 (49,152)         | 4 (4096)          | 20                  | -40 to +105               | 3.0 - 3.6      | PLCC-44 | Z8F4801VN020EC |  |  |  |  |  |

| Z8 Encore®                                                    | 48 (49,152)         | 4 (4096)          | 20                  | -40 to +105               | 3.0 - 3.6      | LQFP-64 | Z8F4802AR020EC |  |  |  |  |  |

| Z8 Encore®                                                    | 48 (49,152)         | 4 (4096)          | 20                  | -40 to +105               | 3.0 - 3.6      | PLCC-68 | Z8F4802VS020EC |  |  |  |  |  |

| Z8 Encore®                                                    | 48 (49,152)         | 4 (4096)          | 20                  | -40 to +105               | 3.0 - 3.6      | QFP-80  | Z8F4803FT020EC |  |  |  |  |  |

| Z8 Encore! <sup>®</sup> with 64KB Flash, Extended Temperature |                     |                   |                     |                           |                |         |                |  |  |  |  |  |

| Z8 Encore®                                                    | 64 (65,536)         | 4 (4096)          | 20                  | -40 to +105               | 3.0 - 3.6      | PDIP-40 | Z8F6401PM020EC |  |  |  |  |  |

| Z8 Encore®                                                    | 64 (65,536)         | 4 (4096)          | 20                  | -40 to +105               | 3.0 - 3.6      | LQFP-44 | Z8F6401AN020EC |  |  |  |  |  |

| Z8 Encore®                                                    | 64 (65,536)         | 4 (4096)          | 20                  | -40 to +105               | 3.0 - 3.6      | PLCC-44 | Z8F6401VN020EC |  |  |  |  |  |

| Z8 Encore®                                                    | 64 (65,536)         | 4 (4096)          | 20                  | -40 to +105               | 3.0 - 3.6      | LQFP-64 | Z8F6402AR020EC |  |  |  |  |  |

| Z8 Encore!v                                                   | 64 (65,536          | 6) 4 (4096)       | ) 20                | -40 to +105               | 3.0 - 3.6      | PLCC-68 | Z8F6402VS020EC |  |  |  |  |  |

| Z8 Encore®                                                    | 64 (65,536)         | 4 (4096)          | 20                  | -40 to +105               | 3.0 - 3.6      | QFP-80  | Z8F6403FT020EC |  |  |  |  |  |

| Z8 Encore! <sup>®</sup> Development Tools                     |                     |                   |                     |                           |                |         |                |  |  |  |  |  |

| Z8 Encore <sup>®</sup>                                        | Developer K         | it                |                     |                           |                |         | Z8ENCORE000ZCO |  |  |  |  |  |

Table 128. Ordering Information (Continued)

Contact ZILOG's worldwide customer support for more information on ordering the Z8 Encore?. The customer support notice is open from 7 a.nto 7 p.m. Pacific Time.

The customer support toll-free number **Z**akCOG is 1-877-ZiLOGCS (1-877-945-6427). For Z8 Encore<sup>®</sup> the customer support toll-free nber is 1-866-498-3636. The FAX number for the customer support center is 1-603-316-0345. Customers can also gain access to customer support using the ZiLOG website. Z8 Encentes its own web page at www.zilog.com/z8encore

For customer service, navigate your browser to:

http://register.zilog.com/login.asp?login = servicelogin

For technical support, navigate your browser to:

http://register.zilog.com/login.asp?login = supportlogin

register109, 126, 184 ADC control (ADCCTL)135 ADC data high byte (ADCDH) 37 ADC data low bits (ADCDL)137 baud low and high byte (I2CI)21 baud rate high and low byte (SPI)0 control (SPI)107 control, I2C119 data, SPI106 DMA status (DMAA\_STAT)131 DMA ADC address128 DMA\_ADC control DMAACTL) 130 DMAx address high nibble (DMAxH)26 DMAx control (DMAxCTL) 124 DMAx end/address low byte (DMAxEND)28 DMAx start/current address low byte register (DMAxSTART) 128 flash control (FCTL)144 flash high and low byte (FFREQH and FREEQL)147 flash page select (FP\$46 flash status (FSTAT)45 GPIO port A-H address (PxADDR3)7 GPIO port A-H alternate function sub-register39 GPIO port A-H control address (PxCTB) GPIO port A-H data direction sub-registes I2C baud rate high (I2CBRH)21 I2C control (I2CCTL)119 I2C data (I2CDATA)118 I2C status118 I2C status (I2CSTAT)18 I2Cbaud rate low (I2CBRL)21 mode, SPI109 OCD control161 OCD status 62 OCD watchpoint addrests64 OCD watchpoint control 63 OCD watchpoint data64 SPI baud rate high byte (SPIBRH)0 SPI baud rate low byte (SPIBRL)0 SPI control (SPICTL)107 SPI data (SPIDATA)106 SPI status (SPISTAT)08

status, I2CI18 status, SP108 UARTx baud rate high byte (UxBRH9)1 UARTx baud rate low byte (UxBRL92 UARTx Control 0 (UxCTL0)89 UARTx control 1 (UxCTL1)90 UARTx receive data (UxRXD§7 UARTx status 0 (UxSTAT087 UARTx status 1 (UxSTAT189 UARTx transmit data (UxTXD86 watch-dog timer control (WDTCTL75 watch-dog timer reload high byte (WDTF/6) watch-dog timer reload low byte (WDTIZ)7 watch-dog timer reload upper byte (WDTKB register file17 register file address mago register pair 84 register pointer 85 reset and stop mode characterist25 and stop mode recove25 carry flag188 controller5 sources<sub>26</sub> **RET 190** return190 return information216 RL 191 **RLC 191** rotate and shift instructions91 rotate left191 rotate left through carry91 rotate right191 rotate right through carr/v91 **RP185** RR 184, 191 rr 184 RRC 191

# S

SBC 188 SCF 188, 189 SCK 101 225