Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 31                                                        |

| Program Memory Size        | 16KB (16K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 2K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 40-DIP (0.620", 15.75mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1601pm020sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Z8F640x/Z8F480x/Z8F320x/Z8F240x/Z8F160x Z8 Encore!®

| Table 101. | Absolute Maximum Ratings                                                      |

|------------|-------------------------------------------------------------------------------|

| Table 102. | DC Characteristics                                                            |

| Table 103. | AC Characteristics                                                            |

| Table 104. | Power-On Reset and Voltage Brown-Out Electrical<br>Characteristics and Timing |

| Table 105. | Flash Memory Electrical Characteristics and Timing 173                        |

| Table 106. | Watch-Dog Timer Electrical Characteristics and Timing 174                     |

| Table 107. | Analog-to-Digital Converter Electrical Characteristics and Timing             |

| Table 108. | GPIO Port Input Timing                                                        |

| Table 109. | GPIO Port Output Timing 177                                                   |

| Table 110. | On-Chip Debugger Timing 178                                                   |

| Table 111. | SPI Master Mode Timing 179                                                    |

| Table 112. | SPI Slave Mode Timing 180                                                     |

| Table 113. | I2C Timing 181                                                                |

| Table 114. | Assembly Language Syntax Example 1                                            |

| Table 115. | Assembly Language Syntax Example 2 183                                        |

| Table 116. | Notational Shorthand                                                          |

| Table 117. | Additional Symbols                                                            |

| Table 118. | Condition Codes                                                               |

| Table 119. | Arithmetic Instructions                                                       |

| Table 120. | Bit Manipulation Instructions                                                 |

| Table 121. | Block Transfer Instructions                                                   |

| Table 122. | CPU Control Instructions 189                                                  |

| Table 123. | Load Instructions                                                             |

| Table 124. | Logical Instructions                                                          |

| Table 125. | Program Control Instructions 190                                              |

| Table 126. | Rotate and Shift Instructions                                                 |

| Table 127. | eZ8 CPU Instruction Summary 191                                               |

| Table 128. | Opcode Map Abbreviations 203                                                  |

| Table 129. | Ordering Information                                                          |

| Address (Hex) | <b>Register Description</b> | Mnemonic | Reset (Hex) | Page # |

|---------------|-----------------------------|----------|-------------|--------|

| FCE           | Interrupt Port Select       | IRQPS    | 00          | 55     |

| FCF           | Interrupt Control           | IRQCTL   | 00          | 56     |

| GPIO Port A   |                             |          |             |        |

| FD0           | Port A Address              | PAADDR   | 00          | 37     |

| FD1           | Port A Control              | PACTL    | 00          | 38     |

| FD2           | Port A Input Data           | PAIN     | XX          | 42     |

| FD3           | Port A Output Data          | PAOUT    | 00          | 43     |

| GPIO Port B   |                             |          |             |        |

| FD4           | Port B Address              | PBADDR   | 00          | 37     |

| FD5           | Port B Control              | PBCTL    | 00          | 38     |

| FD6           | Port B Input Data           | PBIN     | XX          | 42     |

| FD7           | Port B Output Data          | PBOUT    | 00          | 43     |

| GPIO Port C   | -                           |          |             |        |

| FD8           | Port C Address              | PCADDR   | 00          | 37     |

| FD9           | Port C Control              | PCCTL    | 00          | 38     |

| FDA           | Port C Input Data           | PCIN     | XX          | 42     |

| FDB           | Port C Output Data          | PCOUT    | 00          | 43     |

| GPIO Port D   | Ĩ                           |          |             |        |

| FDC           | Port D Address              | PDADDR   | 00          | 37     |

| FDD           | Port D Control              | PDCTL    | 00          | 38     |

| FDE           | Port D Input Data           | PDIN     | XX          | 42     |

| FDF           | Port D Output Data          | PDOUT    | 00          | 43     |

| GPIO Port E   | Ĩ                           |          |             |        |

| FE0           | Port E Address              | PEADDR   | 00          | 37     |

| FE1           | Port E Control              | PECTL    | 00          | 38     |

| FE2           | Port E Input Data           | PEIN     | XX          | 42     |

| FE3           | Port E Output Data          | PEOUT    | 00          | 43     |

| GPIO Port F   | ×                           |          |             |        |

| FE4           | Port F Address              | PFADDR   | 00          | 37     |

| FE5           | Port F Control              | PFCTL    | 00          | 38     |

| FE6           | Port F Input Data           | PFIN     | XX          | 42     |

| FE7           | Port F Output Data          | PFOUT    | 00          | 43     |

| GPIO Port G   | 1                           |          |             |        |

| FE8           | Port G Address              | PGADDR   | 00          | 37     |

| FE9           | Port G Control              | PGCTL    | 00          | 38     |

| FEA           | Port G Input Data           | PGIN     | XX          | 42     |

| FEB           | Port G Output Data          | PGOUT    | 00          | 43     |

| GPIO Port H   |                             |          |             |        |

| FEC           | Port H Address              | PHADDR   | 00          | 37     |

| XX=Undefined  | 1 011 11 / 1001000          | THEDR    |             | 51     |

## Table 6. Register File Address Map (Continued)

## **Power-On Reset**

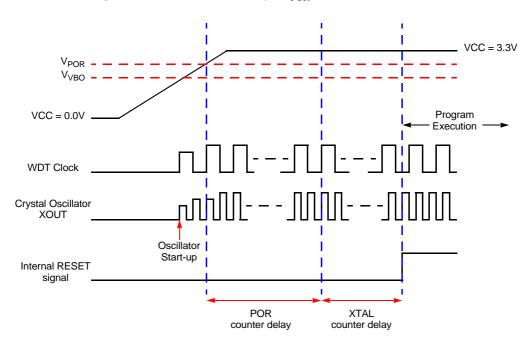

The Z8F640x family products contain an internal Power-On Reset (POR) circuit. The POR circuit monitors the supply voltage and holds the device in the Reset state until the supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold ( $V_{POR}$ ), the POR Counter is enabled and counts 514 cycles of the Watch-Dog Timer oscillator. After the POR counter times out, the XTAL Counter is enabled to count a total of 16 system clock pulses. The Z8F640x family device is held in the Reset state until both the POR Counter and XTAL counter have timed out. After the device exits the Power-On Reset state, the eZ8 CPU fetches the Reset vector. Following Power-On Reset, the POR status bit in the Watch-Dog Timer Control (WDTCTL) register is set to 1.

Figure 62 illustrates Power-On Reset operation. Refer to the **Electrical Characteristics** chapter for the POR threshold voltage ( $V_{POR}$ ).

Figure 62. Power-On Reset Operation (not to scale)

## Voltage Brown-Out Reset

The devices in the Z8F640x family provide low Voltage Brown-Out (VBO) protection. The VBO circuit senses when the supply voltage drops to an unsafe level (below the VBO

| Port Register Mnemonic     | Port Register Name                                              |

|----------------------------|-----------------------------------------------------------------|

| PxADDR                     | Port A-H Address Register<br>(Selects sub-registers)            |

| PxCTL                      | Port A-H Control Register<br>(Provides access to sub-registers) |

| PxIN                       | Port A-H Input Data Register                                    |

| PxOUT                      | Port A-H Output Data Register                                   |

| Port Sub-Register Mnemonic | Port Register Name                                              |

| PxDD                       | Data Direction                                                  |

| PxAF                       | Alternate Function                                              |

| PxOC                       | Output Control (Open-Drain)                                     |

| PxHDE                      | High Drive Enable                                               |

| PxSMRE                     | STOP Mode Recovery Source<br>Enable                             |

Table 12. GPIO Port Registers and Sub-Registers

## **Port A-H Address Registers**

The Port A-H Address registers select the GPIO Port functionality accessible through the Port A-H Control registers. The Port A-H Address and Control registers combine to provide access to all GPIO Port control (Table 13).

Table 13. Port A-H GPIO Address Registers (PxADDR)

| BITS  | 7 | 6          | 5            | 4          | 3            | 2            | 1  | 0 |  |  |

|-------|---|------------|--------------|------------|--------------|--------------|----|---|--|--|

| FIELD |   | PADDR[7:0] |              |            |              |              |    |   |  |  |

| RESET |   | 00H        |              |            |              |              |    |   |  |  |

| R/W   |   | R/W        |              |            |              |              |    |   |  |  |

| ADDR  |   | FĽ         | 00H, FD4H, I | FD8H, FDCH | , FE0H, FE4I | H, FE8H, FE0 | СН |   |  |  |

## Port A-H Output Data Register

The Port A-H Output Data register (Table 21) writes output data to the pins.

BITS 7 6 5 4 3 2 1 0 POUT7 POUT6 POUT5 POUT4 POUT3 POUT2 POUT1 POUT0 FIELD 0 0 0 0 0 0 0 0 RESET R/W R/W R/W R/W R/W R/W R/W R/W R/W FD3H, FD7H, FDBH, FDFH, FE3H, FE7H, FEBH, FEFH ADDR

## Table 21. Port A-H Output Data Register (PxOUT)

#### POUT[7:0]—Port Output Data

These bits contain the data to be driven out from the port pins. The values are only driven if the corresponding pin is configured as an output and the pin is not configured for alternate function operation.

0 =Drive a logical 0 (Low).

1= Drive a logical 1 (High). High value is not driven if the drain has been disabled by setting the corresponding Port Output Control register bit to 1.

## **Interrupt Request 2 Register**

The Interrupt Request 2 (IRQ2) register (Table 25) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 1 register to determine if any interrupt requests are pending.

Table 25. Interrupt Request 2 Register (IRQ2)

| BITS  | 7   | 6     | 5     | 4    | 3    | 2    | 1    | 0    |  |

|-------|-----|-------|-------|------|------|------|------|------|--|

| FIELD | T3I | U1RXI | UITXI | DMAI | PC3I | PC2I | PC1I | PC0I |  |

| RESET | 0   | 0     | 0     | 0    | 0    | 0    | 0    | 0    |  |

| R/W   | R/W | R/W   | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  |  |

| ADDR  |     | FC6H  |       |      |      |      |      |      |  |

T3I—Timer 3 Interrupt Request

- 0 = No interrupt request is pending for Timer 3.

- 1 = An interrupt request from Timer 3 is awaiting service.

U1RXI—UART 1 Receive Interrupt Request

- 0 = No interrupt request is pending for the UART1 receiver.

- 1 = An interrupt request from UART1 receiver is awaiting service.

- U1TXI-UART 1 Transmit Interrupt Request

- 0 = No interrupt request is pending for the UART 1 transmitter.

- 1 = An interrupt request from the UART 1 transmitter is awaiting service.

DMAI—DMA Interrupt Request

- 0 = No interrupt request is pending for the DMA.

- 1 = An interrupt request from the DMA is awaiting service.

PCxI—Port C Pin x Interrupt Request

- 0 = No interrupt request is pending for GPIO Port C pin *x*.

- 1 = An interrupt request from GPIO Port C pin x is awaiting service.

where *x* indicates the specific GPIO Port C pin number (0 through 3).

| BITS  | 7     | 6      | 5      | 4      | 3     | 2     | 1     | 0     |  |  |

|-------|-------|--------|--------|--------|-------|-------|-------|-------|--|--|

| FIELD | T3ENH | U1RENH | UITENH | DMAENH | C3ENH | C2ENH | C1ENH | C0ENH |  |  |

| RESET | 0     | 0      | 0      | 0      | 0     | 0     | 0     | 0     |  |  |

| R/W   | R/W   | R/W    | R/W    | R/W    | R/W   | R/W   | R/W   | R/W   |  |  |

| ADDR  |       | FC7H   |        |        |       |       |       |       |  |  |

Table 33. IRQ2 Enable High Bit Register (IRQ2ENH)

T3ENH—Timer 3 Interrupt Request Enable High Bit U1RENH—UART 1 Receive Interrupt Request Enable High Bit U1TENH—UART 1 Transmit Interrupt Request Enable High Bit DMAENH—DMA Interrupt Request Enable High Bit C3ENH—Port C3 Interrupt Request Enable High Bit C2ENH—Port C2 Interrupt Request Enable High Bit C1ENH—Port C1 Interrupt Request Enable High Bit C0ENH—Port C0 Interrupt Request Enable High Bit

Table 34. IRQ2 Enable Low Bit Register (IRQ2ENL)

| BITS  | 7     | 6      | 5      | 4      | 3     | 2     | 1     | 0     |

|-------|-------|--------|--------|--------|-------|-------|-------|-------|

| FIELD | T3ENL | U1RENL | UITENL | DMAENL | C3ENL | C2ENL | C1ENL | C0ENL |

| RESET | 0     | 0      | 0      | 0      | 0     | 0     | 0     | 0     |

| R/W   | R/W   | R/W    | R/W    | R/W    | R/W   | R/W   | R/W   | R/W   |

| ADDR  | FC8H  |        |        |        |       |       |       |       |

T3ENL—Timer 3 Interrupt Request Enable Low Bit

U1RENL-UART 1 Receive Interrupt Request Enable Low Bit

U1TENL-UART 1 Transmit Interrupt Request Enable Low Bit

DMAENL—DMA Interrupt Request Enable Low Bit

C3ENL—Port C3 Interrupt Request Enable Low Bit

C2ENL—Port C2 Interrupt Request Enable Low Bit

C1ENL—Port C1 Interrupt Request Enable Low Bit

COENL-Port CO Interrupt Request Enable Low Bit

## Interrupt Edge Select Register

The Interrupt Edge Select (IRQES) register (Table 35) determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port input pin. The

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control register to enable the timer.

- 7. Counting begins on the first appropriate transition of the Timer Input signal. No interrupt is generated by this first edge.

In Capture/Compare mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) = (Capture Value – Start Value) × Prescale System Clock Frequency (Hz)

## **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte register is read, the contents of the Timer Low Byte register are placed in a holding register. A subsequent read from the Timer Low Byte register returns the value in the holding register. This operation allows accurate reads of the full 16-bit timer count value while enabled. When the timers are not enabled, a read from the Timer Low Byte register returns the actual value in the counter.

## **Timer Output Signal Operation**

Timer Output is a GPIO Port pin alternate function. Generally, the Timer Output is toggled every time the counter is reloaded.

## **Timer Control Register Definitions**

Timers 0–2 are available in all packages. Timer 3 is available only in the 64-, 68- and 80-pin packages.

## Timer 0-3 High and Low Byte Registers

The Timer 0-3 High and Low Byte (TxH and TxL) registers (Tables 38 and 39) contain the current 16-bit timer count value. When the timer is enabled, a read from TxH causes the value in TxL to be stored in a temporary holding register. A read from TMRL always returns this temporary register when the timers are enabled. When the timer is disabled, reads from the TMRL reads the register directly.

Writing to the Timer High and Low Byte registers while the timer is enabled is not recommended. There are no temporary holding registers available for write operations, so simultaneous 16-bit writes are not possible. If either the Timer High or Low Byte registers are

## **Timer 0-3 Control Registers**

The Timer 0-3 Control (TxCTL) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode.

BITS 7 4 3 2 1 0 6 5 TEN TPOL PRES TMODE FIELD 0 0 0 0 0 0 0 0 RESET R/W R/W R/W R/W R/W R/W R/W R/W R/W F07H, F0FH, F17H, F1FH ADDR

Table 44. Timer 0-3 Control Register (TxCTL)

TEN-Timer Enable

0 = Timer is disabled.

1 = Timer enabled to count.

TPOL-Timer Input/Output Polarity

Operation of this bit is a function of the current operating mode of the timer.

#### **One-Shot mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **Continuous mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

## **Counter mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **PWM mode**

0 = Timer Output is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload.

1 = Timer Output is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload.

mode. Refer to the **Reset and Stop Mode Recovery** chapter for more information on STOP Mode Recovery.

If interrupts are enabled, following completion of the Stop Mode Recovery the eZ8 CPU responds to the interrupt request by fetching the Watch-Dog Timer interrupt vector and executing code from the vector address.

## WDT Reset in Normal Operation

If configured to generate a Reset when a time-out occurs, the Watch-Dog Timer forces the Z8F640x family device into the Short Reset state. The WDT status bit in the Watch-Dog Timer Control register is set to 1. Refer to the **Reset and Stop Mode Recovery** chapter for more information on Short Reset.

#### WDT Reset in Stop Mode

If configured to generate a Reset when a time-out occurs and the Z8F640x family device is in STOP mode, the Watch-Dog Timer initiates a Stop Mode Recovery. Both the WDT status bit and the STOP bit in the Watch-Dog Timer Control register are set to 1 following WDT time-out in STOP mode. Refer to the **Reset and Stop Mode Recovery** chapter for more information.

## Watch-Dog Timer Reload Unlock Sequence

Writing the unlock sequence to the Watch-Dog Timer Control register (WDTCTL) unlocks the three Watch-Dog Timer Reload Byte registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL register address produce no effect on the bits in the WDTCTL register. The locking mechanism prevents spurious writes to the Reload registers. The follow sequence is required to unlock the Watch-Dog Timer Reload Byte registers (WDTU, WDTH, and WDTL) for write access.

- 1. Write 55H to the Watch-Dog Timer Control register (WDTCTL)

- 2. Write AAH to the Watch-Dog Timer Control register (WDTCTL)

- 3. Write the Watch-Dog Timer Reload Upper Byte register (WDTU)

- 4. Write the Watch-Dog Timer Reload High Byte register (WDTH)

- 5. Write the Watch-Dog Timer Reload Low Byte register (WDTL)

All three Watch-Dog Timer Reload registers must be written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur, unless the sequence is restarted. The value in the Watch-Dog Timer Reload registers is loaded into the counter when the Watch-Dog Timer is first enabled and every time a WDT instruction is executed.

mitter and receiver sections, a Baud Rate (clock) Generator and a control unit. The transmitter and receiver sections use the same clock.

During an SPI transfer, data is sent and received simultaneously by both the Master and the Slave SPI devices. Separate signals are required for data and the serial clock. When an SPI transfer occurs, a multi-bit (typically 8-bit) character is shifted out one data pin and an multi-bit character is simultaneously shifted in on a second data pin. An 8-bit shift register in the Master and another 8-bit shift register in the Slave are connected as a circular buffer. The SPI shift register is single-buffered in the transmit and receive directions. New data to be transmitted cannot be written into the shift register until the previous transmission is complete and receive data (if valid) has been read.

## SPI Signals

The four basic SPI signals are:

- MISO (Master-In, Slave-Out)

- MOSI (Master-Out, Slave-In)

- SCK (SPI Serial Clock)

- $\overline{SS}$  (Slave Select)

The following paragraphs discuss these SPI signals. Each signal is described in both Master and Slave modes.

#### Master-In, Slave-Out

The Master-In, Slave-Out (MISO) pin is configured as an input in a Master device and as an output in a Slave device. It is one of the two lines that transfer serial data, with the most significant bit sent first. The MISO pin of a Slave device is placed in a high-impedance state if the Slave is not selected. When the SPI is not enabled, this signal is in a highimpedance state.

#### Master-Out, Slave-In

The Master-Out, Slave-In (MOSI) pin is configured as an output in a Master device and as an input in a Slave device. It is one of the two lines that transfer serial data, with the most significant bit sent first. When the SPI is not enabled, this signal is in a high-impedance state.

## Serial Clock

The Serial Clock (SCK) is used to synchronize data movement both in and out of the device through its MOSI and MISO pins. In Master mode, the SPI's Baud Rate Generator creates the serial clock. The Master drives the serial clock out its own SCK pin to the Slave's SCK pin. When the SPI is configured as a Slave, the SCK pin is an input and the clock signal from the Master synchronizes the data transfer between the Master and Slave devices. Slave devices ignore the SCK signal, unless the  $\overline{SS}$  pin is asserted.

102

The Master and Slave are each capable of exchanging a byte of data during a sequence of eight clock cycles. In both Master and Slave SPI devices, data is shifted on one edge of the SCK and is sampled on the opposite edge where data is stable. Edge polarity is determined by the SPI phase and polarity control.

## **Slave Select**

The active Low Slave Select  $(\overline{SS})$  input signal is used to select a Slave SPI device.  $\overline{SS}$  must be Low prior to all data communication to and from the Slave device.  $\overline{SS}$  must stay Low for the full duration of each character transferred. The  $\overline{SS}$  signal may stay Low during the transfer of multiple characters or may deassert between each character.

When the SPI on the Z8F640x family device is configured as the only Master in an SPI system, the  $\overline{SS}$  pin can be set as either an input or an output. For communication between the Z8F640x family device SPI Master and external Slave devices, the  $\overline{SS}$  signal, as an output, can assert the  $\overline{SS}$  input pin on one of the Slave devices. Other GPIO output pins can also be employed to select external SPI Slave devices.

When the SPI on the Z8F640x family device is configured as one Master in a multi-master SPI system, the  $\overline{SS}$  pin on the should be set as an input. The  $\overline{SS}$  input signal on the Master must be High. If the  $\overline{SS}$  signal goes Low (indicating another Master is driving the SPI bus), a Mode Fault error flag is set in the SPI Status register.

## **SPI Clock Phase and Polarity Control**

The SPI supports four combinations of serial clock phase and polarity using two bits in the SPI Control register. The clock polarity bit, CLKPOL, selects an active high or active low clock and has no effect on the transfer format. Table 59 lists the SPI Clock Phase and Polarity Operation parameters. The clock phase bit, PHASE, selects one of two fundamentally different transfer formats. For proper data transmission, the clock phase and polarity must be identical for the SPI Master and the SPI Slave. The Master always places data on the MOSI line a half-cycle before the clock edge (SCK signal), in order for the Slave to latch the data.

| PHASE | CLKPOL | SCK<br>Transmit<br>Edge | SCK<br>Receive<br>Edge | SCK<br>Idle<br>State |

|-------|--------|-------------------------|------------------------|----------------------|

| 0     | 0      | Falling                 | Rising                 | Low                  |

| 0     | 1      | Rising                  | Falling                | High                 |

| 1     | 0      | Rising                  | Falling                | Low                  |

| 1     | 1      | Falling                 | Rising                 | High                 |

| Table 59. SPI Clock Phase  | (PHASE)      | and Clock Polarit | v (CLKPOL) Operation   |

|----------------------------|--------------|-------------------|------------------------|

| Tuble 57. BIT Clock I hase | (1 111 10 1) | and Clock I blain | y (Chill Oh) Operation |

SPIEN—SPI Enable 0 = SPI disabled. 1 = SPI enabled.

## **SPI Status Register**

The SPI Status register indicates the current state of the SPI.

| Table 62 | SPI | Status | Register | (SPISTAT) |

|----------|-----|--------|----------|-----------|

|----------|-----|--------|----------|-----------|

| BITS         | 7             | 6               | 5                                                       | 4        | 3 | 2 | 1    | 0    |  |  |  |  |

|--------------|---------------|-----------------|---------------------------------------------------------|----------|---|---|------|------|--|--|--|--|

| FIELD        | IRQ           | OVR             | COL                                                     | Reserved |   |   | TXST | SLAS |  |  |  |  |

| RESET        | 0             | 0               | 0                                                       | 0        |   |   | 0    | 1    |  |  |  |  |

| R/W          | R/W*          | R/W*            | R/W*                                                    |          | R |   |      | R    |  |  |  |  |

| ADDR         | R F62H        |                 |                                                         |          |   |   |      |      |  |  |  |  |

| $R/W^* = Re$ | ead access. W | rite a 1 to cle | $R/W^* = Read access.$ Write a 1 to clear the bit to 0. |          |   |   |      |      |  |  |  |  |

IRQ—Interrupt Request

0 =No SPI interrupt request pending.

1 =SPI interrupt request is pending.

OVR-Overrun

0 = An overrun error has not occurred.

1 = An overrun error has been detected.

COL-Collision

0 = A multi-master collision (mode fault) has not occurred.

1 = A multi-master collision (mode fault) has been detected.

Reserved

These bits are reserved and must be 0.

TXST—Transmit Status

0 = No data transmission currently in progress.

1 =Data transmission currently in progress.

SLAS—Slave Select

If SPI enabled as a Slave,

$0 = \overline{SS}$  input pin is asserted (Low)

$1 = \overline{SS}$  input is not asserted (High).

If SPI enabled as a Master, this bit is not applicable.

## SPI Baud Rate High and Low Byte Registers

The SPI Baud Rate High and Low Byte registers combine to form a 16-bit reload value, BRG[15:0], for the SPI Baud Rate Generator. The reload value must be greater than or equal to 0002H for proper SPI operation (maximum baud rate is system clock frequency divided by 4). The SPI baud rate is calculated using the following equation:

SPI Baud Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{2 \times \text{BRG}[15:0]}$

| BITS  | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| FIELD |     |     |     | BF  | RH  |     |     |     |

| RESET | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  |     |     |     | F6  | 6H  |     |     |     |

Table 64. SPI Baud Rate High Byte Register (SPIBRH)

#### BRH = SPI Baud Rate High Byte

Most significant byte, BRG[15:8], of the SPI Baud Rate Generator's reload value.

#### Table 65. SPI Baud Rate Low Byte Register (SPIBRL)

| BITS  | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|------|-----|-----|-----|-----|-----|-----|

| FIELD |     |      |     | BI  | RL  |     |     |     |

| RESET | 1   | 1    | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W   | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/w |

| ADDR  |     | F67H |     |     |     |     |     |     |

BRL = SPI Baud Rate Low Byte

Least significant byte, BRG[7:0], of the SPI Baud Rate Generator's reload value.

#### START-Send Start Condition

This bit sends the Start condition. Once asserted, it is cleared by the I<sup>2</sup>C Controller after it sends the START condition or by deasserting the IEN bit. After this bit is set, the Start condition is sent if there is data in the I<sup>2</sup>C Data or I<sup>2</sup>C Shift register. If there is no data in one of these registers, the I<sup>2</sup>C Controller waits until data is loaded. If this bit is set while the I<sup>2</sup>C Controller is shifting out data, it generates a START condition after the byte shifts and the acknowledge phase completed. If the STOP bit is also set, it also waits until the STOP condition is sent before the START condition. If this bit is 1, it cannot be cleared to 0 by writing to the register. This bit clears when the I<sup>2</sup>C is disabled.

#### STOP-Send Stop Condition

This bit causes the  $I^2C$  Controller to issue a Stop condition after the byte in the  $I^2C$  Shift register has completed transmission or after a byte has been received in a receive operation. Once set, this bit is reset by the  $I^2C$  Controller after a Stop condition has been sent or by deasserting the IEN bit. If this bit is 1, it cannot be cleared to 0 by writing to the register. This bit clears when the  $I^2C$  is disabled.

#### BIRQ-Baud Rate Generator Interrupt Request

This bit causes an interrupt to occur every time the baud rate generator counts down to zero. This bit allows the  $I^2C$  Controller to be used as an additional counter when it is not being used elsewhere. This bit must only be set when the  $I^2C$  Controller is disabled.

#### TXI-Enable TDRE interrupts

This bit enables interrupts when the I<sup>2</sup>C Data register is empty on the I<sup>2</sup>C Controller.

#### NAK—Send NAK

This bit sends a Not Acknowledge condition after the next byte of data has been read from the  $I^2C$  slave. Once asserted, it is deasserted after a Not Acknowledge is sent or the IEN bit is deasserted.

#### FLUSH-Flush Data

Setting this bit to 1 clears the I<sup>2</sup>C Data register and sets the TDRE bit to 1. This bit allows flushing of the I<sup>2</sup>C Data register when an NAK is received after the data has been sent to the I<sup>2</sup>C Data register. Reading this bit always returns 0.

## FILTEN—I<sup>2</sup>C Signal Filter Enable

Setting this bit to 1 enables low-pass digital filters on the SDA and SCL input signals. These filters reject any input pulse with periods less than a full system clock cycle. The filters introduce a 3-system clock cycle latency on the inputs.

122

ZILOG

# **Direct Memory Access Controller**

## **Overview**

The Z8F640x family device's Direct Memory Access (DMA) Controller provides three independent Direct Memory Access channels. Two of the channels (DMA0 and DMA1) transfer data between the on-chip peripherals and the Register File. The third channel (DMA\_ADC) controls the Analog-to-Digital Converter (ADC) operation and transfers the Single-Shot mode ADC output data to the Register File.

## Operation

## **DMA0 and DMA1 Operation**

DMA0 and DMA1, referred to collectively as DMAx, transfer data either from the on-chip peripheral control registers to the Register File, or from the Register File to the on-chip peripheral control registers. The sequence of operations in a DMAx data transfer is:

- 1. DMAx trigger source requests a DMA data transfer.

- 2. DMAx requests control of the system bus (address and data) from the eZ8 CPU.

- 3. After the eZ8 CPU acknowledges the bus request, DMAx transfers either a single byte or a two-byte word (depending upon configuration) and then returns system bus control back to the eZ8 CPU.

- 4. If Current Address equals End Address:

- DMAx reloads the original Start Address

- If configured to generate an interrupt, DMA*x* sends an interrupt request to the Interrupt Controller

- If configured for single-pass operation, DMAx resets the DEN bit in the DMAx Control register to 0 and the DMA is disabled.

If Current Address does not equal End Address, the Current Address increments by 1 (single-byte transfer) or 2 (two-byte word transfer).

## Z8F640x/Z8F480x/Z8F320x/Z8F240x/Z8F160x Z8 Encore!®

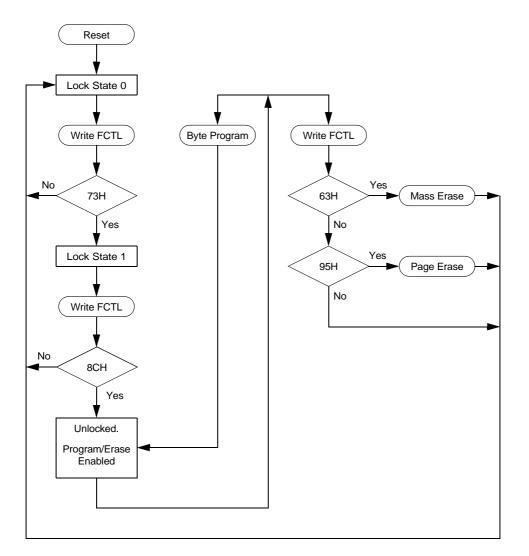

Figure 85. Flash Controller Operation Flow Chart

- Power-on reset

- Voltage Brownout reset

- Asserting the  $\overline{\text{RESET}}$  pin Low to initiate a Reset.

- Driving the DBG pin Low while the Z8F640x family device is in Stop mode initiates a System Reset.

## **OCD Data Format**

The OCD interface uses the asynchronous data format defined for RS-232. Each character is transmitted as 1 Start bit, 8 data bits (least-significant bit first), and 1.5 Stop bits (Figure 89)

| START         D0         D1         D2         D3         D4         D5         D6         D7 | STOP |

|-----------------------------------------------------------------------------------------------|------|

|-----------------------------------------------------------------------------------------------|------|

#### Figure 89. OCD Data Format

## **OCD Auto-Baud Detector/Generator**

To run over a range of baud rates (data bits per second) with various system clock frequencies, the On-Chip Debugger has an Auto-Baud Detector/Generator. After a reset, the OCD is idle until it receives data. The OCD requires that the first character sent from the host is the character 80H. The character 80H has eight continuous bits Low (one Start bit plus 7 data bits). The Auto-Baud Detector measures this period and sets the OCD Baud Rate Generator accordingly.

The Auto-Baud Detector/Generator is clocked by the Z8F640x family device system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation, the maximum recommended baud rate is the system clock frequency divided by 8. The theoretical maximum baud rate is the system clock frequency divided by 4. This theoretical maximum is possible for low noise designs with clean signals. Table 92 lists minimum and recommended maximum baud rates for sample crystal frequencies.

| System Clock Frequency<br>(MHz) | Recommended Maximum Baud Rate<br>(kbits/s) | Minimum Baud Rate<br>(kbits/s) |

|---------------------------------|--------------------------------------------|--------------------------------|

| 20.0                            | 2500                                       | 39.1                           |

| 1.0                             | 125.0                                      | 1.96                           |

| 0.032768 (32KHz)                | 4.096                                      | 0.064                          |

#### Table 92. OCD Baud-Rate Limits

| Table 118. Arithmetic Instructions (Continued) |

|------------------------------------------------|

|------------------------------------------------|

| Mnemonic | Operands | Instruction                                   |

|----------|----------|-----------------------------------------------|

| SBC      | dst, src | Subtract with Carry                           |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |

| SUB      | dst, src | Subtract                                      |

| SUBX     | dst, src | Subtract using Extended Addressing            |

**Table 119. Bit Manipulation Instructions**

| Mnemonic | Operands    | Instruction                                          |

|----------|-------------|------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                            |

| BIT      | p, bit, dst | Bit Set or Clear                                     |

| BSET     | bit, dst    | Bit Set                                              |

| BSWAP    | dst         | Bit Swap                                             |

| CCF      | _           | Complement Carry Flag                                |

| RCF      | _           | Reset Carry Flag                                     |

| SCF      | _           | Set Carry Flag                                       |

| TCM      | dst, src    | Test Complement Under Mask                           |

| TCMX     | dst, src    | Test Complement Under Mask using Extended Addressing |

| ТМ       | dst, src    | Test Under Mask                                      |

| TMX      | dst, src    | Test Under Mask using Extended Addressing            |

**Table 120. Block Transfer Instructions**

| Mnemonic | Operands | Instruction                                                            |

|----------|----------|------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-Increment Addresses      |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-Increment<br>Addresses |

## Z8F640x/Z8F480x/Z8F320x/Z8F240x/Z8F160x Z8 Encore!®

extended addressing register 184 external pin reset 29 eZ8 CPU features 3 eZ8 CPU instruction classes 187 eZ8 CPU instruction notation 183 eZ8 CPU instruction set 182 eZ8 CPU instruction summary 191

## F

FCTL register 144 features, Z8 Encore!<sup>®</sup> 1 first opcode map 204 FLAGS 185 flags register 185 flash controller 4 option bit address space 148 option bit configuration - reset 148 program memory address 0000H 149 program memory address 0001H 150 flash memory 138 arrangement 139 byte programming 142 code protection 141 configurations 138 control register definitions 144 controller bypass 143 electrical characteristics and timing 173 flash control register 144 flash option bits 142 flash status register 145 flow chart 140 frequency high and low byte registers 147 mass erase 143 operation 139 operation timing 141 page erase 143 page select register 146 FPS register 146 FSTAT register 145

# G

gated mode 71 general-purpose I/O 33 GPIO 4, 33 alternate functions 34 architecture 34 control register definitions 36 input data sample timing 176 interrupts 36 port A-H address registers 37 port A-H alternate function sub-registers 39 port A-H control registers 38 port A-H data direction sub-registers 39 port A-H high drive enable sub-registers 41 port A-H input data registers 42 port A-H output control sub-registers 40 port A-H output data registers 43 port A-H stop mode recovery sub-registers 41 port availability by device 33 port input timing 176 port output timing 177

## H

H 185 HALT 189 HALT mode 31, 189 hexadecimal number prefix/suffix 185

# I

I<sup>2</sup>C 4 10-bit address read transaction 116 10-bit address transaction 114 10-bit addressed slave data transfer format 114 10-bit receive data format 116 7-bit address transaction 112 7-bit address, reading a transaction 115 7-bit addressed slave data transfer format 113 7-bit receive data transfer format 115 baud high and low byte registers 121 C status register 118 control register definitions 118