Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 31                                                        |

| Program Memory Size        | 16KB (16K × 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 2K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 44-LCC (J-Lead)                                           |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1601vn020ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Manual Objectives

This Product Specification provides detailed operating information for the Z8F640x, Z8F480x, Z8F320x, Z8F240x, and Z8F160x devices within the Z8 Encore!<sup>™</sup> Microcontroller (MCU) family of products. Within this document, the Z8F640x, Z8F480x, Z8F320x, Z8F240x, and Z8F160x are referred to collectively as Z8 Encore!<sup>™</sup> or the Z8F640x family unless specifically stated otherwise.

#### **About This Manual**

ZiLOG recommends that the user read and understand everything in this manual before setting up and using the product. However, we recognize that there are different styles of learning. Therefore, we have designed this Product Specification to be used either as a *how to* procedural manual or a reference guide to important data.

#### **Intended Audience**

This document is written for ZiLOG customers who are experienced at working with microcontrollers, integrated circuits, or printed circuit assemblies.

#### **Manual Conventions**

The following assumptions and conventions are adopted to provide clarity and ease of use:

#### **Courier Typeface**

Commands, code lines and fragments, bits, equations, hexadecimal addresses, and various executable items are distinguished from general text by the use of the Courier typeface. Where the use of the font is not indicated, as in the Index, the name of the entity is presented in upper case.

• Example: FLAGS[1] is smrf.

#### **Hexadecimal Values**

Hexadecimal values are designated by uppercase *H* suffix and appear in the Courier typeface.

• Example: R1 is set to F8H.

#### Brackets

The square brackets, [], indicate a register or bus.

• Example: for the register R1[7:0], R1 is an 8-bit register, R1[7] is the most significant bit, and R1[0] is the least significant bit.

#### Braces

The curly braces, { }, indicate a single register or bus created by concatenating some combination of smaller registers, buses, or individual bits.

• Example: the 12-bit register address {0H, RP[7:4], R1[3:0]} is composed of a 4-bit hexadecimal value (0H) and two 4-bit register values taken from the Register Pointer (RP) and Working Register R1. 0H is the most significant nibble (4-bit value) of the 12-bit register, and R1[3:0] is the least significant nibble of the 12-bit register.

#### Parentheses

The parentheses, ( ), indicate an indirect register address lookup.

• Example: (R1) is the memory location referenced by the address contained in the Working Register R1.

#### **Parentheses/Bracket Combinations**

The parentheses, (), indicate an indirect register address lookup and the square brackets, [], indicate a register or bus.

• *Example:* assume PC[15:0] contains the value 1234h. (PC[15:0]) then refers to the contents of the memory location at address 1234h.

#### Use of the Words Set, Reset and Clear

The word *set* implies that a register bit or a condition contains a logical 1. The words re*set* or *clear* imply that a register bit or a condition contains a logical 0. When either of these terms is followed by a number, the word *logical* may not be included; however, it is implied.

#### Notation for Bits and Similar Registers

A field of bits within a register is designated as: Register[*n*:*n*].

• Example: ADDR[15:0] refers to bits 15 through bit 0 of the Address.

#### Use of the Terms LSB, MSB, Isb, and msb

In this document, the terms *LSB* and *MSB*, when appearing in upper case, mean *least significant byte* and *most significant byte*, respectively. The lowercase forms, *lsb* and *msb*, mean *least significant bit* and *most significant bit*, respectively.

#### **Use of Initial Uppercase Letters**

Initial uppercase letters designate settings, modes, and conditions in general text.

- Example 1: Stop mode.

- Example 2: The receiver forces the SCL line to Low.

- The Master can generate a Stop condition to abort the transfer.

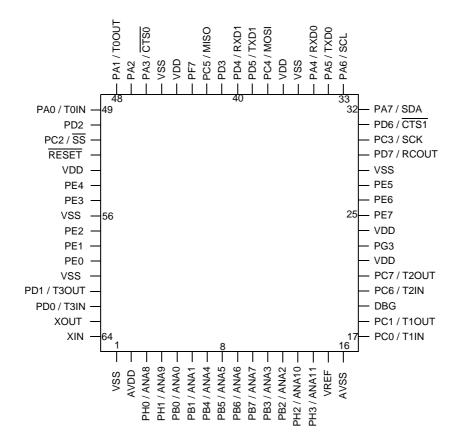

Figure 59. Z8Fxx02 in 64-Pin Low-Profile Quad Flat Package (LQFP)

15

| Signal Mnemonic | I/O | Description                                          |

|-----------------|-----|------------------------------------------------------|

| Reset           |     |                                                      |

| RESET           | Ι   | RESET. Generates a Reset when asserted (driven Low). |

| Power Supply    |     |                                                      |

| VDD             | Ι   | Power Supply.                                        |

| AVDD            | Ι   | Analog Power Supply.                                 |

| VSS             | Ι   | Ground.                                              |

| AVSS            | Ι   | Analog Ground.                                       |

#### Table 2. Signal Descriptions (Continued)

## **Pin Characteristics**

Table 3 provides detailed information on the characteristics for each pin available on the Z8F640x family products. Data in Table 3 is sorted alphabetically by the pin symbol mnemonic.

Table 3. Pin Characteristics of the Z8F640x family

| N/A<br>N/A<br>I/O<br>N/A | N/A<br>N/A<br>I   | N/A<br>N/A<br>N/A            | N/A<br>N/A                                    | No<br>No                                 | No<br>No                                         | N/A<br>N/A                                    |

|--------------------------|-------------------|------------------------------|-----------------------------------------------|------------------------------------------|--------------------------------------------------|-----------------------------------------------|

| I/O                      | Ι                 |                              |                                               | No                                       | No                                               | N/A                                           |

|                          |                   | N/A                          |                                               |                                          |                                                  | 1 1/ 2 1                                      |

| N/A                      |                   |                              | Yes                                           | No                                       | Yes                                              | Yes                                           |

|                          | N/A               | N/A                          | N/A                                           | No                                       | No                                               | N/A                                           |

| I/O                      | Ι                 | N/A                          | Yes                                           | No                                       | Yes                                              | Yes,<br>Programmable                          |

| I/O                      | Ι                 | N/A                          | Yes                                           | No                                       | Yes                                              | Yes,<br>Programmable                          |

| I/O                      | Ι                 | N/A                          | Yes                                           | No                                       | Yes                                              | Yes,<br>Programmable                          |

| I/O                      | Ι                 | N/A                          | Yes                                           | No                                       | Yes                                              | Yes,<br>Programmable                          |

| I/O                      | Ι                 | N/A                          | Yes                                           | No                                       | Yes                                              | Yes,<br>Programmable                          |

| e                        | I/O<br>I/O<br>I/O | VO I<br>VO I<br>VO I<br>VO I | I/O I N/A   I/O I N/A   I/O I N/A   I/O I N/A | I/OIN/AYesI/OIN/AYesI/OIN/AYesI/OIN/AYes | I/OIN/AYesNoI/OIN/AYesNoI/OIN/AYesNoI/OIN/AYesNo | I/OIN/AYesNoYesI/OIN/AYesNoYesI/OIN/AYesNoYes |

## Interrupt Controller

## Overview

The interrupt controller on the Z8F640x family device prioritizes the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of the interrupt controller on the Z8F640x family device include the following:

- 24 unique interrupt vectors:

- 12 GPIO port pin interrupt sources

- 12 on-chip peripheral interrupt sources

- Flexible GPIO interrupts

- 8 selectable rising and falling edge GPIO interrupts

- 4 dual-edge interrupts

- 3 levels of individually programmable interrupt priority

- Watch-Dog Timer can be configured to generate an interrupt

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an interrupt service routine (ISR). Usually this interrupt service routine is involved with the exchange of data, status information, or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the interrupt control has no effect on operation. Refer to the eZ8 CPU User Manual for more information regarding interrupt servicing by the eZ8 CPU. The eZ8 CPU User Manual is available for download at www.zilog.com.

#### Interrupt Vector Listing

Table 22 lists all of the interrupts available on the Z8F640x family device in order of priority. The interrupt vector is stored with the most significant byte (MSB) at the even Program Memory address and the least significant byte (LSB) at the following odd Program Memory address.

| Priority | Program Memory<br>Vector Address | Interrupt Source                                 | Interrupt Assertion Type |

|----------|----------------------------------|--------------------------------------------------|--------------------------|

| Highest  | 0002h                            | Reset (not an interrupt)                         | Not applicable           |

|          | 0004h                            | Watch-Dog Timer                                  | Continuous assertion     |

|          | 0006h                            | Illegal Instruction Trap (not an interrupt)      | Not applicable           |

|          | 0008h                            | Timer 2                                          | Single assertion (pulse) |

|          | 000Ah                            | Timer 1                                          | Single assertion (pulse) |

|          | 000Ch                            | Timer 0                                          | Single assertion (pulse) |

|          | 000Eh                            | UART 0 receiver                                  | Continuous assertion     |

|          | 0010h                            | UART 0 transmitter                               | Continuous assertion     |

|          | 0012h                            | I <sup>2</sup> C                                 | Continuous assertion     |

|          | 0014h                            | SPI                                              | Continuous assertion     |

|          | 0016h                            | ADC                                              | Single assertion (pulse) |

|          | 0018h                            | Port A7 or Port D7, rising or falling input edge | Single assertion (pulse) |

|          | 001Ah                            | Port A6 or Port D6, rising or falling input edge | Single assertion (pulse) |

|          | 001Ch                            | Port A5 or Port D5, rising or falling input edge | Single assertion (pulse) |

|          | 001Eh                            | Port A4 or Port D4, rising or falling input edge | Single assertion (pulse) |

|          | 0020h                            | Port A3 or Port D3, rising or falling input edge | Single assertion (pulse) |

|          | 0022h                            | Port A2 or Port D2, rising or falling input edge | Single assertion (pulse) |

|          | 0024h                            | Port A1 or Port D1, rising or falling input edge | Single assertion (pulse) |

|          | 0026h                            | Port A0 or Port D0, rising or falling input edge | Single assertion (pulse) |

|          | 0028h                            | Timer 3 (not available in 40/44-pin packages)    | Single assertion (pulse) |

|          | 002Ah                            | UART 1 receiver                                  | Continuous assertion     |

|          | 002Ch                            | UART 1 transmitter                               | Continuous assertion     |

|          | 002Eh                            | DMA                                              | Single assertion (pulse) |

|          | 0030h                            | Port C3, both input edges                        | Single assertion (pulse) |

|          | 0032h                            | Port C2, both input edges                        | Single assertion (pulse) |

|          | 0034h                            | Port C1, both input edges                        | Single assertion (pulse) |

| Lowest   | 0036h                            | Port C0, both input edges                        | Single assertion (pulse) |

|          |                                  |                                                  |                          |

#### Table 22. Interrupt Vectors in Order of Priority

53

| BITS  | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|-------|---------|---------|---------|---------|---------|---------|---------|---------|

| FIELD | PAD7ENH | PAD6ENH | PAD5ENH | PAD4ENH | PAD3ENH | PAD2ENH | PAD1ENH | PAD0ENH |

| RESET | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| R/W   | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |

| ADDR  |         | FC4H    |         |         |         |         |         |         |

#### Table 30. IRQ1 Enable High Bit Register (IRQ1ENH)

PAD*x*ENH—Port A or Port D Bit[*x*] Interrupt Request Enable High Bit Refer to the Interrupt Port Select register for selection of either Port A or Port D as the interrupt source.

Table 31. IRQ1 Enable Low Bit Register (IRQ1ENL)

| BITS  | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|-------|---------|---------|---------|---------|---------|---------|---------|---------|

| FIELD | PAD7ENL | PAD6ENL | PAD5ENL | PAD4ENL | PAD3ENL | PAD2ENL | PAD1ENL | PAD0ENL |

| RESET | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| R/W   | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |

| ADDR  |         | FC5H    |         |         |         |         |         |         |

PADxENL—Port A or Port D Bit[x] Interrupt Request Enable Low Bit Refer to the Interrupt Port Select register for selection of either Port A or Port D as the interrupt source.

## **IRQ2 Enable High and Low Bit Registers**

The IRQ2 Enable High and Low Bit registers (Tables 33 and 34) form a priority encoded enabling for interrupts in the Interrupt Request 2 register. Priority is generated by setting bits in each register. Table 32 describes the priority control for IRQ2.

Table 32. IRQ2 Enable and Priority Encoding

| IRQ2ENH[x] | IRQ2ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

| 1          | 1          | Level 3  | High        |

where *x* indicates the register bits from 0 through 7.

Interrupt Port Select register selects between Port A and Port D for the individual interrupts.

| BITS  | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------|------|------|------|------|------|------|------|------|

| FIELD | IES7 | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |

| RESET | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| ADDR  |      | FCDH |      |      |      |      |      |      |

Table 35. Interrupt Edge Select Register (IRQES)

IES*x*—Interrupt Edge Select *x*

where *x* indicates the specific GPIO Port pin number (0 through 7). The pulse width should be greater than 1 system clock to guarantee capture of the edge triggered interrupt. 0 = An interrupt request is generated on the falling edge of the PA*x*/PD*x* input. 1 = An interrupt request is generated on the rising edge of the PA*x*/PD*x* input.

## **Interrupt Port Select Register**

The Port Select (IRQPS) register (Table 36) determines the port pin that generates the PAx/PDx interrupts. This register allows either Port A or Port D pins to be used as interrupts. The Interrupt Edge Select register controls the active interrupt edge.

| BITS  | 7     | 6                         | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|---------------------------|-------|-------|-------|-------|-------|-------|

| FIELD | PAD7S | PAD6S                     | PAD5S | PAD4S | PAD3S | PAD2S | PAD1S | PAD0S |

| RESET | 0     | 0                         | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W   | R/W   | V R/W R/W R/W R/W R/W R/W |       |       |       |       |       |       |

| ADDR  |       | FCEH                      |       |       |       |       |       |       |

Table 36. Interrupt Port Select Register (IRQPS)

PADxS—PAx/PDx Selection

0 = PAx is used for the interrupt for PAx/PDx interrupt request.

1 = PDx is used for the interrupt for PAx/PDx interrupt request.

where *x* indicates the specific GPIO Port pin number (0 through 7).

- Disable the timer

- Configure the timer for PWM mode.

- Set the prescale value.

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the Timer Reload High and Low Byte registers to set the Reload value (PWM period). The Reload value must be greater than the PWM value.

- 5. If desired, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control register to enable the timer and initiate counting.

The PWM period is given by the following equation:

**PWM Period** (s) = Reload Value × Prescale System Clock Frequency (Hz)

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, the One-Shot mode equation must be used to determine the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is given by:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is given by:

PWM Output High Time Ratio (%) =

$$\frac{PWM Value}{Reload Value} \times 100$$

#### **Capture Mode**

In Capture mode, the current timer count value is recorded when the desired external Timer Input transition occurs. The Capture count value is written to the Timer PWM High and Low Byte Registers. The timer input is the system clock. The TPOL bit in the Timer Control register determines if the Capture occurs on a rising edge or a falling edge of the

written during counting, the 8-bit written value is placed in the counter (High or Low Byte) at the next clock edge. The counter continues counting from the new value.

BITS 7 6 5 4 3 2 1 0 TH FIELD 0 0 0 0 0 0 0 0 RESET R/W R/W R/W R/W R/W R/W R/W R/W R/W F00H, F08H, F10H, F18H ADDR

Table 38. Timer 0-3 High Byte Register (TxH)

Table 39>. Timer 0-3 Low Byte Register (TxL)

| BITS  | 7   | 6                                           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-----|---------------------------------------------|---|---|---|---|---|---|--|

| FIELD |     | TL                                          |   |   |   |   |   |   |  |

| RESET | 0   | 0 0 0 0 0 0 1                               |   |   |   |   |   |   |  |

| R/W   | R/W | R/W     R/W     R/W     R/W     R/W     R/W |   |   |   |   |   |   |  |

| ADDR  |     | F01H, F09H, F11H, F19H                      |   |   |   |   |   |   |  |

TH and TL—Timer High and Low Bytes

These 2 bytes, {TMRH[7:0], TMRL[7:0]}, contain the current 16-bit timer count value.

## **Timer Reload High and Low Byte Registers**

The Timer 0-3 Reload High and Low Byte (TxRH and TxRL) registers (Tables 40 and 41) store a 16-bit reload value, {TRH[7:0], TRL[7:0]}. Values written to the Timer Reload High Byte register are stored in a temporary holding register. When a write to the Timer Reload Low Byte register occurs, the temporary holding register value is written to the Timer High Byte register. This operation allows simultaneous updates of the 16-bit Timer Reload value.

In Compare mode, the Timer Reload High and Low Byte registers store the 16-bit Compare value.

In single-byte DMA transactions to the Timer Reload High Byte register, the temporary holding register is bypassed and the value is written directly to the register. If the DMA is

#### **Capture mode**

0 = Count is captured on the rising edge of the Timer Input signal.

1 = Count is captured on the falling edge of the Timer Input signal.

#### **Compare mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### Gated mode

0 = Timer counts when the Timer Input signal is High (1) and interrupts are generated on the falling edge of the Timer Input.

1 = Timer counts when the Timer Input signal is Low (0) and interrupts are generated on the rising edge of the Timer Input.

#### Capture/Compare mode

0 = Counting is started on the first rising edge of the Timer Input signal. The current count is captured on subsequent rising edges of the Timer Input signal.

1 = Counting is started on the first falling edge of the Timer Input signal. The current count is captured on subsequent falling edges of the Timer Input signal.

#### PRES—Prescale value.

The timer input clock is divided by 2<sup>PRES</sup>, where PRES can be set from 0 to 7. The prescaler is reset each time the Timer is disabled. This insures proper clock division each time the Timer is restarted.

- 000 = Divide by 1

- 001 = Divide by 2

- 010 = Divide by 4

- 011 = Divide by 8

- 100 = Divide by 16

- 101 = Divide by 32

- 110 = Divide by 64

- 111 = Divide by 128

TMODE—Timer mode

- 000 =One-Shot mode

- 001 = Continuous mode

- 010 =Counter mode

- 011 = PWM mode

- 100 = Capture mode

- 101 = Compare mode

- 110 = Gated mode

- 111 = Capture/Compare mode

# Infrared Encoder/Decoder

## Overview

The Z8F640x family products contain two fully-functional, high-performance UART to Infrared Encoder/Decoders (Endecs). Each Infrared Endec is integrated with an on-chip UART to allow easy communication between the Z8F640x family device and IrDA Physical Layer Specification Version 1.3-compliant infrared transceivers. Infrared communication provides secure, reliable, low-cost, point-to-point communication between PCs, PDAs, cell phones, printers and other infrared enabled devices.

## Architecture

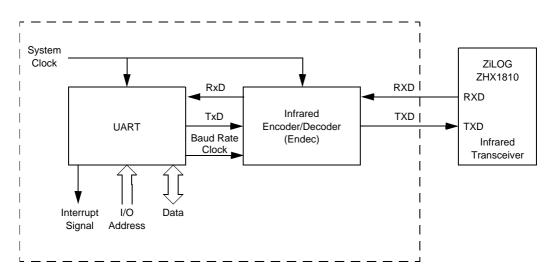

Figure 71 illustrates the architecture of the Infrared Endec.

Figure 71. Infrared Data Communication System Block Diagram

#### **Error Detection**

The SPI contains error detection logic to support SPI communication protocols and recognize when communication errors have occurred. The SPI Status register indicates when a data transmission error has been detected.

#### **Overrun (Write Collision)**

An overrun error (write collision) indicates a write to the SPI Data register was attempted while a data transfer is in progress. An overrun sets the OVR bit in the SPI Status register to 1. Writing a 1 to OVR clears this error flag.

#### Mode Fault (Multi-Master Collision)

A mode fault indicates when more than one Master is trying to communicate at the same time (a multi-master collision). The mode fault is detected when the enabled Master's  $\overline{SS}$  pin is asserted. A mode fault sets the COL bit in the SPI Status register to 1. Writing a 1 to COL clears this error flag.

#### **SPI Interrupts**

When SPI interrupts are enabled, the SPI generates an interrupt after data transmission. The SPI in Master mode generates an interrupt after a character has been sent. A character can be defined to be 1 through 8 bits by the NUMBITS field in the SPI Mode register. The SPI in Slave mode generates an interrupt when the  $\overline{SS}$  signal deasserts to indicate completion of the data transfer. Writing a 1 to the IRQ bit in the SPI Status Register clears the pending interrupt request. If the SPI is disabled, an SPI interrupt can be generated by a Baud Rate Generator time-out.

#### **SPI Baud Rate Generator**

In SPI Master mode, the Baud Rate Generator creates a lower frequency serial clock (SCK) for data transmission synchronization between the Master and the external Slave. The input to the Baud Rate Generator is the system clock. The SPI Baud Rate High and Low Byte registers combine to form a 16-bit reload value, BRG[15:0], for the SPI Baud Rate Generator. The reload value must be greater than or equal to 0002H for SPI operation (maximum baud rate is system clock frequency divided by 4). The SPI baud rate is calculated using the following equation:

# SPI Baud Rate (bits/s) = $\frac{\text{System Clock Frequency (Hz)}}{2 \times \text{BRG}[15:0]}$

When the SPI is disabled, the Baud Rate Generator can function as a basic 16-bit timer with interrupt on time-out. To configure the Baud Rate Generator as a timer with interrupt on time-out, complete the following procedure:

SPIEN—SPI Enable 0 = SPI disabled. 1 = SPI enabled.

#### **SPI Status Register**

The SPI Status register indicates the current state of the SPI.

| Table 62 | SPI | Status | Register | (SPISTAT) |

|----------|-----|--------|----------|-----------|

|----------|-----|--------|----------|-----------|

| BITS         | 7                                                    | 6    | 5    | 4        | 3 | 1 | 0    |      |  |

|--------------|------------------------------------------------------|------|------|----------|---|---|------|------|--|

| FIELD        | IRQ                                                  | OVR  | COL  | Reserved |   |   | TXST | SLAS |  |

| RESET        | 0                                                    | 0    | 0    |          | 0 | 0 | 1    |      |  |

| R/W          | R/W*                                                 | R/W* | R/W* |          | R |   | R    | R    |  |

| ADDR         | ADDR F62H                                            |      |      |          |   |   |      |      |  |

| $R/W^* = Re$ | R/W* = Read access. Write a 1 to clear the bit to 0. |      |      |          |   |   |      |      |  |

IRQ—Interrupt Request

0 =No SPI interrupt request pending.

1 =SPI interrupt request is pending.

OVR-Overrun

0 = An overrun error has not occurred.

1 = An overrun error has been detected.

COL-Collision

0 = A multi-master collision (mode fault) has not occurred.

1 = A multi-master collision (mode fault) has been detected.

Reserved

These bits are reserved and must be 0.

TXST—Transmit Status

0 = No data transmission currently in progress.

1 =Data transmission currently in progress.

SLAS—Slave Select

If SPI enabled as a Slave,

$0 = \overline{SS}$  input pin is asserted (Low)

$1 = \overline{SS}$  input is not asserted (High).

If SPI enabled as a Master, this bit is not applicable.

If the current ADC Analog Input is not the highest numbered input to be converted, DMA\_ADC initiates data conversion in the next higher numbered ADC Analog Input.

## Configuring DMA\_ADC for Data Transfer

Follow these steps to configure and enable DMA\_ADC:

- 1. Write the DMA\_ADC Address register with the 7 most-significant bits of the Register File address for data transfers.

- 2. Write to the DMA\_ADC Control register to complete the following:

- Enable the DMA\_ADC interrupt request, if desired

- Select the number of ADC Analog Inputs to convert

- Enable the DMA\_ADC channel

**Caution:** When using the DMA\_ADC to perform conversions on multiple ADC inputs and the ADC\_IN field in the DMA\_ADC Control Register is greater than 000b, the Analog-to-Digital Converter must be configured for Single-Shot mode.

Continuous mode operation of the ADC can **only** be used in conjunction with DMA\_ADC if the ADC\_IN field in the DMA\_ADC Control Register is reset to 000b to enable conversion on ADC Analog Input 0 only.

## **DMA Control Register Definitions**

## DMAx Control Register

The DMAx Control register is used to enable and select the mode of operation for DMAx.

| BITS  | 7   | 6   | 5    | 4     | 3    | 2   | 1   | 0   |

|-------|-----|-----|------|-------|------|-----|-----|-----|

| FIELD | DEN | DLE | DDIR | IRQEN | WSEL |     | RSS |     |

| RESET | 0   | 0   | 0    | 0     | 0    | 0   | 0   | 0   |

| R/W   | R/W | R/W | R/W  | R/W   | R/W  | R/W | R/W | R/W |

| ADDR  |     |     |      | FB0H, | FB8H |     |     |     |

Table 71. DMAx Control Register (DMAxCTL)

DEN—DMAx Enable

0 = DMAx is disabled and data transfer requests are disregarded.

# **On-Chip Oscillator**

The Z8F640x family devices feature an on-chip oscillator for use with an external 1-20MHz crystal. This oscillator generates the primary system clock for the internal eZ8 CPU and the majority of the on-chip peripherals. Alternatively, the X<sub>IN</sub> input pin can also accept a CMOS-level clock input signal (32kHz-20MHz). If an external clock generator is used, the X<sub>OUT</sub> pin must be left unconnected. The Z8F640x family device does *not* contain in internal clock divider. The frequency of the signal on the X<sub>IN</sub> input pin determines the frequency of the system clock. The Z8F640x family device on-chip oscillator does not support external RC networks or ceramic resonators.

## 20MHz Crystal Oscillator Operation

Figure 90 illustrates a recommended configuration for connection with an external 20MHz, fundamental-mode, parallel-resonant crystal. Recommended crystal specifications are provided in Table 99. Resistor R<sub>1</sub> limits total power dissipation by the crystal. Printed circuit board layout should add no more than 4pF of stray capacitance to either the X<sub>IN</sub> or X<sub>OUT</sub> pins. If oscillation does not occur, reduce the values of capacitors C<sub>1</sub> and C<sub>2</sub> to decrease loading.

## General Purpose I/O Port Output Timing

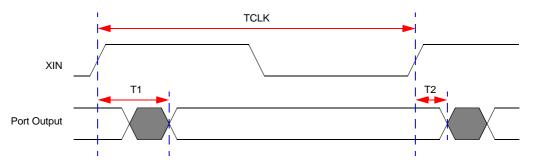

Figure 94 and Table 108 provide timing information for GPIO Port pins.

Figure 94. GPIO Port Output Timing

Table 108. GPIO Port Output Timing

|                |                                     | Delay (ns) |         |

|----------------|-------------------------------------|------------|---------|

| Parameter      | Abbreviation                        | Minimum    | Maximum |

| T <sub>1</sub> | XIN Rise to Port Output Valid Delay | -          | 15      |

| T <sub>2</sub> | XIN Rise to Port Output Hold Time   | 2          | -       |

179

## **SPI Master Mode Timing**

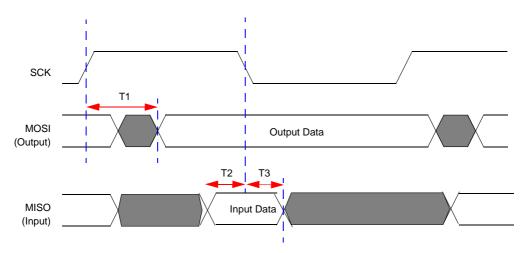

Figure 96 and Table 110 provide timing information for SPI Master mode pins. Timing is shown with SCK rising edge used to source MOSI output data, SCK falling edge used to sample MISO input data. Timing on the SS output pin(s) is controlled by software.

Figure 96. SPI Master Mode Timing

| Table | 110. | SPI | Master | Mode | Timing |

|-------|------|-----|--------|------|--------|

|-------|------|-----|--------|------|--------|

|                |                                             | Delay (ns) |         |

|----------------|---------------------------------------------|------------|---------|

| Parameter      | Abbreviation                                | Minimum    | Maximum |

| T <sub>1</sub> | SCK Rise to MOSI output Valid Delay         | -5         | +5      |

| T <sub>2</sub> | MISO input to SCK (receive edge) Setup Time | 20         |         |

| T <sub>3</sub> | MISO input to SCK (receive edge) Hold Time  | 0          |         |

| Table 118. Arithmetic Instructions (Continued) |

|------------------------------------------------|

|------------------------------------------------|

| Mnemonic | Operands | Instruction                                   |

|----------|----------|-----------------------------------------------|

| SBC      | dst, src | Subtract with Carry                           |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |

| SUB      | dst, src | Subtract                                      |

| SUBX     | dst, src | Subtract using Extended Addressing            |

**Table 119. Bit Manipulation Instructions**

| Mnemonic | Operands    | Instruction                                          |

|----------|-------------|------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                            |

| BIT      | p, bit, dst | Bit Set or Clear                                     |

| BSET     | bit, dst    | Bit Set                                              |

| BSWAP    | dst         | Bit Swap                                             |

| CCF      | _           | Complement Carry Flag                                |

| RCF      | _           | Reset Carry Flag                                     |

| SCF      | _           | Set Carry Flag                                       |

| TCM      | dst, src    | Test Complement Under Mask                           |

| TCMX     | dst, src    | Test Complement Under Mask using Extended Addressing |

| ТМ       | dst, src    | Test Under Mask                                      |

| TMX      | dst, src    | Test Under Mask using Extended Addressing            |

**Table 120. Block Transfer Instructions**

| Mnemonic | Operands | Instruction                                                            |

|----------|----------|------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-Increment Addresses      |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-Increment<br>Addresses |

gated mode 64, 71 one-shot mode 58, 70 operating mode 58 PWM mode 61, 70 reading the timer count values 66 reload high and low byte registers 67 timer control register definitions 66 timer output signal operation 66 timers 0-3 control registers 70 high and low byte registers 66, 69 TM. TMX 188 tools, hardware and software 214 transmit IrDA data 96 transmit interrupt 112 transmitting UART data-polled method 80 transmitting UART data-interrupt-driven method 81 **TRAP 190**

## U

UART 4 architecture 78 asynchronous data format without/with parity 80 baud rate generator 85 baud rates table 93 control register definitions 86 controller signals 14 data format 79 interrupts 85 multiprocessor mode 84 receiving data using DMA controller 83 receiving data using interrupt-driven method 82 receiving data using the polled method 82 transmitting data using the interrupt-driven method 81 transmitting data using the polled method 80 x baud rate high and low registers 91 x control 0 and control 1 registers 89 x status 0 and status 1 registers 87 **UxBRH** register 91

UxBRL register 92 UxCTL0 register 89 UxCTL1 register 90 UxRXD register 87 UxSTAT0 register 87 UxSTAT1 register 89 UxTXD register 86

## V

vector 184 voltage brown-out reset (VBR) 27

## W

watch-dog timer approximate time-out delays 72, 73 CNTL 28 control register 75 electrical characteristics and timing 174 interrupt in normal operation 73 interrupt in stop mode 73 operation 72 refresh 73, 189 reload unlock sequence 74 reload upper, high and low registers 76 reset 28 reset in normal operation 74 reset in stop mode 74 time-out response 73 WDTCTL register 75 WDTH register 76 WDTL register 77 working register 184 working register pair 184 WTDU register 76

## X

X 184 XOR 190 XORX 190