Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betails                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 46                                                        |

| Program Memory Size        | 16KB (16K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 2K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 12x10b                                                |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 64-LQFP                                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1602ar020sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 32. | IRQ2 Enable and Priority Encoding                     |

|-----------|-------------------------------------------------------|

| Table 33. | IRQ1 Enable High Bit Register (IRQ1ENH) 53            |

| Table 34. | IRQ2 Enable Low Bit Register (IRQ2ENL) 54             |

| Table 35. | IRQ2 Enable High Bit Register (IRQ2ENH) 54            |

| Table 36. | Interrupt Edge Select Register (IRQES)                |

| Table 37. | Interrupt Port Select Register (IRQPS) 55             |

| Table 38. | Interrupt Control Register (IRQCTL)                   |

| Table 39. | Timer 0-3 High Byte Register (TxH)                    |

| Table 40. | Timer 0-3 Low Byte Register (TxL)                     |

| Table 41. | Timer 0-3 Reload High Byte Register (TxRH)            |

| Table 42. | Timer 0-3 Reload Low Byte Register (TxRL)             |

| Table 43. | Timer 0-3 PWM High Byte Register (TxPWMH) 69          |

| Table 44. | Timer 0-3 PWM Low Byte Register (TxPWML) 69           |

| Table 45. | Timer 0-3 Control Register (TxCTL)                    |

| Table 46. | Watch-Dog Timer Approximate Time-Out Delays 73        |

| Table 47. | Watch-Dog Timer Control Register (WDTCTL)75           |

| Table 48. | Watch-Dog Timer Reload Upper Byte Register (WDTU) 76  |

| Table 49. | Watch-Dog Timer Reload High Byte Register (WDTH) . 76 |

| Table 50. | Watch-Dog Timer Reload Low Byte Register (WDTL)77     |

| Table 51. | UARTx Transmit Data Register (UxTXD)                  |

| Table 52. | UARTx Receive Data Register (UxRXD)                   |

| Table 53. | UARTx Status 0 Register (UxSTAT0)                     |

| Table 54. | UARTx Control 0 Register (UxCTL0)                     |

| Table 55. | UARTx Status 1 Register (UxSTAT1)                     |

| Table 56. | UARTx Control 1 Register (UxCTL1)                     |

| Table 57. | UARTx Baud Rate High Byte Register (UxBRH)91          |

| Table 58. | UARTx Baud Rate Low Byte Register (UxBRL) 92          |

| Table 59. | UART Baud Rates                                       |

| Table 60. | SPI Clock Phase (PHASE) and Clock Polarity            |

|           | (CLKPOL) Operation                                    |

| Table 61. | SPI Data Register (SPIDATA) 106                       |

| Table 62. | SPI Control Register (SPICTL) 107                     |

| Table 63. | SPI Status Register (SPISTAT) 108                     |

| Table 64. | SPI Mode Register (SPIMODE) 109                       |

| Table 65. | SPI Baud Rate High Byte Register (SPIBRH) 110         |

| Table 66. | SPI Baud Rate Low Byte Register (SPIBRL) 110          |

|           |                                                       |

# Introduction

The Z8 Encore!<sup>®</sup> MCU family of products are the first in a line of ZiLOG microcontroller products based upon the new 8-bit eZ8 CPU. The Z8F640x/Z8F480x/Z8F320x/Z8F240x/Z8F160x products are referred to collectively as either Z8 Encore!<sup>®</sup> or the Z8F640x family. The Z8F640x family of products introduce Flash memory to ZiLOG's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8 CPU is upward compatible with existing Z8 instructions. The rich peripheral set of the Z8F640x family makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices, and sensors.

#### Features

- eZ8 CPU, 20 MHz operation

- 12-channel, 10-bit analog-to-digital converter (ADC)

- 3-channel DMA

- Up to 64KB Flash memory with in-circuit programming capability

- Up to 4KB register RAM

- Serial communication protocols

- Serial Peripheral Interface

- I<sup>2</sup>C

- Two full-duplex 9-bit UARTs

- 24 interrupts with programmable priority

- Three or four 16-bit timers with capture, compare, and PWM capability

- Single-pin On-Chip Debugger

- Two Infrared Data Association (IrDA)-compliant infrared encoder/decoders integrated with the UARTs

- Watch-Dog Timer (WDT) with internal RC oscillator

- Up to 60 I/O pins

- Voltage Brown-out Protection (VBO)

of the port pin direction (input/output) is passed from the Port A-H Data Direction registers to the alternate function assigned to this pin. Table 11 lists the alternate functions associated with each port pin.

| Port   | Pin | Mnemonic     | Alternate Function Description                    |

|--------|-----|--------------|---------------------------------------------------|

| Port A | PA0 | TOIN         | Timer 0 Input                                     |

|        | PA1 | TOOUT        | Timer 0 Output                                    |

|        | PA2 | N/A          | No alternate function                             |

|        | PA3 | CTS0         | UART 0 Clear to Send                              |

|        | PA4 | RXD0 / IRRX0 | UART 0 / IrDA 0 Receive Data                      |

|        | PA5 | TXD0 / IRTX0 | UART 0 / IrDA 0 Transmit Data                     |

|        | PA6 | SCL          | I <sup>2</sup> C Clock (automatically open-drain) |

|        | PA7 | SDA          | I <sup>2</sup> C Data (automatically open-drain)  |

| Port B | PB0 | ANA0         | ADC Analog Input 0                                |

|        | PB1 | ANA1         | ADC Analog Input 1                                |

|        | PB2 | ANA2         | ADC Analog Input 2                                |

|        | PB3 | ANA3         | ADC Analog Input 3                                |

|        | PB4 | ANA4         | ADC Analog Input 4                                |

|        | PB5 | ANA5         | ADC Analog Input 5                                |

|        | PB6 | ANA6         | ADC Analog Input 6                                |

|        | PB7 | ANA7         | ADC Analog Input 7                                |

| Port C | PC0 | T1IN         | Timer 1 Input                                     |

|        | PC1 | T1OUT        | Timer 1 Output                                    |

|        | PC2 | SS           | SPI Slave Select                                  |

|        | PC3 | SCK          | SPI Serial Clock                                  |

|        | PC4 | MOSI         | SPI Master Out Slave In                           |

|        | PC5 | MISO         | SPI Master In Slave Out                           |

|        | PC6 | T2IN         | Timer 2 In                                        |

|        | PC7 | T2OUT        | Timer 2 Out (not available in 40-pin packages)    |

| Table 11 | . Port | Alternate | Function | Mapping |

|----------|--------|-----------|----------|---------|

|----------|--------|-----------|----------|---------|

| Priority | Program Memory<br>Vector Address | Interrupt Source                                 | Interrupt Assertion Type |

|----------|----------------------------------|--------------------------------------------------|--------------------------|

| Highest  | 0002h                            | Reset (not an interrupt)                         | Not applicable           |

|          | 0004h                            | Watch-Dog Timer                                  | Continuous assertion     |

|          | 0006h                            | Illegal Instruction Trap (not an interrupt)      | Not applicable           |

|          | 0008h                            | Timer 2                                          | Single assertion (pulse) |

|          | 000Ah                            | Timer 1                                          | Single assertion (pulse) |

|          | 000Ch                            | Timer 0                                          | Single assertion (pulse) |

|          | 000Eh                            | UART 0 receiver                                  | Continuous assertion     |

|          | 0010h                            | UART 0 transmitter                               | Continuous assertion     |

|          | 0012h                            | I <sup>2</sup> C                                 | Continuous assertion     |

|          | 0014h                            | SPI                                              | Continuous assertion     |

|          | 0016h                            | ADC                                              | Single assertion (pulse) |

|          | 0018h                            | Port A7 or Port D7, rising or falling input edge | Single assertion (pulse) |

|          | 001Ah                            | Port A6 or Port D6, rising or falling input edge | Single assertion (pulse) |

|          | 001Ch                            | Port A5 or Port D5, rising or falling input edge | Single assertion (pulse) |

|          | 001Eh                            | Port A4 or Port D4, rising or falling input edge | Single assertion (pulse) |

|          | 0020h                            | Port A3 or Port D3, rising or falling input edge | Single assertion (pulse) |

|          | 0022h                            | Port A2 or Port D2, rising or falling input edge | Single assertion (pulse) |

|          | 0024h                            | Port A1 or Port D1, rising or falling input edge | Single assertion (pulse) |

|          | 0026h                            | Port A0 or Port D0, rising or falling input edge | Single assertion (pulse) |

|          | 0028h                            | Timer 3 (not available in 40/44-pin packages)    | Single assertion (pulse) |

|          | 002Ah                            | UART 1 receiver                                  | Continuous assertion     |

|          | 002Ch                            | UART 1 transmitter                               | Continuous assertion     |

|          | 002Eh                            | DMA                                              | Single assertion (pulse) |

|          | 0030h                            | Port C3, both input edges                        | Single assertion (pulse) |

|          | 0032h                            | Port C2, both input edges                        | Single assertion (pulse) |

|          | 0034h                            | Port C1, both input edges                        | Single assertion (pulse) |

| Lowest   | 0036h                            | Port C0, both input edges                        | Single assertion (pulse) |

|          |                                  |                                                  |                          |

#### Table 22. Interrupt Vectors in Order of Priority

#### **Interrupt Request 2 Register**

The Interrupt Request 2 (IRQ2) register (Table 25) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 1 register to determine if any interrupt requests are pending.

Table 25. Interrupt Request 2 Register (IRQ2)

| BITS  | 7   | 6     | 5     | 4    | 3    | 2    | 1    | 0    |

|-------|-----|-------|-------|------|------|------|------|------|

| FIELD | T3I | U1RXI | UITXI | DMAI | PC3I | PC2I | PC1I | PC0I |

| RESET | 0   | 0     | 0     | 0    | 0    | 0    | 0    | 0    |

| R/W   | R/W | R/W   | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  |

| ADDR  |     |       |       | FC   | 6H   |      |      |      |

T3I—Timer 3 Interrupt Request

- 0 = No interrupt request is pending for Timer 3.

- 1 = An interrupt request from Timer 3 is awaiting service.

U1RXI—UART 1 Receive Interrupt Request

- 0 = No interrupt request is pending for the UART1 receiver.

- 1 = An interrupt request from UART1 receiver is awaiting service.

- U1TXI-UART 1 Transmit Interrupt Request

- 0 = No interrupt request is pending for the UART 1 transmitter.

- 1 = An interrupt request from the UART 1 transmitter is awaiting service.

DMAI—DMA Interrupt Request

- 0 = No interrupt request is pending for the DMA.

- 1 = An interrupt request from the DMA is awaiting service.

PCxI—Port C Pin x Interrupt Request

- 0 = No interrupt request is pending for GPIO Port C pin *x*.

- 1 = An interrupt request from GPIO Port C pin x is awaiting service.

where *x* indicates the specific GPIO Port C pin number (0 through 3).

set to 2-byte transfers, the temporary holding register for the Timer Reload High Byte is not bypassed.

BITS 7 6 5 4 3 2 1 0 TRH FIELD 1 1 1 1 1 1 1 1 RESET R/W R/W R/W R/W R/W R/W R/W R/W R/W F02H, F0AH, F12H, F1AH ADDR

#### Table 40. Timer 0-3 Reload High Byte Register (TxRH)

#### Table 41. Timer 0-3 Reload Low Byte Register (TxRL)

| BITS  | 7   | 6   | 5   | 4           | 3          | 2   | 1   | 0   |

|-------|-----|-----|-----|-------------|------------|-----|-----|-----|

| FIELD |     |     |     | TI          | RL         |     |     |     |

| RESET | 1   | 1   | 1   | 1           | 1          | 1   | 1   | 1   |

| R/W   | R/W | R/W | R/W | R/W         | R/W        | R/W | R/W | R/W |

| ADDR  |     |     | ]   | F03H, F0BH, | F13H, F1BH | [   |     |     |

TRH and TRL-Timer Reload Register High and Low

These two bytes form the 16-bit Reload value, {TRH[7:0], TRL[7:0]}. This value is used to set the maximum count value which initiates a timer reload to 0001H. In Compare mode, these two byte form the 16-bit Compare value.

information on approximate time-out delays for the minimum and maximum WDT reload values.

Table 45. Watch-Dog Timer Approximate Time-Out Delays

| WDT Reload Value | WDT Reload Value | Approximate Time-Out Delay<br>ad Value (with 50kHz typical WDT oscillator frequency) |                        |  |  |  |

|------------------|------------------|--------------------------------------------------------------------------------------|------------------------|--|--|--|

| (Hex)            | (Decimal)        | Typical                                                                              | Description            |  |  |  |

| 000004           | 4                | 80µs                                                                                 | Minimum time-out delay |  |  |  |

| FFFFFF           | 16,777,215       | 335.5s                                                                               | Maximum time-out delay |  |  |  |

#### Watch-Dog Timer Refresh

When first enabled, the Watch-Dog Timer is loaded with the value in the Watch-Dog Timer Reload registers. The Watch-Dog Timer then counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the downcounter to be reloaded with the WDT Reload value stored in the Watch-Dog Timer Reload registers. Counting resumes following the reload operation.

When the Z8F640x family device is operating in Debug Mode (via the On-Chip Debugger), the Watch-Dog Timer is continuously refreshed to prevent spurious Watch-Dog Timer time-outs.

#### Watch-Dog Timer Time-Out Response

The Watch-Dog Timer times out when the counter reaches 000000H. A time-out of the Watch-Dog Timer generates either an interrupt or a Short Reset. The WDT\_RES Option Bit determines the time-out response of the Watch-Dog Timer. Refer to the **Option Bits** chapter for information regarding programming of the WDT\_RES Option Bit.

#### WDT Interrupt in Normal Operation

If configured to generate an interrupt when a time-out occurs, the Watch-Dog Timer issues an interrupt request to the interrupt controller and sets the WDT status bit in the Watch-Dog Timer Control register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watch-Dog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watch-Dog Timer counter rolls over to its maximum value of FFFFFH and continues counting. The Watch-Dog Timer counter is not automatically returned to its Reload Value.

#### WDT Interrupt in Stop Mode

If configured to generate an interrupt when a time-out occurs and the Z8F640x family device is in STOP mode, the Watch-Dog Timer automatically initiates a STOP Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Watch-Dog Timer Control register are set to 1 following WDT time-out in STOP

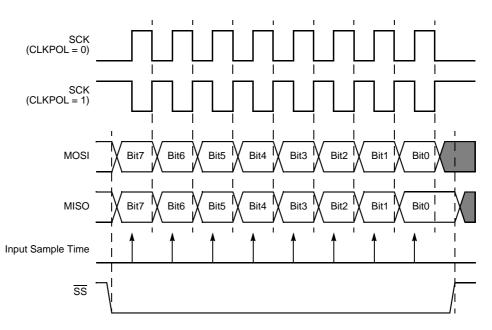

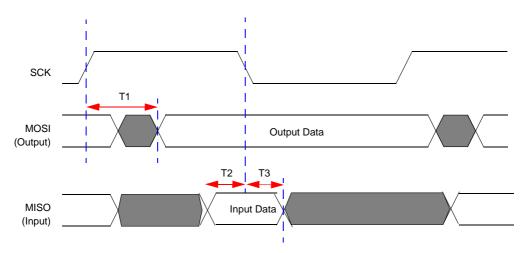

#### Transfer Format PHASE Equals Zero

Figure 77 illustrates the timing diagram for an SPI transfer in which PHASE is cleared to 0. The two SCK waveforms show polarity with CLKPOL reset to 0 and with CLKPOL set to one. The diagram may be interpreted as either a Master or Slave timing diagram since the SCK Master-In/Slave-Out (MISO) and Master-Out/Slave-In (MOSI) pins are directly connected between the Master and the Slave.

Figure 77. SPI Timing When PHASE is 0

#### Transfer Format PHASE Equals One

Figure 78 illustrates the timing diagram for an SPI transfer in which PHASE is one. Two waveforms are depicted for SCK, one for CLKPOL reset to 0 and another for CLKPOL set to 1.

limit to the amount of data transferred in one operation. When transmitting data or acknowledging read data from the slave, the SDA signal changes in the middle of the low period of SCL and is sampled in the middle of the high period of SCL.

## I<sup>2</sup>C Interrupts

the I<sup>2</sup>C Controller contains three sources of interrupts—Transmit, Receive and Not Acknowledge (NAK) interrupts. NAK interrupts occur when a Not Acknowledge is received from the slave or sent by the I<sup>2</sup>C Controller and the Start or Stop bit is set. This source sets bit 0 and can only be cleared by setting the Start or Stop bit. When this interrupt occurs, the I<sup>2</sup>C Controller waits until it is cleared before performing any action. In an interrupt service routine, this interrupt must be the first thing polled. Receive interrupts occur when a byte of data has been received by the I<sup>2</sup>C master. This interrupt is cleared by reading from the I<sup>2</sup>C Data register. If no action is taken, the I<sup>2</sup>C Controller waits until this interrupt is cleared before performing any other action.

For Transmit interrupts to occur, the TXI bit must be 1 in the  $I^2C$  Control register. Transmit interrupts occur under the following conditions when the transmit data register is empty:

- The I<sup>2</sup>C Controller is idle (not performing an operation).

- The START bit is set and there is no valid data in the I<sup>2</sup>C Shift or I<sup>2</sup>C Data register to shift out.

- The first bit of the byte of an address is shifting out and the RD bit of the I<sup>2</sup>C Status register is deasserted.

- The first bit of a 10-bit address shifts out.

- The first bit of write data shifted out.

**Note:** Writing to the I<sup>2</sup>C Data register always clears a Transmit interrupt.

## **Start and Stop Conditions**

The master ( $I^2C$ ) drives all Start and Stop signals and initiates all transactions. To start a transaction, the  $I^2C$  Controller generates a START condition by pulling the SDA signal low while SCL is high. Then a high-to-low transition occurs on the SDA signal while the clock is High. To complete a transaction, the  $I^2C$  Controller generates a Stop condition by creating a low-to-high transition of the SDA signal in the middle of the high period of the SCL signal. When the SCL signal is High, the master generates a Start bit by pulling a High SDA signal Low and generates a Stop bit by releasing the SDA signal. The Start and Stop signals are found in the  $I^2C$  Control register and must be written by software when the Z8F640x family device must begin or end a transaction.

## Writing a Transaction with a 7-Bit Address

1. The  $I^2C$  Controller shifts the  $I^2C$  Shift register out onto SDA signal.

- 1. Software writes the I<sup>2</sup>C Data register with a 7-bit slave address followed by a 1 (read).

- 2. Software asserts the START bit of the I<sup>2</sup>C Control register.

- 3. Software asserts the NAK bit of the I<sup>2</sup>C Control register so that after the first byte of data has been read by the I<sup>2</sup>C Controller, a Not Acknowledge is sent to the I<sup>2</sup>C slave.

- 4. The I<sup>2</sup>C Controller sends the START condition.

- 5. The I<sup>2</sup>C Controller sends the address and read bit by the SDA signal.

- 6. The I<sup>2</sup>C slave sends an Acknowledge by pulling the SDA signal Low during the next high period of SCL.

- 7. The  $I^2C$  Controller reads the first byte of data from the  $I^2C$  slave.

- 8. The I<sup>2</sup>C Controller asserts the Receive interrupt.

- 9. Software responds by reading the  $I^2C$  Data register.

- 10. The  $I^2C$  Controller sends a NAK to the  $I^2C$  slave.

- 11. A NAK interrupt is generated by the I<sup>2</sup>C Controller.

- 12. Software responds by setting the STOP bit of the  $I^2C$  Control register.

- 13. A STOP condition is sent to the  $I^2C$  slave.

#### Reading a Transaction with a 10-Bit Address

Figure 82 illustrates the receive format for a 10-bit addressed slave. The shaded regions indicate data transferred from the I<sup>2</sup>C Controller to slaves and unshaded regions indicate data transferred from the slaves to the I<sup>2</sup>C Controller.

| S | Slave Address | W=0 | А | Slave address | А | S | Slave Address | R=1 | А | Data | А | Data | Ā | Р |

|---|---------------|-----|---|---------------|---|---|---------------|-----|---|------|---|------|---|---|

|   | 1st 7 bits    |     |   | 2nd Byte      |   |   | 1st 7 bits    |     |   |      |   |      |   |   |

#### Figure 82. Receive Data Format for a 10-Bit Addressed Slave

The first seven bits transmitted in the first byte are 11110XX. The two bits XX are the two most-significant bits of the 10-bit address. The lowest bit of the first byte transferred is the write signal.

The data transfer format for a receive operation on a 10-bit addressed slave is as follows:

- 1. Software writes an address 11110B followed by the two address bits and a 0 (write).

- 2. Software asserts the START bit of the  $I^2C$  Control register.

- 3. The  $I^2C$  Controller sends the Start condition.

- Set CONT to 1 to select continuous conversion.

- Write to VREF to enable or disable the internal voltage reference generator.

- Set CEN to 1 to start the conversions.

- 3. When the first conversion in continuous operation is complete (after 5129 system clock cycles, plus the 40 cycles for power-up, if necessary), the ADC control logic performs the following operations:

- CEN resets to 0 to indicate the first conversion is complete. CEN remains 0 for all subsequent conversions in continuous operation.

- An interrupt request is sent to the Interrupt Controller to indicate the *first* conversion is complete. An interrupt request is not sent for subsequent conversions in continuous operation.

- 4. Thereafter, the ADC writes a new 10-bit data result to {ADCD\_H[7:0], ADCD\_L[7:6]} every 256 system clock cycles.

- 5. To disable continuous conversion, clear the CONT bit in the ADC Control register to 0.

#### **DMA Control of the ADC**

The Direct Memory Access (DMA) Controller can control operation of the ADC including analog input selection and conversion enable. For more information on the DMA and configuring for ADC operations refer to the **Direct Memory Access Controller** chapter.

## **ADC Control Register Definitions**

#### **ADC Control Register**

The ADC Control register selects the analog input channel and initiates the analog-to-digital conversion.

| BITS  | 7   | 6        | 5    | 4    | 3  | 2    | 1      | 0 |

|-------|-----|----------|------|------|----|------|--------|---|

| FIELD | CEN | Reserved | VREF | CONT |    | ANAI | N[3:0] |   |

| RESET | 0   | 0        | 0    | 0    |    | 00   | 00     |   |

| R/W   | R/W | R/W      | R/W  | R/W  |    | R/   | W      |   |

| ADDR  |     |          |      | F7   | 0H |      |        |   |

Table 80. ADC Control Register (ADCCTL)

CEN—Conversion Enable

0 = Conversion is complete. Writing a 0 produces no effect. The ADC automatically clears

# Flash Memory

## **Overview**

The Z8F640x family features up to 64KB (65,536 bytes) of non-volatile Flash memory with read/write/erase capability. The Flash Memory can be programmed and erased in-circuit by either user code or through the On-Chip Debugger.

The Flash memory array is arranged in pages with 512 bytes per page. The 512-byte page is the minimum Flash block size that can be erased. Each page is divided into 8 rows of 64 bytes. The Flash memory also contains a High Sector that can be enabled for writes and erase separately from the rest of the Flash array. The first 2 bytes of the Flash Program memory are used as Option Bits. Refer to the **Option Bits** chapter for more information on their operation.

Table 83 describes the Flash memory configuration for each device in the Z8F640x family. Figure 84 illustrates the Flash memory arrangement.

| Part Number | Flash Size<br>KB (Bytes) | Flash<br>Pages | Program Memory<br>Addresses | Flash High Sector Size<br>KB (Bytes) | High Sector<br>Addresses |

|-------------|--------------------------|----------------|-----------------------------|--------------------------------------|--------------------------|

| Z8F160x     | 16 (16,384)              | 32             | 0000H - 3FFFH               | 1 (1024)                             | 3C00H - 3FFFH            |

| Z8F240x     | 24 (24,576)              | 48             | 0000H - 5FFFH               | 2 (2048)                             | 5800H - 5FFFH            |

| Z8F320x     | 32 (32,768)              | 64             | 0000H - 7FFFH               | 2 (2048)                             | 7800H - 7FFFH            |

| Z8F480x     | 48 (49,152)              | 96             | 0000H - BFFFH               | 4 (4096)                             | B000H - BFFFH            |

| Z8F640x     | 64 (65,536)              | 128            | 0000H - FFFFH               | 8 (8192)                             | E000H - FFFFH            |

#### Table 83. Z8F640x family Flash Memory Configurations

# **On-Chip Debugger**

## **Overview**

The Z8F640x family devices have an integrated On-Chip Debugger (OCD) that provides advanced debugging features including:

- Reading and writing of the Register File

- Reading and writing of Program and Data Memory

- Setting of Breakpoints and Watchpoints

- Execution of eZ8 CPU instructions.

## Architecture

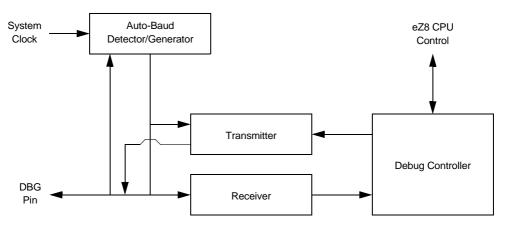

The On-Chip Debugger consists of four primary functional blocks: transmitter, receiver, auto-baud generator, and debug controller. Figure 86 illustrates the architecture of the On-Chip Debugger

Figure 86. On-Chip Debugger Block Diagram

| Debug Command           | Command Byte | Enabled when NOT in Debug mode? | Disabled by<br>Read Protect Option Bit |

|-------------------------|--------------|---------------------------------|----------------------------------------|

| Write Program Memory    | 0AH          | -                               | Disabled                               |

| Read Program Memory     | 0BH          | -                               | Disabled                               |

| Write Data Memory       | 0CH          | -                               | Yes                                    |

| Read Data Memory        | 0DH          | -                               | -                                      |

| Read Program Memory CRC | 0EH          | -                               | -                                      |

| Reserved                | 0FH          | -                               | -                                      |

| Step Instruction        | 10H          | -                               | Disabled                               |

| Stuff Instruction       | 11H          | -                               | Disabled                               |

| Execute Instruction     | 12H          | -                               | Disabled                               |

| Reserved                | 13H - 1FH    | -                               | -                                      |

| Write Watchpoint        | 20H          | -                               | Disabled                               |

| Read Watchpoint         | 21H          | -                               | -                                      |

| Reserved                | 22H - FFH    | -                               | -                                      |

#### **Table 93. On-Chip Debugger Commands**

In the following bulleted list of OCD Commands, data and commands sent from the host to the On-Chip Debugger are identified by 'DBG <-- Command/Data'. Data sent from the On-Chip Debugger back to the host is identified by 'DBG --> Data'

Read OCD Revision (00H)—The Read OCD Revision command is used to determine the version of the On-Chip Debugger. If OCD commands are added, removed, or changed, this revision number changes.

```

DEG <-- 00H

DEG --> OCDREV[15:8] (Major revision number)

DEG --> OCDREV[7:0] (Minor revision number)

```

• **Read OCD Status Register (02H)**—The Read OCD Status Register command is used to read the OCDSTAT register.

```

DBG <-- 02H

DBG --> OCDSTAT[7:0]

```

• **Read Runtime Counter (03H)**—The Runtime Counter is used to count Z8 Encore! system clock cycles in between Breakpoints. The 16-bit Runtime Counter counts up from 0000H and stops at the maximum count of FFFFH. The Runtime Counter is overwritten during the Write Memory, Read Memory, Write Register, Read Register, Read Memory CRC, Step Instruction, Stuff Instruction, and Execute Instruction commands.

# **DC Characteristics**

Table 101 lists the DC characteristics of the Z8F640x family devices. All voltages are referenced to  $V_{SS}$ , the primary system ground.

|                   |                           | $T_A = -40^0 C$ to $105^0 C$ |                  |                      |       |                                                                                                   |  |

|-------------------|---------------------------|------------------------------|------------------|----------------------|-------|---------------------------------------------------------------------------------------------------|--|

| Symbol            | Parameter                 | Minimum Typical              |                  | Maximum              | Units | Conditions                                                                                        |  |

| V <sub>DD</sub>   | Supply Voltage            | 3.0                          | -                | 3.6                  | V     |                                                                                                   |  |

| V <sub>IL1</sub>  | Low Level Input Voltage   | -0.3                         | _                | 0.3*V <sub>DD</sub>  | V     | For all input pins except RESET, DBG, and XIN.                                                    |  |

| V <sub>IL2</sub>  | Low Level Input Voltage   | -0.3                         | _                | 0.2*V <sub>DD</sub>  | V     | For RESET, DBG, and XIN.                                                                          |  |

| $V_{IH1}$         | High Level Input Voltage  | 0.7*V <sub>DD</sub>          | _                | 5.5                  | V     | Port A, C, D, E, F, and G pins.                                                                   |  |

| V <sub>IH2</sub>  | High Level Input Voltage  | 0.7*V <sub>DD</sub>          | -                | V <sub>DD</sub> +0.3 | V     | Port B and H pins.                                                                                |  |

| V <sub>IH3</sub>  | High Level Input Voltage  | 0.8*V <sub>DD</sub>          | _                | V <sub>DD</sub> +0.3 | V     | RESET, DBG, and XIN pins.                                                                         |  |

| V <sub>OL1</sub>  | Low Level Output Voltage  | -                            | -                | 0.4                  | V     | V <sub>DD</sub> = 3.0V; I <sub>OL</sub> = 2mA<br>High Output Drive disabled.                      |  |

| V <sub>OH1</sub>  | High Level Output Voltage | 2.4                          | -                | -                    | V     | V <sub>DD</sub> = 3.0V; I <sub>OH</sub> = -2mA<br>High Output Drive disabled.                     |  |

| V <sub>OL2</sub>  | Low Level Output Voltage  | -                            | _                | 0.6                  | V     | $V_{DD} = 3.3V; I_{OL} = 20mA$<br>High Output Drive enabled.<br>$T_A = -40^0 C$ to $+70^0 C$      |  |

| V <sub>OL3</sub>  | Low Level Output Voltage  | -                            | -                | 0.6                  | V     | $V_{DD} = 3.3V; I_{OL} = 15mA$<br>High Output Drive enabled.<br>$T_A = 70^0C \text{ to } +105^0C$ |  |

| V <sub>OH2</sub>  | High Level Output Voltage | 2.4                          | _                | -                    | V     | $V_{DD} = 3.3V; I_{OH} = -20mA$<br>High Output Drive enabled.<br>$T_A = -40^0 C$ to $+70^0 C$     |  |

| V <sub>OH3</sub>  | High Level Output Voltage | 2.4                          | -                | -                    | V     | $V_{DD} = 3.3V; I_{OH} = -15mA$<br>High Output Drive enabled.<br>$T_A = 70^0C$ to $+105^0C$       |  |

| I <sub>IL</sub>   | Input Leakage Current     | -5                           | -                | +5                   | μA    | $V_{DD} = 3.6V;$<br>$V_{IN} = VDD \text{ or } VSS^1$                                              |  |

| I <sub>TL</sub>   | Tri-State Leakage Current | -5                           | -                | +5                   | μΑ    | V <sub>DD</sub> = 3.6V                                                                            |  |

| C <sub>PAD</sub>  | GPIO Port Pad Capacitance | -                            | 8.0 <sup>2</sup> | -                    | pF    |                                                                                                   |  |

| C <sub>XIN</sub>  | XIN Pad Capacitance       | -                            | 8.0 <sup>2</sup> | -                    | pF    |                                                                                                   |  |

| C <sub>XOUT</sub> | XOUT Pad Capacitance      | -                            | 9.5 <sup>2</sup> | -                    | pF    |                                                                                                   |  |

#### Table 101. DC Characteristics

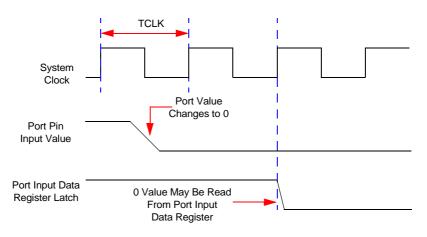

## General Purpose I/O Port Input Data Sample Timing

Figure 93 illustrates timing of the GPIO Port input sampling. The input value on a GPIO Port pin is sampled on the rising edge of the system clock. The Port value is then available to the eZ8 CPU on the second rising clock edge following the change of the Port value.

#### Figure 93. Port Input Sample Timing

#### **Table 107. GPIO Port Input Timing**

|                     |                                                                                                       | Delay (ns) |         |  |

|---------------------|-------------------------------------------------------------------------------------------------------|------------|---------|--|

| Parameter           | Abbreviation                                                                                          | Minimum    | Maximum |  |

| T <sub>S_PORT</sub> | Port Input Transition to XIN Rise Setup Time<br>(Not pictured)                                        | 5          | -       |  |

| T <sub>H_PORT</sub> | XIN Rise to Port Input Transition Hold Time<br>(Not pictured)                                         | 5          | -       |  |

| T <sub>SMR</sub>    | GPIO Port Pin Pulse Width to Insure Stop Mode Recovery<br>(for GPIO Port Pins enabled as SMR sources) | 1µs        |         |  |

## **SPI Master Mode Timing**

Figure 96 and Table 110 provide timing information for SPI Master mode pins. Timing is shown with SCK rising edge used to source MOSI output data, SCK falling edge used to sample MISO input data. Timing on the SS output pin(s) is controlled by software.

Figure 96. SPI Master Mode Timing

| Table | 110. | SPI | Master | Mode | Timing |

|-------|------|-----|--------|------|--------|

|-------|------|-----|--------|------|--------|

|                |                                             | Delay (ns) |         |  |

|----------------|---------------------------------------------|------------|---------|--|

| Parameter      | Abbreviation                                | Minimum    | Maximum |  |

| T <sub>1</sub> | SCK Rise to MOSI output Valid Delay         | -5         | +5      |  |

| T <sub>2</sub> | MISO input to SCK (receive edge) Setup Time | 20         |         |  |

| T <sub>3</sub> | MISO input to SCK (receive edge) Hold Time  | 0          |         |  |

ZILOG

# eZ8 CPU Instruction Set

# Assembly Language Programming Introduction

The eZ8 CPU assembly language provides a means for writing an application program without having to be concerned with actual memory addresses or machine instruction formats. A program written in assembly language is called a source program. Assembly language allows the use of symbolic addresses to identify memory locations. It also allows mnemonic codes (opcodes and operands) to represent the instructions themselves. The opcodes identify the instruction while the operands represent memory locations, registers, or immediate data values.

Each assembly language program consists of a series of symbolic commands called statements. Each statement can contain labels, operations, operands and comments.

Labels can be assigned to a particular instruction step in a source program. The label identifies that step in the program as an entry point for use by other instructions.

The assembly language also includes assembler directives that supplement the machine instruction. The assembler directives, or pseudo-ops, are not translated into a machine instruction. Rather, the pseudo-ops are interpreted as directives that control or assist the assembly process.

The source program is processed (assembled) by the assembler to obtain a machine language program called the object code. The object code is executed by the eZ8 CPU. An example segment of an assembly language program is detailed in the following example.

#### Assembly Language Source Program Example

| JP START      | ; Everything after the semicolon is a comment.                                                                                                                                                                         |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START:        | ; A label called "START". The first instruction (JP START) in this ; example causes program execution to jump to the point within the ; program where the START label occurs.                                          |

| LD R4, R7     | ; A Load (LD) instruction with two operands. The first operand,<br>; Working Register R4, is the destination. The second operand,<br>; Working Register R7, is the source. The contents of R7 is<br>; written into R4. |

| LD 234H, #%01 | ; Another Load (LD) instruction with two operands.<br>; The first operand, Extended Mode Register Address 234H,<br>; identifies the destination. The second operand, Immediate Data                                    |

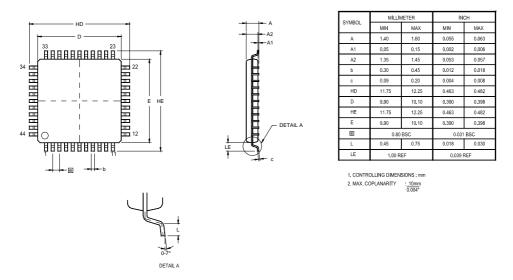

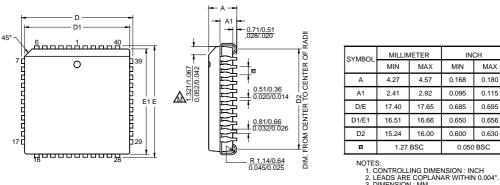

Figure 104 illustrates the 44-pin LQFP (low profile quad flat package) available for the Z8F1601, Z8F2401, Z8F3201, Z8F4801, and Z8F6401 devices.

Figure 104. 44-Lead Low-Profile Quad Flat Package (LQFP)

Figure 105 illustrates the 44-pin PLCC (plastic lead chip carrier) package available for the Z8F1601, Z8F2401, Z8F3201, Z8F4801, and Z8F6401 devices.

3. DIMENSION : MM

Figure 105. 44-Lead Plastic Lead Chip Carrier Package (PLCC)

MAX

0.180

0.115

0.695

0.656

0.630

# Index

# **Symbols**

# 185 % 185 @ 185

# Numerics

10-bit ADC 4

40-lead plastic dual-inline package 206

44-lead low-profile quad flat package 207

44-lead plastic lead chip carrier package 207

64-lead low-profile quad flat package 208

68-lead plastic lead chip carrier package 209

80-lead quad flat package 210

# A

absolute maximum ratings 167 AC characteristics 172 ADC 187 architecture 132 automatic power-down 133 block diagram 133 continuous conversion 134 control register 135 control register definitions 135 data high byte register 137 data low bits register 137 DMA control 135 electrical characteristics and timing 174 operation 133 single-shot conversion 133 ADCCTL register 135 ADCDH register 137 ADCDL register 137 **ADCX 187** ADD 187 add - extended addressing 187 add with carry 187 add with carry - extended addressing 187

additional symbols 185 address space 17 ADDX 187 analog signals 14 analog-to-digital converter (ADC) 132 AND 190 ANDX 190 arithmetic instructions 187 assembly language programming 182 assembly language syntax 183

# B

B 185 b 184 baud rate generator, UART 85 **BCLR 188** binary number suffix 185 **BIT 188** bit 184 clear 188 manipulation instructions 188 set 188 set or clear 188 swap 188 test and jump 190 test and jump if non-zero 190 test and jump if zero 190 bit jump and test if non-zero 190 bit swap 191 block diagram 3 block transfer instructions 188 **BRK 190 BSET 188** BSWAP 188, 191 **BTJ 190 BTJNZ 190 BTJZ 190**

# С

CALL procedure 190 capture mode 71 capture/compare mode 71