# E·XFL

# Zilog - Z8F1602AR020SC00TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                               |

|----------------------------|---------------------------------------------------------------|

| Product Status             | Obsolete                                                      |

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                    |

| Number of I/O              | 46                                                            |

| Program Memory Size        | 16KB (16K x 8)                                                |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 2K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                     |

| Data Converters            | A/D 12x10b                                                    |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | 0°C ~ 70°C (TA)                                               |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 64-LQFP                                                       |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1602ar020sc00tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Pin Configurations**

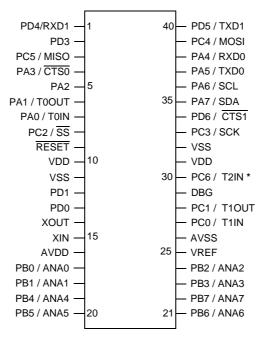

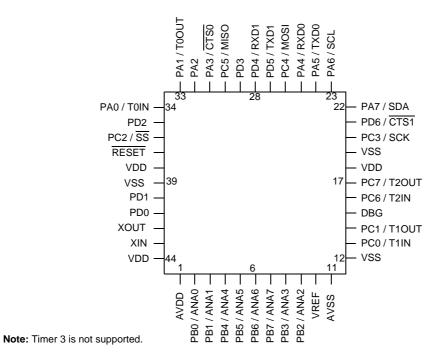

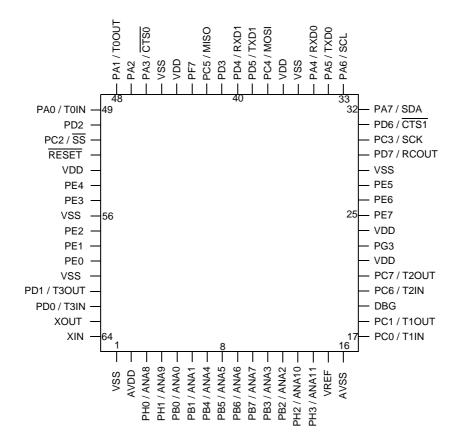

Figures 56 through 61 illustrate the pin configurations for all of the packages available in the Z8 Encore!® MCU family. Refer to Table 2 for a description of the signals.

Note: Timer 3 is not supported.

Figure 56. Z8Fxx01 in 40-Pin Dual Inline Package (DIP)

\* T2OUT is not supported.

Figure 58. Z8Fxx01 in 44-Pin Low-Profile Quad Flat Package (LQFP)

Figure 59. Z8Fxx02 in 64-Pin Low-Profile Quad Flat Package (LQFP)

# **Signal Descriptions**

Table 2 describes the Z8F640x family signals. Refer to the section **Pin Configurations on page 7** to determine the signals available for the specific package styles.

| Signal Mnemonic             | I/O       | Description                                                                                                                                                                                                                                                                           |

|-----------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General-Purpose I/C         | ) Ports A | -Н                                                                                                                                                                                                                                                                                    |

| PA[7:0]                     | I/O       | Port A[7:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                             |

| PB[7:0]                     | I/O       | Port B[7:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                             |

| PC[7:0]                     | I/O       | Port C[7:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                             |

| PD[7:0]                     | I/O       | Port D[7:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                             |

| PE[7:0]                     | I/O       | Port E[7:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                             |

| PF[7:0]                     | I/O       | Port F[7:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                             |

| PG[7:0]                     | I/O       | Port G[7:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                             |

| PH[3:0]                     | I/O       | Port H[3:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                             |

| I <sup>2</sup> C Controller |           |                                                                                                                                                                                                                                                                                       |

| SCL                         | 0         | Serial Clock. This is the output clock for the I <sup>2</sup> C. This pin is multiplexed with a general-purpose I/O pin. When the general-purpose I/O pin is configured for alternate function to enable the SCL function, this pin is open-drain.                                    |

| SDA                         | I/O       | Serial Data. This open-drain pin is used to transfer data between the I <sup>2</sup> C and a slave. This pin is multiplexed with a general-purpose I/O pin. When the general-purpose I/O pin is configured for alternate function to enable the SDA function, this pin is open-drain. |

| SPI Controller              |           |                                                                                                                                                                                                                                                                                       |

| SS                          | I/O       | Slave Select. This signal can be an output or an input. If the Z8 Encore! is the SPI master, this pin may be configured as the Slave Select output. If the Z8 Encore! is the SPI slave, this pin is the input slave select. It is multiplexed with a general-purpose I/O pin.         |

| SCK                         | I/O       | SPI Serial Clock. The SPI master supplies this pin. If the Z8 Encore! is the SPI master, this pin is an output. If the Z8 Encore! is the SPI slave, this pin is an input. It is multiplexed with a general-purpose I/O pin.                                                           |

| MOSI                        | I/O       | Master Out Slave In. This signal is the data output from the SPI master device and the data input to the SPI slave device. It is multiplexed with a general-purpose I/O pin.                                                                                                          |

| MISO                        | I/O       | Master In Slave Out. This pin is the data input to the SPI master device and the data output from the SPI slave device. It is multiplexed with a general-purpose I/O pin.                                                                                                             |

Table 2. Signal Descriptions

| Signal Mnemonic | I/O | Description                                          |

|-----------------|-----|------------------------------------------------------|

| Reset           |     |                                                      |

| RESET           | Ι   | RESET. Generates a Reset when asserted (driven Low). |

| Power Supply    |     |                                                      |

| VDD             | Ι   | Power Supply.                                        |

| AVDD            | Ι   | Analog Power Supply.                                 |

| VSS             | Ι   | Ground.                                              |

| AVSS            | Ι   | Analog Ground.                                       |

#### Table 2. Signal Descriptions (Continued)

# **Pin Characteristics**

Table 3 provides detailed information on the characteristics for each pin available on the Z8F640x family products. Data in Table 3 is sorted alphabetically by the pin symbol mnemonic.

Table 3. Pin Characteristics of the Z8F640x family

| N/A<br>N/A<br>I/O<br>N/A | N/A<br>N/A<br>I   | N/A<br>N/A<br>N/A            | N/A<br>N/A                                                                                | No<br>No                                 | No<br>No                                         | N/A<br>N/A                                    |

|--------------------------|-------------------|------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------|-----------------------------------------------|

| I/O                      | Ι                 |                              |                                                                                           | No                                       | No                                               | N/A                                           |

|                          |                   | N/A                          |                                                                                           |                                          |                                                  | 1 1/ 2 1                                      |

| N/A                      |                   |                              | Yes                                                                                       | No                                       | Yes                                              | Yes                                           |

|                          | N/A               | N/A                          | N/A                                                                                       | No                                       | No                                               | N/A                                           |

| I/O                      | Ι                 | N/A                          | Yes                                                                                       | No                                       | Yes                                              | Yes,<br>Programmable                          |

| I/O                      | Ι                 | N/A                          | Yes                                                                                       | No                                       | Yes                                              | Yes,<br>Programmable                          |

| I/O                      | Ι                 | N/A                          | Yes                                                                                       | No                                       | Yes                                              | Yes,<br>Programmable                          |

| I/O                      | Ι                 | N/A                          | Yes                                                                                       | No                                       | Yes                                              | Yes,<br>Programmable                          |

| I/O                      | Ι                 | N/A                          | Yes                                                                                       | No                                       | Yes                                              | Yes,<br>Programmable                          |

| e                        | I/O<br>I/O<br>I/O | VO I<br>VO I<br>VO I<br>VO I | I/O     I     N/A       I/O     I     N/A       I/O     I     N/A       I/O     I     N/A | I/OIN/AYesI/OIN/AYesI/OIN/AYesI/OIN/AYes | I/OIN/AYesNoI/OIN/AYesNoI/OIN/AYesNoI/OIN/AYesNo | I/OIN/AYesNoYesI/OIN/AYesNoYesI/OIN/AYesNoYes |

AF[7:0]—Port Alternate Function enabled

0 = The port pin is in normal mode and the DDx bit in the Port A-H Data Direction subregister determines the direction of the pin.

1 = The alternate function is selected. Port pin operation is controlled by the alternate function.

#### Port A-H Output Control Sub-Registers

The Port A-H Output Control sub-register (Table 17) is accessed through the Port A-H Control register by writing 03H to the Port A-H Address register. Setting the bits in the Port A-H Output Control sub-registers to 1 configures the specified port pins for opendrain operation. These sub-registers affect the pins directly and, as a result, alternate functions are also affected.

| BITS  | 7    | 6            | 5            | 4              | 3             | 2            | 1             | 0    |

|-------|------|--------------|--------------|----------------|---------------|--------------|---------------|------|

| FIELD | POC7 | POC6         | POC5         | POC4           | POC3          | POC2         | POC1          | POC0 |

| RESET | 0    | 0            | 0            | 0              | 0             | 0            | 0             | 0    |

| R/W   | R/W  | R/W          | R/W          | R/W            | R/W           | R/W          | R/W           | R/W  |

| ADDR  |      | If 03H in Po | rt A-H Addre | ss Register, a | ccessible via | Port A-H Cor | trol Register |      |

#### POC[7:0]—Port Output Control

These bits function independently of the alternate function bit and disables the drains if set to 1.

0 = The drains are enabled for any output mode.

1 = The drain of the associated pin is disabled (open-drain mode).

| BITS  | 7      | 6                                                                             | 5      | 4      | 3      | 2      | 1      | 0      |  |  |  |

|-------|--------|-------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|--|--|

| FIELD | PSMRE7 | PSMRE6                                                                        | PSMRE5 | PSMRE4 | PSMRE3 | PSMRE2 | PSMRE1 | PSMRE0 |  |  |  |

| RESET | 0      | 0                                                                             | 0      | 0      | 0      | 0      | 0      | 0      |  |  |  |

| R/W   | R/W    | R/W                                                                           | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |  |  |

| ADDR  |        | If 05H in Port A-H Address Register, accessible via Port A-H Control Register |        |        |        |        |        |        |  |  |  |

#### Table 19. Port A-H STOP Mode Recovery Source Enable Sub-Registers

PSMRE[7:0]—Port STOP Mode Recovery Source Enabled

0 = The Port pin is not configured as a STOP Mode Recovery source. Transitions on this pin during Stop mode do not initiate STOP Mode Recovery.

1 = The Port pin is configured as a STOP Mode Recovery source. Any logic transition on this pin during Stop mode initiates STOP Mode Recovery.

## Port A-H Input Data Registers

Reading from the Port A-H Input Data registers (Table 20) returns the sampled values from the corresponding port pins. The Port A-H Input Data registers are Read-only.

| BITS  | 7    | 6                                              | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|-------|------|------------------------------------------------|------|------|------|------|------|------|--|--|

| FIELD | PIN7 | PIN6                                           | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |  |  |

| RESET | Х    | Х                                              | Х    | Х    | Х    | Х    | Х    | Х    |  |  |

| R/W   | R    | R                                              | R    | R    | R    | R    | R    | R    |  |  |

| ADDR  |      | FD2H, FD6H, FDAH, FDEH, FE2H, FE6H, FEAH, FEEH |      |      |      |      |      |      |  |  |

Table 20. Port A-H Input Data Registers (PxIN)

PIN[7:0]—Port Input Data

Sampled data from the corresponding port pin input.

0 = Input data is logical 0 (Low).

1 = Input data is logical 1 (High).

# **IRQ0 Enable High and Low Bit Registers**

The IRQ0 Enable High and Low Bit registers (Tables 27 and 28) form a priority encoded enabling for interrupts in the Interrupt Request 0 register. Priority is generated by setting bits in each register. Table 26 describes the priority control for IRQ0.

| IRQ0ENH[x] | IRQ0ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

| 1          | 1          | Level 3  | High        |

Table 26. IRQ0 Enable and Priority Encoding

where *x* indicates the register bits from 0 through 7.

Table 27. IRQ0 Enable High Bit Register (IRQ0ENH)

| BITS  | 7     | 6     | 5            | 4             | 3      | 2      | 1      | 0      |  |  |  |

|-------|-------|-------|--------------|---------------|--------|--------|--------|--------|--|--|--|

| FIELD | T2ENH | T1ENH | <b>T0ENH</b> | <b>UORENH</b> | U0TENH | I2CENH | SPIENH | ADCENH |  |  |  |

| RESET | 0     | 0     | 0            | 0             | 0      | 0      | 0      | 0      |  |  |  |

| R/W   | R/W   | R/W   | R/W          | R/W           | R/W    | R/W    | R/W    | R/W    |  |  |  |

| ADDR  |       | FC1H  |              |               |        |        |        |        |  |  |  |

T2ENH—Timer 2 Interrupt Request Enable High Bit T1ENH—Timer 1 Interrupt Request Enable High Bit T0ENH—Timer 0 Interrupt Request Enable High Bit U0RENH—UART 0 Receive Interrupt Request Enable High Bit U0TENH—UART 0 Transmit Interrupt Request Enable High Bit I2CENH—I<sup>2</sup>C Interrupt Request Enable High Bit SPIENH—SPI Interrupt Request Enable High Bit ADCENH—ADC Interrupt Request Enable High Bit

| BITS  | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |  |  |  |

|-------|---------|---------|---------|---------|---------|---------|---------|---------|--|--|--|

| FIELD | PAD7ENH | PAD6ENH | PAD5ENH | PAD4ENH | PAD3ENH | PAD2ENH | PAD1ENH | PAD0ENH |  |  |  |

| RESET | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |  |  |  |

| R/W   | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |  |  |  |

| ADDR  |         | FC4H    |         |         |         |         |         |         |  |  |  |

#### Table 30. IRQ1 Enable High Bit Register (IRQ1ENH)

PAD*x*ENH—Port A or Port D Bit[*x*] Interrupt Request Enable High Bit Refer to the Interrupt Port Select register for selection of either Port A or Port D as the interrupt source.

Table 31. IRQ1 Enable Low Bit Register (IRQ1ENL)

| BITS  | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |  |  |  |

|-------|---------|---------|---------|---------|---------|---------|---------|---------|--|--|--|

| FIELD | PAD7ENL | PAD6ENL | PAD5ENL | PAD4ENL | PAD3ENL | PAD2ENL | PAD1ENL | PAD0ENL |  |  |  |

| RESET | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |  |  |  |

| R/W   | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |  |  |  |

| ADDR  |         | FC5H    |         |         |         |         |         |         |  |  |  |

PADxENL—Port A or Port D Bit[x] Interrupt Request Enable Low Bit Refer to the Interrupt Port Select register for selection of either Port A or Port D as the interrupt source.

# **IRQ2 Enable High and Low Bit Registers**

The IRQ2 Enable High and Low Bit registers (Tables 33 and 34) form a priority encoded enabling for interrupts in the Interrupt Request 2 register. Priority is generated by setting bits in each register. Table 32 describes the priority control for IRQ2.

Table 32. IRQ2 Enable and Priority Encoding

| IRQ2ENH[x] | IRQ2ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

| 1          | 1          | Level 3  | High        |

where *x* indicates the register bits from 0 through 7.

#### Z8F640x/Z8F480x/Z8F320x/Z8F240x/Z8F160x Z8 Encorel<sup>®</sup>

58

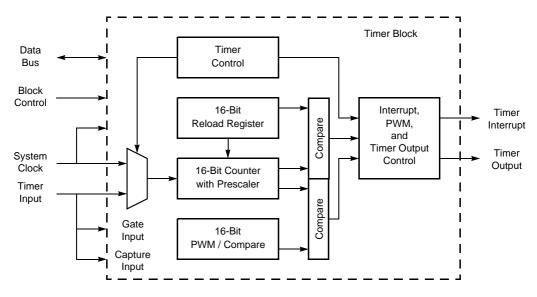

Figure 66. Timer Block Diagram

# Operation

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer rolls over to 0000H and continues counting.

# **Timer Operating Modes**

The timers can be configured to operate in the following modes:

#### **One-Shot Mode**

In One-Shot mode, the timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the Reload value, the timer generates an interrupt and the count value in the Timer High and Low Byte registers is reset to 0001H. Then, the timer is automatically disabled and stops counting.

Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state for one system clock cycle (from Low to High or from High to Low) upon timer Reload. If it is desired to have the Timer Output make a permanent state change upon One-Shot time-

information on approximate time-out delays for the minimum and maximum WDT reload values.

Table 45. Watch-Dog Timer Approximate Time-Out Delays

| WDT Reload Value | WDT Reload Value | * *     | te Time-Out Delay<br>WDT oscillator frequency) |

|------------------|------------------|---------|------------------------------------------------|

| (Hex)            | (Decimal)        | Typical | Description                                    |

| 000004           | 4                | 80µs    | Minimum time-out delay                         |

| FFFFFF           | 16,777,215       | 335.5s  | Maximum time-out delay                         |

#### Watch-Dog Timer Refresh

When first enabled, the Watch-Dog Timer is loaded with the value in the Watch-Dog Timer Reload registers. The Watch-Dog Timer then counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the downcounter to be reloaded with the WDT Reload value stored in the Watch-Dog Timer Reload registers. Counting resumes following the reload operation.

When the Z8F640x family device is operating in Debug Mode (via the On-Chip Debugger), the Watch-Dog Timer is continuously refreshed to prevent spurious Watch-Dog Timer time-outs.

#### Watch-Dog Timer Time-Out Response

The Watch-Dog Timer times out when the counter reaches 000000H. A time-out of the Watch-Dog Timer generates either an interrupt or a Short Reset. The WDT\_RES Option Bit determines the time-out response of the Watch-Dog Timer. Refer to the **Option Bits** chapter for information regarding programming of the WDT\_RES Option Bit.

#### WDT Interrupt in Normal Operation

If configured to generate an interrupt when a time-out occurs, the Watch-Dog Timer issues an interrupt request to the interrupt controller and sets the WDT status bit in the Watch-Dog Timer Control register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watch-Dog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watch-Dog Timer counter rolls over to its maximum value of FFFFFH and continues counting. The Watch-Dog Timer counter is not automatically returned to its Reload Value.

#### WDT Interrupt in Stop Mode

If configured to generate an interrupt when a time-out occurs and the Z8F640x family device is in STOP mode, the Watch-Dog Timer automatically initiates a STOP Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Watch-Dog Timer Control register are set to 1 following WDT time-out in STOP

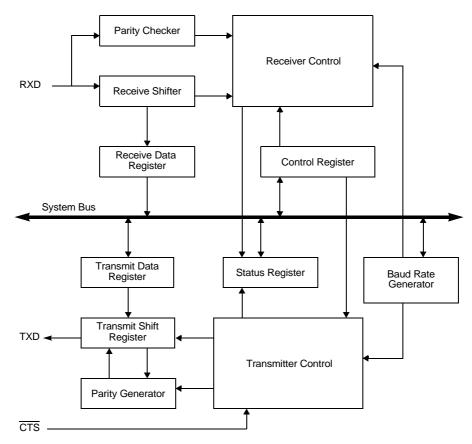

# Operation

#### **Data Format**

The UART always transmits and receives data in an 8-bit data format, least-significant bit first. An even or odd parity bit can be optionally added to the data stream. Each character begins with an active Low Start bit and ends with either 1 or 2 active High Stop bits.

- 5. Check the TDRE bit in the UART Status 0 register to determine if the Transmit Data register is empty (indicated by a 1). If empty, continue to Step 6. If the Transmit Data register is full (indicated by a 0), continue to monitor the TDRE bit until the Transmit Data register becomes available to receive new data.

- 6. Write the data byte to the UART Transmit Data register. The transmitter automatically transfers the data to the Transmit Shift register and transmit the data.

- 7. To transmit additional bits, return to Step 5.

#### Transmitting Data using the Interrupt-Driven Method

The UART Transmitter interrupt indicates the availability of the Transmit Data register to accept new data for transmission. Follow these steps to configure the UART for interrupt-driven data transmission:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the desired baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Transmitter interrupt and set the desired priority.

- 5. Write to the UART Control 1 register to enable Multiprocessor (9-bit) mode functions, if desired.

- 6. Write to the UART Control 0 register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission

- Enable parity, if desired, and select either even or odd parity.

- Set or clear the CTSE bit to enable or disable control from the receiver via the  $\overline{\text{CTS}}$  pin.

- 7. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data transmission. When the UART Transmit interrupt is detected, the associated interrupt service routine (ISR) should perform the following:

- 8. Write the data byte to the UART Transmit Data register. The transmitter will automatically transfer the data to the Transmit Shift register and transmit the data.

- 9. Clear the UART Transmit interrupt bit in the applicable Interrupt Request register.

- 10. Execute the IRET instruction to return from the interrupt-service routine and wait for the Transmit Data register to again become empty.

Table 76 provides an example of the Register File addresses if the DMA\_ADC Address register contains the value 72H.

| ADC Analog Input | Register File Address (Hex) <sup>1</sup> |

|------------------|------------------------------------------|

| 0                | 720H-721H                                |

| 1                | 722H-723H                                |

| 2                | 724H-725H                                |

| 3                | 726H-727H                                |

| 4                | 728H-729H                                |

| 5                | 72AH-72BH                                |

| 6                | 72CH-72DH                                |

| 7                | 72EH-72FH                                |

| 8                | 730H-731H                                |

| 9                | 732H-733H                                |

| 10               | 734H-735H                                |

| 11               | 736H-737H                                |

| 1                |                                          |

Table 76. DMA\_ADC Register File Address Example

<sup>1</sup> DMAA\_ADDR set to 72H.

Table 77. DMA\_ADC Address Register (DMAA\_ADDR)

| BITS  | 7         | 6   | 5   | 4   | 3   | 2   | 1        | 0   |

|-------|-----------|-----|-----|-----|-----|-----|----------|-----|

| FIELD | DMAA_ADDR |     |     |     |     |     | Reserved |     |

| RESET | Х         | Х   | Х   | Х   | Х   | Х   | Х        | Х   |

| R/W   | R/W       | R/W | R/W | R/W | R/W | R/W | R/W      | R/W |

| ADDR  | FBDH      |     |     |     |     |     |          |     |

#### DMAA\_ADDR—DMA\_ADC Address

These bits specify the seven most-significant bits of the 12-bit Register File addresses used for storing the ADC output data. The ADC Analog Input Number defines the five least-significant bits of the Register File address. Full 12-bit address is {DMAA\_ADDR[7:1], 4-bit ADC Analog Input Number, 0}.

Reserved This bit is reserved and must be 0.

ister. When the Watchpoint event occurs, the Z8F640x family device enters Debug mode and the DBGMODE bit in the OCDCTL register becomes 1.

#### **Runtime Counter**

The On-Chip Debugger contains a 16-bit Runtime Counter. It counts system clock cycles between Breakpoints. The counter starts counting when the On-Chip Debugger leaves Debug mode and stops counting when it enters Debug mode again or when it reaches the maximum count of FFFFH.

# **On-Chip Debugger Commands**

The host communicates to the On-Chip Debugger by sending OCD commands using the DBG interface. During normal operation of the Z8F640x family device, only a subset of the OCD commands are available. In Debug mode, all OCD commands become available unless the user code and control registers are protected by programming the Read Protect Option Bit (RP). The Read Protect Option Bit prevents the code in memory from being read out of the Z8F640x family device. When this option is enabled, several of the OCD commands are disabled. Table 93 contains a summary of the On-Chip Debugger commands. Each OCD command is described in further detail in the bulleted list following Table 93. Table 93 indicates those commands that operate when the Z8F640x family device is not in Debug mode (normal operation) and those commands that are disabled by programming the Read Protect Option Bit.

| Debug Command              | Command Byte | Enabled when NOT in Debug mode? | Disabled by<br>Read Protect Option Bit                                                                                                                                    |

|----------------------------|--------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read OCD Revision          | 00H          | Yes                             | -                                                                                                                                                                         |

| Reserved                   | 01H          | -                               | -                                                                                                                                                                         |

| Read OCD Status Register   | 02H          | Yes                             | -                                                                                                                                                                         |

| Read Runtime Counter       | 03H          | -                               | -                                                                                                                                                                         |

| Write OCD Control Register | 04H          | Yes                             | Cannot clear DBGMODE bit                                                                                                                                                  |

| Read OCD Control Register  | 05H          | Yes                             | -                                                                                                                                                                         |

| Write Program Counter      | 06H          | -                               | Disabled                                                                                                                                                                  |

| Read Program Counter       | 07H          | -                               | Disabled                                                                                                                                                                  |

| Write Register             | 08H          | -                               | Only writes of the Flash Memory Control<br>registers are allowed. Additionally, only the<br>Mass Erase command is allowed to be<br>written to the Flash Control register. |

| Read Register              | 09H          | -                               | Disabled                                                                                                                                                                  |

#### Table 93. On-Chip Debugger Commands

# **On-Chip Oscillator**

The Z8F640x family devices feature an on-chip oscillator for use with an external 1-20MHz crystal. This oscillator generates the primary system clock for the internal eZ8 CPU and the majority of the on-chip peripherals. Alternatively, the X<sub>IN</sub> input pin can also accept a CMOS-level clock input signal (32kHz-20MHz). If an external clock generator is used, the X<sub>OUT</sub> pin must be left unconnected. The Z8F640x family device does *not* contain in internal clock divider. The frequency of the signal on the X<sub>IN</sub> input pin determines the frequency of the system clock. The Z8F640x family device on-chip oscillator does not support external RC networks or ceramic resonators.

# 20MHz Crystal Oscillator Operation

Figure 90 illustrates a recommended configuration for connection with an external 20MHz, fundamental-mode, parallel-resonant crystal. Recommended crystal specifications are provided in Table 99. Resistor R<sub>1</sub> limits total power dissipation by the crystal. Printed circuit board layout should add no more than 4pF of stray capacitance to either the X<sub>IN</sub> or X<sub>OUT</sub> pins. If oscillation does not occur, reduce the values of capacitors C<sub>1</sub> and C<sub>2</sub> to decrease loading.

# **AC Characteristics**

The section provides information on the AC characteristics and timing of the Z8 Encore!<sup>TM</sup>. All AC timing information assumes a standard load of 50pF on all outputs.

## Table 102. AC Characteristics

|                     |                              | $V_{DD} = 3.0 - 3.6V$<br>$T_A = -40^{\circ}C$ to $105^{\circ}C$ |         |       |                                                                                                       |

|---------------------|------------------------------|-----------------------------------------------------------------|---------|-------|-------------------------------------------------------------------------------------------------------|

| Symbol              | Parameter                    | Minimum                                                         | Maximum | Units | Conditions                                                                                            |

| F <sub>sysclk</sub> | System Clock Frequency       | -                                                               | 20.0    | MHz   | Read-only from Flash memory.                                                                          |

|                     |                              | 0.032768                                                        | 20.0    | MHz   | Program or erasure of the Flash memory.                                                               |

| F <sub>XTAL</sub>   | Crystal Oscillator Frequency | 1.0                                                             | 20.0    | MHz   | System clock frequencies below<br>the crystal oscillator minimum<br>require an external clock driver. |

| T <sub>XIN</sub>    | System Clock Period          | 50                                                              | -       | ns    | $T_{CLK} = 1/F_{sysclk}$                                                                              |

| T <sub>XINH</sub>   | System Clock High Time       | 20                                                              | 30      | ns    | T <sub>CLK</sub> = 50ns                                                                               |

| T <sub>XINL</sub>   | System Clock Low Time        | 20                                                              | 30      | ns    | T <sub>CLK</sub> = 50ns                                                                               |

| T <sub>XINR</sub>   | System Clock Rise Time       | -                                                               | 3       | ns    | T <sub>CLK</sub> = 50ns                                                                               |

| T <sub>XINF</sub>   | System Clock Fall Time       | -                                                               | 3       | ns    | T <sub>CLK</sub> = 50ns                                                                               |

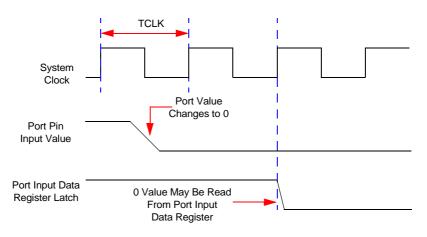

# General Purpose I/O Port Input Data Sample Timing

Figure 93 illustrates timing of the GPIO Port input sampling. The input value on a GPIO Port pin is sampled on the rising edge of the system clock. The Port value is then available to the eZ8 CPU on the second rising clock edge following the change of the Port value.

#### Figure 93. Port Input Sample Timing

#### **Table 107. GPIO Port Input Timing**

|                     |                                                                                                       | Dela    | y (ns)  |

|---------------------|-------------------------------------------------------------------------------------------------------|---------|---------|

| Parameter           | Abbreviation                                                                                          | Minimum | Maximum |

| T <sub>S_PORT</sub> | Port Input Transition to XIN Rise Setup Time<br>(Not pictured)                                        | 5       | -       |

| T <sub>H_PORT</sub> | XIN Rise to Port Input Transition Hold Time<br>(Not pictured)                                         | 5       | -       |

| T <sub>SMR</sub>    | GPIO Port Pin Pulse Width to Insure Stop Mode Recovery<br>(for GPIO Port Pins enabled as SMR sources) | 1µs     |         |

| Notation | Description                    | Operand | Range                                                                                                                     |

|----------|--------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------|

| b        | Bit                            | b       | b represents a value from 0 to 7 (000B to 111B).                                                                          |

| сс       | Condition Code                 | —       | See Condition Codes overview in the eZ8 CPU User Manual.                                                                  |

| DA       | Direct Address                 | Addrs   | Addrs. represents a number in the range of 0000H to FFFFH                                                                 |

| ER       | Extended Addressing Register   | Reg     | Reg. represents a number in the range of 000H to FFFH                                                                     |

| IM       | Immediate Data                 | #Data   | Data is a number between 00H to FFH                                                                                       |

| Ir       | Indirect Working Register      | @Rn     | n = 0 - 15                                                                                                                |

| IR       | Indirect Register              | @Reg    | Reg. represents a number in the range of 00H to FFH                                                                       |

| Irr      | Indirect Working Register Pair | @RRp    | p = 0, 2, 4, 6, 8, 10, 12, or 14                                                                                          |

| IRR      | Indirect Register Pair         | @Reg    | Reg. represents an even number in the range 00H to FEH                                                                    |

| p        | Polarity                       | р       | Polarity is a single bit binary value of either 0B or 1B.                                                                 |

| r        | Working Register               | Rn      | n = 0 - 15                                                                                                                |

| R        | Register                       | Reg     | Reg. represents a number in the range of 00H to FFH                                                                       |

| RA       | Relative Address               | Х       | X represents an index in the range of $+127$ to $-128$ which is an offset relative to the address of the next instruction |

| rr       | Working Register Pair          | RRp     | p = 0, 2, 4, 6, 8, 10, 12, or 14                                                                                          |

| RR       | Register Pair                  | Reg     | Reg. represents an even number in the range of 00H to FEH                                                                 |

| Vector   | Vector Address                 | Vector  | Vector represents a number in the range of 00H to FFH                                                                     |

| X        | Indexed                        | #Index  | The register or register pair to be indexed is offset by<br>the signed Index value (#Index) in a +127 to -128<br>range.   |

#### Table 115. Notational Shorthand

Table 116 contains additional symbols that are used throughout the Instruction Summary and Instruction Set Description sections.

# Z8F640x/Z8F480x/Z8F320x/Z8F240x/Z8F160x Z8 Encore!®

205

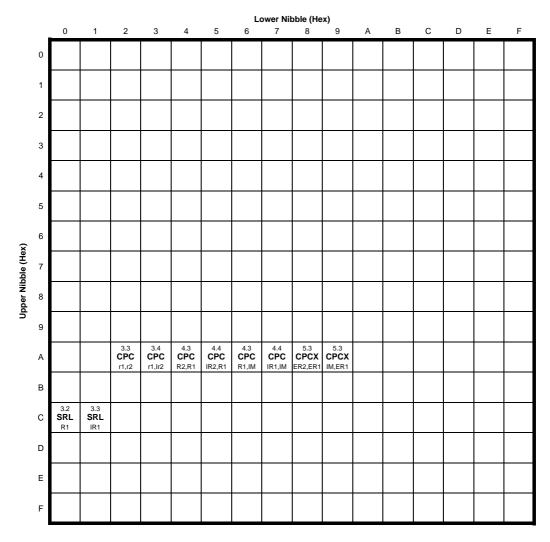

Figure 102. Second Opcode Map after 1FH