#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 46                                                        |

| Program Memory Size        | 16KB (16K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                |                                                           |

| RAM Size                   | 2K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 12x10b                                                |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 68-LCC (J-Lead)                                           |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1602vs020ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

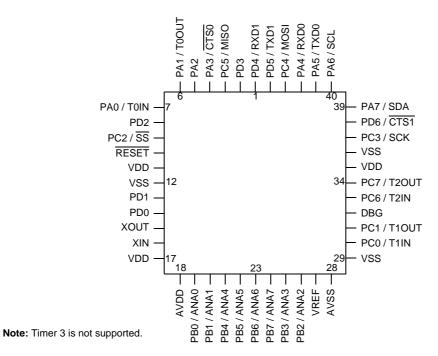

Figure 57. Z8Fxx01 in 44-Pin Plastic Leaded Chip Carrier (PLCC)

| BITS  | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|-------|---------|---------|---------|---------|---------|---------|---------|---------|

| FIELD | PAD7ENH | PAD6ENH | PAD5ENH | PAD4ENH | PAD3ENH | PAD2ENH | PAD1ENH | PAD0ENH |

| RESET | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| R/W   | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |

| ADDR  |         | FC4H    |         |         |         |         |         |         |

#### Table 30. IRQ1 Enable High Bit Register (IRQ1ENH)

PAD*x*ENH—Port A or Port D Bit[*x*] Interrupt Request Enable High Bit Refer to the Interrupt Port Select register for selection of either Port A or Port D as the interrupt source.

Table 31. IRQ1 Enable Low Bit Register (IRQ1ENL)

| BITS  | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|-------|---------|---------|---------|---------|---------|---------|---------|---------|

| FIELD | PAD7ENL | PAD6ENL | PAD5ENL | PAD4ENL | PAD3ENL | PAD2ENL | PAD1ENL | PAD0ENL |

| RESET | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| R/W   | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |

| ADDR  |         | FC5H    |         |         |         |         |         |         |

PADxENL—Port A or Port D Bit[x] Interrupt Request Enable Low Bit Refer to the Interrupt Port Select register for selection of either Port A or Port D as the interrupt source.

### **IRQ2 Enable High and Low Bit Registers**

The IRQ2 Enable High and Low Bit registers (Tables 33 and 34) form a priority encoded enabling for interrupts in the Interrupt Request 2 register. Priority is generated by setting bits in each register. Table 32 describes the priority control for IRQ2.

Table 32. IRQ2 Enable and Priority Encoding

| IRQ2ENH[x] | IRQ2ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

| 1          | 1          | Level 3  | High        |

where *x* indicates the register bits from 0 through 7.

#### **Timer 0-3 Control Registers**

The Timer 0-3 Control (TxCTL) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode.

BITS 7 4 3 2 1 0 6 5 TEN TPOL PRES TMODE FIELD 0 0 0 0 0 0 0 0 RESET R/W R/W R/W R/W R/W R/W R/W R/W R/W F07H, F0FH, F17H, F1FH ADDR

Table 44. Timer 0-3 Control Register (TxCTL)

TEN-Timer Enable

0 = Timer is disabled.

1 = Timer enabled to count.

TPOL-Timer Input/Output Polarity

Operation of this bit is a function of the current operating mode of the timer.

#### **One-Shot mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **Continuous mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **Counter mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **PWM mode**

0 = Timer Output is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload.

1 = Timer Output is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload.

| BITS  | 7        | 6 | 5 | 4       | 3      | 2 | 1 | 0    |

|-------|----------|---|---|---------|--------|---|---|------|

| FIELD | Reserved |   |   |         |        |   |   | MPRX |

| RESET | 0        | 0 | 0 | 0       | 0      | 0 | 0 | 0    |

| R/W   | R        | R | R | R       | R      | R | R | R    |

| ADDR  |          |   |   | F44H ar | d F4CH |   |   |      |

#### Table 53. UARTx Status 1 Register (UxSTAT1)

Reserved

These bits are reserved and must be 0.

MPRX—Multiprocessor Receive

This status bit is for the receiver and reflects the actual status of the last multiprocessor bit received. Reading from the UART Data register resets this bit to 0.

## UARTx Control 0 and Control 1 Registers

The UART*x* Control 0 and Control 1 registers (Tables 54 and 55) configure the properties of the UART's transmit and receive operations. The UART Control registers must ben be written while the UART is enabled.

| BITS  | 7   | 6             | 5    | 4   | 3    | 2    | 1    | 0    |

|-------|-----|---------------|------|-----|------|------|------|------|

| FIELD | TEN | REN           | CTSE | PEN | PSEL | SBRK | STOP | LBEN |

| RESET | 0   | 0             | 0    | 0   | 0    | 0    | 0    | 0    |

| R/W   | R/W | R/W           | R/W  | R/W | R/W  | R/W  | R/W  | R/W  |

| ADDR  |     | F42H and F4AH |      |     |      |      |      |      |

Table 54. UARTx Control 0 Register (UxCTL0)

TEN—Transmit Enable

This bit enables or disables the transmitter. The enable is also controlled by the  $\overline{\text{CTS}}$  signal and the CTSE bit. If the  $\overline{\text{CTS}}$  signal is low and the CTSE bit is 1, the transmitter is enabled.

0 = Transmitter disabled.

1 = Transmitter enabled.

REN—Receive Enable

This bit enables or disables the receiver.

- 0 = Receiver disabled.

- 1 =Receiver enabled.

CTSE—CTS Enable 0 = The CTS signal has no effect on the transmitter.

1 = The UART recognizes the  $\overline{\text{CTS}}$  signal as an enable control from the transmitter.

PEN—Parity Enable

This bit enables or disables parity. Even or odd is determined by the PSEL bit.

0 = Parity is disabled.

1 = The transmitter sends data with an additional parity bit and the receiver receives an additional parity bit.

PSEL—Parity Select

0 = Even parity is transmitted and expected on all received data.

1 = Odd parity is transmitted and expected on all received data.

SBRK-Send Break

This bit pauses or breaks data transmission. Sending a break interrupts any transmission in progress, so insure that the transmitter has finished sending data before setting this bit.

0 = No break is sent.

1 = The output of the transmitter is zero.

STOP-Stop Bit Select

0 = The transmitter sends one stop bit.

1 = The transmitter sends two stop bits.

LBEN—Loop Back Enable

0 = Normal operation.

1 = All transmitted data is looped back to the receiver.

BITS 7 6 5 4 3 2 1 0 RDAIRQ BIRQ MPM MPE MPBT Reserved IREN FIELD 0 0 0 0 0 0 0 0 RESET R/W R/W R/W R/W R/W R/W R/W R/W R/W F43H and F4BH ADDR

Table 55. UARTx Control 1 Register (UxCTL1)

BIRQ-Baud Rate Generator Interrupt Request

This bit sets an interrupt request when the Baud Rate Generator times out and is only set if a UART is not enabled. The is bit produces no effect when the UART is enabled.

0 = Interrupts behave as set by UART control.

1 = The Baud Rate Generator generates a receive interrupt when it counts down to zero.

MPM—Multiprocessor (9-bit) mode Select

This bit is used to enable Multiprocessor (9-bit) mode.

## Operation

When the Infrared Endec is enabled, the transmit data from the associated on-chip UART is encoded as digital signals in accordance with the IrDA standard and output to the infrared transceiver via the TXD pin. Likewise, data received from the infrared transceiver is passed to the Infrared Endec via the RXD pin, decoded by the Infrared Endec, and then passed to the UART. Communication is half-duplex, which means simultaneous data transmission and reception is not allowed.

The baud rate is set by the UART's Baud Rate Generator and supports IrDA standard baud rates from 9600 baud to 115.2 kbaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled to use the Infrared Endec. The Infrared Endec data rate is calculated using the following equation:

# Infrared Data Rate (bits/s) = $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

#### **Transmitting IrDA Data**

The data to be transmitted using the infrared transceiver is first sent to the UART. The UART's transmit signal (TXD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drives the infrared transceiver. Each UART/Infrared data bit is 16-clocks wide. If the data to be transmitted is 1, the IR\_TXD signal remains low for the full 16-clock period. If the data to be transmitted is 0, a 3-clock high pulse is output following a 7-clock low period. After the 3-clock high pulse, a 6-clock low pulse is output to complete the full 16-clock data period. Figure 72 illustrates IrDA data transmission. When the Infrared Endec is enabled, the UART's TXD signal is internal to the Z8F640x family device while the IR\_TXD signal is output through the TXD pin.

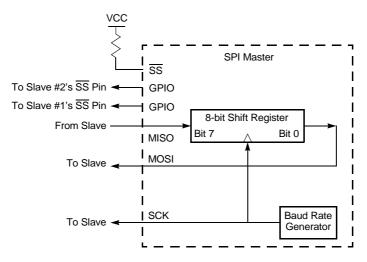

Figure 75. SPI Configured as a Master in a Single Master, Multiple Slave System

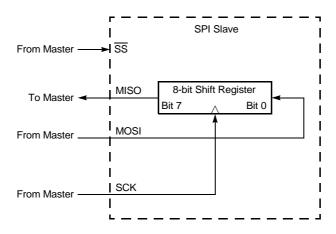

Figure 76. SPI Configured as a Slave

## Operation

The SPI is a full-duplex, synchronous, character-oriented channel that supports a four-wire interface (serial clock, transmit, receive and Slave select). The SPI block consists of trans-

The Master and Slave are each capable of exchanging a byte of data during a sequence of eight clock cycles. In both Master and Slave SPI devices, data is shifted on one edge of the SCK and is sampled on the opposite edge where data is stable. Edge polarity is determined by the SPI phase and polarity control.

#### **Slave Select**

The active Low Slave Select  $(\overline{SS})$  input signal is used to select a Slave SPI device.  $\overline{SS}$  must be Low prior to all data communication to and from the Slave device.  $\overline{SS}$  must stay Low for the full duration of each character transferred. The  $\overline{SS}$  signal may stay Low during the transfer of multiple characters or may deassert between each character.

When the SPI on the Z8F640x family device is configured as the only Master in an SPI system, the  $\overline{SS}$  pin can be set as either an input or an output. For communication between the Z8F640x family device SPI Master and external Slave devices, the  $\overline{SS}$  signal, as an output, can assert the  $\overline{SS}$  input pin on one of the Slave devices. Other GPIO output pins can also be employed to select external SPI Slave devices.

When the SPI on the Z8F640x family device is configured as one Master in a multi-master SPI system, the  $\overline{SS}$  pin on the should be set as an input. The  $\overline{SS}$  input signal on the Master must be High. If the  $\overline{SS}$  signal goes Low (indicating another Master is driving the SPI bus), a Mode Fault error flag is set in the SPI Status register.

### **SPI Clock Phase and Polarity Control**

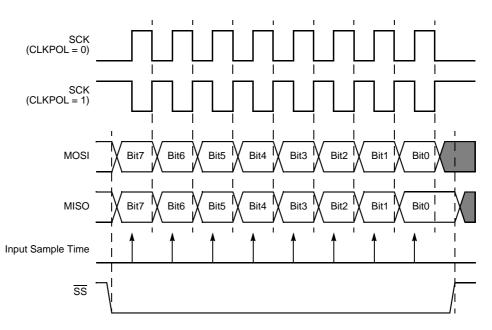

The SPI supports four combinations of serial clock phase and polarity using two bits in the SPI Control register. The clock polarity bit, CLKPOL, selects an active high or active low clock and has no effect on the transfer format. Table 59 lists the SPI Clock Phase and Polarity Operation parameters. The clock phase bit, PHASE, selects one of two fundamentally different transfer formats. For proper data transmission, the clock phase and polarity must be identical for the SPI Master and the SPI Slave. The Master always places data on the MOSI line a half-cycle before the clock edge (SCK signal), in order for the Slave to latch the data.

| PHASE | CLKPOL | SCK<br>Transmit<br>Edge | SCK<br>Receive<br>Edge | SCK<br>Idle<br>State |

|-------|--------|-------------------------|------------------------|----------------------|

| 0     | 0      | Falling                 | Rising                 | Low                  |

| 0     | 1      | Rising                  | Falling                | High                 |

| 1     | 0      | Rising                  | Falling                | Low                  |

| 1     | 1      | Falling                 | Rising                 | High                 |

| Table 59. SPI Clock Phase  | (PHASE)      | and Clock Polarit | v (CLKPOL) Operation   |

|----------------------------|--------------|-------------------|------------------------|

| Tuble 57. BIT Clock I hase | (1 111 10 1) | and Clock I blain | y (Chill Oh) Operation |

#### Transfer Format PHASE Equals Zero

Figure 77 illustrates the timing diagram for an SPI transfer in which PHASE is cleared to 0. The two SCK waveforms show polarity with CLKPOL reset to 0 and with CLKPOL set to one. The diagram may be interpreted as either a Master or Slave timing diagram since the SCK Master-In/Slave-Out (MISO) and Master-Out/Slave-In (MOSI) pins are directly connected between the Master and the Slave.

Figure 77. SPI Timing When PHASE is 0

#### Transfer Format PHASE Equals One

Figure 78 illustrates the timing diagram for an SPI transfer in which PHASE is one. Two waveforms are depicted for SCK, one for CLKPOL reset to 0 and another for CLKPOL set to 1.

If the current ADC Analog Input is not the highest numbered input to be converted, DMA\_ADC initiates data conversion in the next higher numbered ADC Analog Input.

## Configuring DMA\_ADC for Data Transfer

Follow these steps to configure and enable DMA\_ADC:

- 1. Write the DMA\_ADC Address register with the 7 most-significant bits of the Register File address for data transfers.

- 2. Write to the DMA\_ADC Control register to complete the following:

- Enable the DMA\_ADC interrupt request, if desired

- Select the number of ADC Analog Inputs to convert

- Enable the DMA\_ADC channel

**Caution:** When using the DMA\_ADC to perform conversions on multiple ADC inputs and the ADC\_IN field in the DMA\_ADC Control Register is greater than 000b, the Analog-to-Digital Converter must be configured for Single-Shot mode.

Continuous mode operation of the ADC can **only** be used in conjunction with DMA\_ADC if the ADC\_IN field in the DMA\_ADC Control Register is reset to 000b to enable conversion on ADC Analog Input 0 only.

## **DMA Control Register Definitions**

### DMAx Control Register

The DMAx Control register is used to enable and select the mode of operation for DMAx.

| BITS  | 7   | 6          | 5    | 4     | 3    | 2   | 1   | 0   |

|-------|-----|------------|------|-------|------|-----|-----|-----|

| FIELD | DEN | DLE        | DDIR | IRQEN | WSEL |     | RSS |     |

| RESET | 0   | 0          | 0    | 0     | 0    | 0   | 0   | 0   |

| R/W   | R/W | R/W        | R/W  | R/W   | R/W  | R/W | R/W | R/W |

| ADDR  |     | FB0H, FB8H |      |       |      |     |     |     |

Table 71. DMAx Control Register (DMAxCTL)

DEN—DMAx Enable

0 = DMAx is disabled and data transfer requests are disregarded.

ZILOG

# Analog-to-Digital Converter

## Overview

The Analog-to-Digital Converter (ADC) converts an analog input signal to a 10-bit binary number. The features of the sigma-delta ADC include:

- 12 analog input sources are multiplexed with general-purpose I/O ports

- Interrupt upon conversion complete

- Internal voltage reference generator

- Direct Memory Access (DMA) controller can automatically initiate data conversion and transfer of the data from 1 to 12 of the analog inputs.

## Architecture

Figure 83 illustrates the three major functional blocks (converter, analog multiplexer, and voltage reference generator) of the ADC. The ADC converts an analog input signal to its digital representation. The 12-input analog multiplexer selects one of the 12 analog input sources. The ADC requires an input reference voltage for the conversion. The voltage reference for the conversion may be input through the external VREF pin or generated internally by the voltage reference generator.

- Power-on reset

- Voltage Brownout reset

- Asserting the  $\overline{\text{RESET}}$  pin Low to initiate a Reset.

- Driving the DBG pin Low while the Z8F640x family device is in Stop mode initiates a System Reset.

### **OCD Data Format**

The OCD interface uses the asynchronous data format defined for RS-232. Each character is transmitted as 1 Start bit, 8 data bits (least-significant bit first), and 1.5 Stop bits (Figure 89)

| START         D0         D1         D2         D3         D4         D5         D6         D7 | STOP |

|-----------------------------------------------------------------------------------------------|------|

|-----------------------------------------------------------------------------------------------|------|

#### Figure 89. OCD Data Format

#### **OCD Auto-Baud Detector/Generator**

To run over a range of baud rates (data bits per second) with various system clock frequencies, the On-Chip Debugger has an Auto-Baud Detector/Generator. After a reset, the OCD is idle until it receives data. The OCD requires that the first character sent from the host is the character 80H. The character 80H has eight continuous bits Low (one Start bit plus 7 data bits). The Auto-Baud Detector measures this period and sets the OCD Baud Rate Generator accordingly.

The Auto-Baud Detector/Generator is clocked by the Z8F640x family device system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation, the maximum recommended baud rate is the system clock frequency divided by 8. The theoretical maximum baud rate is the system clock frequency divided by 4. This theoretical maximum is possible for low noise designs with clean signals. Table 92 lists minimum and recommended maximum baud rates for sample crystal frequencies.

| System Clock Frequency<br>(MHz) | Recommended Maximum Baud Rate<br>(kbits/s) | Minimum Baud Rate<br>(kbits/s) |

|---------------------------------|--------------------------------------------|--------------------------------|

| 20.0                            | 2500                                       | 39.1                           |

| 1.0                             | 125.0                                      | 1.96                           |

| 0.032768 (32KHz)                | 4.096                                      | 0.064                          |

#### Table 92. OCD Baud-Rate Limits

ister. When the Watchpoint event occurs, the Z8F640x family device enters Debug mode and the DBGMODE bit in the OCDCTL register becomes 1.

#### **Runtime Counter**

The On-Chip Debugger contains a 16-bit Runtime Counter. It counts system clock cycles between Breakpoints. The counter starts counting when the On-Chip Debugger leaves Debug mode and stops counting when it enters Debug mode again or when it reaches the maximum count of FFFFH.

## **On-Chip Debugger Commands**

The host communicates to the On-Chip Debugger by sending OCD commands using the DBG interface. During normal operation of the Z8F640x family device, only a subset of the OCD commands are available. In Debug mode, all OCD commands become available unless the user code and control registers are protected by programming the Read Protect Option Bit (RP). The Read Protect Option Bit prevents the code in memory from being read out of the Z8F640x family device. When this option is enabled, several of the OCD commands are disabled. Table 93 contains a summary of the On-Chip Debugger commands. Each OCD command is described in further detail in the bulleted list following Table 93. Table 93 indicates those commands that operate when the Z8F640x family device is not in Debug mode (normal operation) and those commands that are disabled by programming the Read Protect Option Bit.

| Debug Command              | Command Byte | Enabled when NOT in Debug mode? | Disabled by<br>Read Protect Option Bit                                                                                                                                    |

|----------------------------|--------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read OCD Revision          | 00H          | Yes                             | -                                                                                                                                                                         |

| Reserved                   | 01H          | -                               | -                                                                                                                                                                         |

| Read OCD Status Register   | 02H          | Yes                             | -                                                                                                                                                                         |

| Read Runtime Counter       | 03H          | -                               | -                                                                                                                                                                         |

| Write OCD Control Register | 04H          | Yes                             | Cannot clear DBGMODE bit                                                                                                                                                  |

| Read OCD Control Register  | 05H          | Yes                             | -                                                                                                                                                                         |

| Write Program Counter      | 06H          | -                               | Disabled                                                                                                                                                                  |

| Read Program Counter       | 07H          | -                               | Disabled                                                                                                                                                                  |

| Write Register             | 08H          | -                               | Only writes of the Flash Memory Control<br>registers are allowed. Additionally, only the<br>Mass Erase command is allowed to be<br>written to the Flash Control register. |

| Read Register              | 09H          | -                               | Disabled                                                                                                                                                                  |

#### Table 93. On-Chip Debugger Commands

```

DBG <-- 03H

DBG --> RuntimeCounter[15:8]

DBG --> RuntimeCounter[7:0]

```

• Write OCD Control Register (04H)—The Write OCD Control Register command writes the data that follows to the OCDCTL register. When the Read Protect Option Bit is enabled, the DBGMODE bit (OCDCTL[7]) can only be set to 1, it cannot be cleared to 0 and the only method of putting the Z8F640x family device back into normal operating mode is to reset the device.

```

DBG <-- 04H

DBG <-- OCDCTL[7:0]

```

• **Read OCD Control Register (05H)**—The Read OCD Control Register command reads the value of the OCDCTL register.

```

DBG <-- 05H

DBG --> OCDCTL[7:0]

```

• Write Program Counter (06H)—The Write Program Counter command writes the data that follows to the eZ8 CPU's Program Counter (PC). If the Z8F640x family device is not in Debug mode or if the Read Protect Option Bit is enabled, the Program Counter (PC) values are discarded.

```

DBG <-- 06H

DBG <-- ProgramCounter[15:8]

DBG <-- ProgramCounter[7:0]

```

• **Read Program Counter (07H)**—The Read Program Counter command reads the value in the eZ8 CPU's Program Counter (PC). If the Z8F640x family device is not in Debug mode or if the Read Protect Option Bit is enabled, this command returns FFFFH.

```

DEG <-- 07H

DEG --> ProgramCounter[15:8]

DEG --> ProgramCounter[7:0]

```

• Write Register (08H)—The Write Register command writes data to the Register File. Data can be written 1-256 bytes at a time (256 bytes can be written by setting size to zero). If the Z8F640x family device is not in Debug mode, the address and data values are discarded. If the Read Protect Option Bit is enabled, then only writes to the Flash Control Registers are allowed and all other register write data values are discarded.

```

DBG <-- 08H

DBG <-- {4'h0,Register Address[11:8]}

DBG <-- Register Address[7:0]

DBG <-- Size[7:0]

DBG <-- 1-256 data bytes

```

• **Read Register (09H)**—The Read Register command reads data from the Register File. Data can be read 1-256 bytes at a time (256 bytes can be read by setting size to

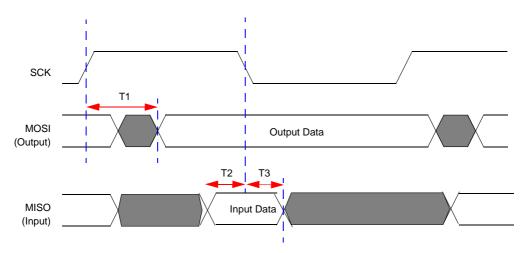

### **SPI Master Mode Timing**

Figure 96 and Table 110 provide timing information for SPI Master mode pins. Timing is shown with SCK rising edge used to source MOSI output data, SCK falling edge used to sample MISO input data. Timing on the SS output pin(s) is controlled by software.

Figure 96. SPI Master Mode Timing

| Table | 110. | SPI | Master | Mode | Timing |

|-------|------|-----|--------|------|--------|

|-------|------|-----|--------|------|--------|

|                |                                             | Delay (ns) |         |  |  |  |

|----------------|---------------------------------------------|------------|---------|--|--|--|

| Parameter      | Abbreviation                                | Minimum    | Maximum |  |  |  |

| T <sub>1</sub> | SCK Rise to MOSI output Valid Delay         | -5         | +5      |  |  |  |

| T <sub>2</sub> | MISO input to SCK (receive edge) Setup Time | 20         |         |  |  |  |

| T <sub>3</sub> | MISO input to SCK (receive edge) Hold Time  | 0          |         |  |  |  |

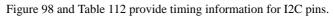

# I<sup>2</sup>C Timing

## Figure 98. I<sup>2</sup>C Timing

| Table | 112. | I <sup>2</sup> C | Timing |

|-------|------|------------------|--------|

|-------|------|------------------|--------|

|                |                                         | Delay (ns)      |

|----------------|-----------------------------------------|-----------------|

| Parameter      | Abbreviation                            | Minimum Maximum |

| T <sub>1</sub> | SCL Fall to SDA output delay            | SCL period/4    |

| T <sub>2</sub> | SDA Input to SCL rising edge Setup Time | 0               |

| T <sub>3</sub> | SDA Input to SCL falling edge Hold Time | 0               |

| Assembly        | Symbolic Operation                                                                                                         | Addres | Address Mode |                                 | Flags |   |   |   |   |   | – Fetch | Instr |

|-----------------|----------------------------------------------------------------------------------------------------------------------------|--------|--------------|---------------------------------|-------|---|---|---|---|---|---------|-------|

| Mnemonic        |                                                                                                                            | dst    | src          | Opcode(s)<br>(Hex)              | С     | Z | S | V | D | Н | Cycles  |       |

| LDX dst, src    | dst ← src                                                                                                                  | r      | ER           | 84                              | -     | - | - | - | - | - | 3       | 2     |

|                 |                                                                                                                            | Ir     | ER           | 85                              | -     |   |   |   |   |   | 3       | 3     |

|                 |                                                                                                                            | R      | IRR          | 86                              | -     |   |   |   |   |   | 3       | 4     |

|                 |                                                                                                                            | IR     | IRR          | 87                              | -     |   |   |   |   |   | 3       | 5     |

|                 |                                                                                                                            | r      | X(rr)        | 88                              | -     |   |   |   |   |   | 3       | 4     |

|                 |                                                                                                                            | X(rr)  | r            | 89                              | -     |   |   |   |   |   | 3       | 4     |

|                 |                                                                                                                            | ER     | r            | 94                              | -     |   |   |   |   |   | 3       | 2     |

|                 |                                                                                                                            | ER     | Ir           | 95                              | -     |   |   |   |   |   | 3       | 3     |

|                 |                                                                                                                            | IRR    | R            | 96                              | -     |   |   |   |   |   | 3       | 4     |

|                 |                                                                                                                            | IRR    | IR           | 97                              | -     |   |   |   |   |   | 3       | 5     |

|                 |                                                                                                                            | ER     | ER           | E8                              | -     |   |   |   |   |   | 4       | 2     |

|                 |                                                                                                                            | ER     | IM           | E9                              | -     |   |   |   |   |   | 4       | 2     |

| LEA dst, X(src) | $dst \leftarrow src + X$                                                                                                   | r      | X(r)         | 98                              | -     | - | - | - | - | - | 3       | 3     |

|                 |                                                                                                                            | rr     | X(rr)        | 99                              | -     |   |   |   |   |   | 3       | 5     |

| MULT dst        | dst[15:0] ←<br>dst[15:8] * dst[7:0]                                                                                        | RR     |              | F4                              | -     | - | - | - | - | - | 2       | 8     |

| NOP             | No operation                                                                                                               |        |              | 0F                              | -     | - | - | - | - | - | 1       | 2     |

| OR dst, src     | $dst \leftarrow dst \text{ OR } src$                                                                                       | r      | r            | 42                              | -     | * | * | 0 | - | - | 2       | 3     |

|                 |                                                                                                                            | r      | Ir           | 43                              | -     |   |   |   |   |   | 2       | 4     |

|                 |                                                                                                                            | R      | R            | 44                              | -     |   |   |   |   |   | 3       | 3     |

|                 |                                                                                                                            | R      | IR           | 45                              | -     |   |   |   |   |   | 3       | 4     |

|                 |                                                                                                                            | R      | IM           | 46                              | -     |   |   |   |   |   | 3       | 3     |

|                 |                                                                                                                            | IR     | IM           | 47                              | -     |   |   |   |   |   | 3       | 4     |

| ORX dst, src    | $dst \leftarrow dst \text{ OR } src$                                                                                       | ER     | ER           | 48                              | -     | * | * | 0 | - | - | 4       | 3     |

|                 |                                                                                                                            | ER     | IM           | 49                              | -     |   |   |   |   |   | 4       | 3     |

| Flags Notation: | <ul> <li>* = Value is a function of the result of the operation.</li> <li>- = Unaffected</li> <li>X = Undefined</li> </ul> |        |              | 0 = Reset to  0 $1 = Set to  1$ |       |   |   |   |   |   |         |       |

Table 126. eZ8 CPU Instruction Summary (Continued)

For valuable information about hardware and software development tools, visit the ZiLOG web site at <u>www.zilog.com</u>. The latest released version of ZDS can be downloaded from this site.

#### **Part Number Description**

ZiLOG part numbers consist of a number of components, as indicated in the following examples:

| ZiLOG Base Products |                                     |  |  |  |

|---------------------|-------------------------------------|--|--|--|

| Z8                  | ZiLOG 8-bit microcontroller product |  |  |  |

| F6                  | Flash Memory                        |  |  |  |

| 64                  | Program Memory Size                 |  |  |  |

| 01                  | Device Number                       |  |  |  |

| А                   | Package                             |  |  |  |

| Ν                   | Pin Count                           |  |  |  |

| 020                 | Speed                               |  |  |  |

| S                   | Temperature Range                   |  |  |  |

| С                   | Environmental Flow                  |  |  |  |

| Packages                  | A = LQFP                                      |

|---------------------------|-----------------------------------------------|

| 0                         | S = SOIC                                      |

|                           | H = SSOP                                      |

|                           | P = PDIP                                      |

|                           | V = PLCC                                      |

|                           | $\mathbf{F} = \mathbf{Q}\mathbf{F}\mathbf{P}$ |

| Pin Count                 | H = 20 pins                                   |

|                           | J = 28 pins                                   |

|                           | M = 40 pins                                   |

|                           | N = 44 pins                                   |

|                           | R = 64 pins                                   |

|                           | S = 68 pins                                   |

|                           | T = 80 pins                                   |

| Speed                     | 020 = 20MHz                                   |

| Temperature               | $S = 0^{\circ}C$ to $+70^{\circ}C$            |

| •                         | $E = -40^{\circ}C$ to $+105^{\circ}C$         |

| <b>Environmental Flow</b> | C = Plastic-Standard                          |

Example: Part number Z8F06401AN020SC is an 8-bit microcontroller product in an LQFP package, using 44 pins, operating with a maximum 20MHz external clock frequency over a 0°C to +70°C temperature range and built using the Plastic-Standard environmental flow.

cc 184 CCF 189 characteristics, electrical 167 clear 189 clock phase (SPI) 102 **CLR 189** COM 190 compare 71 compare - extended addressing 187 compare mode 71 compare with carry 187 compare with carry - extended addressing 187 complement 190 complement carry flag 188, 189 condition code 184 continuous assertion interrupt sources 47 continuous conversion (ADC) 134 continuous mode 70 control register definition, UART 86 control register, I2C 119 counter modes 70 CP 187 CPC 187 **CPCX 187** CPU and peripheral overview 3 CPU control instructions 189 CPX 187 customer feedback form 216 customer information 216 customer service 213

# D

DA 184, 187 data memory 19 data register, I2C 118 DC characteristics 169 debugger, on-chip 151 DEC 187 decimal adjust 187 decrement 187 decrement and jump non-zero 190 decrement word 187 DECW 187 destination operand 185 device, port availability 33 DI 189 direct address 184 direct memory access controller 122 disable interrupts 189 **DJNZ 190** DMA address high nibble register 126 configuring for DMA\_ADC data transfer 124 confiigurting DMA0-1 data transfer 123 control of ADC 135 control register 124 control register definitions 124 controller 5 DMA ADC address register 128 DMA\_ADC control register 130 DMA ADC operation 123 end address low byte register 128 I/O address register 125 operation 122 start/current address low byte register 127 status register 131 DMAA\_STAT register 131 DMAACTL register 130 DMAxCTL register 124 DMAxEND register 128 DMAxH register 126 DMAxI/O address (DMAxIO) 126 DMAxIO register 126 DMAxSTART register 128 document number description 215 dst 185

## E

EI 189 electrical characteristics 167 ADC 174 flash memory and timing 173 GPIO input data sample timing 176 watch-dog timer 174 enable interrupt 189 ER 184

**RRC** 191 **SBC 188** SCF 188, 189 **SRA 191** SRL 191 **SRP 189 STOP 189 SUB 188 SUBX 188 SWAP 191 TCM 188 TCMX 188** TM 188 TMX 188 **TRAP 190** watch-dog timer refresh 189 XOR 190 **XORX 190** instructions, eZ8 classes of 187 interrupt control register 56 interrupt controller 5, 44 architecture 44 interrupt assertion types 47 interrupt vectors and priority 47 operation 46 register definitions 48 interrupt edge select register 54 interrupt port select register 55 interrupt request 0 register 48 interrupt request 1 register 49 interrupt request 2 register 50 interrupt return 190 interrupt vector listing 44 interrupts not acknowledge 112 receive 112 SPI 105 transmit 112 **UART 85** introduction 1 IR 184 Ir 184 IrDA architecture 95

block diagram 95 control register definitions 98 jitter 98 operation 96 receiving data 97 transmitting data 96 IRET 190 IRQ0 enable high and low bit registers 51 IRQ1 enable high and low bit registers 52 IRQ2 enable high and low bit registers 53 IRR 184 Irr 184

## J

jitter 98 JP 190 jump, conditional, relative, and relative conditional 190

## L

LD 189 LDC 189 LDCI 188, 189 LDE 189 LDEI 188, 189 LDX 189 LEA 189 load 189 load constant 188 load constant to/from program memory 189 load constant with auto-increment addresses 189 load effective address 189 load external data 189 load external data to/from data memory and autoincrement addresses 188 load external to/from data memory and auto-increment addresses 189 load instructions 189 load using extended addressing 189 logical AND 190 logical AND/extended addressing 190 logical exclusive OR 190