# E·XFL

## Zilog - Z8F2401AN020EC00TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                    |

| Number of I/O              | 31                                                            |

| Program Memory Size        | 24KB (24K x 8)                                                |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 2K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                     |

| Data Converters            | A/D 8x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 44-LQFP                                                       |

| Supplier Device Package    | 44-LQFP (10x10)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f2401an020ec00tr |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Timer Operating Modes                                          |

|----------------------------------------------------------------|

| Reading the Timer Count Values                                 |

| Timer Output Signal Operation                                  |

| Timer Control Register Definitions                             |

| Timer 0-3 High and Low Byte Registers                          |

| Timer Reload High and Low Byte Registers                       |

| Timer 0-3 PWM High and Low Byte Registers                      |

| Timer 0-3 Control Registers                                    |

| Watch-Dog Timer                                                |

| Overview                                                       |

| Operation                                                      |

| Watch-Dog Timer Refresh                                        |

| Watch-Dog Timer Time-Out Response                              |

| Watch-Dog Timer Reload Unlock Sequence                         |

| Watch-Dog Timer Control Register Definitions                   |

| Watch-Dog Timer Control Register                               |

| Watch-Dog Timer Reload Upper, High and Low Byte Registers . 76 |

| UART                                                           |

| Overview                                                       |

| Architecture                                                   |

| Operation                                                      |

| Data Format                                                    |

| Transmitting Data using the Polled Method                      |

| Transmitting Data using the Interrupt-Driven Method            |

| Receiving Data using the Polled Method                         |

| Receiving Data using the Interrupt-Driven Method               |

| Receiving Data using the Direct Memory Access                  |

| Controller (DMA)                                               |

| Multiprocessor (9-bit) Mode                                    |

| UART Interrupts                                                |

| UART Baud Rate Generator                                       |

| UART Control Register Definitions                              |

| UARTx Transmit Data Register                                   |

| UARTx Receive Data Register                                    |

| UARTx Status 0 and Status 1 Registers                          |

| UARTx Control 0 and Control 1 Registers                        |

| UARTx Baud Rate High and Low Byte Registers                    |

| Infrared Encoder/Decoder                                       |

| Overview                                                       |

| Architecture                                                   |

| Operation                                                      |

| Figure 31. | Flash Controller Operation Flow Chart 140                               |

|------------|-------------------------------------------------------------------------|

| Figure 32. | On-Chip Debugger Block Diagram 151                                      |

| Figure 33. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (1) |

| Figure 34. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (2) |

| Figure 35. | OCD Data Format                                                         |

| Figure 36. | Recommended Crystal Oscillator Configuration<br>(20MHz operation)       |

| Figure 37. | Nominal ICC Versus System Clock Frequency 170                           |

| Figure 38. | Nominal Halt Mode ICC Versus System                                     |

|            | Clock Frequency                                                         |

| Figure 39. | Port Input Sample Timing 176                                            |

| Figure 40. | GPIO Port Output Timing 177                                             |

| Figure 41. | On-Chip Debugger Timing 178                                             |

| Figure 42. | SPI Master Mode Timing 179                                              |

| Figure 43. | SPI Slave Mode Timing 180                                               |

| Figure 44. | $I^2C$ Timing                                                           |

| Figure 45. | Flags Register 201                                                      |

| Figure 46. | Opcode Map Cell Description 202                                         |

| Figure 47. | First Opcode Map 204                                                    |

| Figure 48. | Second Opcode Map after 1FH 205                                         |

| Figure 49. | 40-Lead Plastic Dual-Inline Package (PDIP) 206                          |

| Figure 50. | 44-Lead Low-Profile Quad Flat Package (LQFP) 207                        |

| Figure 51. | 44-Lead Plastic Lead Chip Carrier Package (PLCC) 207                    |

| Figure 52. | 64-Lead Low-Profile Quad Flat Package (LQFP) 208                        |

| Figure 53. | 68-Lead Plastic Lead Chip Carrier Package (PLCC) 209                    |

| Figure 54. | 80-Lead Quad-Flat Package (QFP) 210                                     |

15

| Signal Mnemonic | I/O | Description                                          |

|-----------------|-----|------------------------------------------------------|

| Reset           |     |                                                      |

| RESET           | Ι   | RESET. Generates a Reset when asserted (driven Low). |

| Power Supply    |     |                                                      |

| VDD             | Ι   | Power Supply.                                        |

| AVDD            | Ι   | Analog Power Supply.                                 |

| VSS             | Ι   | Ground.                                              |

| AVSS            | Ι   | Analog Ground.                                       |

#### Table 2. Signal Descriptions (Continued)

## **Pin Characteristics**

Table 3 provides detailed information on the characteristics for each pin available on the Z8F640x family products. Data in Table 3 is sorted alphabetically by the pin symbol mnemonic.

Table 3. Pin Characteristics of the Z8F640x family

| N/A<br>N/A<br>I/O<br>N/A | N/A<br>N/A<br>I   | N/A<br>N/A<br>N/A            | N/A<br>N/A                                                                                | No<br>No                                 | No<br>No                                         | N/A<br>N/A                                    |

|--------------------------|-------------------|------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------|-----------------------------------------------|

| I/O                      | Ι                 |                              |                                                                                           | No                                       | No                                               | N/A                                           |

|                          |                   | N/A                          |                                                                                           |                                          |                                                  | 1 1/ / 1                                      |

| N/A                      |                   |                              | Yes                                                                                       | No                                       | Yes                                              | Yes                                           |

|                          | N/A               | N/A                          | N/A                                                                                       | No                                       | No                                               | N/A                                           |

| I/O                      | Ι                 | N/A                          | Yes                                                                                       | No                                       | Yes                                              | Yes,<br>Programmable                          |

| I/O                      | Ι                 | N/A                          | Yes                                                                                       | No                                       | Yes                                              | Yes,<br>Programmable                          |

| I/O                      | Ι                 | N/A                          | Yes                                                                                       | No                                       | Yes                                              | Yes,<br>Programmable                          |

| I/O                      | Ι                 | N/A                          | Yes                                                                                       | No                                       | Yes                                              | Yes,<br>Programmable                          |

| I/O                      | Ι                 | N/A                          | Yes                                                                                       | No                                       | Yes                                              | Yes,<br>Programmable                          |

| e                        | I/O<br>I/O<br>I/O | VO I<br>VO I<br>VO I<br>VO I | I/O     I     N/A       I/O     I     N/A       I/O     I     N/A       I/O     I     N/A | I/OIN/AYesI/OIN/AYesI/OIN/AYesI/OIN/AYes | I/OIN/AYesNoI/OIN/AYesNoI/OIN/AYesNoI/OIN/AYesNo | I/OIN/AYesNoYesI/OIN/AYesNoYesI/OIN/AYesNoYes |

# **Reset and Stop Mode Recovery**

## **Overview**

The Reset Controller within the Z8F640x family devices controls Reset and STOP Mode Recovery operation. In typical operation, the following events cause a Reset to occur:

- Power-On Reset (POR)

- Voltage Brown-Out (VBO)

- Watch-Dog Timer time-out (when configured via the WDT\_RES Option Bit to initiate a reset)

- External **RESET** pin assertion

- On-Chip Debugger initiated Reset (OCDCTL[1] set to 1)

When the Z8F640x family device is in Stop mode, a Stop Mode Recovery is initiated by either of the following:

- Watch-Dog Timer time-out

- GPIO Port input pin transition on an enabled Stop Mode Recovery source

- DBG pin driven Low

## **Reset Types**

The Z8F640x family provides several different types of Reset operation. Stop Mode Recovery is considered a form of Reset. The type of Reset is a function of both the current operating mode of the Z8F640x family device and the source of the Reset. Table 7 lists the types of Reset and their operating characteristics. The System Reset is longer than the Short Reset to allow additional time for external oscillator start-up.

| Table 7. Reset and Stop M | Mode Recovery | <b>Characteristics and Latency</b> |

|---------------------------|---------------|------------------------------------|

|---------------------------|---------------|------------------------------------|

|                    | <b>Reset Characteristics and Latency</b> |         |                                                    |  |  |  |  |

|--------------------|------------------------------------------|---------|----------------------------------------------------|--|--|--|--|

| Reset Type         | Control Registers                        | eZ8 CPU | Reset Latency (Delay)                              |  |  |  |  |

| System Reset       | Reset (as applicable)                    | Reset   | 514 WDT Oscillator cycles + 16 System Clock cycles |  |  |  |  |

| Short Reset        | Reset (as applicable)                    | Reset   | 66 WDT Oscillator cycles + 16 System Clock cycles  |  |  |  |  |

| Stop Mode Recovery | Unaffected, except<br>WDT_CTL register   | Reset   | 514 WDT Oscillator cycles + 16 System Clock cycles |  |  |  |  |

| BITS  | 7                                                                             | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |

|-------|-------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--|

| FIELD | PSMRE7                                                                        | PSMRE6 | PSMRE5 | PSMRE4 | PSMRE3 | PSMRE2 | PSMRE1 | PSMRE0 |  |

| RESET | 0                                                                             | 0      | 0      | 0      | 0      | 0      | 0      | 0      |  |

| R/W   | R/W                                                                           | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |

| ADDR  | If 05H in Port A-H Address Register, accessible via Port A-H Control Register |        |        |        |        |        |        |        |  |

#### Table 19. Port A-H STOP Mode Recovery Source Enable Sub-Registers

PSMRE[7:0]—Port STOP Mode Recovery Source Enabled

0 = The Port pin is not configured as a STOP Mode Recovery source. Transitions on this pin during Stop mode do not initiate STOP Mode Recovery.

1 = The Port pin is configured as a STOP Mode Recovery source. Any logic transition on this pin during Stop mode initiates STOP Mode Recovery.

## Port A-H Input Data Registers

Reading from the Port A-H Input Data registers (Table 20) returns the sampled values from the corresponding port pins. The Port A-H Input Data registers are Read-only.

| BITS  | 7                                              | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------|------------------------------------------------|------|------|------|------|------|------|------|

| FIELD | PIN7                                           | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |

| RESET | Х                                              | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

| R/W   | R                                              | R    | R    | R    | R    | R    | R    | R    |

| ADDR  | FD2H, FD6H, FDAH, FDEH, FE2H, FE6H, FEAH, FEEH |      |      |      |      |      |      |      |

Table 20. Port A-H Input Data Registers (PxIN)

PIN[7:0]—Port Input Data

Sampled data from the corresponding port pin input.

0 = Input data is logical 0 (Low).

1 = Input data is logical 1 (High).

I<sup>2</sup>CI—I<sup>2</sup>C Interrupt Request

0 = No interrupt request is pending for the I<sup>2</sup>C.

1 = An interrupt request from the I<sup>2</sup>C is awaiting service.

SPII-SPI Interrupt Request

- 0 = No interrupt request is pending for the SPI.

- 1 = An interrupt request from the SPI is awaiting service.

ADCI-ADC Interrupt Request

0 = No interrupt request is pending for the Analog-to-Digital Converter.

1 = An interrupt request from the Analog-to-Digital Converter is awaiting service.

## Interrupt Request 1 Register

The Interrupt Request 1 (IRQ1) register (Table 24) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ1 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 1 register to determine if any interrupt requests are pending.

| lable 24. li | able 24. Interrupt Request 1 Register (IRQ1) |       |       |       |       |       |  |  |  |  |  |  |

|--------------|----------------------------------------------|-------|-------|-------|-------|-------|--|--|--|--|--|--|

| BITS         | 7                                            | 6     | 5     | 4     | 3     | 2     |  |  |  |  |  |  |

| FIELD        | PAD7I                                        | PAD6I | PAD5I | PAD4I | PAD3I | PAD2I |  |  |  |  |  |  |

| RESET        | 0                                            | 0     | 0     | 0     | 0     | 0     |  |  |  |  |  |  |

Тź

R/W

R/W

R/W

ADDR

PADxI—Port A or Port D Pin x Interrupt Request

R/W

0 = No interrupt request is pending for GPIO Port A or Port D pin x.

R/W

1 = An interrupt request from GPIO Port A or Port D pin x is awaiting service.

FC3H

where x indicates the specific GPIO Port pin number (0 through 7). For each pin, only 1 of either Port A or Port D can be enabled for interrupts at any one time. Port selection (A or D) is determined by the values in the Interrupt Port Select Register.

R/W

R/W

1

PAD1I

0

R/W

0

PAD01

0

R/W

Middle byte, Bits[15:8], of the 24-bit WDT reload value.

| BITS      | 7                                                                                     | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|-----------|---------------------------------------------------------------------------------------|------|------|------|------|------|------|------|--|--|

| FIELD     | WDTL                                                                                  |      |      |      |      |      |      |      |  |  |

| RESET     | 1                                                                                     | 1    | 1    | 1    | 1    | 1    | 1    | 1    |  |  |

| R/W       | R/W*                                                                                  | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* |  |  |

| ADDR      | FF3H                                                                                  |      |      |      |      |      |      |      |  |  |

| R/W* - Re | R/W* - Read returns the current WDT count value. Write sets the desired Reload Value. |      |      |      |      |      |      |      |  |  |

Table 49. Watch-Dog Timer Reload Low Byte Register (WDTL)

WDTL-WDT Reload Low

Least significant byte (LSB), Bits[7:0], of the 24-bit WDT reload value.

- 5. Check the TDRE bit in the UART Status 0 register to determine if the Transmit Data register is empty (indicated by a 1). If empty, continue to Step 6. If the Transmit Data register is full (indicated by a 0), continue to monitor the TDRE bit until the Transmit Data register becomes available to receive new data.

- 6. Write the data byte to the UART Transmit Data register. The transmitter automatically transfers the data to the Transmit Shift register and transmit the data.

- 7. To transmit additional bits, return to Step 5.

#### Transmitting Data using the Interrupt-Driven Method

The UART Transmitter interrupt indicates the availability of the Transmit Data register to accept new data for transmission. Follow these steps to configure the UART for interrupt-driven data transmission:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the desired baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Transmitter interrupt and set the desired priority.

- 5. Write to the UART Control 1 register to enable Multiprocessor (9-bit) mode functions, if desired.

- 6. Write to the UART Control 0 register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission

- Enable parity, if desired, and select either even or odd parity.

- Set or clear the CTSE bit to enable or disable control from the receiver via the  $\overline{\text{CTS}}$  pin.

- 7. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data transmission. When the UART Transmit interrupt is detected, the associated interrupt service routine (ISR) should perform the following:

- 8. Write the data byte to the UART Transmit Data register. The transmitter will automatically transfer the data to the Transmit Shift register and transmit the data.

- 9. Clear the UART Transmit interrupt bit in the applicable Interrupt Request register.

- 10. Execute the IRET instruction to return from the interrupt-service routine and wait for the Transmit Data register to again become empty.

3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BIRQ bit in the UART*x* Control 1 register to 1.

## **UART Control Register Definitions**

The UART control registers support both the UARTs and the associated Infrared Encoder/ Decoders. For more information on the infrared operation, refer to the **Infrared Encoder/ Decoder** chapter on page 95.

## UARTx Transmit Data Register

Data bytes written to the UART*x* Transmit Data register (Table 50) are shifted out on the TXD*x* pin. The Write-only UART*x* Transmit Data register shares a Register File address with the Read-only UART*x* Receive Data register.

| BITS  | 7   | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-----|---------------|---|---|---|---|---|---|--|

| FIELD | TXD |               |   |   |   |   |   |   |  |

| RESET | Х   | Х             | Х | Х | Х | Х | Х | Х |  |

| R/W   | W   | W             | W | W | W | W | W | W |  |

| ADDR  |     | F40H and F48H |   |   |   |   |   |   |  |

Table 50. UARTx Transmit Data Register (UxTXD)

TXD—Transmit Data

UART transmitter data byte to be shifted out through the TXD*x* pin.

0 = No parity error has occurred.

1 = A parity error has occurred.

#### OE—Overrun Error

This bit indicates that an overrun error has occurred. An overrun occurs when new data is received and the UART Receive Data register has not been read. If the RDA bit is reset to 0, then reading the UART Receive Data register clears this bit.

0 = No overrun error occurred.

1 = An overrun error occurred.

FE—Framing Error

This bit indicates that a framing error (no Stop bit following data reception) was detected. Reading the UART Receive Data register clears this bit.

0 = No framing error occurred.

1 = A framing error occurred.

#### BRKD—Break Detect

This bit indicates that a break occurred. If the data bits, parity/multiprocessor bit, and Stop bit(s) are all zeros then this bit is set to 1. Reading the UART Receive Data register clears this bit.

0 = No break occurred.

1 = A break occurred.

#### TDRE—Transmitter Data Register Empty

This bit indicates that the UART Transmit Data register is empty and ready for additional data. Writing to the UART Transmit Data register resets this bit.

0 = Do not write to the UART Transmit Data register.

1 = The UART Transmit Data register is ready to receive an additional byte to be transmitted.

#### TXE—Transmitter Empty

This bit indicates that the transmit shift register is empty and character transmission is finished.

0 = Data is currently transmitting.

1 = Transmission is complete.

CTS—CTS signal

When this bit is read it returns the level of the  $\overline{\text{CTS}}$  signal.

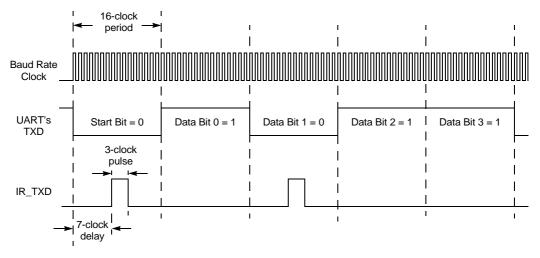

Figure 72. Infrared Data Transmission

#### **Receiving IrDA Data**

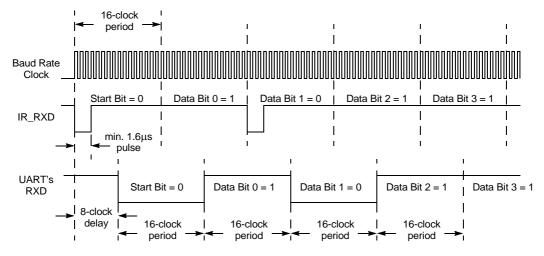

Data received from the infrared transceiver via the IR\_RXD signal through the RXD pin is decoded by the Infrared Endec and passed to the UART. The UART's baud rate clock is used by the Infrared Endec to generate the demodulated signal (RXD) that drives the UART. Each UART/Infrared data bit is 16-clocks wide. Figure 73 illustrates data reception. When the Infrared Endec is enabled, the UART's RXD signal is internal to the Z8F640x family device while the IR\_RXD signal is received through the RXD pin.

**Figure 73. Infrared Data Reception**

## Jitter

Because of the inherent sampling of the received IR\_RXD signal by the bit rate clock, some jitter can be expected on the first bit in any sequence of data. All subsequent bits in the received data stream are a fixed 16-clock periods wide.

## Infrared Encoder/Decoder Control Register Definitions

All Infrared Endec configuration and status information is set by the UART control registers as defined beginning on page 86.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART*x* Control 1 register to 1 to enable the Infrared Encoder/ Decoder *before* enabling the GPIO Port alternate function for the corresponding pin.

## SPI Baud Rate High and Low Byte Registers

The SPI Baud Rate High and Low Byte registers combine to form a 16-bit reload value, BRG[15:0], for the SPI Baud Rate Generator. The reload value must be greater than or equal to 0002H for proper SPI operation (maximum baud rate is system clock frequency divided by 4). The SPI baud rate is calculated using the following equation:

SPI Baud Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{2 \times \text{BRG}[15:0]}$

| BITS  | 7                                                               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-----------------------------------------------------------------|---|---|---|---|---|---|---|--|

| FIELD | BRH                                                             |   |   |   |   |   |   |   |  |

| RESET | 1                                                               | 1 | 1 | 1 | 1 | 1 | 1 | 1 |  |

| R/W   | R/W         R/W         R/W         R/W         R/W         R/W |   |   |   |   |   |   |   |  |

| ADDR  | F66H                                                            |   |   |   |   |   |   |   |  |

Table 64. SPI Baud Rate High Byte Register (SPIBRH)

#### BRH = SPI Baud Rate High Byte

Most significant byte, BRG[15:8], of the SPI Baud Rate Generator's reload value.

#### Table 65. SPI Baud Rate Low Byte Register (SPIBRL)

| BITS  | 7    | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|--|

| FIELD | BRL  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |   |   |   |   |   |  |

| RESET | 1    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 | 1 | 1 | 1 | 1 | 1 |  |

| R/W   | R/W  | R/W         R/W |   |   |   |   |   |   |  |

| ADDR  | F67H |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |   |   |   |   |   |  |

BRL = SPI Baud Rate Low Byte

Least significant byte, BRG[7:0], of the SPI Baud Rate Generator's reload value.

## I<sup>2</sup>C Baud Rate High and Low Byte Registers

The I<sup>2</sup>C Baud Rate High and Low Byte registers combine to form a 16-bit reload value, BRG[15:0], for the I<sup>2</sup>C Baud Rate Generator. The I<sup>2</sup>C baud rate is calculated using the following equation:

I2C Baud Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{4 \times \text{BRG}[15:0]}$

| BITS  | 7                                                               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-----------------------------------------------------------------|---|---|---|---|---|---|---|--|

| FIELD | BRH                                                             |   |   |   |   |   |   |   |  |

| RESET | 1                                                               | 1 | 1 | 1 | 1 | 1 | 1 | 1 |  |

| R/W   | R/W         R/W         R/W         R/W         R/W         R/W |   |   |   |   |   |   |   |  |

| ADDR  | F53H                                                            |   |   |   |   |   |   |   |  |

## Table 69. I<sup>2</sup>C Baud Rate High Byte Register (I2CBRH)

$BRH = I^2C$  Baud Rate High Byte

Most significant byte, BRG[15:8], of the I<sup>2</sup>C Baud Rate Generator's reload value.

Table 70. I<sup>2</sup>C Baud Rate Low Byte Register (I2CBRL)

| BITS  | 7                                                               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----------------------------------------------------------------|---|---|---|---|---|---|---|

| FIELD | BRL                                                             |   |   |   |   |   |   |   |

| RESET | 1                                                               | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| R/W   | R/W         R/W         R/W         R/W         R/W         R/W |   |   |   |   |   |   |   |

| ADDR  | F54H                                                            |   |   |   |   |   |   |   |

$BRL = I^2C$  Baud Rate Low Byte

Least significant byte, BRG[7:0], of the  $I^2C$  Baud Rate Generator's reload value.

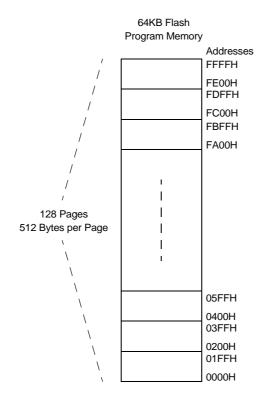

Figure 84. Flash Memory Arrangement

## Operation

The Flash Controller programs and erases the Flash memory. The Flash Controller provides the proper Flash controls and timing for byte programming, Page Erase, and Mass Erase of the Flash memory. The Flash Controller contains a protection mechanism, via the Flash Control register (FCTL) to prevent accidental programming or erasure. The Flow Chart in Figure 85 illustrates basic Flash Controller operation. The following subsections provide details on the various operations (Lock, Unlock, Byte Programming, Page Erase, and Mass Erase) listed in Figure 85.

156

ister. When the Watchpoint event occurs, the Z8F640x family device enters Debug mode and the DBGMODE bit in the OCDCTL register becomes 1.

## **Runtime Counter**

The On-Chip Debugger contains a 16-bit Runtime Counter. It counts system clock cycles between Breakpoints. The counter starts counting when the On-Chip Debugger leaves Debug mode and stops counting when it enters Debug mode again or when it reaches the maximum count of FFFFH.

## **On-Chip Debugger Commands**

The host communicates to the On-Chip Debugger by sending OCD commands using the DBG interface. During normal operation of the Z8F640x family device, only a subset of the OCD commands are available. In Debug mode, all OCD commands become available unless the user code and control registers are protected by programming the Read Protect Option Bit (RP). The Read Protect Option Bit prevents the code in memory from being read out of the Z8F640x family device. When this option is enabled, several of the OCD commands are disabled. Table 93 contains a summary of the On-Chip Debugger commands. Each OCD command is described in further detail in the bulleted list following Table 93. Table 93 indicates those commands that operate when the Z8F640x family device is not in Debug mode (normal operation) and those commands that are disabled by programming the Read Protect Option Bit.

| Debug Command              | Command Byte | Enabled when NOT in Debug mode? | Disabled by<br>Read Protect Option Bit                                                                                                                                    |

|----------------------------|--------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read OCD Revision          | 00H          | Yes                             | -                                                                                                                                                                         |

| Reserved                   | 01H          | -                               | -                                                                                                                                                                         |

| Read OCD Status Register   | 02H          | Yes                             | -                                                                                                                                                                         |

| Read Runtime Counter       | 03H          | -                               | -                                                                                                                                                                         |

| Write OCD Control Register | 04H          | Yes                             | Cannot clear DBGMODE bit                                                                                                                                                  |

| Read OCD Control Register  | 05H          | Yes                             | -                                                                                                                                                                         |

| Write Program Counter      | 06H          | -                               | Disabled                                                                                                                                                                  |

| Read Program Counter       | 07H          | -                               | Disabled                                                                                                                                                                  |

| Write Register             | 08H          | -                               | Only writes of the Flash Memory Control<br>registers are allowed. Additionally, only the<br>Mass Erase command is allowed to be<br>written to the Flash Control register. |

| Read Register              | 09H          | -                               | Disabled                                                                                                                                                                  |

#### Table 93. On-Chip Debugger Commands

zero). If the Z8F640x family device is not in Debug mode or if the Read Protect Option Bit is enabled, this command returns FFH for all the data values.

```

DEG <-- 09H

DEG <-- {4'h0,Register Address[11:8]

DEG <-- Register Address[7:0]

DEG <-- Size[7:0]

DEG --> 1-256 data bytes

```

• Write Program Memory (0AH)—The Write Program Memory command writes data to Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be written 1-65536 bytes at a time (65536 bytes can be written by setting size to zero). The on-chip Flash Controller must be written to and unlocked for the programming operation to occur. If the Flash Controller is not unlocked, the data is discarded. If the Z8F640x family device is not in Debug mode or if the Read Protect Option Bit is enabled, the data is discarded.

```

DBG <-- 0AH

DBG <-- Program Memory Address[15:8]

DBG <-- Program Memory Address[7:0]

DBG <-- Size[15:8]

DBG <-- Size[7:0]

DBG <-- 1-65536 data bytes

```

• **Read Program Memory (0BH)**—The Read Program Memory command reads data from Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be read 1-65536 bytes at a time (65536 bytes can be read by setting size to zero). If the Z8F640x family device is not in Debug mode or if the Read Protect Option Bit is enabled, this command returns FFH for the data.

```

DEG <-- 0BH

DEG <-- Program Memory Address[15:8]

DEG <-- Program Memory Address[7:0]

DEG <-- Size[15:8]

DEG <-- Size[7:0]

DEG --> 1-65536 data bytes

```

• Write Data Memory (0CH)—The Write Data Memory command writes data to Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be written 1-65536 bytes at a time (65536 bytes can be written by setting size to zero). If the Z8F640x family device is not in Debug mode or if the Read Protect Option Bit is enabled, the data is discarded.

```

DBG <-- 0CH

DBG <-- Data Memory Address[15:8]

DBG <-- Data Memory Address[7:0]

DBG <-- Size[15:8]

DBG <-- Size[7:0]

DBG <-- 1-65536 data bytes

```

## **DC Characteristics**

Table 101 lists the DC characteristics of the Z8F640x family devices. All voltages are referenced to  $V_{SS}$ , the primary system ground.

|                   |                           | $T_A = -40^{0}C$ to $105^{0}C$ |                  |                      |       |                                                                                                   |  |

|-------------------|---------------------------|--------------------------------|------------------|----------------------|-------|---------------------------------------------------------------------------------------------------|--|

| Symbol            | Parameter                 | Minimum                        | Typical          | Maximum              | Units | Conditions                                                                                        |  |

| V <sub>DD</sub>   | Supply Voltage            | 3.0                            | -                | 3.6                  | V     |                                                                                                   |  |

| V <sub>IL1</sub>  | Low Level Input Voltage   | -0.3                           | _                | 0.3*V <sub>DD</sub>  | V     | For all input pins except RESET, DBG, and XIN.                                                    |  |

| V <sub>IL2</sub>  | Low Level Input Voltage   | -0.3                           | _                | 0.2*V <sub>DD</sub>  | V     | For RESET, DBG, and XIN.                                                                          |  |

| $V_{IH1}$         | High Level Input Voltage  | 0.7*V <sub>DD</sub>            | _                | 5.5                  | V     | Port A, C, D, E, F, and G pins.                                                                   |  |

| V <sub>IH2</sub>  | High Level Input Voltage  | 0.7*V <sub>DD</sub>            | -                | V <sub>DD</sub> +0.3 | V     | Port B and H pins.                                                                                |  |

| V <sub>IH3</sub>  | High Level Input Voltage  | 0.8*V <sub>DD</sub>            | -                | V <sub>DD</sub> +0.3 | V     | RESET, DBG, and XIN pins.                                                                         |  |

| V <sub>OL1</sub>  | Low Level Output Voltage  | -                              | -                | 0.4                  | V     | V <sub>DD</sub> = 3.0V; I <sub>OL</sub> = 2mA<br>High Output Drive disabled.                      |  |

| V <sub>OH1</sub>  | High Level Output Voltage | 2.4                            | -                | -                    | V     | V <sub>DD</sub> = 3.0V; I <sub>OH</sub> = -2mA<br>High Output Drive disabled.                     |  |

| V <sub>OL2</sub>  | Low Level Output Voltage  | _                              | -                | 0.6                  | V     | $V_{DD} = 3.3V; I_{OL} = 20mA$<br>High Output Drive enabled.<br>$T_A = -40^0 C$ to $+70^0 C$      |  |

| V <sub>OL3</sub>  | Low Level Output Voltage  | -                              | -                | 0.6                  | V     | $V_{DD} = 3.3V; I_{OL} = 15mA$<br>High Output Drive enabled.<br>$T_A = 70^0C \text{ to } +105^0C$ |  |

| V <sub>OH2</sub>  | High Level Output Voltage | 2.4                            | -                | -                    | V     | $V_{DD} = 3.3V; I_{OH} = -20mA$<br>High Output Drive enabled.<br>$T_A = -40^0 C$ to $+70^0 C$     |  |

| V <sub>OH3</sub>  | High Level Output Voltage | 2.4                            | -                | -                    | V     | $V_{DD} = 3.3V; I_{OH} = -15mA$<br>High Output Drive enabled.<br>$T_A = 70^0C$ to $+105^0C$       |  |

| I <sub>IL</sub>   | Input Leakage Current     | -5                             | -                | +5                   | μA    | $V_{DD} = 3.6V;$<br>$V_{IN} = VDD \text{ or } VSS^1$                                              |  |

| I <sub>TL</sub>   | Tri-State Leakage Current | -5                             | -                | +5                   | μΑ    | V <sub>DD</sub> = 3.6V                                                                            |  |

| C <sub>PAD</sub>  | GPIO Port Pad Capacitance | -                              | 8.0 <sup>2</sup> | -                    | pF    |                                                                                                   |  |

| C <sub>XIN</sub>  | XIN Pad Capacitance       | -                              | 8.0 <sup>2</sup> | -                    | pF    |                                                                                                   |  |

| C <sub>XOUT</sub> | XOUT Pad Capacitance      | -                              | 9.5 <sup>2</sup> | -                    | pF    |                                                                                                   |  |

## Table 101. DC Characteristics

|                                               | V <sub>I</sub><br>T <sub>A</sub> = | $_{\rm DD} = 3.0 - 3.0$<br>- 40 <sup>0</sup> C to 1 | .6V<br>05 <sup>0</sup> C |        |                                                                                                                                                                |

|-----------------------------------------------|------------------------------------|-----------------------------------------------------|--------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                     | Minimum                            | Typical                                             | Maximum                  | Units  | Notes                                                                                                                                                          |

| Writes to Single Address Before<br>Next Erase | -                                  | -                                                   | 2                        |        |                                                                                                                                                                |

| Flash Row Program Time                        | _                                  | _                                                   | 8                        | ms     | Cumulative program time for<br>single row cannot exceed limit<br>before next erase. This parameter<br>is only an issue when bypassing<br>the Flash Controller. |

| Data Retention                                | 100                                | _                                                   | -                        | years  | 25 <sup>0</sup> C                                                                                                                                              |

| Endurance                                     | 10,000                             | _                                                   | -                        | cycles | Program / erase cycles                                                                                                                                         |

#### Table 104. Flash Memory Electrical Characteristics and Timing (Continued)

#### Table 105. Watch-Dog Timer Electrical Characteristics and Timing

|                  |                          | $V_{DD} = 3.0 - 3.6V$<br>$T_A = -40^{0}$ C to $105^{0}$ C |         |         |       |            |

|------------------|--------------------------|-----------------------------------------------------------|---------|---------|-------|------------|

| Symbol           | Parameter                | Minimum                                                   | Typical | Maximum | Units | Conditions |

| F <sub>WDT</sub> | WDT Oscillator Frequency | 25                                                        | 50      | 100     | kHz   |            |

#### Table 106. Analog-to-Digital Converter Electrical Characteristics and Timing

|                     |                                                                                                                       | $V_{DD} = 3.0 - 3.6V$<br>$T_A = -40^{0}$ C to $105^{0}$ C |         |         |       |                                                      |  |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------|---------|-------|------------------------------------------------------|--|--|--|--|

| Symbol              | Parameter                                                                                                             | Minimum                                                   | Typical | Maximum | Units | Conditions                                           |  |  |  |  |

|                     | Resolution                                                                                                            | -                                                         | 10      | -       | bits  | External $V_{REF} = 3.0V$ ;<br>$R_S \ll 3.0 k\Omega$ |  |  |  |  |

|                     | Differential Nonlinearity<br>(DNL)                                                                                    | -1.0                                                      | _       | 1.0     | LSB   | External $V_{REF} = 3.0V$ ;<br>$R_S \ll 3.0 k\Omega$ |  |  |  |  |

|                     | Integral Nonlinearity (INL)                                                                                           | -3.0                                                      | _       | 3.0     | LSB   | External $V_{REF} = 3.0V$ ;<br>$R_S \le 3.0 k\Omega$ |  |  |  |  |

|                     | DC Offset Error                                                                                                       | -35                                                       | -       | 25      | mV    | 80-pin QFP and 64-pin LQFP packages.                 |  |  |  |  |

| <sup>1</sup> Analog | <sup>1</sup> Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time. |                                                           |         |         |       |                                                      |  |  |  |  |

## Z8F640x/Z8F480x/Z8F320x/Z8F240x/Z8F160x Z8 Encorel<sup>®</sup>

read watchpoint (21H) 161 step instruction (10H) 160 stuff instruction (11H) 160 write data memory (0CH) 159 write OCD control register (04H) 158 write program counter (06H) 158 write program memory (0AH) 159 write register (08H) 158 write watchpoint (20H) 161 on-chip debugger 5 on-chip debugger (OCD) 151 on-chip debugger signals 14 on-chip oscillator 165 one-shot mode 70 opcode map abbreviations 203 cell description 202 first 204 second after 1FH 205 OR 190 ordering information 211 **ORX 190** oscillator signals 14

## Р

p 184 packaging LOFP 44 lead 207 64 lead 208 **PDIP 206** PLCC 44 lead 207 68 lead 209 **OFP 210** part number description 214 part selection guide 2 PC 185 **PDIP 206** peripheral AC and DC electrical characteristics 173 PHASE=0 timing (SPI) 103 PHASE=1 timing (SPI) 104 pin characteristics 15

PLCC 44 lead 207 68-lead 209 polarity 184 POP 189 pop using extended addressing 189 **POPX 189** port availability, device 33 port input timing (GPIO) 176 port output timing, GPIO 177 power supply signals 15 power-down, automatic (ADC) 133 power-on and voltage brown-out 173 power-on reset (POR) 27 problem description or suggestion 217 product information 216 program control instructions 190 program counter 185 program memory 18 **PUSH 189** push using extended addressing 189 PUSHX 189 PWM mode 70 PxADDR register 37 PxCTL register 38

# Q

QFP 210

## R

R 184 r 184 RA, register address 184 RCF 188, 189 receive 10-bit data format (I2C) 116 7-bit data transfer format (I2C) 115 IrDA data 97 receive interrupt 112 receiving UART data-DMA controller 83 receiving UART data-interrupt-driven method 82 receiving UART data-polled method 82