# E·XFL

#### Zilog - Z8F2401AN020SC00TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                    |

| Number of I/O              | 31                                                            |

| Program Memory Size        | 24KB (24K x 8)                                                |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 2K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                     |

| Data Converters            | A/D 8x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | 0°C ~ 70°C (TA)                                               |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 44-LQFP                                                       |

| Supplier Device Package    | 44-LQFP (10x10)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f2401an020sc00tr |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 32. | IRQ2 Enable and Priority Encoding                     |

|-----------|-------------------------------------------------------|

| Table 33. | IRQ1 Enable High Bit Register (IRQ1ENH) 53            |

| Table 34. | IRQ2 Enable Low Bit Register (IRQ2ENL) 54             |

| Table 35. | IRQ2 Enable High Bit Register (IRQ2ENH) 54            |

| Table 36. | Interrupt Edge Select Register (IRQES)                |

| Table 37. | Interrupt Port Select Register (IRQPS) 55             |

| Table 38. | Interrupt Control Register (IRQCTL)                   |

| Table 39. | Timer 0-3 High Byte Register (TxH)                    |

| Table 40. | Timer 0-3 Low Byte Register (TxL)                     |

| Table 41. | Timer 0-3 Reload High Byte Register (TxRH)            |

| Table 42. | Timer 0-3 Reload Low Byte Register (TxRL)             |

| Table 43. | Timer 0-3 PWM High Byte Register (TxPWMH) 69          |

| Table 44. | Timer 0-3 PWM Low Byte Register (TxPWML) 69           |

| Table 45. | Timer 0-3 Control Register (TxCTL)                    |

| Table 46. | Watch-Dog Timer Approximate Time-Out Delays 73        |

| Table 47. | Watch-Dog Timer Control Register (WDTCTL)75           |

| Table 48. | Watch-Dog Timer Reload Upper Byte Register (WDTU) 76  |

| Table 49. | Watch-Dog Timer Reload High Byte Register (WDTH) . 76 |

| Table 50. | Watch-Dog Timer Reload Low Byte Register (WDTL)77     |

| Table 51. | UARTx Transmit Data Register (UxTXD)                  |

| Table 52. | UARTx Receive Data Register (UxRXD)                   |

| Table 53. | UARTx Status 0 Register (UxSTAT0)                     |

| Table 54. | UARTx Control 0 Register (UxCTL0)                     |

| Table 55. | UARTx Status 1 Register (UxSTAT1)                     |

| Table 56. | UARTx Control 1 Register (UxCTL1)                     |

| Table 57. | UARTx Baud Rate High Byte Register (UxBRH)91          |

| Table 58. | UARTx Baud Rate Low Byte Register (UxBRL) 92          |

| Table 59. | UART Baud Rates                                       |

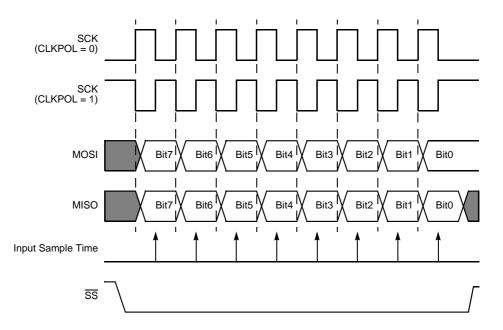

| Table 60. | SPI Clock Phase (PHASE) and Clock Polarity            |

|           | (CLKPOL) Operation                                    |

| Table 61. | SPI Data Register (SPIDATA) 106                       |

| Table 62. | SPI Control Register (SPICTL) 107                     |

| Table 63. | SPI Status Register (SPISTAT) 108                     |

| Table 64. | SPI Mode Register (SPIMODE) 109                       |

| Table 65. | SPI Baud Rate High Byte Register (SPIBRH) 110         |

| Table 66. | SPI Baud Rate Low Byte Register (SPIBRL) 110          |

|           |                                                       |

- Watch-Dog Timer's internal RC oscillator continues to operate

- If enabled, the Watch-Dog Timer continues to operate

- All other on-chip peripherals continue to operate

The eZ8 CPU can be brought out of Halt mode by any of the following operations:

- Interrupt

- Watch-Dog Timer time-out (interrupt or reset)

- Power-on reset

- Voltage-brown out reset

- External **RESET** pin assertion

To minimize current in Halt mode, all GPIO pins which are configured as inputs must be driven to one of the supply rails ( $V_{CC}$  or GND).

| BITS  | 7                                                                             | 6      | 5      | 4      | 3                       | 2   | 1      | 0      |  |  |  |

|-------|-------------------------------------------------------------------------------|--------|--------|--------|-------------------------|-----|--------|--------|--|--|--|

| FIELD | PSMRE7                                                                        | PSMRE6 | PSMRE5 | PSMRE4 | MRE4 PSMRE3 PSMRE2 PSMR |     | PSMRE1 | PSMRE0 |  |  |  |

| RESET | 0                                                                             | 0      | 0      | 0      | 0                       | 0   | 0      | 0      |  |  |  |

| R/W   | R/W                                                                           | R/W    | R/W    | R/W    | R/W                     | R/W | R/W    | R/W    |  |  |  |

| ADDR  | If 05H in Port A-H Address Register, accessible via Port A-H Control Register |        |        |        |                         |     |        |        |  |  |  |

#### Table 19. Port A-H STOP Mode Recovery Source Enable Sub-Registers

PSMRE[7:0]—Port STOP Mode Recovery Source Enabled

0 = The Port pin is not configured as a STOP Mode Recovery source. Transitions on this pin during Stop mode do not initiate STOP Mode Recovery.

1 = The Port pin is configured as a STOP Mode Recovery source. Any logic transition on this pin during Stop mode initiates STOP Mode Recovery.

#### Port A-H Input Data Registers

Reading from the Port A-H Input Data registers (Table 20) returns the sampled values from the corresponding port pins. The Port A-H Input Data registers are Read-only.

| BITS  | 7                                              | 6    | 5    | 4    | 3    | 2             | 1 | 0    |  |  |  |

|-------|------------------------------------------------|------|------|------|------|---------------|---|------|--|--|--|

| FIELD | PIN7                                           | PIN6 | PIN5 | PIN4 | PIN3 | PIN3 PIN2 PIN |   | PIN0 |  |  |  |

| RESET | Х                                              | Х    | Х    | Х    | Х    | Х             | Х | Х    |  |  |  |

| R/W   | R                                              | R    | R    | R    | R    | R             | R | R    |  |  |  |

| ADDR  | FD2H, FD6H, FDAH, FDEH, FE2H, FE6H, FEAH, FEEH |      |      |      |      |               |   |      |  |  |  |

Table 20. Port A-H Input Data Registers (PxIN)

PIN[7:0]—Port Input Data

Sampled data from the corresponding port pin input.

0 = Input data is logical 0 (Low).

1 = Input data is logical 1 (High).

- Disable the timer

- Configure the timer for PWM mode.

- Set the prescale value.

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the Timer Reload High and Low Byte registers to set the Reload value (PWM period). The Reload value must be greater than the PWM value.

- 5. If desired, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control register to enable the timer and initiate counting.

The PWM period is given by the following equation:

**PWM Period** (s) = Reload Value × Prescale System Clock Frequency (Hz)

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, the One-Shot mode equation must be used to determine the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is given by:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is given by:

PWM Output High Time Ratio (%) =

$$\frac{PWM Value}{Reload Value} \times 100$$

#### **Capture Mode**

In Capture mode, the current timer count value is recorded when the desired external Timer Input transition occurs. The Capture count value is written to the Timer PWM High and Low Byte Registers. The timer input is the system clock. The TPOL bit in the Timer Control register determines if the Capture occurs on a rising edge or a falling edge of the

information on approximate time-out delays for the minimum and maximum WDT reload values.

Table 45. Watch-Dog Timer Approximate Time-Out Delays

| WDT Reload Value | WDT Reload Value | Approximate Time-Out Delay<br>(with 50kHz typical WDT oscillator frequency) |                        |  |  |  |  |  |

|------------------|------------------|-----------------------------------------------------------------------------|------------------------|--|--|--|--|--|

| (Hex)            | (Decimal)        | Typical                                                                     | Description            |  |  |  |  |  |

| 000004           | 4                | 80µs                                                                        | Minimum time-out delay |  |  |  |  |  |

| FFFFFF           | 16,777,215       | 335.5s                                                                      | Maximum time-out delay |  |  |  |  |  |

#### Watch-Dog Timer Refresh

When first enabled, the Watch-Dog Timer is loaded with the value in the Watch-Dog Timer Reload registers. The Watch-Dog Timer then counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the downcounter to be reloaded with the WDT Reload value stored in the Watch-Dog Timer Reload registers. Counting resumes following the reload operation.

When the Z8F640x family device is operating in Debug Mode (via the On-Chip Debugger), the Watch-Dog Timer is continuously refreshed to prevent spurious Watch-Dog Timer time-outs.

#### Watch-Dog Timer Time-Out Response

The Watch-Dog Timer times out when the counter reaches 000000H. A time-out of the Watch-Dog Timer generates either an interrupt or a Short Reset. The WDT\_RES Option Bit determines the time-out response of the Watch-Dog Timer. Refer to the **Option Bits** chapter for information regarding programming of the WDT\_RES Option Bit.

#### WDT Interrupt in Normal Operation

If configured to generate an interrupt when a time-out occurs, the Watch-Dog Timer issues an interrupt request to the interrupt controller and sets the WDT status bit in the Watch-Dog Timer Control register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watch-Dog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watch-Dog Timer counter rolls over to its maximum value of FFFFFH and continues counting. The Watch-Dog Timer counter is not automatically returned to its Reload Value.

#### WDT Interrupt in Stop Mode

If configured to generate an interrupt when a time-out occurs and the Z8F640x family device is in STOP mode, the Watch-Dog Timer automatically initiates a STOP Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Watch-Dog Timer Control register are set to 1 following WDT time-out in STOP

#### Operation

When the Infrared Endec is enabled, the transmit data from the associated on-chip UART is encoded as digital signals in accordance with the IrDA standard and output to the infrared transceiver via the TXD pin. Likewise, data received from the infrared transceiver is passed to the Infrared Endec via the RXD pin, decoded by the Infrared Endec, and then passed to the UART. Communication is half-duplex, which means simultaneous data transmission and reception is not allowed.

The baud rate is set by the UART's Baud Rate Generator and supports IrDA standard baud rates from 9600 baud to 115.2 kbaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled to use the Infrared Endec. The Infrared Endec data rate is calculated using the following equation:

### Infrared Data Rate (bits/s) = $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

#### **Transmitting IrDA Data**

The data to be transmitted using the infrared transceiver is first sent to the UART. The UART's transmit signal (TXD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drives the infrared transceiver. Each UART/Infrared data bit is 16-clocks wide. If the data to be transmitted is 1, the IR\_TXD signal remains low for the full 16-clock period. If the data to be transmitted is 0, a 3-clock high pulse is output following a 7-clock low period. After the 3-clock high pulse, a 6-clock low pulse is output to complete the full 16-clock data period. Figure 72 illustrates IrDA data transmission. When the Infrared Endec is enabled, the UART's TXD signal is internal to the Z8F640x family device while the IR\_TXD signal is output through the TXD pin.

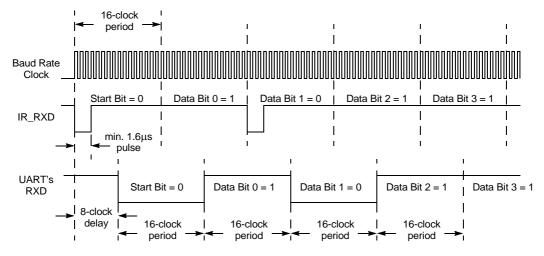

**Figure 73. Infrared Data Reception**

#### Jitter

Because of the inherent sampling of the received IR\_RXD signal by the bit rate clock, some jitter can be expected on the first bit in any sequence of data. All subsequent bits in the received data stream are a fixed 16-clock periods wide.

#### Infrared Encoder/Decoder Control Register Definitions

All Infrared Endec configuration and status information is set by the UART control registers as defined beginning on page 86.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART*x* Control 1 register to 1 to enable the Infrared Encoder/ Decoder *before* enabling the GPIO Port alternate function for the corresponding pin.

104

Figure 78. SPI Timing When PHASE is 1

#### **Multi-Master Operation**

In a multi-master SPI system, all SCK pins are tied together, all MOSI pins are tied together and all MISO pins are tied together. All SPI pins must then be configured in open-drain mode to prevent bus contention. At any one time, only one SPI device is configured as the Master and all other SPI devices on the bus are configured as Slaves. The Master enables a single Slave by asserting the  $\overline{SS}$  pin on that Slave only. Then, the single Master drives data out its SCK and MOSI pins to the SCK and MOSI pins on the Slaves (including those which are not enabled). The enabled Slave drives data out its MISO pin to the MISO Master pin.

For a Master device operating in a multi-master system, if the  $\overline{SS}$  pin is configured as an input and is driven Low by another Master, the COL bit is set to 1 in the SPI Status Register. The COL bit indicates the occurrence of a multi-master collision (mode fault error condition).

#### **Error Detection**

The SPI contains error detection logic to support SPI communication protocols and recognize when communication errors have occurred. The SPI Status register indicates when a data transmission error has been detected.

#### **Overrun (Write Collision)**

An overrun error (write collision) indicates a write to the SPI Data register was attempted while a data transfer is in progress. An overrun sets the OVR bit in the SPI Status register to 1. Writing a 1 to OVR clears this error flag.

#### Mode Fault (Multi-Master Collision)

A mode fault indicates when more than one Master is trying to communicate at the same time (a multi-master collision). The mode fault is detected when the enabled Master's  $\overline{SS}$  pin is asserted. A mode fault sets the COL bit in the SPI Status register to 1. Writing a 1 to COL clears this error flag.

#### **SPI Interrupts**

When SPI interrupts are enabled, the SPI generates an interrupt after data transmission. The SPI in Master mode generates an interrupt after a character has been sent. A character can be defined to be 1 through 8 bits by the NUMBITS field in the SPI Mode register. The SPI in Slave mode generates an interrupt when the  $\overline{SS}$  signal deasserts to indicate completion of the data transfer. Writing a 1 to the IRQ bit in the SPI Status Register clears the pending interrupt request. If the SPI is disabled, an SPI interrupt can be generated by a Baud Rate Generator time-out.

#### **SPI Baud Rate Generator**

In SPI Master mode, the Baud Rate Generator creates a lower frequency serial clock (SCK) for data transmission synchronization between the Master and the external Slave. The input to the Baud Rate Generator is the system clock. The SPI Baud Rate High and Low Byte registers combine to form a 16-bit reload value, BRG[15:0], for the SPI Baud Rate Generator. The reload value must be greater than or equal to 0002H for SPI operation (maximum baud rate is system clock frequency divided by 4). The SPI baud rate is calculated using the following equation:

## SPI Baud Rate (bits/s) = $\frac{\text{System Clock Frequency (Hz)}}{2 \times \text{BRG}[15:0]}$

When the SPI is disabled, the Baud Rate Generator can function as a basic 16-bit timer with interrupt on time-out. To configure the Baud Rate Generator as a timer with interrupt on time-out, complete the following procedure:

1 = DMAx is enabled and initiates a data transfer upon receipt of a request from the trigger source.

#### DLE—DMAx Loop Enable

0 = DMAx reloads the original Start Address and is then disabled after the End Address data is transferred.

1 = DMAx, after the End Address data is transferred, reloads the original Start Address and continues operating.

DDIR—DMAx Data Transfer Direction

0 =Register File  $\rightarrow$  on-chip peripheral control register.

1 = on-chip peripheral control register  $\rightarrow$  Register File.

IRQEN—DMAx Interrupt Enable

0 = DMAx does not generate any interrupts.

1 = DMAx generates an interrupt when the End Address data is transferred.

WSEL-Word Select

0 = DMAx transfers a single byte per request.

1 = DMAx transfers a two-byte word per request. The address for the on-chip peripheral control register must be an even address.

#### RSS-Request Trigger Source Select

The Request Trigger Source Select field determines the peripheral that can initiate a DMA request transfer. The corresponding interrupts do not need to be enabled within the Interrupt Controller to initiate a DMA transfer. However, if the Request Trigger Source can enable or disable the interrupt request sent to the Interrupt Controller, the interrupt request must be enabled within the Request Trigger Source block.

- 000 = Timer 0.

- 001 = Timer 1.

- 010 = Timer 2.

- 011 = Timer 3.

100 = DMA0 Control register: UART0 Received Data register contains valid data. DMA1 Control register: UART0 Transmit Data register empty.

101 = DMA0 Control register: UART1 Received Data register contains valid data. DMA1 Control register: UART1 Transmit Data register empty.

110 = DMA0 Control register: I<sup>2</sup>C Receiver Interrupt. DMA1 Control register: I<sup>2</sup>C Transmitter Interrupt register empty.

111 = Reserved.

#### DMAx I/O Address Register

The DMAx I/O Address register contains the low byte of the on-chip peripheral address for data transfer. The full 12-bit Register File address is given by {FH, DMAx\_IO[7:0]}.

145

#### **Flash Status Register**

The Flash Status register indicates the current state of the Flash Controller. This register can be read at any time. The Read-only Flash Status Register shares its Register File address with the Write-only Flash Control Register.

| BITS  | 7    | 6     | 5     | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|------|-------|-------|---|---|---|---|---|--|--|

| FIELD | Rese | erved | FSTAT |   |   |   |   |   |  |  |

| RESET | 0    | 0     | 0     | 0 | 0 | 0 | 0 | 0 |  |  |

| R/W   | R    | R     | R     | R | R | R | R | R |  |  |

| ADDR  | FF8H |       |       |   |   |   |   |   |  |  |

Reserved

These bits are reserved and must be 0.

FSTAT—Flash Controller Status

000000 = Flash Controller locked.

000001 = First unlock command received.

000010 = Flash Controller unlocked (second unlock command received).

001xxx = Program operation in progress.

010xxx = Page erase operation in progress.

100xxx = Mass erase operation in progress.

#### Flash Frequency High and Low Byte Registers

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz) and is calculated using the following equation:.

$FFREQ[15:0] = \{FFREQH[7:0], FFREQL[7:0]\} = \frac{System Clock Frequency}{1000}$

**Caution:** Flash programming and erasure is not supported for system clock frequencies below 32KHz (32768Hz) or above 20MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to insure proper operation of the Z8F640x family device.

| Table 88. Flash Frequency H | igh Byte Register (FFREQH) |

|-----------------------------|----------------------------|

|-----------------------------|----------------------------|

| BITS  | 7      | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-------|--------|-----|-----|-----|-----|-----|-----|-----|--|--|--|

| FIELD | FFREQH |     |     |     |     |     |     |     |  |  |  |

| RESET | 0      | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

| R/W   | R/W    | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| ADDR  | FFAH   |     |     |     |     |     |     |     |  |  |  |

FFREQH—Flash Frequency High Byte High byte of the 16-bit Flash Frequency value.

#### Table 89. Flash Frequency Low Byte Register (FFREQL)

| BITS  | 7      | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-------|--------|------|-----|-----|-----|-----|-----|-----|--|--|--|

| FIELD | FFREQL |      |     |     |     |     |     |     |  |  |  |

| RESET | 0      | 0    | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

| R/W   | R/W    | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| ADDR  |        | FFBH |     |     |     |     |     |     |  |  |  |

FFREQL—Flash Frequency Low Byte Low byte of the 16-bit Flash Frequency value.

### **Option Bits**

#### **Overview**

Option Bits allow user configuration of certain aspects of Z8F640x family device operation. The feature configuration data is stored in the Program Memory and read during Reset. The features available for control via the Option Bits are:

- Watch-Dog Timer time-out response selection-interrupt or Short Reset.

- Watch-Dog Timer enabled at Reset.

- The ability to prevent unwanted read access to user code in Program Memory.

- The ability to prevent accidental programming and erasure of all or a portion of the user code in Program Memory.

#### Operation

#### **Option Bit Configuration By Reset**

Each time the Option Bits are programmed or erased, the Z8F640x family device must be Reset for the change to take place. During any reset operation (System Reset, Short Reset, or Stop Mode Recovery), the Option Bits are automatically read from the Program Memory and written to Option Configuration registers. The Option Configuration registers control operation of the Z8F640x family device. Option Bit control of the Z8F640x family device is established before the device exits Reset and the eZ8 CPU begins code execution. The Option Configuration registers are not part of the Register File and are not accessible for read or write access.

#### **Option Bit Address Space**

The first two bytes of Program Memory at addresses 0000H and 0001H are reserved for the user Option Bits. The byte at Program Memory address 0000H is used to configure user options. The byte at Program Memory address 0001H is reserved for future use and must be left in its unprogrammed state.

### **On-Chip Debugger**

#### Overview

The Z8F640x family devices have an integrated On-Chip Debugger (OCD) that provides advanced debugging features including:

- Reading and writing of the Register File

- Reading and writing of Program and Data Memory

- Setting of Breakpoints and Watchpoints

- Execution of eZ8 CPU instructions.

#### Architecture

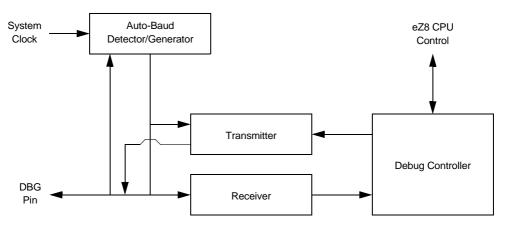

The On-Chip Debugger consists of four primary functional blocks: transmitter, receiver, auto-baud generator, and debug controller. Figure 86 illustrates the architecture of the On-Chip Debugger

Figure 86. On-Chip Debugger Block Diagram

#### Operation

#### **OCD** Interface

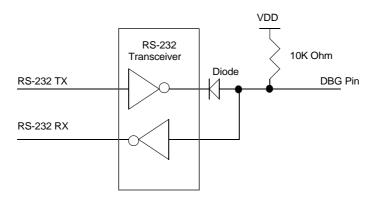

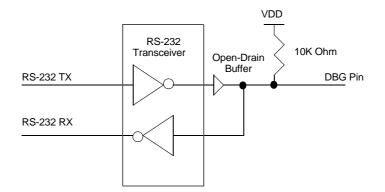

The On-Chip Debugger uses the DBG pin for communication with an external host. This one-pin interface is a bi-directional open-drain interface that transmits and receives data. Data transmission is half-duplex, in that transmit and receive cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin can interface the Z8F640x family device to the serial port of a host PC using minimal external hardware.Two different methods for connecting the DBG pin to an RS-232 interface are depicted in Figures 87 and 88.

### Caution:

For operation of the On-Chip Debugger, *all* power pins (VDD and AVDD) must be supplied with power, and *all* ground pins (VSS and AVSS) must be properly grounded.

The DBG pin is open-drain and must always be connected to  $V_{DD}$  through an external pull-up resistor to ensure proper operation.

Figure 87. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (1)

#### Figure 88. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (2)

#### Debug Mode

The operating characteristics of the Z8F640x family devices in Debug mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions.

- The system clock operates unless in Stop mode.

- All enabled on-chip peripherals operate unless in Stop mode.

- Automatically exits Halt mode.

- Constantly refreshes the Watch-Dog Timer, if enabled.

#### **Entering Debug Mode**

The Z8F640x family device enters Debug mode following any of the following operations:

- Writing the DBGMODE bit in the OCD Control Register to 1 using the OCD interface.

- eZ8 CPU execution of a BRK (Breakpoint) instruction (when enabled).

- Break upon a Watchpoint match.

- If the DBG pin is Low when the Z8F640x family device exits Reset, the On-Chip Debugger automatically puts the device into Debug mode.

#### **Exiting Debug Mode**

The device exits Debug mode following any of the following operations:

• Clearing the DBGMODE bit in the OCD Control Register to 0.

### **On-Chip Oscillator**

The Z8F640x family devices feature an on-chip oscillator for use with an external 1-20MHz crystal. This oscillator generates the primary system clock for the internal eZ8 CPU and the majority of the on-chip peripherals. Alternatively, the X<sub>IN</sub> input pin can also accept a CMOS-level clock input signal (32kHz-20MHz). If an external clock generator is used, the X<sub>OUT</sub> pin must be left unconnected. The Z8F640x family device does *not* contain in internal clock divider. The frequency of the signal on the X<sub>IN</sub> input pin determines the frequency of the system clock. The Z8F640x family device on-chip oscillator does not support external RC networks or ceramic resonators.

#### 20MHz Crystal Oscillator Operation

Figure 90 illustrates a recommended configuration for connection with an external 20MHz, fundamental-mode, parallel-resonant crystal. Recommended crystal specifications are provided in Table 99. Resistor R<sub>1</sub> limits total power dissipation by the crystal. Printed circuit board layout should add no more than 4pF of stray capacitance to either the X<sub>IN</sub> or X<sub>OUT</sub> pins. If oscillation does not occur, reduce the values of capacitors C<sub>1</sub> and C<sub>2</sub> to decrease loading.

#### Table 116. Additional Symbols

| Symbol | Definition                |

|--------|---------------------------|

| dst    | Destination Operand       |

| src    | Source Operand            |

| @      | Indirect Address Prefix   |

| SP     | Stack Pointer             |

| PC     | Program Counter           |

| FLAGS  | Flags Register            |

| RP     | Register Pointer          |

| #      | Immediate Operand Prefix  |

| В      | Binary Number Suffix      |

| %      | Hexadecimal Number Prefix |

| Н      | Hexadecimal Number Suffix |

|        |                           |

Assignment of a value is indicated by an arrow. For example,

$dst \leftarrow dst + src$

indicates the source data is added to the destination data and the result is stored in the destination location.

194

| Assembly        |                                                                                                                   | Addres       | s Mode   | Opcode(s)  |   |   | Fl         | Fotob | Instr. |   |        |   |

|-----------------|-------------------------------------------------------------------------------------------------------------------|--------------|----------|------------|---|---|------------|-------|--------|---|--------|---|

| Mnemonic        | Symbolic Operation                                                                                                | dst          | src      | (Hex)      | С | Z | S          | V     | D      | Н | Cycles |   |

| DA dst          | $dst \leftarrow DA(dst)$                                                                                          | R            |          | 40         | * | * | *          | Х     | -      | - | 2      | 2 |

|                 |                                                                                                                   | IR           |          | 41         | - |   |            |       |        |   | 2      | 3 |

| DEC dst         | $dst \leftarrow dst - 1$                                                                                          | R            |          | 30         | - | * | *          | *     | -      | - | 2      | 2 |

|                 |                                                                                                                   | IR           |          | 31         | - |   |            |       |        |   | 2      | 3 |

| DECW dst        | $dst \leftarrow dst - 1$                                                                                          | RR           |          | 80         | - | * | *          | *     | -      | - | 2      | 5 |

|                 |                                                                                                                   | IRR          |          | 81         | - |   |            |       |        |   | 2      | 6 |

| DI              | $IRQCTL[7] \leftarrow 0$                                                                                          |              |          | 8F         | - | - | -          | -     | -      | - | 1      | 2 |

| DJNZ dst, RA    | $dst \leftarrow dst - 1$<br>if $dst \neq 0$<br>PC \leftarrow PC + X                                               | r            |          | 0A-FA      | - | - | -          | -     | -      | - | 2      | 3 |

| EI              | $IRQCTL[7] \leftarrow 1$                                                                                          |              |          | 9F         | - | - | -          | -     | -      | - | 1      | 2 |

| HALT            | Halt Mode                                                                                                         |              |          | 7F         | - | - | -          | -     | -      | - | 1      | 2 |

| INC dst         | $dst \leftarrow dst + 1$                                                                                          | R            |          | 20         | - | * | *          | *     | -      | - | 2      | 2 |

|                 |                                                                                                                   | IR           |          | 21         | - |   |            |       |        |   | 2      | 3 |

|                 |                                                                                                                   | r            |          | 0E-FE      | - |   |            |       |        |   | 1      | 2 |

| INCW dst        | $dst \leftarrow dst + 1$                                                                                          | RR           |          | A0         | - | * | *          | *     | -      | - | 2      | 5 |

|                 |                                                                                                                   | IRR          |          | A1         | - |   |            |       |        |   | 2      | 6 |

| IRET            | $FLAGS \leftarrow @SP$ $SP \leftarrow SP + 1$ $PC \leftarrow @SP$ $SP \leftarrow SP + 2$ $IRQCTL[7] \leftarrow 1$ |              |          | BF         | * | * | *          | *     | *      | * | 1      | 5 |

| JP dst          | $PC \leftarrow dst$                                                                                               | DA           |          | 8D         | - | - | -          | -     | -      | - | 3      | 2 |

|                 |                                                                                                                   | IRR          |          | C4         | - |   |            |       |        |   | 2      | 3 |

| JP cc, dst      | if cc is true<br>PC ← dst                                                                                         | DA           |          | 0D-FD      | - | - | -          | -     | -      | - | 3      | 2 |

| JR dst          | $\text{PC} \leftarrow \text{PC} + \text{X}$                                                                       | DA           |          | 8B         | - | - | -          | -     | -      | - | 2      | 2 |

| JR cc, dst      | if cc is true<br>PC $\leftarrow$ PC + X                                                                           | DA           |          | 0B-FB      | - | - | -          | -     | -      | - | 2      | 2 |

| Flags Notation: | * = Value is a function<br>- = Unaffected<br>X = Undefined                                                        | of the resul | t of the | operation. |   |   | Res<br>Set | to 1  | 0      |   |        |   |

#### Table 126. eZ8 CPU Instruction Summary (Continued)

| Abbreviation | Description                        | Abbreviation                                   | Description            |

|--------------|------------------------------------|------------------------------------------------|------------------------|

| b            | Bit position                       | IRR                                            | Indirect Register Pair |

| сс           | Condition code                     | р                                              | Polarity (0 or 1)      |

| Х            | 8-bit signed index or displacement | r                                              | 4-bit Working Register |

| DA           | Destination address                | R                                              | 8-bit register         |

| ER           | Extended Addressing register       | r1, R1, Ir1, Irr1, IR1, rr1,<br>RR1, IRR1, ER1 | Destination address    |

| IM           | Immediate data value               | r2, R2, Ir2, Irr2, IR2, rr2,<br>RR2, IRR2, ER2 | Source address         |

| Ir           | Indirect Working Register          | RA                                             | Relative               |

| IR           | Indirect register                  | rr                                             | Working Register Pair  |

| Irr          | Indirect Working Register Pair     | RR                                             | Register Pair          |

#### Table 127. Opcode Map Abbreviations