Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 31                                                        |

| Program Memory Size        | 24KB (24K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 2K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

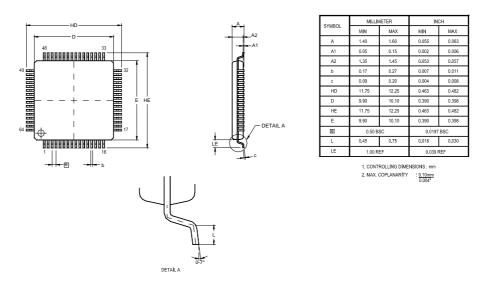

| Package / Case             | 44-LCC (J-Lead)                                           |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f2401vn020sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Manual Objectives

This Product Specification provides detailed operating information for the Z8F640x, Z8F480x, Z8F320x, Z8F240x, and Z8F160x devices within the Z8 Encore!<sup>™</sup> Microcontroller (MCU) family of products. Within this document, the Z8F640x, Z8F480x, Z8F320x, Z8F240x, and Z8F160x are referred to collectively as Z8 Encore!<sup>™</sup> or the Z8F640x family unless specifically stated otherwise.

## **About This Manual**

ZiLOG recommends that the user read and understand everything in this manual before setting up and using the product. However, we recognize that there are different styles of learning. Therefore, we have designed this Product Specification to be used either as a *how to* procedural manual or a reference guide to important data.

## **Intended Audience**

This document is written for ZiLOG customers who are experienced at working with microcontrollers, integrated circuits, or printed circuit assemblies.

## **Manual Conventions**

The following assumptions and conventions are adopted to provide clarity and ease of use:

## **Courier Typeface**

Commands, code lines and fragments, bits, equations, hexadecimal addresses, and various executable items are distinguished from general text by the use of the Courier typeface. Where the use of the font is not indicated, as in the Index, the name of the entity is presented in upper case.

• Example: FLAGS[1] is smrf.

### **Hexadecimal Values**

Hexadecimal values are designated by uppercase *H* suffix and appear in the Courier typeface.

• Example: R1 is set to F8H.

### Brackets

The square brackets, [], indicate a register or bus.

• Example: for the register R1[7:0], R1 is an 8-bit register, R1[7] is the most significant bit, and R1[0] is the least significant bit.

15

| Signal Mnemonic | I/O | Description                                          |

|-----------------|-----|------------------------------------------------------|

| Reset           |     |                                                      |

| RESET           | Ι   | RESET. Generates a Reset when asserted (driven Low). |

| Power Supply    |     |                                                      |

| VDD             | Ι   | Power Supply.                                        |

| AVDD            | Ι   | Analog Power Supply.                                 |

| VSS             | Ι   | Ground.                                              |

| AVSS            | Ι   | Analog Ground.                                       |

#### Table 2. Signal Descriptions (Continued)

# **Pin Characteristics**

Table 3 provides detailed information on the characteristics for each pin available on the Z8F640x family products. Data in Table 3 is sorted alphabetically by the pin symbol mnemonic.

Table 3. Pin Characteristics of the Z8F640x family

| N/A<br>N/A<br>I/O<br>N/A | N/A<br>N/A<br>I   | N/A<br>N/A<br>N/A            | N/A<br>N/A                                    | No<br>No                                 | No<br>No                                         | N/A<br>N/A                                    |

|--------------------------|-------------------|------------------------------|-----------------------------------------------|------------------------------------------|--------------------------------------------------|-----------------------------------------------|

| I/O                      | Ι                 |                              |                                               | No                                       | No                                               | N/A                                           |

|                          |                   | N/A                          |                                               |                                          |                                                  | 1 1/ / 1                                      |

| N/A                      |                   |                              | Yes                                           | No                                       | Yes                                              | Yes                                           |

|                          | N/A               | N/A                          | N/A                                           | No                                       | No                                               | N/A                                           |

| I/O                      | Ι                 | N/A                          | Yes                                           | No                                       | Yes                                              | Yes,<br>Programmable                          |

| I/O                      | Ι                 | N/A                          | Yes                                           | No                                       | Yes                                              | Yes,<br>Programmable                          |

| I/O                      | Ι                 | N/A                          | Yes                                           | No                                       | Yes                                              | Yes,<br>Programmable                          |

| I/O                      | Ι                 | N/A                          | Yes                                           | No                                       | Yes                                              | Yes,<br>Programmable                          |

| I/O                      | Ι                 | N/A                          | Yes                                           | No                                       | Yes                                              | Yes,<br>Programmable                          |

| e                        | I/O<br>I/O<br>I/O | VO I<br>VO I<br>VO I<br>VO I | I/O I N/A   I/O I N/A   I/O I N/A   I/O I N/A | I/OIN/AYesI/OIN/AYesI/OIN/AYesI/OIN/AYes | I/OIN/AYesNoI/OIN/AYesNoI/OIN/AYesNoI/OIN/AYesNo | I/OIN/AYesNoYesI/OIN/AYesNoYesI/OIN/AYesNoYes |

## **External Pin Reset**

The  $\overline{\text{RESET}}$  pin has a Schmitt-triggered input and an internal pull-up. Once the  $\overline{\text{RESET}}$  pin is asserted, the device progresses through the Short Reset sequence. While the  $\overline{\text{RESET}}$  input pin is asserted Low, the Z8F640x family device continues to be held in the Reset state. If the  $\overline{\text{RESET}}$  pin is held Low beyond the Short Reset time-out, the device exits the Reset state immediately following  $\overline{\text{RESET}}$  pin deassertion. Following a Short Reset initiated by the external  $\overline{\text{RESET}}$  pin, the EXT status bit in the Watch-Dog Timer Control (WDTCTL) register is set to 1.

# Stop Mode Recovery

Stop mode is entered by execution of a STOP instruction by the eZ8 CPU. Refer to the **Low-Power Modes** chapter for detailed Stop mode information. During Stop Mode Recovery, the Z8F640x family device is held in reset for 514 cycles of the Watch-Dog Timer oscillator followed by 16 cycles of the system clock (crystal oscillator). Stop Mode Recovery does not affect any values in the Register File, including the Stack Pointer, Register Pointer, Flags and general-purpose RAM.

The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address. Following Stop Mode Recovery, the STOP bit in the Watch-Dog Timer Control Register is set to 1. Table 9 lists the Stop Mode Recovery sources and resulting actions. The text following provides more detailed information on each of the Stop Mode Recovery sources.

| <b>Operating Mode</b> | Stop Mode Recovery Source                                                      | Action                                                               |

|-----------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Stop mode             | Watch-Dog Timer time-out<br>when configured for Reset                          | Stop Mode Recovery                                                   |

|                       | Watch-Dog Timer time-out<br>when configured for interrupt                      | Stop Mode Recovery followed by interrupt (if interrupts are enabled) |

|                       | Data transition on any GPIO Port pin<br>enabled as a Stop Mode Recovery source | Stop Mode Recovery                                                   |

# Stop Mode Recovery Using Watch-Dog Timer Time-Out

If the Watch-Dog Timer times out during Stop mode, the Z8F640x family device undergoes a STOP Mode Recovery sequence. In the Watch-Dog Timer Control register, the WDT and STOP bits are set to 1. If the Watch-Dog Timer is configured to generate an interrupt upon time-out and the device is configured to respond to interrupts, the Z8F640x family device services the Watch-Dog Timer interrupt request following the normal Stop Mode Recovery sequence.

## Port A-H Data Direction Sub-Registers

The Port A-H Data Direction sub-register is accessed through the Port A-H Control register by writing 01H to the Port A-H Address register (Table 15).

Table 15. Port A-H Data Direction Sub-Registers

| BITS  | 7   | 6            | 5            | 4              | 3             | 2            | 1              | 0   |

|-------|-----|--------------|--------------|----------------|---------------|--------------|----------------|-----|

| FIELD | DD7 | DD6          | DD5          | DD4            | DD3           | DD2          | DD1            | DD0 |

| RESET | 1   | 1            | 1            | 1              | 1             | 1            | 1              | 1   |

| R/W   | R/W | R/W          | R/W          | R/W            | R/W           | R/W          | R/W            | R/W |

| ADDR  |     | If 01H in Po | rt A-H Addre | ss Register, a | ccessible via | Port A-H Cor | ntrol Register |     |

#### DD[7:0]—Data Direction

These bits control the direction of the associated port pin. Port Alternate Function operation overrides the Data Direction register setting.

0 =Output. Data in the Port A-H Output Data register is driven onto the port pin. 1 =Input. The port pin is sampled and the value written into the Port A-H Input Data Register. The output driver is tri-stated.

### Port A-H Alternate Function Sub-Registers

The Port A-H Alternate Function sub-register (Table 16) is accessed through the Port A-H Control register by writing 02H to the Port A-H Address register. The Port A-H Alternate Function sub-registers select the alternate functions for the selected pins. Refer to the **GPIO Alternate Functions** section to determine the alternate function associated with each port pin.

**Caution:** Do not enable alternate function for GPIO port pins which do not have an associated alternate function. Failure to follow this guideline may result in unpredictable operation.

| BITS  | 7   | 6            | 5            | 4              | 3             | 2            | 1             | 0   |

|-------|-----|--------------|--------------|----------------|---------------|--------------|---------------|-----|

| FIELD | AF7 | AF6          | AF5          | AF4            | AF3           | AF2          | AF1           | AF0 |

| RESET | 0   | 0            | 0            | 0              | 0             | 0            | 0             | 0   |

| R/W   | R/W | R/W          | R/W          | R/W            | R/W           | R/W          | R/W           | R/W |

| ADDR  |     | If 02H in Po | rt A-H Addre | ss Register, a | ccessible via | Port A-H Cor | trol Register |     |

Table 16. Port A-H Alternate Function Sub-Registers

# Interrupt Controller

# Overview

The interrupt controller on the Z8F640x family device prioritizes the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of the interrupt controller on the Z8F640x family device include the following:

- 24 unique interrupt vectors:

- 12 GPIO port pin interrupt sources

- 12 on-chip peripheral interrupt sources

- Flexible GPIO interrupts

- 8 selectable rising and falling edge GPIO interrupts

- 4 dual-edge interrupts

- 3 levels of individually programmable interrupt priority

- Watch-Dog Timer can be configured to generate an interrupt

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an interrupt service routine (ISR). Usually this interrupt service routine is involved with the exchange of data, status information, or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the interrupt control has no effect on operation. Refer to the eZ8 CPU User Manual for more information regarding interrupt servicing by the eZ8 CPU. The eZ8 CPU User Manual is available for download at www.zilog.com.

## Interrupt Vector Listing

Table 22 lists all of the interrupts available on the Z8F640x family device in order of priority. The interrupt vector is stored with the most significant byte (MSB) at the even Program Memory address and the least significant byte (LSB) at the following odd Program Memory address.

| Priority | Program Memory<br>Vector Address | Interrupt Source                                 | Interrupt Assertion Type |

|----------|----------------------------------|--------------------------------------------------|--------------------------|

| Highest  | 0002h                            | Reset (not an interrupt)                         | Not applicable           |

|          | 0004h                            | Watch-Dog Timer                                  | Continuous assertion     |

|          | 0006h                            | Illegal Instruction Trap (not an interrupt)      | Not applicable           |

|          | 0008h                            | Timer 2                                          | Single assertion (pulse) |

|          | 000Ah                            | Timer 1                                          | Single assertion (pulse) |

|          | 000Ch                            | Timer 0                                          | Single assertion (pulse) |

|          | 000Eh                            | UART 0 receiver                                  | Continuous assertion     |

|          | 0010h                            | UART 0 transmitter                               | Continuous assertion     |

|          | 0012h                            | I <sup>2</sup> C                                 | Continuous assertion     |

|          | 0014h                            | SPI                                              | Continuous assertion     |

|          | 0016h                            | ADC                                              | Single assertion (pulse) |

|          | 0018h                            | Port A7 or Port D7, rising or falling input edge | Single assertion (pulse) |

|          | 001Ah                            | Port A6 or Port D6, rising or falling input edge | Single assertion (pulse) |

|          | 001Ch                            | Port A5 or Port D5, rising or falling input edge | Single assertion (pulse) |

|          | 001Eh                            | Port A4 or Port D4, rising or falling input edge | Single assertion (pulse) |

|          | 0020h                            | Port A3 or Port D3, rising or falling input edge | Single assertion (pulse) |

|          | 0022h                            | Port A2 or Port D2, rising or falling input edge | Single assertion (pulse) |

|          | 0024h                            | Port A1 or Port D1, rising or falling input edge | Single assertion (pulse) |

|          | 0026h                            | Port A0 or Port D0, rising or falling input edge | Single assertion (pulse) |

|          | 0028h                            | Timer 3 (not available in 40/44-pin packages)    | Single assertion (pulse) |

|          | 002Ah                            | UART 1 receiver                                  | Continuous assertion     |

|          | 002Ch                            | UART 1 transmitter                               | Continuous assertion     |

|          | 002Eh                            | DMA                                              | Single assertion (pulse) |

|          | 0030h                            | Port C3, both input edges                        | Single assertion (pulse) |

|          | 0032h                            | Port C2, both input edges                        | Single assertion (pulse) |

|          | 0034h                            | Port C1, both input edges                        | Single assertion (pulse) |

| Lowest   | 0036h                            | Port C0, both input edges                        | Single assertion (pulse) |

|          |                                  |                                                  |                          |

#### Table 22. Interrupt Vectors in Order of Priority

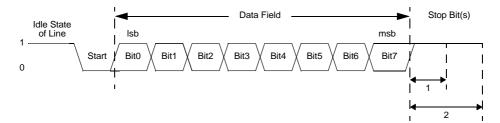

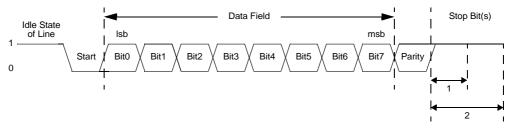

Figure 68. UART Asynchronous Data Format without Parity

Figure 69. UART Asynchronous Data Format with Parity

# **Transmitting Data using the Polled Method**

Follow these steps to transmit data using the polled method of operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the desired baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Write to the UART Control 1 register to enable Multiprocessor (9-bit) mode functions, if desired.

- 4. Write to the UART Control 0 register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission

- Enable parity, if desired, and select either even or odd parity.

- Set or clear the CTSE bit to enable or disable control from the receiver using the  $\overline{\text{CTS}}$  pin.

89

| BITS  | 7 | 6        | 5 | 4       | 3      | 2 | 1 | 0 |  |

|-------|---|----------|---|---------|--------|---|---|---|--|

| FIELD |   | Reserved |   |         |        |   |   |   |  |

| RESET | 0 | 0        | 0 | 0       | 0      | 0 | 0 | 0 |  |

| R/W   | R | R        | R | R       | R      | R | R | R |  |

| ADDR  |   |          |   | F44H ar | d F4CH |   |   |   |  |

#### Table 53. UARTx Status 1 Register (UxSTAT1)

Reserved

These bits are reserved and must be 0.

MPRX—Multiprocessor Receive

This status bit is for the receiver and reflects the actual status of the last multiprocessor bit received. Reading from the UART Data register resets this bit to 0.

# UARTx Control 0 and Control 1 Registers

The UART*x* Control 0 and Control 1 registers (Tables 54 and 55) configure the properties of the UART's transmit and receive operations. The UART Control registers must ben be written while the UART is enabled.

| BITS  | 7   | 6   | 5    | 4       | 3       | 2    | 1    | 0    |

|-------|-----|-----|------|---------|---------|------|------|------|

| FIELD | TEN | REN | CTSE | PEN     | PSEL    | SBRK | STOP | LBEN |

| RESET | 0   | 0   | 0    | 0       | 0       | 0    | 0    | 0    |

| R/W   | R/W | R/W | R/W  | R/W     | R/W     | R/W  | R/W  | R/W  |

| ADDR  |     |     |      | F42H ar | nd F4AH |      |      |      |

Table 54. UARTx Control 0 Register (UxCTL0)

TEN—Transmit Enable

This bit enables or disables the transmitter. The enable is also controlled by the  $\overline{\text{CTS}}$  signal and the CTSE bit. If the  $\overline{\text{CTS}}$  signal is low and the CTSE bit is 1, the transmitter is enabled.

0 = Transmitter disabled.

1 = Transmitter enabled.

REN—Receive Enable

This bit enables or disables the receiver.

- 0 = Receiver disabled.

- 1 =Receiver enabled.

| 10.0 MHz System | Clock       |             |        | 5.5296 MHz Syst | em Clock    |             |       |

|-----------------|-------------|-------------|--------|-----------------|-------------|-------------|-------|

| Desired Rate    | BRG Divisor | Actual Rate | Error  | Desired Rate    | BRG Divisor | Actual Rate | Error |

| (kHz)           | (Decimal)   | (kHz)       | (%)    | (kHz)           | (Decimal)   | (kHz)       | (%)   |

| 1250.0          | N/A         | N/A         | N/A    | 1250.0          | N/A         | N/A         | N/A   |

| 625.0           | 1           | 625.0       | 0.00   | 625.0           | N/A         | N/A         | N/A   |

| 250.0           | 3           | 208.33      | -16.67 | 250.0           | 1           | 345.6       | 38.24 |

| 115.2           | 5           | 125.0       | 8.51   | 115.2           | 3           | 115.2       | 0.00  |

| 57.6            | 11          | 56.8        | -1.36  | 57.6            | 6           | 57.6        | 0.00  |

| 38.4            | 16          | 39.1        | 1.73   | 38.4            | 9           | 38.4        | 0.00  |

| 19.2            | 33          | 18.9        | 0.16   | 19.2            | 18          | 19.2        | 0.00  |

| 9.60            | 65          | 9.62        | 0.16   | 9.60            | 36          | 9.60        | 0.00  |

| 4.80            | 130         | 4.81        | 0.16   | 4.80            | 72          | 4.80        | 0.00  |

| 2.40            | 260         | 2.40        | -0.03  | 2.40            | 144         | 2.40        | 0.00  |

| 1.20            | 521         | 1.20        | -0.03  | 1.20            | 288         | 1.20        | 0.00  |

| 0.60            | 1042        | 0.60        | -0.03  | 0.60            | 576         | 0.60        | 0.00  |

| 0.30            | 2083        | 0.30        | 0.02   | 0.30            | 1152        | 0.30        | 0.00  |

#### Table 58. UART Baud Rates (Continued)

#### 3.579545 MHz System Clock

| Desired Rate | BRG Divisor | Actual Rate | Error  | Desired Rate | BRG Divisor | Actual Rate | Error |

|--------------|-------------|-------------|--------|--------------|-------------|-------------|-------|

| (kHz)        | (Decimal)   | (kHz)       | (%)    | (kHz)        | (Decimal)   | (kHz)       | (%)   |

| 1250.0       | N/A         | N/A         | N/A    | 1250.0       | N/A         | N/A         | N/A   |

| 625.0        | N/A         | N/A         | N/A    | 625.0        | N/A         | N/A         | N/A   |

| 250.0        | 1           | 223.72      | -10.51 | 250.0        | N/A         | N/A         | N/A   |

| 115.2        | 2           | 111.9       | -2.90  | 115.2        | 1           | 115.2       | 0.00  |

| 57.6         | 4           | 55.9        | -2.90  | 57.6         | 2           | 57.6        | 0.00  |

| 38.4         | 6           | 37.3        | -2.90  | 38.4         | 3           | 38.4        | 0.00  |

| 19.2         | 12          | 18.6        | -2.90  | 19.2         | 6           | 19.2        | 0.00  |

| 9.60         | 23          | 9.73        | 1.32   | 9.60         | 12          | 9.60        | 0.00  |

| 4.80         | 47          | 4.76        | -0.83  | 4.80         | 24          | 4.80        | 0.00  |

| 2.40         | 93          | 2.41        | 0.23   | 2.40         | 48          | 2.40        | 0.00  |

| 1.20         | 186         | 1.20        | 0.23   | 1.20         | 96          | 1.20        | 0.00  |

| 0.60         | 373         | 0.60        | -0.04  | 0.60         | 192         | 0.60        | 0.00  |

| 0.30         | 746         | 0.30        | -0.04  | 0.30         | 384         | 0.30        | 0.00  |

|              |             |             |        | -            |             |             |       |

1.8432 MHz System Clock

1 = DMAx is enabled and initiates a data transfer upon receipt of a request from the trigger source.

#### DLE—DMAx Loop Enable

0 = DMAx reloads the original Start Address and is then disabled after the End Address data is transferred.

1 = DMAx, after the End Address data is transferred, reloads the original Start Address and continues operating.

DDIR—DMAx Data Transfer Direction

0 =Register File  $\rightarrow$  on-chip peripheral control register.

1 = on-chip peripheral control register  $\rightarrow$  Register File.

IRQEN—DMAx Interrupt Enable

0 = DMAx does not generate any interrupts.

1 = DMAx generates an interrupt when the End Address data is transferred.

WSEL-Word Select

0 = DMAx transfers a single byte per request.

1 = DMAx transfers a two-byte word per request. The address for the on-chip peripheral control register must be an even address.

#### RSS-Request Trigger Source Select

The Request Trigger Source Select field determines the peripheral that can initiate a DMA request transfer. The corresponding interrupts do not need to be enabled within the Interrupt Controller to initiate a DMA transfer. However, if the Request Trigger Source can enable or disable the interrupt request sent to the Interrupt Controller, the interrupt request must be enabled within the Request Trigger Source block.

- 000 = Timer 0.

- 001 = Timer 1.

- 010 = Timer 2.

- 011 = Timer 3.

100 = DMA0 Control register: UART0 Received Data register contains valid data. DMA1 Control register: UART0 Transmit Data register empty.

101 = DMA0 Control register: UART1 Received Data register contains valid data. DMA1 Control register: UART1 Transmit Data register empty.

110 = DMA0 Control register: I<sup>2</sup>C Receiver Interrupt. DMA1 Control register: I<sup>2</sup>C Transmitter Interrupt register empty.

111 = Reserved.

## DMAx I/O Address Register

The DMAx I/O Address register contains the low byte of the on-chip peripheral address for data transfer. The full 12-bit Register File address is given by {FH, DMAx\_IO[7:0]}.

Table 76 provides an example of the Register File addresses if the DMA\_ADC Address register contains the value 72H.

| ADC Analog Input | Register File Address (Hex) <sup>1</sup> |

|------------------|------------------------------------------|

| 0                | 720H-721H                                |

| 1                | 722H-723H                                |

| 2                | 724H-725H                                |

| 3                | 726H-727H                                |

| 4                | 728H-729H                                |

| 5                | 72AH-72BH                                |

| 6                | 72CH-72DH                                |

| 7                | 72EH-72FH                                |

| 8                | 730H-731H                                |

| 9                | 732H-733H                                |

| 10               | 734H-735H                                |

| 11               | 736H-737H                                |

| 1                |                                          |

Table 76. DMA\_ADC Register File Address Example

<sup>1</sup> DMAA\_ADDR set to 72H.

Table 77. DMA\_ADC Address Register (DMAA\_ADDR)

| BITS  | 7   | 6           | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-------|-----|-------------|-----|-----|-----|-----|-----|-----|--|--|--|

| FIELD |     | DMAA_ADDR 1 |     |     |     |     |     |     |  |  |  |

| RESET | Х   | X X X X X   |     | Х   | Х   | Х   |     |     |  |  |  |

| R/W   | R/W | R/W         | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| ADDR  |     |             |     | FB  | DH  |     |     |     |  |  |  |

## DMAA\_ADDR—DMA\_ADC Address

These bits specify the seven most-significant bits of the 12-bit Register File addresses used for storing the ADC output data. The ADC Analog Input Number defines the five least-significant bits of the Register File address. Full 12-bit address is {DMAA\_ADDR[7:1], 4-bit ADC Analog Input Number, 0}.

Reserved This bit is reserved and must be 0.

131

## **DMA Status Register**

The DMA Status register indicates the DMA channel that generated the interrupt and the ADC Analog Input that is currently undergoing conversion. Reads from this register reset the Interrupt Request Indicator bits (IRQA, IRQ1, and IRQ0) to 0. Therefore, software interrupt service routines that read this register must process all three interrupt sources from the DMA.

| Table 79. DMA_ADC Status Register (DMAA_STAT) |

|-----------------------------------------------|

|-----------------------------------------------|

| BITS  | 7 | 6   | 5      | 4  | 3        | 2    | 1    | 0    |  |

|-------|---|-----|--------|----|----------|------|------|------|--|

| FIELD |   | CAD | C[3:0] |    | Reserved | IRQA | IRQ1 | IRQ0 |  |

| RESET | 0 | 0   | 0      | 0  | 0        | 0    | 0    | 0    |  |

| R/W   | R | R   | R      | R  | R        | R    | R    | R    |  |

| ADDR  |   |     |        | FB | FH       |      |      |      |  |

CADC[3:0]—Current ADC Analog Input

This field identifies the Analog Input that the ADC is currently converting.

Reserved

This bit is reserved and must be 0.

IRQA—DMA\_ADC Interrupt Request Indicator

This bit is automatically reset to 0 each time a read from this register occurs.

$0 = DMA\_ADC$  is not the source of the interrupt from the DMA Controller.

1 = DMA\_ADC completed transfer of data from the last ADC Analog Input and generated an interrupt.

IRQ1—DMA1 Interrupt Request Indicator

This bit is automatically reset to 0 each time a read from this register occurs.

0 = DMA1 is not the source of the interrupt from the DMA Controller.

1 = DMA1 completed transfer of data to/from the End Address and generated an interrupt.

IRQ0—DMA0 Interrupt Request Indicator

This bit is automatically reset to 0 each time a read from this register occurs.

0 = DMA0 is not the source of the interrupt from the DMA Controller.

1 = DMA0 completed transfer of data to/from the End Address and generated an interrupt.

- Set CONT to 1 to select continuous conversion.

- Write to VREF to enable or disable the internal voltage reference generator.

- Set CEN to 1 to start the conversions.

- 3. When the first conversion in continuous operation is complete (after 5129 system clock cycles, plus the 40 cycles for power-up, if necessary), the ADC control logic performs the following operations:

- CEN resets to 0 to indicate the first conversion is complete. CEN remains 0 for all subsequent conversions in continuous operation.

- An interrupt request is sent to the Interrupt Controller to indicate the *first* conversion is complete. An interrupt request is not sent for subsequent conversions in continuous operation.

- 4. Thereafter, the ADC writes a new 10-bit data result to {ADCD\_H[7:0], ADCD\_L[7:6]} every 256 system clock cycles.

- 5. To disable continuous conversion, clear the CONT bit in the ADC Control register to 0.

## **DMA Control of the ADC**

The Direct Memory Access (DMA) Controller can control operation of the ADC including analog input selection and conversion enable. For more information on the DMA and configuring for ADC operations refer to the **Direct Memory Access Controller** chapter.

# **ADC Control Register Definitions**

## **ADC Control Register**

The ADC Control register selects the analog input channel and initiates the analog-to-digital conversion.

| BITS  | 7   | 6        | 5    | 4    | 3          | 0 |  |  |  |  |  |  |

|-------|-----|----------|------|------|------------|---|--|--|--|--|--|--|

| FIELD | CEN | Reserved | VREF | CONT | ANAIN[3:0] |   |  |  |  |  |  |  |

| RESET | 0   | 0        | 0    | 0    | 0000       |   |  |  |  |  |  |  |

| R/W   | R/W | R/W      | R/W  | R/W  | R/W        |   |  |  |  |  |  |  |

| ADDR  |     |          |      | F7   | 0H         |   |  |  |  |  |  |  |

| Table 80. | ADC | Control | Register | (ADCCTL) |

|-----------|-----|---------|----------|----------|

|-----------|-----|---------|----------|----------|

CEN—Conversion Enable

0 = Conversion is complete. Writing a 0 produces no effect. The ADC automatically clears

# Flash Memory

# **Overview**

The Z8F640x family features up to 64KB (65,536 bytes) of non-volatile Flash memory with read/write/erase capability. The Flash Memory can be programmed and erased in-circuit by either user code or through the On-Chip Debugger.

The Flash memory array is arranged in pages with 512 bytes per page. The 512-byte page is the minimum Flash block size that can be erased. Each page is divided into 8 rows of 64 bytes. The Flash memory also contains a High Sector that can be enabled for writes and erase separately from the rest of the Flash array. The first 2 bytes of the Flash Program memory are used as Option Bits. Refer to the **Option Bits** chapter for more information on their operation.

Table 83 describes the Flash memory configuration for each device in the Z8F640x family. Figure 84 illustrates the Flash memory arrangement.

| Part Number | Flash Size<br>KB (Bytes) | Flash<br>Pages | Program Memory<br>Addresses | Flash High Sector Size<br>KB (Bytes) | High Sector<br>Addresses |

|-------------|--------------------------|----------------|-----------------------------|--------------------------------------|--------------------------|

| Z8F160x     | 16 (16,384)              | 32             | 0000H - 3FFFH               | 1 (1024)                             | 3C00H - 3FFFH            |

| Z8F240x     | 24 (24,576)              | 48             | 0000H - 5FFFH               | 2 (2048)                             | 5800H - 5FFFH            |

| Z8F320x     | 32 (32,768)              | 64             | 0000H - 7FFFH               | 2 (2048)                             | 7800H - 7FFFH            |

| Z8F480x     | 48 (49,152)              | 96             | 0000H - BFFFH               | 4 (4096)                             | B000H - BFFFH            |

| Z8F640x     | 64 (65,536)              | 128            | 0000H - FFFFH               | 8 (8192)                             | E000H - FFFFH            |

#### Table 83. Z8F640x family Flash Memory Configurations

## **Flash Status Register**

The Flash Status register indicates the current state of the Flash Controller. This register can be read at any time. The Read-only Flash Status Register shares its Register File address with the Write-only Flash Control Register.

| BITS  | 7    | 6     | 5 | 4 | 3     | 2 | 1 | 0 |  |  |  |

|-------|------|-------|---|---|-------|---|---|---|--|--|--|

| FIELD | Rese | erved |   |   | FSTAT |   |   |   |  |  |  |

| RESET | 0    | 0     | 0 | 0 | 0     |   |   |   |  |  |  |

| R/W   | R    | R     | R | R | R     | R | R | R |  |  |  |

| ADDR  |      | FF8H  |   |   |       |   |   |   |  |  |  |

Reserved

These bits are reserved and must be 0.

FSTAT—Flash Controller Status

000000 = Flash Controller locked.

000001 = First unlock command received.

000010 = Flash Controller unlocked (second unlock command received).

001xxx = Program operation in progress.

010xxx = Page erase operation in progress.

100xxx = Mass erase operation in progress.

# **Option Bits**

# **Overview**

Option Bits allow user configuration of certain aspects of Z8F640x family device operation. The feature configuration data is stored in the Program Memory and read during Reset. The features available for control via the Option Bits are:

- Watch-Dog Timer time-out response selection-interrupt or Short Reset.

- Watch-Dog Timer enabled at Reset.

- The ability to prevent unwanted read access to user code in Program Memory.

- The ability to prevent accidental programming and erasure of all or a portion of the user code in Program Memory.

# Operation

## **Option Bit Configuration By Reset**

Each time the Option Bits are programmed or erased, the Z8F640x family device must be Reset for the change to take place. During any reset operation (System Reset, Short Reset, or Stop Mode Recovery), the Option Bits are automatically read from the Program Memory and written to Option Configuration registers. The Option Configuration registers control operation of the Z8F640x family device. Option Bit control of the Z8F640x family device is established before the device exits Reset and the eZ8 CPU begins code execution. The Option Configuration registers are not part of the Register File and are not accessible for read or write access.

# **Option Bit Address Space**

The first two bytes of Program Memory at addresses 0000H and 0001H are reserved for the user Option Bits. The byte at Program Memory address 0000H is used to configure user options. The byte at Program Memory address 0001H is reserved for future use and must be left in its unprogrammed state.

178

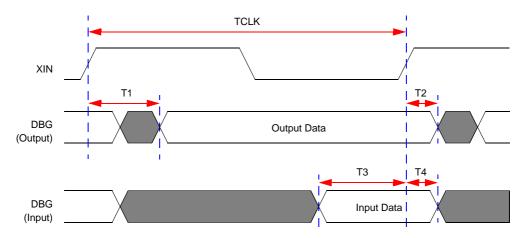

# **On-Chip Debugger Timing**

Figure 95 and Table 109 provide timing information for DBG pins. The timing specifications presume a rise and fall time on DBG of less than  $4\mu$ s.

Figure 95. On-Chip Debugger Timing

|                |                                  | Dela    | y (ns)              |

|----------------|----------------------------------|---------|---------------------|

| Parameter      | Abbreviation                     | Minimum | Maximum             |

| DBG            |                                  |         |                     |

| T <sub>1</sub> | XIN Rise to DBG Valid Delay      | _       | 15                  |

| T <sub>2</sub> | XIN Rise to DBG Output Hold Time | 2       | _                   |

| T <sub>3</sub> | DBG to XIN Rise Input Setup Time | 10      | _                   |

| T <sub>4</sub> | DBG to XIN Rise Input Hold Time  | 5       | _                   |

|                | DBG frequency                    |         | System<br>Clock / 4 |

| Table | 109. | <b>On-Chip</b> | Debugger | Timing |

|-------|------|----------------|----------|--------|

| Inoie | 10/1 | on omp         | Debugger |        |

# Z8F640x/Z8F480x/Z8F320x/Z8F240x/Z8F160x Z8 Encore!®

204

|                           |                          |                                  |                                  |                                     |                                     |                                  | Le                                  | ower Nil                       | ble (He                | x)                    |                     |                   |                    |                           |                  |                          |

|---------------------------|--------------------------|----------------------------------|----------------------------------|-------------------------------------|-------------------------------------|----------------------------------|-------------------------------------|--------------------------------|------------------------|-----------------------|---------------------|-------------------|--------------------|---------------------------|------------------|--------------------------|

|                           | 0                        | 1                                | 2                                | 3                                   | 4                                   | 5                                | 6                                   | 7                              | 8                      | 9                     | А                   | В                 | С                  | D                         | Е                | F                        |

| 0                         | 1.2<br>BRK               | 2.2<br>SRP<br>IM                 | 2.3<br>ADD<br>r1,r2              | 2.4<br>ADD<br>r1,lr2                | 3.3<br>ADD<br>R2,R1                 | 3.4<br>ADD<br>IR2,R1             | 3.3<br>ADD<br>R1,IM                 | 3.4<br>ADD<br>IR1,IM           | 4.3<br>ADDX<br>ER2,ER1 | 4.3<br>ADDX<br>IM,ER1 | 2.3<br>DJNZ<br>r1,X | 2.2<br>JR<br>cc,X | 2.2<br>LD<br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br>INC<br>r1 | 1.2<br>NOP               |

| 1                         | 2.2<br>RLC<br>R1         | 2.3<br>RLC<br>IR1                | 2.3<br>ADC<br>r1,r2              | 2.4<br>ADC<br>r1,lr2                | 3.3<br>ADC<br>R2,R1                 | 3.4<br>ADC<br>IR2,R1             | 3.3<br>ADC<br>R1,IM                 | 3.4<br>ADC<br>IR1,IM           | 4.3<br>ADCX<br>ER2,ER1 | 4.3<br>ADCX<br>IM,ER1 |                     |                   |                    |                           |                  | See 2nd<br>Opcode<br>Map |

| 2                         | 2.2<br>INC<br>R1         | 2.3<br>INC<br>IR1                | 2.3<br>SUB<br>r1,r2              | 2.4<br>SUB<br>r1,lr2                | 3.3<br>SUB<br>R2,R1                 | 3.4<br>SUB<br>IR2,R1             | 3.3<br>SUB<br>R1,IM                 | 3.4<br>SUB<br>IR1,IM           | 4.3<br>SUBX<br>ER2,ER1 | 4.3<br>SUBX<br>IM,ER1 |                     |                   |                    |                           |                  |                          |

| 3                         | 2.2<br>DEC<br>R1         | 2.3<br>DEC<br>IR1                | 2.3<br>SBC<br>r1,r2              | 2.4<br>SBC<br>r1,lr2                | 3.3<br>SBC<br>R2,R1                 | 3.4<br>SBC<br>IR2,R1             | 3.3<br>SBC<br>R1,IM                 | 3.4<br>SBC<br>IR1,IM           | 4.3<br>SBCX<br>ER2,ER1 | 4.3<br>SBCX           |                     |                   |                    |                           |                  |                          |

| 4                         | 2.2<br>DA<br>R1          | 2.3<br>DA<br>IR1                 | 2.3<br>OR<br>r1,r2               | 2.4<br>OR<br>r1,lr2                 | 3.3<br>OR                           | 3.4<br>OR<br>IR2,R1              | 3.3<br>OR                           | 3.4<br>OR<br>IR1,IM            | 4.3<br>ORX<br>ER2,ER1  | 4.3<br>ORX<br>IM,ER1  |                     |                   |                    |                           |                  |                          |

| 5                         | 2.2<br>POP               | 2.3<br>POP<br>IR1                | 2.3<br>AND<br>r1,r2              | 2.4<br>AND<br>r1,lr2                | R2,R1<br>3.3<br><b>AND</b><br>R2,R1 | 3.4<br>AND<br>IR2,R1             | R1,IM<br>3.3<br><b>AND</b><br>R1,IM | 3.4<br>AND<br>IR1,IM           | 4.3<br>ANDX<br>ER2,ER1 | 4.3<br>ANDX<br>IM,ER1 |                     |                   |                    |                           |                  | 1.2<br>WDT               |

| 6                         | R1<br>2.2<br>COM<br>R1   | 2.3<br>COM<br>IR1                | 2.3<br>TCM<br>r1,r2              | 2.4<br>TCM<br>r1,lr2                | 3.3<br>TCM<br>R2,R1                 | 3.4<br>TCM<br>IR2,R1             | 3.3<br>TCM<br>R1,IM                 | 3.4<br>TCM<br>IR1,IM           | 4.3<br>TCMX<br>ER2,ER1 | 4.3<br>TCMX<br>IM,ER1 |                     |                   |                    |                           |                  | STOP                     |

| XeH) ol                   | 2.2<br>PUSH              | 2.3<br>PUSH<br>IR2               | 2.3<br>TM                        | 2.4<br>TM                           | 3.3<br>TM                           | 3.4<br>TM                        | 3.3<br>TM                           | 3.4<br>TM                      | 4.3<br>TMX             | 4.3<br>TMX            |                     |                   |                    |                           |                  | 1.2<br>HALT              |

| Upper Nibble (Hex)<br>8 2 | R2<br>2.5<br>DECW<br>RR1 | 2.6<br>DECW<br>IRR1              | r1,r2<br>2.5<br>LDE              | r1,lr2<br>2.9<br>LDEI               | 82,R1<br>3.2<br>LDX                 | 3.3<br>LDX                       | 81,IM<br>3.4<br>LDX                 | 3.5<br>LDX                     | 3.4<br>LDX             | 3.4<br>LDX            |                     |                   |                    |                           |                  | 1.2<br>DI                |

| <b>1</b><br>9             | 2.2<br>RL<br>R1          | 2.3<br>RL<br>IR1                 | r1,Irr2<br>2.5<br>LDE<br>r2,Irr1 | 1r1,1rr2<br>2.9<br>LDEI<br>1r2,1rr1 | r1,ER2<br>3.2<br>LDX<br>r2,ER1      | 1r1,ER2<br>3.3<br>LDX<br>Ir2,ER1 | 3.4<br>LDX                          | 3.5<br>LDX<br>IR2,IRR1         | r1,rr2,X<br>3.3<br>LEA | 3.5<br>LEA            |                     |                   |                    |                           |                  | 1.2<br>El                |

| A                         | 2.5<br>INCW              | 2.6<br>INCW                      | 2.3<br>CP                        | 2.4<br>CP                           | 3.3<br>CP                           | 3.4<br>CP                        | 3.3<br>CP                           | 3.4<br>CP                      | r1,r2,X<br>4.3<br>CPX  | 4.3<br>CPX            |                     |                   |                    |                           |                  | 1.4<br>RET               |

| В                         | 2.2<br>CLR               | IRR1<br>2.3<br><b>CLR</b><br>IR1 | r1,r2<br>2.3<br>XOR              | r1,lr2<br>2.4<br>XOR                | 82,R1<br>3.3<br>XOR                 | 3.4<br>XOR                       | 81,IM<br>3.3<br><b>XOR</b>          | 3.4<br>XOR                     | 4.3<br>XORX            | 4.3<br>XORX           |                     |                   |                    |                           |                  | 1.5<br>IRET              |

| С                         | R1<br>2.2<br>RRC<br>R1   | 2.3<br>RRC<br>IR1                | r1,r2<br>2.5<br>LDC<br>r1,lrr2   | r1,lr2<br>2.9<br>LDCI<br>lr1,lrr2   | R2,R1<br>2.3<br>JP<br>IRR1          | 2.9<br>LDC                       | R1,IM                               | IR1,IM<br>3.3<br>LD<br>r1,r2,X | 3.2<br>PUSHX<br>ER2    | IM,ER1                |                     |                   |                    |                           |                  | 1.2<br>RCF               |

| D                         | 2.2<br>SRA<br>R1         | 2.3<br>SRA<br>IR1                | 2.5<br>LDC<br>r2,lrr1            | 2.9<br>LDCI<br>Ir2,Irr1             | 2.6                                 | Ir1,Irr2<br>2.2<br>BSWAP<br>R1   | 3.3<br>CALL<br>DA                   | 3.4<br>LD<br>r2,r1,X           | 3.2<br>POPX<br>ER1     |                       |                     |                   |                    |                           |                  | 1.2<br>SCF               |

| E                         | 2.2<br>RR                | 2.3<br>RR<br>IR1                 | 2.2<br>BIT                       | 2.3<br>LD                           | 3.2<br>LD<br>R2,R1                  | 3.3<br>LD<br>IR2,R1              | 3.2<br>LD<br>R1,IM                  | 3.3<br>LD<br>IR1,IM            | 4.2<br>LDX<br>ER2,ER1  | 4.2<br>LDX<br>IM,ER1  |                     |                   |                    |                           |                  | 1.2<br>CCF               |

| F                         | R1<br>2.2<br>SWAP<br>R1  | 2.3<br>SWAP<br>IR1               | p,b,r1<br>2.6<br>TRAP<br>Vector  | r1,lr2<br>2.3<br>LD<br>lr1,r2       | 2.8<br>MULT<br>RR1                  | 3.3<br>LD<br>R2,IR1              | 3.3<br>BTJ                          | 3.4<br>BTJ<br>p,b,lr1,X        | EKZ,EK1                | IIVI,ER1              |                     | V                 |                    |                           |                  |                          |

Figure 101. First Opcode Map

## Z8F640x/Z8F480x/Z8F320x/Z8F240x/Z8F160x Z8 Encore!®

Figure 105 illustrates the 64-pin LQFP (low-profile quad flat package) available for the Z8F1602, Z8F2402, Z8F3202, Z8F4802, and Z8F6402 devices.

Figure 106. 64-Lead Low-Profile Quad Flat Package (LQFP)

register 109, 126, 184 ADC control (ADCCTL) 135 ADC data high byte (ADCDH) 137 ADC data low bits (ADCDL) 137 baud low and high byte (I2C) 121 baud rate high and low byte (SPI) 110 control (SPI) 107 control, I2C 119 data, SPI 106 DMA status (DMAA\_STAT) 131 DMA\_ADC address 128 DMA\_ADC control DMAACTL) 130 DMAx address high nibble (DMAxH) 126 DMAx control (DMAxCTL) 124 DMAx end/address low byte (DMAxEND) 128 DMAx start/current address low byte register (DMAxSTART) 128 flash control (FCTL) 144 flash high and low byte (FFREQH and FREEQL) 147 flash page select (FPS) 146 flash status (FSTAT) 145 GPIO port A-H address (PxADDR) 37 GPIO port A-H alternate function sub-registers 39 GPIO port A-H control address (PxCTL) 38 GPIO port A-H data direction sub-registers 39 I2C baud rate high (I2CBRH) 121 I2C control (I2CCTL) 119 I2C data (I2CDATA) 118 I2C status 118 I2C status (I2CSTAT) 118 I2Cbaud rate low (I2CBRL) 121 mode, SPI 109 OCD control 161 OCD status 162 OCD watchpoint address 164 OCD watchpoint control 163 OCD watchpoint data 164 SPI baud rate high byte (SPIBRH) 110 SPI baud rate low byte (SPIBRL) 110 SPI control (SPICTL) 107 SPI data (SPIDATA) 106 SPI status (SPISTAT) 108

status, I2C 118 status, SPI 108 UARTx baud rate high byte (UxBRH) 91 UARTx baud rate low byte (UxBRL) 92 UARTx Control 0 (UxCTL0) 89 UARTx control 1 (UxCTL1) 90 UARTx receive data (UxRXD) 87 UARTx status 0 (UxSTAT0) 87 UARTx status 1 (UxSTAT1) 89 UARTx transmit data (UxTXD) 86 watch-dog timer control (WDTCTL) 75 watch-dog timer reload high byte (WDTH) 76 watch-dog timer reload low byte (WDTL) 77 watch-dog timer reload upper byte (WDTU) 76 register file 17 register file address map 20 register pair 184 register pointer 185 reset and stop mode characteristics 25 and stop mode recovery 25 carry flag 188 controller 5 sources 26 **RET 190** return 190 return information 216 RL 191 **RLC 191** rotate and shift instructions 191 rotate left 191 rotate left through carry 191 rotate right 191 rotate right through carry 191 RP 185 RR 184, 191 rr 184 **RRC 191**

# S

SBC 188 SCF 188, 189 SCK 101