Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 46                                                        |

| Program Memory Size        | 24KB (24K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 2K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 12x10b                                                |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 64-LQFP                                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f2402ar020sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Option Bits                                                 |

|-------------------------------------------------------------|

| Overview                                                    |

| Operation                                                   |

| Option Bit Configuration By Reset                           |

| Option Bit Address Space                                    |

| Program Memory Address 0000H 149                            |

| Program Memory Address 0001H 150                            |

| On-Chip Debugger                                            |

| Overview                                                    |

| Architecture                                                |

| Operation                                                   |

| OCD Interface                                               |

| Debug Mode                                                  |

| OCD Data Format                                             |

| OCD Auto-Baud Detector/Generator                            |

| OCD Serial Errors 155                                       |

| Breakpoints                                                 |

| Watchpoints                                                 |

| Runtime Counter                                             |

| On-Chip Debugger Commands 156                               |

| On-Chip Debugger Control Register Definitions               |

| OCD Control Register 161                                    |

| OCD Status Register 162                                     |

| OCD Watchpoint Control Register                             |

| OCD Watchpoint Address Register                             |

| OCD Watchpoint Data Register                                |

| On-Chip Oscillator                                          |

| 20MHz Crystal Oscillator Operation                          |

| Electrical Characteristics                                  |

| Absolute Maximum Ratings 167                                |

| DC Characteristics                                          |

| AC Characteristics                                          |

| On-Chip Peripheral AC and DC Electrical Characteristics 173 |

| General Purpose I/O Port Input Data Sample Timing           |

| General Purpose I/O Port Output Timing 177                  |

| On-Chip Debugger Timing 178                                 |

| SPI Master Mode Timing 179                                  |

| SPI Slave Mode Timing 180                                   |

| I2C Timing                                                  |

| eZ8 CPU Instruction Set                                     |

| Assembly Language Programming Introduction                  |

## **Signal Descriptions**

Table 2 describes the Z8F640x family signals. Refer to the section **Pin Configurations on page 7** to determine the signals available for the specific package styles.

| Signal Mnemonic             | I/O       | Description                                                                                                                                                                                                                                                                           |

|-----------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General-Purpose I/C         | ) Ports A | -Н                                                                                                                                                                                                                                                                                    |

| PA[7:0]                     | I/O       | Port A[7:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                             |

| PB[7:0]                     | I/O       | Port B[7:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                             |

| PC[7:0]                     | I/O       | Port C[7:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                             |

| PD[7:0]                     | I/O       | Port D[7:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                             |

| PE[7:0]                     | I/O       | Port E[7:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                             |

| PF[7:0]                     | I/O       | Port F[7:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                             |

| PG[7:0]                     | I/O       | Port G[7:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                             |

| PH[3:0]                     | I/O       | Port H[3:0]. These pins are used for general-purpose I/O.                                                                                                                                                                                                                             |

| I <sup>2</sup> C Controller |           |                                                                                                                                                                                                                                                                                       |

| SCL                         | 0         | Serial Clock. This is the output clock for the I <sup>2</sup> C. This pin is multiplexed with a general-purpose I/O pin. When the general-purpose I/O pin is configured for alternate function to enable the SCL function, this pin is open-drain.                                    |

| SDA                         | I/O       | Serial Data. This open-drain pin is used to transfer data between the I <sup>2</sup> C and a slave. This pin is multiplexed with a general-purpose I/O pin. When the general-purpose I/O pin is configured for alternate function to enable the SDA function, this pin is open-drain. |

| SPI Controller              |           |                                                                                                                                                                                                                                                                                       |

| SS                          | I/O       | Slave Select. This signal can be an output or an input. If the Z8 Encore! is the SPI master, this pin may be configured as the Slave Select output. If the Z8 Encore! is the SPI slave, this pin is the input slave select. It is multiplexed with a general-purpose I/O pin.         |

| SCK                         | I/O       | SPI Serial Clock. The SPI master supplies this pin. If the Z8 Encore! is the SPI master, this pin is an output. If the Z8 Encore! is the SPI slave, this pin is an input. It is multiplexed with a general-purpose I/O pin.                                                           |

| MOSI                        | I/O       | Master Out Slave In. This signal is the data output from the SPI master device and the data input to the SPI slave device. It is multiplexed with a general-purpose I/O pin.                                                                                                          |

| MISO                        | I/O       | Master In Slave Out. This pin is the data input to the SPI master device and the data output from the SPI slave device. It is multiplexed with a general-purpose I/O pin.                                                                                                             |

Table 2. Signal Descriptions

## System and Short Resets

During a System Reset, the Z8F640x family device is held in Reset for 514 cycles of the Watch-Dog Timer oscillator followed by 16 cycles of the system clock (crystal oscillator). A Short Reset differs from a System Reset only in the number of Watch-Dog Timer oscillator cycles required to exit Reset. A Short Reset requires only 66 Watch-Dog Timer oscillator cycles. Unless specifically stated otherwise, System Reset and Short Reset are referred to collectively as Reset.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watch-Dog Timer oscillator continue to run. The system clock begins operating following the Watch-Dog Timer oscillator cycle count. The eZ8 CPU and on-chip peripherals remain idle through the 16 cycles of the system clock.

Upon Reset, control registers within the Register File that have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer, and Flags) and general-purpose RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

## **Reset Sources**

Table 8 lists the reset sources and type of Reset as a function of the Z8F640x family device operating mode. The text following provides more detailed information on the individual Reset sources. Please note that Power-On Reset / Voltage Brown-Out events always have priority over all other possible reset sources to insure a full system reset occurs.

| <b>Operating Mode</b> | Reset Source                                             | Reset Type                                                          |

|-----------------------|----------------------------------------------------------|---------------------------------------------------------------------|

| Normal or Halt modes  | Power-On Reset / Voltage Brown-Out                       | System Reset                                                        |

|                       | Watch-Dog Timer time-out<br>when configured for Reset    | Short Reset                                                         |

|                       | RESET pin assertion                                      | Short Reset                                                         |

|                       | On-Chip Debugger initiated Reset<br>(OCDCTL[1] set to 1) | System Reset except the On-Chip Debugger is unaffected by the reset |

| Stop mode             | Power-On Reset / Voltage Brown-Out                       | System Reset                                                        |

|                       | RESET pin assertion                                      | System Reset                                                        |

|                       | DBG pin driven Low                                       | System Reset                                                        |

Table 8. Reset Sources and Resulting Reset Type

## Port A-H Data Direction Sub-Registers

The Port A-H Data Direction sub-register is accessed through the Port A-H Control register by writing 01H to the Port A-H Address register (Table 15).

Table 15. Port A-H Data Direction Sub-Registers

| BITS  | 7   | 6                                                                             | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------|-----|-------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|--|

| FIELD | DD7 | DD6                                                                           | DD5 | DD4 | DD3 | DD2 | DD1 | DD0 |  |

| RESET | 1   | 1                                                                             | 1   | 1   | 1   | 1   | 1   | 1   |  |

| R/W   | R/W | R/W                                                                           | R/W | R/W | R/W | R/W | R/W | R/W |  |

| ADDR  |     | If 01H in Port A-H Address Register, accessible via Port A-H Control Register |     |     |     |     |     |     |  |

#### DD[7:0]—Data Direction

These bits control the direction of the associated port pin. Port Alternate Function operation overrides the Data Direction register setting.

0 =Output. Data in the Port A-H Output Data register is driven onto the port pin. 1 =Input. The port pin is sampled and the value written into the Port A-H Input Data Register. The output driver is tri-stated.

#### Port A-H Alternate Function Sub-Registers

The Port A-H Alternate Function sub-register (Table 16) is accessed through the Port A-H Control register by writing 02H to the Port A-H Address register. The Port A-H Alternate Function sub-registers select the alternate functions for the selected pins. Refer to the **GPIO Alternate Functions** section to determine the alternate function associated with each port pin.

**Caution:** Do not enable alternate function for GPIO port pins which do not have an associated alternate function. Failure to follow this guideline may result in unpredictable operation.

| BITS  | 7   | 6                                                                             | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------|-----|-------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|--|

| FIELD | AF7 | AF6                                                                           | AF5 | AF4 | AF3 | AF2 | AF1 | AF0 |  |

| RESET | 0   | 0                                                                             | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W   | R/W | R/W                                                                           | R/W | R/W | R/W | R/W | R/W | R/W |  |

| ADDR  |     | If 02H in Port A-H Address Register, accessible via Port A-H Control Register |     |     |     |     |     |     |  |

Table 16. Port A-H Alternate Function Sub-Registers

52

| BITS  | 7     | 6     | 5     | 4             | 3      | 2      | 1      | 0      |  |  |

|-------|-------|-------|-------|---------------|--------|--------|--------|--------|--|--|

| FIELD | T2ENL | T1ENL | T0ENL | <b>U0RENL</b> | U0TENL | I2CENL | SPIENL | ADCENL |  |  |

| RESET | 0     | 0     | 0     | 0             | 0      | 0      | 0      | 0      |  |  |

| R/W   | R/W   | R/W   | R/W   | R/W           | R/W    | R/W    | R/W    | R/W    |  |  |

| ADDR  |       | FC2H  |       |               |        |        |        |        |  |  |

#### Table 28. IRQ0 Enable Low Bit Register (IRQ0ENL)

T2ENL—Timer 2 Interrupt Request Enable Low Bit T1ENL—Timer 1 Interrupt Request Enable Low Bit T0ENL—Timer 0 Interrupt Request Enable Low Bit U0RENL—UART 0 Receive Interrupt Request Enable Low Bit U0TENL—UART 0 Transmit Interrupt Request Enable Low Bit I2CENL—I<sup>2</sup>C Interrupt Request Enable Low Bit SPIENL—SPI Interrupt Request Enable Low Bit ADCENL—ADC Interrupt Request Enable Low Bit

## **IRQ1 Enable High and Low Bit Registers**

The IRQ1 Enable High and Low Bit registers (Tables 30 and 31) form a priority encoded enabling for interrupts in the Interrupt Request 1 register. Priority is generated by setting bits in each register. Table 29 describes the priority control for IRQ1.

| IRQ1ENH[x] | IRQ1ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

| 1          | 1          | Level 3  | High        |

Table 29. IRQ1 Enable and Priority Encoding

where *x* indicates the register bits from 0 through 7.

#### Z8F640x/Z8F480x/Z8F320x/Z8F240x/Z8F160x Z8 Encorel<sup>®</sup>

58

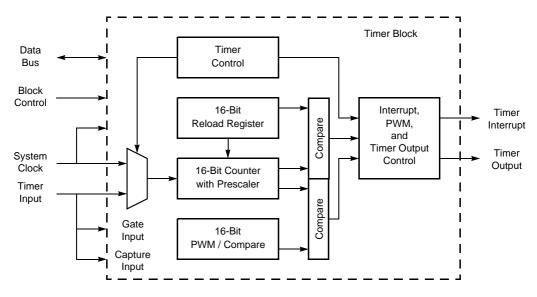

Figure 66. Timer Block Diagram

## Operation

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer rolls over to 0000H and continues counting.

## **Timer Operating Modes**

The timers can be configured to operate in the following modes:

#### **One-Shot Mode**

In One-Shot mode, the timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the Reload value, the timer generates an interrupt and the count value in the Timer High and Low Byte registers is reset to 0001H. Then, the timer is automatically disabled and stops counting.

Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state for one system clock cycle (from Low to High or from High to Low) upon timer Reload. If it is desired to have the Timer Output make a permanent state change upon One-Shot time-

written during counting, the 8-bit written value is placed in the counter (High or Low Byte) at the next clock edge. The counter continues counting from the new value.

BITS 7 6 5 4 3 2 1 0 TH FIELD 0 0 0 0 0 0 0 0 RESET R/W R/W R/W R/W R/W R/W R/W R/W R/W F00H, F08H, F10H, F18H ADDR

Table 38. Timer 0-3 High Byte Register (TxH)

Table 39>. Timer 0-3 Low Byte Register (TxL)

| BITS  | 7   | 6                      | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------|-----|------------------------|-----|-----|-----|-----|-----|-----|--|

| FIELD |     | TL                     |     |     |     |     |     |     |  |

| RESET | 0   | 0                      | 0   | 0   | 0   | 0   | 0   | 1   |  |

| R/W   | R/W | R/W                    | R/W | R/W | R/W | R/W | R/W | R/W |  |

| ADDR  |     | F01H, F09H, F11H, F19H |     |     |     |     |     |     |  |

TH and TL—Timer High and Low Bytes

These 2 bytes, {TMRH[7:0], TMRL[7:0]}, contain the current 16-bit timer count value.

## **Timer Reload High and Low Byte Registers**

The Timer 0-3 Reload High and Low Byte (TxRH and TxRL) registers (Tables 40 and 41) store a 16-bit reload value, {TRH[7:0], TRL[7:0]}. Values written to the Timer Reload High Byte register are stored in a temporary holding register. When a write to the Timer Reload Low Byte register occurs, the temporary holding register value is written to the Timer High Byte register. This operation allows simultaneous updates of the 16-bit Timer Reload value.

In Compare mode, the Timer Reload High and Low Byte registers store the 16-bit Compare value.

In single-byte DMA transactions to the Timer Reload High Byte register, the temporary holding register is bypassed and the value is written directly to the register. If the DMA is

- 5. Check the TDRE bit in the UART Status 0 register to determine if the Transmit Data register is empty (indicated by a 1). If empty, continue to Step 6. If the Transmit Data register is full (indicated by a 0), continue to monitor the TDRE bit until the Transmit Data register becomes available to receive new data.

- 6. Write the data byte to the UART Transmit Data register. The transmitter automatically transfers the data to the Transmit Shift register and transmit the data.

- 7. To transmit additional bits, return to Step 5.

#### Transmitting Data using the Interrupt-Driven Method

The UART Transmitter interrupt indicates the availability of the Transmit Data register to accept new data for transmission. Follow these steps to configure the UART for interrupt-driven data transmission:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the desired baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Transmitter interrupt and set the desired priority.

- 5. Write to the UART Control 1 register to enable Multiprocessor (9-bit) mode functions, if desired.

- 6. Write to the UART Control 0 register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission

- Enable parity, if desired, and select either even or odd parity.

- Set or clear the CTSE bit to enable or disable control from the receiver via the  $\overline{\text{CTS}}$  pin.

- 7. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data transmission. When the UART Transmit interrupt is detected, the associated interrupt service routine (ISR) should perform the following:

- 8. Write the data byte to the UART Transmit Data register. The transmitter will automatically transfer the data to the Transmit Shift register and transmit the data.

- 9. Clear the UART Transmit interrupt bit in the applicable Interrupt Request register.

- 10. Execute the IRET instruction to return from the interrupt-service routine and wait for the Transmit Data register to again become empty.

#### Table 58. UART Baud Rates

#### 20.0 MHz System Clock

| •            |             |             |       |

|--------------|-------------|-------------|-------|

| Desired Rate | BRG Divisor | Actual Rate | Error |

| (kHz)        | (Decimal)   | (kHz)       | (%)   |

| 1250.0       | 1           | 1250.0      | 0.00  |

| 625.0        | 2           | 625.0       | 0.00  |

| 250.0        | 5           | 250.0       | 0.00  |

| 115.2        | 11          | 113.6       | -1.36 |

| 57.6         | 22          | 56.8        | -1.36 |

| 38.4         | 33          | 37.9        | -1.36 |

| 19.2         | 65          | 19.2        | 0.16  |

| 9.60         | 130         | 9.62        | 0.16  |

| 4.80         | 260         | 4.81        | 0.16  |

| 2.40         | 521         | 2.40        | -0.03 |

| 1.20         | 1042        | 1.20        | -0.03 |

| 0.60         | 2083        | 0.60        | 0.02  |

| 0.30         | 4167        | 0.30        | -0.01 |

|              |             |             |       |

| Desired Rate | BRG Divisor | Actual Rate | Error  |

|--------------|-------------|-------------|--------|

| (kHz)        | (Decimal)   | (kHz)       | (%)    |

| 1250.0       | 1           | 1152.0      | -7.84% |

| 625.0        | 2           | 576.0       | -7.84% |

| 250.0        | 5           | 230.4       | -7.84% |

| 115.2        | 10          | 115.2       | 0.00   |

| 57.6         | 20          | 57.6        | 0.00   |

| 38.4         | 30          | 38.4        | 0.00   |

| 19.2         | 60          | 19.2        | 0.00   |

| 9.60         | 120         | 9.60        | 0.00   |

| 4.80         | 240         | 4.80        | 0.00   |

| 2.40         | 480         | 2.40        | 0.00   |

| 1.20         | 960         | 1.20        | 0.00   |

| 0.60         | 1920        | 0.60        | 0.00   |

| 0.30         | 3840        | 0.30        | 0.00   |

#### 16.667 MHz System Clock

| Desired Rate | BRG Divisor | Actual Rate | Error  | Desired Rate | BRG Divisor | Actual Rate | Error |

|--------------|-------------|-------------|--------|--------------|-------------|-------------|-------|

| (kHz)        | (Decimal)   | (kHz)       | (%)    | (kHz)        | (Decimal)   | (kHz)       | (%)   |

| 1250.0       | 1           | 1041.69     | -16.67 | 1250.0       | N/A         | N/A         | N/A   |

| 625.0        | 2           | 520.8       | -16.67 | 625.0        | 1           | 691.2       | 10.59 |

| 250.0        | 4           | 260.4       | 4.17   | 250.0        | 3           | 230.4       | -7.84 |

| 115.2        | 9           | 115.7       | 0.47   | 115.2        | 6           | 115.2       | 0.00  |

| 57.6         | 18          | 57.87       | 0.47   | 57.6         | 12          | 57.6        | 0.00  |

| 38.4         | 27          | 38.6        | 0.47   | 38.4         | 18          | 38.4        | 0.00  |

| 19.2         | 54          | 19.3        | 0.47   | 19.2         | 36          | 19.2        | 0.00  |

| 9.60         | 109         | 9.56        | -0.45  | 9.60         | 72          | 9.60        | 0.00  |

| 4.80         | 217         | 4.80        | -0.83  | 4.80         | 144         | 4.80        | 0.00  |

| 2.40         | 434         | 2.40        | 0.01   | 2.40         | 288         | 2.40        | 0.00  |

| 1.20         | 868         | 1.20        | 0.01   | 1.20         | 576         | 1.20        | 0.00  |

| 0.60         | 1736        | 0.60        | 0.01   | 0.60         | 1152        | 0.60        | 0.00  |

| 0.30         | 3472        | 0.30        | 0.01   | 0.30         | 2304        | 0.30        | 0.00  |

11.0592 MHz System Clock

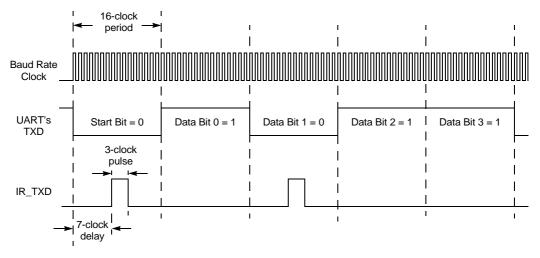

Figure 72. Infrared Data Transmission

#### **Receiving IrDA Data**

Data received from the infrared transceiver via the IR\_RXD signal through the RXD pin is decoded by the Infrared Endec and passed to the UART. The UART's baud rate clock is used by the Infrared Endec to generate the demodulated signal (RXD) that drives the UART. Each UART/Infrared data bit is 16-clocks wide. Figure 73 illustrates data reception. When the Infrared Endec is enabled, the UART's RXD signal is internal to the Z8F640x family device while the IR\_RXD signal is received through the RXD pin.

## **Error Detection**

The SPI contains error detection logic to support SPI communication protocols and recognize when communication errors have occurred. The SPI Status register indicates when a data transmission error has been detected.

#### **Overrun (Write Collision)**

An overrun error (write collision) indicates a write to the SPI Data register was attempted while a data transfer is in progress. An overrun sets the OVR bit in the SPI Status register to 1. Writing a 1 to OVR clears this error flag.

#### Mode Fault (Multi-Master Collision)

A mode fault indicates when more than one Master is trying to communicate at the same time (a multi-master collision). The mode fault is detected when the enabled Master's  $\overline{SS}$  pin is asserted. A mode fault sets the COL bit in the SPI Status register to 1. Writing a 1 to COL clears this error flag.

## **SPI Interrupts**

When SPI interrupts are enabled, the SPI generates an interrupt after data transmission. The SPI in Master mode generates an interrupt after a character has been sent. A character can be defined to be 1 through 8 bits by the NUMBITS field in the SPI Mode register. The SPI in Slave mode generates an interrupt when the  $\overline{SS}$  signal deasserts to indicate completion of the data transfer. Writing a 1 to the IRQ bit in the SPI Status Register clears the pending interrupt request. If the SPI is disabled, an SPI interrupt can be generated by a Baud Rate Generator time-out.

## **SPI Baud Rate Generator**

In SPI Master mode, the Baud Rate Generator creates a lower frequency serial clock (SCK) for data transmission synchronization between the Master and the external Slave. The input to the Baud Rate Generator is the system clock. The SPI Baud Rate High and Low Byte registers combine to form a 16-bit reload value, BRG[15:0], for the SPI Baud Rate Generator. The reload value must be greater than or equal to 0002H for SPI operation (maximum baud rate is system clock frequency divided by 4). The SPI baud rate is calculated using the following equation:

# SPI Baud Rate (bits/s) = $\frac{\text{System Clock Frequency (Hz)}}{2 \times \text{BRG}[15:0]}$

When the SPI is disabled, the Baud Rate Generator can function as a basic 16-bit timer with interrupt on time-out. To configure the Baud Rate Generator as a timer with interrupt on time-out, complete the following procedure:

## SPI Baud Rate High and Low Byte Registers

The SPI Baud Rate High and Low Byte registers combine to form a 16-bit reload value, BRG[15:0], for the SPI Baud Rate Generator. The reload value must be greater than or equal to 0002H for proper SPI operation (maximum baud rate is system clock frequency divided by 4). The SPI baud rate is calculated using the following equation:

SPI Baud Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{2 \times \text{BRG}[15:0]}$

| BITS  | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| FIELD |     |     |     | BF  | RH  |     |     |     |

| RESET | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  |     |     |     | F6  | 6H  |     |     |     |

Table 64. SPI Baud Rate High Byte Register (SPIBRH)

#### BRH = SPI Baud Rate High Byte

Most significant byte, BRG[15:8], of the SPI Baud Rate Generator's reload value.

#### Table 65. SPI Baud Rate Low Byte Register (SPIBRL)

| BITS  | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| FIELD |     |     |     | BI  | RL  |     |     |     |

| RESET | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/w |

| ADDR  |     |     |     | F6  | 7H  |     |     |     |

BRL = SPI Baud Rate Low Byte

Least significant byte, BRG[7:0], of the SPI Baud Rate Generator's reload value.

#### START-Send Start Condition

This bit sends the Start condition. Once asserted, it is cleared by the I<sup>2</sup>C Controller after it sends the START condition or by deasserting the IEN bit. After this bit is set, the Start condition is sent if there is data in the I<sup>2</sup>C Data or I<sup>2</sup>C Shift register. If there is no data in one of these registers, the I<sup>2</sup>C Controller waits until data is loaded. If this bit is set while the I<sup>2</sup>C Controller is shifting out data, it generates a START condition after the byte shifts and the acknowledge phase completed. If the STOP bit is also set, it also waits until the STOP condition is sent before the START condition. If this bit is 1, it cannot be cleared to 0 by writing to the register. This bit clears when the I<sup>2</sup>C is disabled.

#### STOP-Send Stop Condition

This bit causes the  $I^2C$  Controller to issue a Stop condition after the byte in the  $I^2C$  Shift register has completed transmission or after a byte has been received in a receive operation. Once set, this bit is reset by the  $I^2C$  Controller after a Stop condition has been sent or by deasserting the IEN bit. If this bit is 1, it cannot be cleared to 0 by writing to the register. This bit clears when the  $I^2C$  is disabled.

#### BIRQ-Baud Rate Generator Interrupt Request

This bit causes an interrupt to occur every time the baud rate generator counts down to zero. This bit allows the  $I^2C$  Controller to be used as an additional counter when it is not being used elsewhere. This bit must only be set when the  $I^2C$  Controller is disabled.

#### TXI-Enable TDRE interrupts

This bit enables interrupts when the I<sup>2</sup>C Data register is empty on the I<sup>2</sup>C Controller.

#### NAK—Send NAK

This bit sends a Not Acknowledge condition after the next byte of data has been read from the  $I^2C$  slave. Once asserted, it is deasserted after a Not Acknowledge is sent or the IEN bit is deasserted.

#### FLUSH-Flush Data

Setting this bit to 1 clears the I<sup>2</sup>C Data register and sets the TDRE bit to 1. This bit allows flushing of the I<sup>2</sup>C Data register when an NAK is received after the data has been sent to the I<sup>2</sup>C Data register. Reading this bit always returns 0.

## FILTEN—I<sup>2</sup>C Signal Filter Enable

Setting this bit to 1 enables low-pass digital filters on the SDA and SCL input signals. These filters reject any input pulse with periods less than a full system clock cycle. The filters introduce a 3-system clock cycle latency on the inputs.

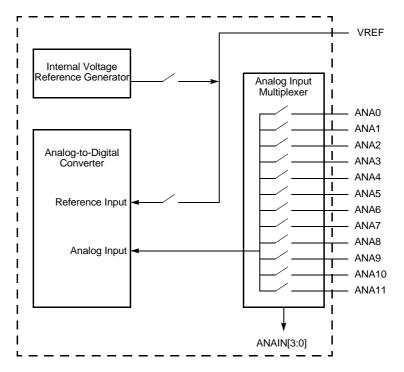

Figure 83. Analog-to-Digital Converter Block Diagram

## Operation

## **Automatic Power-Down**

If the ADC is idle (no conversions in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered-down. From this power-down state, the ADC requires 40 system clock cycles to power-up. The ADC powers up when a conversion is requested using the ADC Control register.

## **Single-Shot Conversion**

When configured for single-shot conversion, the ADC performs a single analog-to-digital conversion on the selected analog input channel. After completion of the conversion, the ADC shuts down. The steps for setting up the ADC and initiating a single-shot conversion are as follows:

- Power-on reset

- Voltage Brownout reset

- Asserting the  $\overline{\text{RESET}}$  pin Low to initiate a Reset.

- Driving the DBG pin Low while the Z8F640x family device is in Stop mode initiates a System Reset.

## **OCD Data Format**

The OCD interface uses the asynchronous data format defined for RS-232. Each character is transmitted as 1 Start bit, 8 data bits (least-significant bit first), and 1.5 Stop bits (Figure 89)

| START         D0         D1         D2         D3         D4         D5         D6         D7 | STOP |

|-----------------------------------------------------------------------------------------------|------|

|-----------------------------------------------------------------------------------------------|------|

#### Figure 89. OCD Data Format

## **OCD Auto-Baud Detector/Generator**

To run over a range of baud rates (data bits per second) with various system clock frequencies, the On-Chip Debugger has an Auto-Baud Detector/Generator. After a reset, the OCD is idle until it receives data. The OCD requires that the first character sent from the host is the character 80H. The character 80H has eight continuous bits Low (one Start bit plus 7 data bits). The Auto-Baud Detector measures this period and sets the OCD Baud Rate Generator accordingly.

The Auto-Baud Detector/Generator is clocked by the Z8F640x family device system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation, the maximum recommended baud rate is the system clock frequency divided by 8. The theoretical maximum baud rate is the system clock frequency divided by 4. This theoretical maximum is possible for low noise designs with clean signals. Table 92 lists minimum and recommended maximum baud rates for sample crystal frequencies.

| System Clock Frequency<br>(MHz) | Recommended Maximum Baud Rate<br>(kbits/s) | Minimum Baud Rate<br>(kbits/s) |  |

|---------------------------------|--------------------------------------------|--------------------------------|--|

| 20.0                            | 2500                                       | 39.1                           |  |

| 1.0                             | 125.0                                      | 1.96                           |  |

| 0.032768 (32KHz)                | 4.096                                      | 0.064                          |  |

#### Table 92. OCD Baud-Rate Limits

```

DBG <-- 03H

DBG --> RuntimeCounter[15:8]

DBG --> RuntimeCounter[7:0]

```

• Write OCD Control Register (04H)—The Write OCD Control Register command writes the data that follows to the OCDCTL register. When the Read Protect Option Bit is enabled, the DBGMODE bit (OCDCTL[7]) can only be set to 1, it cannot be cleared to 0 and the only method of putting the Z8F640x family device back into normal operating mode is to reset the device.

```

DBG <-- 04H

DBG <-- OCDCTL[7:0]

```

• **Read OCD Control Register (05H)**—The Read OCD Control Register command reads the value of the OCDCTL register.

```

DBG <-- 05H

DBG --> OCDCTL[7:0]

```

• Write Program Counter (06H)—The Write Program Counter command writes the data that follows to the eZ8 CPU's Program Counter (PC). If the Z8F640x family device is not in Debug mode or if the Read Protect Option Bit is enabled, the Program Counter (PC) values are discarded.

```

DBG <-- 06H

DBG <-- ProgramCounter[15:8]

DBG <-- ProgramCounter[7:0]

```

• **Read Program Counter (07H)**—The Read Program Counter command reads the value in the eZ8 CPU's Program Counter (PC). If the Z8F640x family device is not in Debug mode or if the Read Protect Option Bit is enabled, this command returns FFFFH.

```

DEG <-- 07H

DEG --> ProgramCounter[15:8]

DEG --> ProgramCounter[7:0]

```

• Write Register (08H)—The Write Register command writes data to the Register File. Data can be written 1-256 bytes at a time (256 bytes can be written by setting size to zero). If the Z8F640x family device is not in Debug mode, the address and data values are discarded. If the Read Protect Option Bit is enabled, then only writes to the Flash Control Registers are allowed and all other register write data values are discarded.

```

DBG <-- 08H

DBG <-- {4'h0,Register Address[11:8]}

DBG <-- Register Address[7:0]

DBG <-- Size[7:0]

DBG <-- 1-256 data bytes

```

• **Read Register (09H)**—The Read Register command reads data from the Register File. Data can be read 1-256 bytes at a time (256 bytes can be read by setting size to

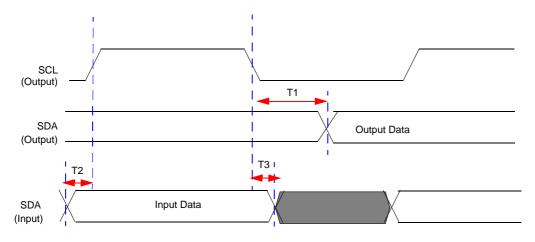

## I<sup>2</sup>C Timing

## Figure 98. I<sup>2</sup>C Timing

| Table | 112. | I <sup>2</sup> C | Timing |

|-------|------|------------------|--------|

|-------|------|------------------|--------|

|                |                                         | Delay (ns)      |  |

|----------------|-----------------------------------------|-----------------|--|

| Parameter      | Abbreviation                            | Minimum Maximum |  |

| T <sub>1</sub> | SCL Fall to SDA output delay            | SCL period/4    |  |

| T <sub>2</sub> | SDA Input to SCL rising edge Setup Time | 0               |  |

| T <sub>3</sub> | SDA Input to SCL falling edge Hold Time | 0               |  |

## Z8F640x/Z8F480x/Z8F320x/Z8F240x/Z8F160x Z8 Encore!®

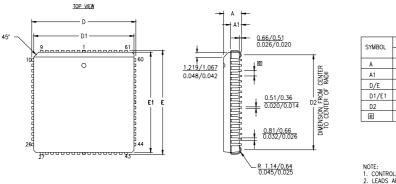

INCH

MIN

MAX

Figure 107 illustrates the 68-pin PLCC (plastic lead chip carrier) package available for the Z8F1602, Z8F2402, Z8F3202, Z8F4802, and Z8F6402 devices.

| A     | 4.32  | 4.57  | .170 | .180  |

|-------|-------|-------|------|-------|

| A1    | 2.43  | 2.92  | .095 | .115  |

| D/E   | 25.02 | 25.40 | .985 | 1.000 |

| D1/E1 | 24.13 | 24.33 | .950 | .958  |

| D2    | 22.86 | 23.62 | .900 | .930  |

| e     | 1.27  | BSC   | .050 | BSC   |

|       |       |       |      |       |

|       |       |       |      |       |

MAX

MILLIMETER

MIN

NOTE: 1. CONTROLLING DIVENSIONS : INCH. 2. LEADS ARE COPLANAR WITHIN 0.004 IN. RANGE. 3. DIVENSION : MM INCH.

Figure 107. 68-Lead Plastic Lead Chip Carrier Package (PLCC)

## **Precharacterization Product**

The product represented by this document is newly introduced and ZiLOG has not completed the full characterization of the product. The document states what ZiLOG knows about this product at this time, but additional features or nonconformance with some aspects of the document might be found, either by ZiLOG or its customers in the course of further application and characterization work. In addition, ZiLOG cautions that delivery might be uncertain at times, due to start-up yield issues.

ZiLOG, Inc. 532 Race Street San Jose, CA 95126 Telephone (408) 558-8500 FAX 408 558-8300 Internet: www.zilog.com

## Document Information

## **Document Number Description**

The Document Control Number that appears in the footer on each page of this document contains unique identifying attributes, as indicated in the following table:

| PS   | Product Specification    |  |

|------|--------------------------|--|

| 0176 | Unique Document Number   |  |

| 01   | Revision Number          |  |

| 0702 | Month and Year Published |  |

register 109, 126, 184 ADC control (ADCCTL) 135 ADC data high byte (ADCDH) 137 ADC data low bits (ADCDL) 137 baud low and high byte (I2C) 121 baud rate high and low byte (SPI) 110 control (SPI) 107 control, I2C 119 data, SPI 106 DMA status (DMAA\_STAT) 131 DMA\_ADC address 128 DMA\_ADC control DMAACTL) 130 DMAx address high nibble (DMAxH) 126 DMAx control (DMAxCTL) 124 DMAx end/address low byte (DMAxEND) 128 DMAx start/current address low byte register (DMAxSTART) 128 flash control (FCTL) 144 flash high and low byte (FFREQH and FREEQL) 147 flash page select (FPS) 146 flash status (FSTAT) 145 GPIO port A-H address (PxADDR) 37 GPIO port A-H alternate function sub-registers 39 GPIO port A-H control address (PxCTL) 38 GPIO port A-H data direction sub-registers 39 I2C baud rate high (I2CBRH) 121 I2C control (I2CCTL) 119 I2C data (I2CDATA) 118 I2C status 118 I2C status (I2CSTAT) 118 I2Cbaud rate low (I2CBRL) 121 mode, SPI 109 OCD control 161 OCD status 162 OCD watchpoint address 164 OCD watchpoint control 163 OCD watchpoint data 164 SPI baud rate high byte (SPIBRH) 110 SPI baud rate low byte (SPIBRL) 110 SPI control (SPICTL) 107 SPI data (SPIDATA) 106 SPI status (SPISTAT) 108

status, I2C 118 status, SPI 108 UARTx baud rate high byte (UxBRH) 91 UARTx baud rate low byte (UxBRL) 92 UARTx Control 0 (UxCTL0) 89 UARTx control 1 (UxCTL1) 90 UARTx receive data (UxRXD) 87 UARTx status 0 (UxSTAT0) 87 UARTx status 1 (UxSTAT1) 89 UARTx transmit data (UxTXD) 86 watch-dog timer control (WDTCTL) 75 watch-dog timer reload high byte (WDTH) 76 watch-dog timer reload low byte (WDTL) 77 watch-dog timer reload upper byte (WDTU) 76 register file 17 register file address map 20 register pair 184 register pointer 185 reset and stop mode characteristics 25 and stop mode recovery 25 carry flag 188 controller 5 sources 26 **RET 190** return 190 return information 216 RL 191 **RLC 191** rotate and shift instructions 191 rotate left 191 rotate left through carry 191 rotate right 191 rotate right through carry 191 RP 185 RR 184, 191 rr 184 **RRC 191**

## S

SBC 188 SCF 188, 189 SCK 101