Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 31                                                        |

| Program Memory Size        | 48KB (48K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 4K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 40-DIP (0.620", 15.75mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f4801pm020ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

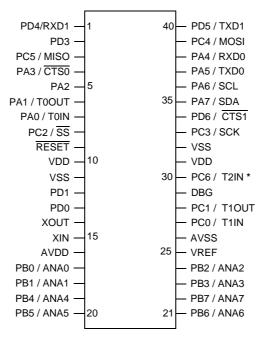

# **Pin Configurations**

Figures 56 through 61 illustrate the pin configurations for all of the packages available in the Z8 Encore!® MCU family. Refer to Table 2 for a description of the signals.

Note: Timer 3 is not supported.

Figure 56. Z8Fxx01 in 40-Pin Dual Inline Package (DIP)

\* T2OUT is not supported.

| Port   | Pin     | Mnemonic     | Alternate Function Description                         |

|--------|---------|--------------|--------------------------------------------------------|

| Port D | PD0     | T3IN         | Timer 3 In (not available in 40- and 44-pin packages)  |

|        | PD1     | T3OUT        | Timer 3 Out (not available in 40- and 44-pin packages) |

|        | PD2     | N/A          | No alternate function                                  |

|        | PD3     | N/A          | No alternate function                                  |

|        | PD4     | RXD1 / IRRX1 | UART 1 / IrDA 1 Receive Data                           |

|        | PD5     | TXD1 / IRTX1 | UART 1 / IrDA 1 Transmit Data                          |

|        | PD6     | CTS1         | UART 1 Clear to Send                                   |

|        | PD7     | RCOUT        | Watch-Dog Timer RC Oscillator Output                   |

| Port E | PE[7:0] | N/A          | No alternate functions                                 |

| Port F | PF[7:0] | N/A          | No alternate functions                                 |

| Port G | PG[7:0] | N/A          | No alternate functions                                 |

| Port H | PH0     | ANA8         | ADC Analog Input 8                                     |

|        | PH1     | ANA9         | ADC Analog Input 9                                     |

|        | PH2     | ANA10        | ADC Analog Input 10                                    |

|        | PH3     | ANA11        | ADC Analog Input 11                                    |

Table 11. Port Alternate Function Mapping (Continued)

## **GPIO Interrupts**

Many of the GPIO port pins can be used as interrupt sources. Some port pins may be configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupts generate an interrupt when any edge occurs (both rising and falling). Refer to the **Interrupt Controller** chapter for more information on interrupts using the GPIO pins.

# **GPIO Control Register Definitions**

Four registers for each Port provide access to GPIO control, input data, and output data. Table 12 lists these Port registers. Use the Port A-H Address and Control registers together to provide access to sub-registers for Port configuration and control.

| BITS  | 7     | 6     | 5     | 4             | 3      | 2      | 1      | 0      |

|-------|-------|-------|-------|---------------|--------|--------|--------|--------|

| FIELD | T2ENL | T1ENL | T0ENL | <b>U0RENL</b> | U0TENL | I2CENL | SPIENL | ADCENL |

| RESET | 0     | 0     | 0     | 0             | 0      | 0      | 0      | 0      |

| R/W   | R/W   | R/W   | R/W   | R/W           | R/W    | R/W    | R/W    | R/W    |

| ADDR  |       |       |       | FC            | 2H     |        |        |        |

#### Table 28. IRQ0 Enable Low Bit Register (IRQ0ENL)

T2ENL—Timer 2 Interrupt Request Enable Low Bit T1ENL—Timer 1 Interrupt Request Enable Low Bit T0ENL—Timer 0 Interrupt Request Enable Low Bit U0RENL—UART 0 Receive Interrupt Request Enable Low Bit U0TENL—UART 0 Transmit Interrupt Request Enable Low Bit I2CENL—I<sup>2</sup>C Interrupt Request Enable Low Bit SPIENL—SPI Interrupt Request Enable Low Bit ADCENL—ADC Interrupt Request Enable Low Bit

#### **IRQ1 Enable High and Low Bit Registers**

The IRQ1 Enable High and Low Bit registers (Tables 30 and 31) form a priority encoded enabling for interrupts in the Interrupt Request 1 register. Priority is generated by setting bits in each register. Table 29 describes the priority control for IRQ1.

| IRQ1ENH[x] | IRQ1ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

| 1          | 1          | Level 3  | High        |

Table 29. IRQ1 Enable and Priority Encoding

where *x* indicates the register bits from 0 through 7.

set to 2-byte transfers, the temporary holding register for the Timer Reload High Byte is not bypassed.

BITS 7 6 5 4 3 2 1 0 TRH FIELD 1 1 1 1 1 1 1 1 RESET R/W R/W R/W R/W R/W R/W R/W R/W R/W F02H, F0AH, F12H, F1AH ADDR

### Table 40. Timer 0-3 Reload High Byte Register (TxRH)

### Table 41. Timer 0-3 Reload Low Byte Register (TxRL)

| BITS  | 7   | 6                                                               | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-----|-----------------------------------------------------------------|---|---|---|---|---|---|--|

| FIELD |     | TRL                                                             |   |   |   |   |   |   |  |

| RESET | 1   | 1 1 1 1 1 1 1 1                                                 |   |   |   |   |   |   |  |

| R/W   | R/W | R/W         R/W         R/W         R/W         R/W         R/W |   |   |   |   |   |   |  |

| ADDR  |     | F03H, F0BH, F13H, F1BH                                          |   |   |   |   |   |   |  |

TRH and TRL-Timer Reload Register High and Low

These two bytes form the 16-bit Reload value, {TRH[7:0], TRL[7:0]}. This value is used to set the maximum count value which initiates a timer reload to 0001H. In Compare mode, these two byte form the 16-bit Compare value.

## Timer 0-3 PWM High and Low Byte Registers

The Timer 0-3 PWM High and Low Byte (TxPWMH and TxPWML) registers (Tables 42 and 43) are used for Pulse-Width Modulator (PWM) operations. These registers also store the Capture values for the Capture and Capture/Compare modes.

| BITS  | 7   | 6                                                               | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-----|-----------------------------------------------------------------|---|---|---|---|---|---|--|

| FIELD |     | PWMH                                                            |   |   |   |   |   |   |  |

| RESET | 0   | 0 0 0 0 0 0 0 0                                                 |   |   |   |   |   |   |  |

| R/W   | R/W | R/W         R/W         R/W         R/W         R/W         R/W |   |   |   |   |   |   |  |

| ADDR  |     | F04H, F0CH, F14H, F1CH                                          |   |   |   |   |   |   |  |

#### Table 42. Timer 0-3 PWM High Byte Register (TxPWMH)

#### Table 43. Timer 0-3 PWM Low Byte Register (TxPWML)

| BITS  | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-----|-----------------------------|---|---|---|---|---|---|--|

| FIELD |     | PWML                        |   |   |   |   |   |   |  |

| RESET | 0   | 0 0 0 0 0 0 0 0             |   |   |   |   |   |   |  |

| R/W   | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |

| ADDR  |     | F05H, F0DH, F15H, F1DH      |   |   |   |   |   |   |  |

PWMH and PWML—Pulse-Width Modulator High and Low Bytes

These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output value is set by the TPOL bit in the Timer Control Register (TxCTL) register.

The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operating in Capture or Capture/Compare modes.

# **UART**

# **Overview**

The Universal Asynchronous Receiver/Transmitter (UART) is a full-duplex communication channel capable of handling asynchronous data transfers. The Z8F640x family device contains two fully independent UARTs. The UART uses a single 8-bit data mode with selectable parity. Features of the UART include:

- 8-bit asynchronous data transfer

- Selectable even- and odd-parity generation and checking

- Option of one or two Stop bits

- Separate transmit and receive interrupts

- Framing, parity, overrun and break detection

- Separate transmit and receive enables

- Selectable 9-bit multiprocessor (9-bit) mode

- 16-bit Baud Rate Generator (BRG)

## Architecture

The UART consists of three primary functional blocks: transmitter, receiver, and baud rate generator. The UART's transmitter and receiver function independently, but employ the same baud rate and data format. Figure 67 illustrates the UART architecture.

| 10.0 MHz System | Clock       |             |        | 5.5296 MHz Syst | em Clock    |             |       |

|-----------------|-------------|-------------|--------|-----------------|-------------|-------------|-------|

| Desired Rate    | BRG Divisor | Actual Rate | Error  | Desired Rate    | BRG Divisor | Actual Rate | Error |

| (kHz)           | (Decimal)   | (kHz)       | (%)    | (kHz)           | (Decimal)   | (kHz)       | (%)   |

| 1250.0          | N/A         | N/A         | N/A    | 1250.0          | N/A         | N/A         | N/A   |

| 625.0           | 1           | 625.0       | 0.00   | 625.0           | N/A         | N/A         | N/A   |

| 250.0           | 3           | 208.33      | -16.67 | 250.0           | 1           | 345.6       | 38.24 |

| 115.2           | 5           | 125.0       | 8.51   | 115.2           | 3           | 115.2       | 0.00  |

| 57.6            | 11          | 56.8        | -1.36  | 57.6            | 6           | 57.6        | 0.00  |

| 38.4            | 16          | 39.1        | 1.73   | 38.4            | 9           | 38.4        | 0.00  |

| 19.2            | 33          | 18.9        | 0.16   | 19.2            | 18          | 19.2        | 0.00  |

| 9.60            | 65          | 9.62        | 0.16   | 9.60            | 36          | 9.60        | 0.00  |

| 4.80            | 130         | 4.81        | 0.16   | 4.80            | 72          | 4.80        | 0.00  |

| 2.40            | 260         | 2.40        | -0.03  | 2.40            | 144         | 2.40        | 0.00  |

| 1.20            | 521         | 1.20        | -0.03  | 1.20            | 288         | 1.20        | 0.00  |

| 0.60            | 1042        | 0.60        | -0.03  | 0.60            | 576         | 0.60        | 0.00  |

| 0.30            | 2083        | 0.30        | 0.02   | 0.30            | 1152        | 0.30        | 0.00  |

#### Table 58. UART Baud Rates (Continued)

#### 3.579545 MHz System Clock

| Desired Rate | BRG Divisor | Actual Rate | Error  | Desired Rate | BRG Divisor | Actual Rate | Error |  |  |

|--------------|-------------|-------------|--------|--------------|-------------|-------------|-------|--|--|

| (kHz)        | (Decimal)   | (kHz)       | (%)    | (kHz)        | (Decimal)   | (kHz)       | (%)   |  |  |

| 1250.0       | N/A         | N/A         | N/A    | 1250.0       | N/A         | N/A         | N/A   |  |  |

| 625.0        | N/A         | N/A         | N/A    | 625.0        | N/A         | N/A         | N/A   |  |  |

| 250.0        | 1           | 223.72      | -10.51 | 250.0        | N/A         | N/A         | N/A   |  |  |

| 115.2        | 2           | 111.9       | -2.90  | 115.2        | 1           | 115.2       | 0.00  |  |  |

| 57.6         | 4           | 55.9        | -2.90  | 57.6         | 2           | 57.6        | 0.00  |  |  |

| 38.4         | 6           | 37.3        | -2.90  | 38.4         | 3           | 38.4        | 0.00  |  |  |

| 19.2         | 12          | 18.6        | -2.90  | 19.2         | 6           | 19.2        | 0.00  |  |  |

| 9.60         | 23          | 9.73        | 1.32   | 9.60         | 12          | 9.60        | 0.00  |  |  |

| 4.80         | 47          | 4.76        | -0.83  | 4.80         | 24          | 4.80        | 0.00  |  |  |

| 2.40         | 93          | 2.41        | 0.23   | 2.40         | 48          | 2.40        | 0.00  |  |  |

| 1.20         | 186         | 1.20        | 0.23   | 1.20         | 96          | 1.20        | 0.00  |  |  |

| 0.60         | 373         | 0.60        | -0.04  | 0.60         | 192         | 0.60        | 0.00  |  |  |

| 0.30         | 746         | 0.30        | -0.04  | 0.30         | 384         | 0.30        | 0.00  |  |  |

|              |             |             |        | -            |             |             |       |  |  |

1.8432 MHz System Clock

ZILOG

# Analog-to-Digital Converter

# Overview

The Analog-to-Digital Converter (ADC) converts an analog input signal to a 10-bit binary number. The features of the sigma-delta ADC include:

- 12 analog input sources are multiplexed with general-purpose I/O ports

- Interrupt upon conversion complete

- Internal voltage reference generator

- Direct Memory Access (DMA) controller can automatically initiate data conversion and transfer of the data from 1 to 12 of the analog inputs.

# Architecture

Figure 83 illustrates the three major functional blocks (converter, analog multiplexer, and voltage reference generator) of the ADC. The ADC converts an analog input signal to its digital representation. The 12-input analog multiplexer selects one of the 12 analog input sources. The ADC requires an input reference voltage for the conversion. The voltage reference for the conversion may be input through the external VREF pin or generated internally by the voltage reference generator.

## ADC Data High Byte Register

The ADC Data High Byte register contains the upper eight bits of the 10-bit ADC output. During a conversion, this value is invalid. Access to the ADC Data High Byte register is read-only. The full 10-bit ADC result is given by {ADCD\_H[7:0], ADCD\_L[7:6]}.

| BITS  | 7 | 6      | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|---|--------|---|----|----|---|---|---|--|--|

| FIELD |   | ADCD_H |   |    |    |   |   |   |  |  |

| RESET |   | Х      |   |    |    |   |   |   |  |  |

| R/W   |   | R      |   |    |    |   |   |   |  |  |

| ADDR  |   |        |   | F7 | 2H |   |   |   |  |  |

#### Table 81. ADC Data High Byte Register (ADCD\_H)

ADCD\_H—ADC Data High Byte

This byte contains the upper eight bits of the 10-bit ADC output. These bits are not valid during a conversion. These bits are undefined after a Reset.

#### ADC Data Low Bits Register

The ADC Data Low Bits register contains the lower two bits of the conversion value. During a conversion this value is invalid. Access to the ADC Data Low Bits register is readonly. The full 10-bit ADC result is given by {ADCD\_H[7:0], ADCD\_L[7:6]}.

| BITS  | 7   | 6    | 5        | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|-----|------|----------|----|----|---|---|---|--|--|

| FIELD | ADC | CD_L | Reserved |    |    |   |   |   |  |  |

| RESET | 2   | X    | X        |    |    |   |   |   |  |  |

| R/W   | I   | ર    |          | R  |    |   |   |   |  |  |

| ADDR  |     |      |          | F7 | 3Н |   |   |   |  |  |

Table 82. ADC Data Low Bits Register (ADCD\_L)

#### ADCD\_L—ADC Data Low Bits

These are the least significant two bits of the 10-bit ADC output. During a conversion, this value is invalid. These bits are undefined after a Reset.

#### Reserved

These bits are reserved and are always undefined.

# Caution:

The byte at each address of the Flash memory cannot be programmed (any bits written to 0) more than twice before an erase cycle occurs.

## Page Erase

The Flash memory can be erased one page (512 bytes) at a time. Page Erasing the Flash memory sets all bytes in that page to the value FFH. The Flash Page Select register identifies the page to be erased. With the Flash Controller unlocked, writing the value 95H to the Flash Control register initiates the Page Erase operation. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the Page Erase operation completes. If the Page Erase operation is performed through the On-Chip Debugger, poll the Flash Status register to determine when the Page Erase operation is complete. When the Page Erase is complete, the Flash Controller returns to its locked state.

#### **Mass Erase**

The Flash memory can also be Mass Erased using the Flash Controller. Mass Erasing the Flash memory sets all bytes to the value FFH. With the Flash Controller unlocked, writing the value 63H to the Flash Control register initiates the Mass Erase operation. While the Flash Controller executes the Mass Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. Typically, the Flash Memory is Mass Erased using the On-Chip Debugger. Via the On-Chip Debugger, poll the Flash Status register to determine when the Mass Erase operation is complete. Although the Flash can be Mass Erased by user program code, when the Mass Erase is complete the user program code is completely erased. When the Mass Erase is complete, the Flash Controller returns to its locked state.

## **Flash Controller Bypass**

The Flash Controller can be bypassed and the control signals for the Flash memory brought out to the GPIO pins. Bypassing the Flash Controller allows faster Row Programming algorithms by controlling the Flash programming signals directly.

Row programing is recommended for gang programming applications and large volume customers who do not require in-circuit initial programming of the Flash memory. Mass Erase and Page Erase operations are also supported when the Flash Controller is bypassed.

Please refer to the document entitled *Third-Party Flash Programming Support for Z8 Encore*!<sup>TM</sup> for more information on bypassing the Flash Controller. This document is available for download at <u>www.zilog.com</u>.

## **Flash Status Register**

The Flash Status register indicates the current state of the Flash Controller. This register can be read at any time. The Read-only Flash Status Register shares its Register File address with the Write-only Flash Control Register.

| BITS  | 7    | 6     | 5 | 4           | 3  | 2 | 1 | 0 |  |  |  |

|-------|------|-------|---|-------------|----|---|---|---|--|--|--|

| FIELD | Rese | erved |   | FSTAT       |    |   |   |   |  |  |  |

| RESET | 0    | 0     | 0 | 0           | 0  | 0 | 0 | 0 |  |  |  |

| R/W   | R    | R     | R | R R R R R R |    |   |   |   |  |  |  |

| ADDR  |      |       |   | FF          | 8H |   |   |   |  |  |  |

Reserved

These bits are reserved and must be 0.

FSTAT—Flash Controller Status

000000 = Flash Controller locked.

000001 = First unlock command received.

000010 = Flash Controller unlocked (second unlock command received).

001xxx = Program operation in progress.

010xxx = Page erase operation in progress.

100xxx = Mass erase operation in progress.

- Power-on reset

- Voltage Brownout reset

- Asserting the  $\overline{\text{RESET}}$  pin Low to initiate a Reset.

- Driving the DBG pin Low while the Z8F640x family device is in Stop mode initiates a System Reset.

## **OCD Data Format**

The OCD interface uses the asynchronous data format defined for RS-232. Each character is transmitted as 1 Start bit, 8 data bits (least-significant bit first), and 1.5 Stop bits (Figure 89)

| START         D0         D1         D2         D3         D4         D5         D6         D7 | STOP |

|-----------------------------------------------------------------------------------------------|------|

|-----------------------------------------------------------------------------------------------|------|

#### Figure 89. OCD Data Format

#### **OCD Auto-Baud Detector/Generator**

To run over a range of baud rates (data bits per second) with various system clock frequencies, the On-Chip Debugger has an Auto-Baud Detector/Generator. After a reset, the OCD is idle until it receives data. The OCD requires that the first character sent from the host is the character 80H. The character 80H has eight continuous bits Low (one Start bit plus 7 data bits). The Auto-Baud Detector measures this period and sets the OCD Baud Rate Generator accordingly.

The Auto-Baud Detector/Generator is clocked by the Z8F640x family device system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation, the maximum recommended baud rate is the system clock frequency divided by 8. The theoretical maximum baud rate is the system clock frequency divided by 4. This theoretical maximum is possible for low noise designs with clean signals. Table 92 lists minimum and recommended maximum baud rates for sample crystal frequencies.

| System Clock Frequency<br>(MHz) | Recommended Maximum Baud Rate<br>(kbits/s) | Minimum Baud Rate<br>(kbits/s) |

|---------------------------------|--------------------------------------------|--------------------------------|

| 20.0                            | 2500                                       | 39.1                           |

| 1.0                             | 125.0                                      | 1.96                           |

| 0.032768 (32KHz)                | 4.096                                      | 0.064                          |

#### Table 92. OCD Baud-Rate Limits

# **OCD Watchpoint Address Register**

The OCD Watchpoint Address register specifies the lower 8 bits of the Register File address bus to match when generating Watchpoint Debug Breaks. The full 12-bit Register File address is given by {WPTCTL3:0], WPTADDR[7:0]}.

Table 97. OCD Watchpoint Address (WPTADDR)

| BITS  | 7   | 6            | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------|-----|--------------|-----|-----|-----|-----|-----|-----|--|

| FIELD |     | WPTADDR[7:0] |     |     |     |     |     |     |  |

| RESET | 0   | 0            | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W   | R/W | R/W          | R/W | R/W | R/W | R/W | R/W | R/W |  |

WPTADDR[7:0]—Watchpoint Register File Address

These bits specify the lower eight bits of the register address to match when generating a Watchpoint Debug Break.

## **OCD Watchpoint Data Register**

The OCD Watchpoint Data register specifies the data to match if Watchpoint data match is enabled.

Table 98. OCD Watchpoint Data (WPTDATA)

| BITS  | 7   | 6            | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------|-----|--------------|-----|-----|-----|-----|-----|-----|--|

| FIELD |     | WPTDATA[7:0] |     |     |     |     |     |     |  |

| RESET | 0   | 0            | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W   | R/W | R/W          | R/W | R/W | R/W | R/W | R/W | R/W |  |

WPTDATA[7:0]—Watchpoint Register File Data

These bits specify the Register File data to match when generating Watchpoint Debug Breaks with the WPDM bit (WPTCTL[5]) is set to 1.

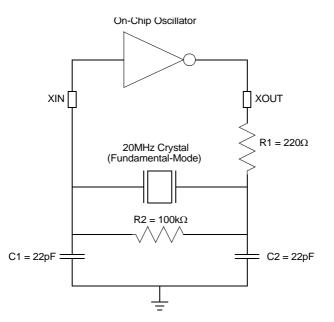

Figure 90. Recommended Crystal Oscillator Configuration (20MHz operation)

| Parameter                           | Value       | Units | Comments |

|-------------------------------------|-------------|-------|----------|

| Frequency                           | 20          | MHz   |          |

| Resonance                           | Parallel    |       |          |

| Mode                                | Fundamental |       |          |

| Series Resistance (R <sub>S</sub> ) | 25          | Ω     | Maximum  |

| Load Capacitance (CL)               | 20          | pF    | Maximum  |

| Shunt Capacitance (C <sub>0</sub> ) | 7           | pF    | Maximum  |

| Drive Level                         | 1           | mW    | Maximum  |

Table 99. Recommended Crystal Oscillator Specifications (20MHz Operation)

; value 01H, is the source. The value 01H is written into the

; Register at address 234H.

# Assembly Language Syntax

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. This binary format must be followed by users that prefer manual program coding or intend to implement their own assembler.

**Example 1**: If the contents of Registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

Table 113. Assembly Language Syntax Example 1

| Assembly Language Code | ADD | 43H, | 08H | (ADD dst, src) |

|------------------------|-----|------|-----|----------------|

| Object Code            | 04  | 08   | 43  | (OPC src, dst) |

**Example 2**: In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0 - 255 or, using Escaped Mode Addressing, a Working Register R0 - R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

Table 114. Assembly Language Syntax Example 2

| Assembly Language Code | ADD | 43H, | R8 | (ADD dst, src) |

|------------------------|-----|------|----|----------------|

| Object Code            | 04  | E8   | 43 | (OPC src, dst) |

See the device-specific Product Specification to determine the exact register file range available. The register file size varies, depending on the device type.

# eZ8 CPU Instruction Notation

In the eZ8 CPU Instruction Summary and Description sections, the operands, condition codes, status flags, and address modes are represented by a notational shorthand that is described in Table 115

| Mnemonic | Operands | Instruction             |

|----------|----------|-------------------------|

| CCF      | —        | Complement Carry Flag   |

| DI       | —        | Disable Interrupts      |

| EI       | _        | Enable Interrupts       |

| HALT     | _        | Halt Mode               |

| NOP      | _        | No Operation            |

| RCF      | —        | Reset Carry Flag        |

| SCF      | _        | Set Carry Flag          |

| SRP      | src      | Set Register Pointer    |

| STOP     | —        | Stop Mode               |

| WDT      | _        | Watch-Dog Timer Refresh |

#### **Table 121. CPU Control Instructions**

#### Table 122. Load Instructions

| Mnemonic | Operands    | Instruction                                                            |

|----------|-------------|------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                  |

| LD       | dst, src    | Load                                                                   |

| LDC      | dst, src    | Load Constant to/from Program Memory                                   |

| LDCI     | dst, src    | Load Constant to/from Program Memory and Auto-Increment<br>Addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                 |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-Increment<br>Addresses |

| LDX      | dst, src    | Load using Extended Addressing                                         |

| LEA      | dst, X(src) | Load Effective Address                                                 |

| POP      | dst         | Рор                                                                    |

| POPX     | dst         | Pop using Extended Addressing                                          |

| PUSH     | src         | Push                                                                   |

| PUSHX    | src         | Push using Extended Addressing                                         |

| Assembly        |                                                                                                                        | Addre       | ess Mode     | <b>Opcode</b> (s) |   |   | Fl | ags            |   |   | Fetch  | Instr. |

|-----------------|------------------------------------------------------------------------------------------------------------------------|-------------|--------------|-------------------|---|---|----|----------------|---|---|--------|--------|

| Mnemonic        | Symbolic Operation                                                                                                     | dst         | src          | (Hex)             | С | Z | S  | V              | D | Н | Cycles |        |

| TCM dst, src    | (NOT dst) AND src                                                                                                      | r           | r            | 62                | - | * | *  | 0              | - | - | 2      | 3      |

|                 |                                                                                                                        | r           | Ir           | 63                | - |   |    |                |   |   | 2      | 4      |

|                 |                                                                                                                        | R           | R            | 64                | - |   |    |                |   |   | 3      | 3      |

|                 |                                                                                                                        | R           | IR           | 65                | - |   |    |                |   |   | 3      | 4      |

|                 |                                                                                                                        | R           | IM           | 66                | - |   |    |                |   |   | 3      | 3      |

|                 |                                                                                                                        | IR          | IM           | 67                | - |   |    |                |   |   | 3      | 4      |

| TCMX dst, src   | (NOT dst) AND src                                                                                                      | ER          | ER           | 68                | - | * | *  | 0              | - | - | 4      | 3      |

|                 |                                                                                                                        | ER          | IM           | 69                | - |   |    |                |   |   | 4      | 3      |

| TM dst, src     | dst AND src                                                                                                            | r           | r            | 72                | - | * | *  | 0              | - | - | 2      | 3      |

|                 |                                                                                                                        | r           | Ir           | 73                | - |   |    |                |   |   | 2      | 4      |

|                 |                                                                                                                        | R           | R            | 74                | - |   |    |                |   |   | 3      | 3      |

|                 |                                                                                                                        | R           | IR           | 75                | - |   |    |                |   |   | 3      | 4      |

|                 |                                                                                                                        | R           | IM           | 76                | - |   |    |                |   |   | 3      | 3      |

|                 |                                                                                                                        | IR          | IM           | 77                | - |   |    |                |   |   | 3      | 4      |

| TMX dst, src    | dst AND src                                                                                                            | ER          | ER           | 78                | - | * | *  | 0              | - | - | 4      | 3      |

|                 |                                                                                                                        | ER          | IM           | 79                | - |   |    |                |   |   | 4      | 3      |

| TRAP Vector     | $SP \leftarrow SP - 2$<br>@SP \leftarrow PC<br>$SP \leftarrow SP - 1$<br>@SP \leftarrow FLAGS<br>PC \leftarrow @Vector |             | Vector       | F2                | - | - | -  | -              | - | - | 2      | 6      |

| WDT             |                                                                                                                        |             |              | 5F                | - | - | -  | -              | - | - | 1      | 2      |

| Flags Notation: | * = Value is a function of<br>- = Unaffected<br>X = Undefined                                                          | of the resu | ult of the o | operation.        |   |   |    | set to<br>to 1 | 0 |   |        |        |

### Table 126. eZ8 CPU Instruction Summary (Continued)

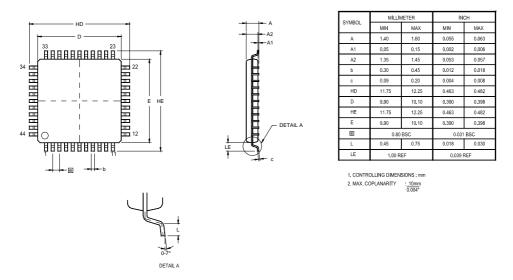

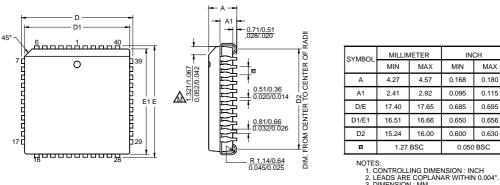

Figure 104 illustrates the 44-pin LQFP (low profile quad flat package) available for the Z8F1601, Z8F2401, Z8F3201, Z8F4801, and Z8F6401 devices.

Figure 104. 44-Lead Low-Profile Quad Flat Package (LQFP)

Figure 105 illustrates the 44-pin PLCC (plastic lead chip carrier) package available for the Z8F1601, Z8F2401, Z8F3201, Z8F4801, and Z8F6401 devices.

3. DIMENSION : MM

Figure 105. 44-Lead Plastic Lead Chip Carrier Package (PLCC)

MAX

0.180

0.115

0.695

0.656

0.630

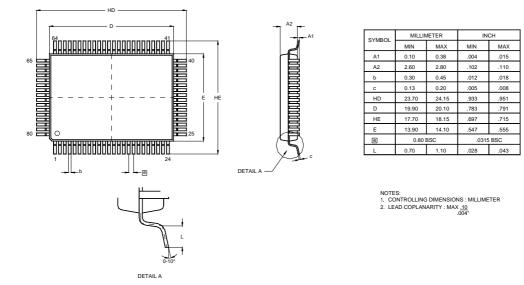

Figure 108 illustrates the 80-pin QFP (quad flat package) available for the Z8F4803 and Z8F6403 devices.

Figure 108. 80-Lead Quad-Flat Package (QFP)

# **Ordering Information**

| Part        | Flash<br>KB (Bytes) | RAM<br>KB (Bytes) | Max. Speed<br>(MHz) | Temp<br>( <sup>0</sup> C) | Voltage<br>(V) | Package | Part Number    |

|-------------|---------------------|-------------------|---------------------|---------------------------|----------------|---------|----------------|

| Z8 Encore!® | with 16KB           | Flash, Stand      | lard Tempera        | ture                      |                |         |                |

| Z8 Encore!® | 16 (16,384)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PDIP-40 | Z8F1601PM020SC |

| Z8 Encore!® | 16 (16,384)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-44 | Z8F1601AN020SC |

| Z8 Encore!® | 16 (16,384)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-44 | Z8F1601VN020SC |

| Z8 Encore!® | 16 (16,384)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-64 | Z8F1602AR020SC |

| Z8 Encore!® | 16 (16,384)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-68 | Z8F1602VS020SC |

| Z8 Encore!® | with 24KB           | Flash, Stand      | lard Tempera        | ture                      |                |         |                |

| Z8 Encore!® | 24 (24,576)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PDIP-40 | Z8F2401PM020SC |

| Z8 Encore!® | 24 (24,576)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-44 | Z8F2401AN020SC |

| Z8 Encore!® | 24 (24,576)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-44 | Z8F2401VN020SC |

| Z8 Encore!® | 24 (24,576)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-64 | Z8F2402AR020SC |

| Z8 Encore!® | 24 (24,576)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-68 | Z8F2402VS020SC |

| Z8 Encore!® | with 32KB           | Flash, Stand      | lard Tempera        | ture                      |                |         |                |

| Z8 Encore!® | 32 (32,768)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PDIP-40 | Z8F3201PM020SC |

| Z8 Encore!® | 32 (32,768)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-44 | Z8F3201AN020SC |

| Z8 Encore!® | 32 (32,768)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-44 | Z8F3201VN020SC |

| Z8 Encore!® | 32 (32,768)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-64 | Z8F3202AR020SC |

| Z8 Encore!® | 32 (32,768)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-68 | Z8F3202VS020SC |

| Z8 Encore!® | with 48KB           | Flash, Stand      | ard Temperat        | ure                       |                |         |                |

| Z8 Encore!® | 48 (49,152)         | 4 (4096)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PDIP-40 | Z8F4801PM020SC |

| Z8 Encore!® | 48 (49,152)         | 4 (4096)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-44 | Z8F4801AN020SC |

| Z8 Encore!® | 48 (49,152)         | 4 (4096)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-44 | Z8F4801VN020SC |

| Z8 Encore!® | 48 (49,152)         | 4 (4096)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-64 | Z8F4802AR020SC |

| Z8 Encore!® | 48 (49,152)         | 4 (4096)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-68 | Z8F4802VS020SC |

| Z8 Encore!® | 48 (49,152)         | 4 (4096)          | 20                  | 0 to +70                  | 3.0 - 3.6      | QFP-80  | Z8F4803FT020SC |

#### Table 128. Ordering Information