Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 31                                                        |

| Program Memory Size        | 48KB (48K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 4K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 44-LCC (J-Lead)                                           |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f4801vn020sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

This publication is subject to replacement by a later edition. To determine whether a later edition exists, or to request copies of publications, contact:

#### ZiLOG Worldwide Headquarters

532 Race Street San Jose, CA 95126 Telephone: 408.558.8500 Fax: 408.558.8300 www.ZiLOG.com

#### **Document Disclaimer**

ZiLOG is a registered trademark of ZiLOG Inc. in the United States and in other countries. All other products and/or service names mentioned herein may be trademarks of the companies with which they are associated.

©2004 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZiLOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Devices sold by ZiLOG, Inc. are covered by warranty and limitation of liability provisions appearing in the ZiLOG, Inc. Terms and Conditions of Sale. ZiLOG, Inc. makes no warranty of merchantability or fitness for any purpose Except with the express written approval of ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

- Power-On Reset (POR)

- 3.0-3.6V operating voltage with 5V-tolerant inputs

- 0° to +70°C standard temperature and -40° to +105°C extended temperature operating ranges

## **Part Selection Guide**

Table 1 identifies the basic features and package styles available for each device within the Z8F640x family product line.

Table 1. Z8F640x Family Part Selection Guide

| Part<br>Number | Flash<br>(KB) | RAM<br>(KB) | I/O | 16-bit Timers<br>with PWM |    | UARTs<br>with IrDA | I <sup>2</sup> C | SPI |   | 64/68-pin<br>packages |   |

|----------------|---------------|-------------|-----|---------------------------|----|--------------------|------------------|-----|---|-----------------------|---|

| Z8F1601        | 16            | 2           | 31  | 3                         | 8  | 2                  | 1                | 1   | Х |                       |   |

| Z8F1602        | 16            | 2           | 46  | 4                         | 12 | 2                  | 1                | 1   |   | Х                     |   |

| Z8F2401        | 24            | 2           | 31  | 3                         | 8  | 2                  | 1                | 1   | Х |                       |   |

| Z8F2402        | 24            | 2           | 46  | 4                         | 12 | 2                  | 1                | 1   |   | Х                     |   |

| Z8F3201        | 32            | 2           | 31  | 3                         | 8  | 2                  | 1                | 1   | Х |                       |   |

| Z8F3202        | 32            | 2           | 46  | 4                         | 12 | 2                  | 1                | 1   |   | Х                     |   |

| Z8F4801        | 48            | 4           | 31  | 3                         | 8  | 2                  | 1                | 1   | Х |                       |   |

| Z8F4802        | 48            | 4           | 46  | 4                         | 12 | 2                  | 1                | 1   |   | Х                     |   |

| Z8F4803        | 48            | 4           | 60  | 4                         | 12 | 2                  | 1                | 1   |   |                       | Х |

| Z8F6401        | 64            | 4           | 31  | 3                         | 8  | 2                  | 1                | 1   | Х |                       |   |

| Z8F6402        | 64            | 4           | 46  | 4                         | 12 | 2                  | 1                | 1   |   | Х                     |   |

| Z8F6403        | 64            | 4           | 60  | 4                         | 12 | 2                  | 1                | 1   |   |                       | Х |

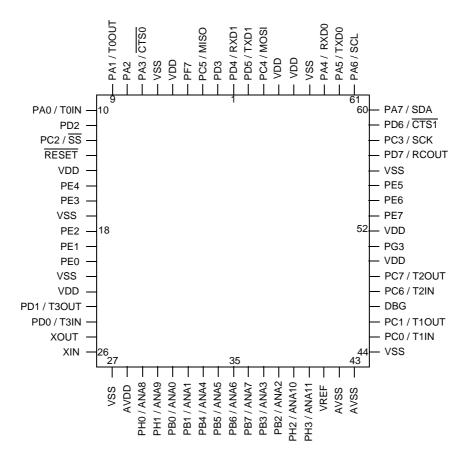

Figure 60. Z8Fxx02 in 68-Pin Plastic Leaded Chip Carrier (PLCC)

| Address (Hex)   | <b>Register Description</b>        | Mnemonic  | Reset (Hex) | Page # |

|-----------------|------------------------------------|-----------|-------------|--------|

| F62             | SPI Status                         | SPISTAT   | 01          | 108    |

| F63             | SPI Mode                           | SPIMODE   | 00          | 109    |

| F64-F65         | Reserved                           |           | XX          |        |

| F66             | SPI Baud Rate High Byte            | SPIBRH    | FF          | 110    |

| F67             | SPI Baud Rate Low Byte             | SPIBRL    | FF          | 110    |

| F68-F69         | Reserved                           | —         | XX          |        |

| Analog-to-Digit | al Converter (ADC)                 |           |             |        |

| F70             | ADC Control                        | ADCCTL    | 20          | 135    |

| F71             | Reserved                           |           | XX          |        |

| F72             | ADC Data High Byte                 | ADCD_H    | XX          | 137    |

| F73             | ADC Data Low Bits                  | ADCD_L    | XX          | 137    |

| F74-FAF         | Reserved                           | _         | XX          |        |

| DMA 0           |                                    |           |             |        |

| FB0             | DMA0 Control                       | DMA0CTL   | 00          | 124    |

| FB1             | DMA0 I/O Address                   | DMA0IO    | XX          | 125    |

| FB2             | DMA0 End/Start Address High Nibble | DMA0H     | XX          | 126    |

| FB3             | DMA0 Start Address Low Byte        | DMA0START | XX          | 127    |

| FB4             | DMA0 End Address Low Byte          | DMA0END   | XX          | 128    |

| DMA 1           |                                    |           |             |        |

| FB8             | DMA1 Control                       | DMA1CTL   | 00          | 124    |

| FB9             | DMA1 I/O Address                   | DMA1IO    | XX          | 125    |

| FBA             | DMA1 End/Start Address High Nibble | DMA1H     | XX          | 126    |

| FBB             | DMA1 Start Address Low Byte        | DMA1START | XX          | 127    |

| FBC             | DMA1 End Address Low Byte          | DMA1END   | XX          | 128    |

| DMA ADC         |                                    |           |             |        |

| FBD             | DMA_ADC Address                    | DMAA_ADDR | XX          | 128    |

| FBE             | DMA_ADC Control                    | DMAACTL   | 00          | 130    |

| FBF             | DMA_ADC Status                     | DMAASTAT  | 00          | 131    |

| Interrupt Conti | oller                              |           |             |        |

| FC0             | Interrupt Request 0                | IRQ0      | 00          | 48     |

| FC1             | IRQ0 Enable High Bit               | IRQ0ENH   | 00          | 51     |

| FC2             | IRQ0 Enable Low Bit                | IRQ0ENL   | 00          | 51     |

| FC3             | Interrupt Request 1                | IRQ1      | 00          | 49     |

| FC4             | IRQ1 Enable High Bit               | IRQIENH   | 00          | 52     |

| FC5             | IRQ1 Enable Low Bit                | IRQIENL   | 00          | 52     |

| FC6             | Interrupt Request 2                | IRQ2      | 00          | 50     |

| FC7             | IRQ2 Enable High Bit               | IRQ2ENH   | 00          | 53     |

| FC8             | IRQ2 Enable Low Bit                | IRQ2ENL   | 00          | 53     |

| FC9-FCC         | Reserved                           | _         | XX          |        |

| FCD             | Interrupt Edge Select              | IRQES     | 00          | 54     |

#### Table 6. Register File Address Map (Continued)

| Device  | Packages       | Port A | Port B | Port C | Port D | Port E | Port F | Port G | Port H |

|---------|----------------|--------|--------|--------|--------|--------|--------|--------|--------|

| Z8F6401 | 44-pin         | [7:0]  | [7:0]  | [7:0]  | [6:0]  | -      | -      | -      | -      |

| Z8F6402 | 64- and 68-pin | [7:0]  | [7:0]  | [7:0]  | [7:0]  | [7:0]  | [7]    | [3]    | [3:0]  |

| Z8F6403 | 80-pin         | [7:0]  | [7:0]  | [7:0]  | [7:0]  | [7:0]  | [7:0]  | [7:0]  | [3:0]  |

Table 10. Port Availability by Device and Package Type (Continued)

#### Architecture

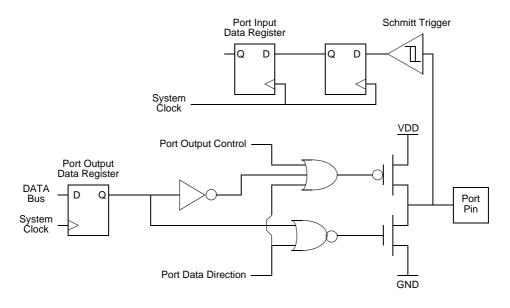

Figure 64 illustrates a simplified block diagram of a GPIO port pin. In this figure, the ability to accommodate alternate functions and variable port current drive strength are not illustrated.

Figure 64. GPIO Port Pin Block Diagram

### **GPIO Alternate Functions**

Many of the GPIO port pins can be used as both general-purpose I/O and to provide access to on-chip peripheral functions such as the timers and serial communication devices. The Port A-H Alternate Function sub-registers configure these pins for either general-purpose I/O or alternate function operation. When a pin is configured for alternate function, control

| Port Register Mnemonic     | Port Register Name                                              |

|----------------------------|-----------------------------------------------------------------|

| PxADDR                     | Port A-H Address Register<br>(Selects sub-registers)            |

| PxCTL                      | Port A-H Control Register<br>(Provides access to sub-registers) |

| PxIN                       | Port A-H Input Data Register                                    |

| PxOUT                      | Port A-H Output Data Register                                   |

| Port Sub-Register Mnemonic | Port Register Name                                              |

| PxDD                       | Data Direction                                                  |

| PxAF                       | Alternate Function                                              |

| PxOC                       | Output Control (Open-Drain)                                     |

| PxHDE                      | High Drive Enable                                               |

| PxSMRE                     | STOP Mode Recovery Source<br>Enable                             |

Table 12. GPIO Port Registers and Sub-Registers

#### **Port A-H Address Registers**

The Port A-H Address registers select the GPIO Port functionality accessible through the Port A-H Control registers. The Port A-H Address and Control registers combine to provide access to all GPIO Port control (Table 13).

Table 13. Port A-H GPIO Address Registers (PxADDR)

| BITS  | 7 | 6                                              | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|------------------------------------------------|---|---|---|---|---|---|

| FIELD |   | PADDR[7:0]                                     |   |   |   |   |   |   |

| RESET |   | 00H                                            |   |   |   |   |   |   |

| R/W   |   | R/W                                            |   |   |   |   |   |   |

| ADDR  |   | FD0H, FD4H, FD8H, FDCH, FE0H, FE4H, FE8H, FECH |   |   |   |   |   |   |

| BITS  | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|-------|---------|---------|---------|---------|---------|---------|---------|---------|

| FIELD | PAD7ENH | PAD6ENH | PAD5ENH | PAD4ENH | PAD3ENH | PAD2ENH | PAD1ENH | PAD0ENH |

| RESET | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| R/W   | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |

| ADDR  |         |         |         | FC      | 4H      |         |         |         |

#### Table 30. IRQ1 Enable High Bit Register (IRQ1ENH)

PAD*x*ENH—Port A or Port D Bit[*x*] Interrupt Request Enable High Bit Refer to the Interrupt Port Select register for selection of either Port A or Port D as the interrupt source.

Table 31. IRQ1 Enable Low Bit Register (IRQ1ENL)

| BITS  | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|-------|---------|---------|---------|---------|---------|---------|---------|---------|

| FIELD | PAD7ENL | PAD6ENL | PAD5ENL | PAD4ENL | PAD3ENL | PAD2ENL | PAD1ENL | PAD0ENL |

| RESET | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| R/W   | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |

| ADDR  |         |         |         | FC      | 5H      |         |         |         |

PADxENL—Port A or Port D Bit[x] Interrupt Request Enable Low Bit Refer to the Interrupt Port Select register for selection of either Port A or Port D as the interrupt source.

### **IRQ2 Enable High and Low Bit Registers**

The IRQ2 Enable High and Low Bit registers (Tables 33 and 34) form a priority encoded enabling for interrupts in the Interrupt Request 2 register. Priority is generated by setting bits in each register. Table 32 describes the priority control for IRQ2.

Table 32. IRQ2 Enable and Priority Encoding

| IRQ2ENH[x] | IRQ2ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

| 1          | 1          | Level 3  | High        |

where *x* indicates the register bits from 0 through 7.

## I<sup>2</sup>C Control Register Definitions

## I<sup>2</sup>C Data Register

The I<sup>2</sup>C Data register holds the data that is to be loaded into the I<sup>2</sup>C Shift register during a write to a slave. This register also holds data that is loaded from the I<sup>2</sup>C Shift register during a read from a slave. The I<sup>2</sup>C Shift is not accessible in the Register File address space, but is used only to buffer incoming and outgoing data.

Table 66. I<sup>2</sup>C Data Register (I2CDATA)

| BITS  | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-----|-----------------------------|---|---|---|---|---|---|--|

| FIELD |     | DATA                        |   |   |   |   |   |   |  |

| RESET | 0   | 0                           | 0 | 0 | 0 | 0 | 0 | 0 |  |

| R/W   | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |

| ADDR  |     | F50H                        |   |   |   |   |   |   |  |

## I<sup>2</sup>C Status Register

The Read-only I<sup>2</sup>C Status register indicates the status of the I<sup>2</sup>C Controller.

| BITS  | 7    | 6    | 5   | 4   | 3  | 2   | 1   | 0    |

|-------|------|------|-----|-----|----|-----|-----|------|

| FIELD | TDRE | RDRF | ACK | 10B | RD | TAS | DSS | NCKI |

| RESET | 1    | 0    | 0   | 0   | 0  | 0   | 0   | 0    |

| R/W   | R    | R    | R   | R   | R  | R   | R   | R    |

| ADDR  |      | F51H |     |     |    |     |     |      |

Table 67. I<sup>2</sup>C Status Register (I2CSTAT)

TDRE—Transmit Data Register Empty

When the I<sup>2</sup>C Controller is enabled, this bit is 1 when the I<sup>2</sup>C Data register is empty. When active, this bit causes the I<sup>2</sup>C Controller to generate an interrupt, except when the I<sup>2</sup>C Controller is shifting in data during the reception of a byte or when shifting an address and the RD bit is set. This bit and the interrupt are cleared by writing to the I<sup>2</sup>CD register.

RDRF—Receive Data Register Full

This bit is set active high when the I<sup>2</sup>C Controller is enabled and the I<sup>2</sup>C Controller has

#### FHSWP—Flash High Sector Write Protect FWP—Flash Write Protect These two Option Bits combine to provide 3 levels of Program Memory protection:

| FHSWP  | FWP | Description                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0   | Programming and erasure disabled for all of Program Memory.<br>Programming, Page Erase, and Mass Erase via User Code is disabled. Mass<br>Erase is available through the On-Chip Debugger.                                                                                                                                                                                                                                     |

| 1      | 0   | Programming and Page Erase are enabled for the High Sector of the<br>Program Memory only. The High Sector on the Z8F640x family device<br>contains 1KB to 4KB of Flash with addresses at the top of the available<br>Flash memory. Programming and Page Erase are disabled for the other<br>portions of the Program Memory. Mass erase through user code is disabled.<br>Mass Erase is available through the On-Chip Debugger. |

| 0 or 1 | 1   | Programming, Page Erase, and Mass Erase are enabled for all of Program Memory.                                                                                                                                                                                                                                                                                                                                                 |

### Program Memory Address 0001H

#### Table 91. Options Bits at Program Memory Address 0001H

| BITS                                            | 7                      | 6   | 5   | 4   | 3   | 2   | 1   | 0 |  |  |

|-------------------------------------------------|------------------------|-----|-----|-----|-----|-----|-----|---|--|--|

| FIELD                                           | Reserved               |     |     |     |     |     |     |   |  |  |

| RESET                                           | U                      | U   | U   | U   | U   | U   | U   | U |  |  |

| R/W                                             | R/W                    | R/W | R/W | R/W | R/W | R/W | R/W |   |  |  |

| ADDR                                            | R Program Memory 0001H |     |     |     |     |     |     |   |  |  |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                        |     |     |     |     |     |     |   |  |  |

Reserved

These Option Bits are reserved for future use and must always be 1. This setting is the default for unprogrammed (erased) Flash.

ister. When the Watchpoint event occurs, the Z8F640x family device enters Debug mode and the DBGMODE bit in the OCDCTL register becomes 1.

#### **Runtime Counter**

The On-Chip Debugger contains a 16-bit Runtime Counter. It counts system clock cycles between Breakpoints. The counter starts counting when the On-Chip Debugger leaves Debug mode and stops counting when it enters Debug mode again or when it reaches the maximum count of FFFFH.

### **On-Chip Debugger Commands**

The host communicates to the On-Chip Debugger by sending OCD commands using the DBG interface. During normal operation of the Z8F640x family device, only a subset of the OCD commands are available. In Debug mode, all OCD commands become available unless the user code and control registers are protected by programming the Read Protect Option Bit (RP). The Read Protect Option Bit prevents the code in memory from being read out of the Z8F640x family device. When this option is enabled, several of the OCD commands are disabled. Table 93 contains a summary of the On-Chip Debugger commands. Each OCD command is described in further detail in the bulleted list following Table 93. Table 93 indicates those commands that operate when the Z8F640x family device is not in Debug mode (normal operation) and those commands that are disabled by programming the Read Protect Option Bit.

| Debug Command              | Command Byte | Enabled when NOT in Debug mode? | Disabled by<br>Read Protect Option Bit                                                                                                                                    |

|----------------------------|--------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read OCD Revision          | 00H          | Yes                             | -                                                                                                                                                                         |

| Reserved                   | 01H          | -                               | -                                                                                                                                                                         |

| Read OCD Status Register   | 02H          | Yes                             | -                                                                                                                                                                         |

| Read Runtime Counter       | 03H          | -                               | -                                                                                                                                                                         |

| Write OCD Control Register | 04H          | Yes                             | Cannot clear DBGMODE bit                                                                                                                                                  |

| Read OCD Control Register  | 05H          | Yes                             | -                                                                                                                                                                         |

| Write Program Counter      | 06H          | -                               | Disabled                                                                                                                                                                  |

| Read Program Counter       | 07H          | -                               | Disabled                                                                                                                                                                  |

| Write Register             | 08H          | -                               | Only writes of the Flash Memory Control<br>registers are allowed. Additionally, only the<br>Mass Erase command is allowed to be<br>written to the Flash Control register. |

| Read Register              | 09H          | -                               | Disabled                                                                                                                                                                  |

#### Table 93. On-Chip Debugger Commands

#### Table 101. DC Characteristics

|                  |                                | T <sub>A</sub> = | $T_{\rm A} = -40^{0} {\rm C} \text{ to } 105^{0} {\rm C}$ |         |       |                       |

|------------------|--------------------------------|------------------|-----------------------------------------------------------|---------|-------|-----------------------|

| Symbol           | Parameter                      | Minimum          | Typical                                                   | Maximum | Units | Conditions            |

| I <sub>PU</sub>  | Weak Pull-up Current           | 30               | 100                                                       | 350     | μA    | $V_{DD} = 3.0 - 3.6V$ |

| I <sub>CCS</sub> | Supply Current in Stop<br>Mode |                  | 600                                                       |         | μA    | $V_{DD} = 3.3 V$      |

<sup>1</sup> This condition excludes all pins that have on-chip pull-ups, when driven Low.

<sup>2</sup> These values are provided for design guidance only and are not tested in production.

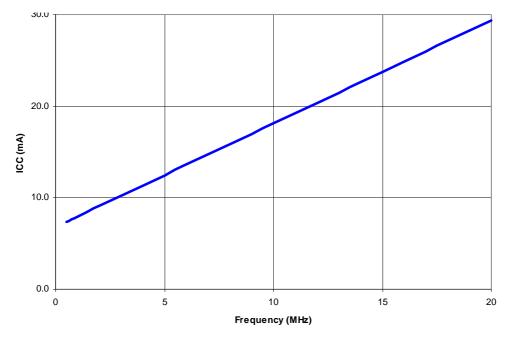

Figure 91 illustrates the typical current consumption while operating at 25°C, 3.3V, versus the system clock frequency.

Figure 91. Nominal ICC Versus System Clock Frequency

#### Table 116. Additional Symbols

| Symbol | Definition                |

|--------|---------------------------|

| dst    | Destination Operand       |

| src    | Source Operand            |

| @      | Indirect Address Prefix   |

| SP     | Stack Pointer             |

| PC     | Program Counter           |

| FLAGS  | Flags Register            |

| RP     | Register Pointer          |

| #      | Immediate Operand Prefix  |

| В      | Binary Number Suffix      |

| %      | Hexadecimal Number Prefix |

| Н      | Hexadecimal Number Suffix |

|        |                           |

Assignment of a value is indicated by an arrow. For example,

$dst \leftarrow dst + src$

indicates the source data is added to the destination data and the result is stored in the destination location.

## eZ8 CPU Instruction Classes

eZ8 CPU instructions can be divided functionally into the following groups:

- Arithmetic

- Bit Manipulation

- Block Transfer

- CPU Control

- Load

- Logical

- Program Control

- Rotate and Shift

Tables 118 through 125 contain the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table as these instruction can be considered as a subset of more than one category. Within these tables, the source operand is identified as 'src', the destination operand is 'dst' and a condition code is 'cc'.

| Mnemonic | Operands | Instruction                                  |

|----------|----------|----------------------------------------------|

| ADC      | dst, src | Add with Carry                               |

| ADCX     | dst, src | Add with Carry using Extended Addressing     |

| ADD      | dst, src | Add                                          |

| ADDX     | dst, src | Add using Extended Addressing                |

| СР       | dst, src | Compare                                      |

| CPC      | dst, src | Compare with Carry                           |

| CPCX     | dst, src | Compare with Carry using Extended Addressing |

| CPX      | dst, src | Compare using Extended Addressing            |

| DA       | dst      | Decimal Adjust                               |

| DEC      | dst      | Decrement                                    |

| DECW     | dst      | Decrement Word                               |

| INC      | dst      | Increment                                    |

| INCW     | dst      | Increment Word                               |

| MULT     | dst      | Multiply                                     |

|          |          |                                              |

#### Table 118. Arithmetic Instructions

| Mnemonic | Operands | Instruction             |

|----------|----------|-------------------------|

| CCF      | —        | Complement Carry Flag   |

| DI       | —        | Disable Interrupts      |

| EI       | _        | Enable Interrupts       |

| HALT     | _        | Halt Mode               |

| NOP      | _        | No Operation            |

| RCF      | —        | Reset Carry Flag        |

| SCF      | _        | Set Carry Flag          |

| SRP      | src      | Set Register Pointer    |

| STOP     | —        | Stop Mode               |

| WDT      | _        | Watch-Dog Timer Refresh |

#### **Table 121. CPU Control Instructions**

#### Table 122. Load Instructions

| Mnemonic | Operands    | Instruction                                                            |

|----------|-------------|------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                  |

| LD       | dst, src    | Load                                                                   |

| LDC      | dst, src    | Load Constant to/from Program Memory                                   |

| LDCI     | dst, src    | Load Constant to/from Program Memory and Auto-Increment<br>Addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                 |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-Increment<br>Addresses |

| LDX      | dst, src    | Load using Extended Addressing                                         |

| LEA      | dst, X(src) | Load Effective Address                                                 |

| POP      | dst         | Рор                                                                    |

| POPX     | dst         | Pop using Extended Addressing                                          |

| PUSH     | src         | Push                                                                   |

| PUSHX    | src         | Push using Extended Addressing                                         |

| Assembly           |                                                            | Addres        | s Mode    | Opcode(s)  |   |   | Fl | ags           |   |   | Fetch    | Instr. |

|--------------------|------------------------------------------------------------|---------------|-----------|------------|---|---|----|---------------|---|---|----------|--------|

| Mnemonic           | Symbolic Operation                                         | dst           | src       | (Hex)      | С | Z | S  | V             | D | Н | Cycles C |        |

| BTJZ bit, src, dst | if $src[bit] = 0$                                          |               | r         | F6         | - | - | -  | -             | - | - | 3        | 3      |

|                    | $PC \leftarrow PC + X$                                     |               | Ir        | F7         | - |   |    |               |   |   | 3        | 4      |

| CALL dst           | $SP \leftarrow SP - 2$                                     | IRR           |           | D4         | - | - | -  | -             | - | - | 2        | 6      |

|                    | $ @ SP \leftarrow PC  PC \leftarrow dst $                  | DA            |           | D6         | - |   |    |               |   |   | 3        | 3      |

| CCF                | $C \leftarrow \sim C$                                      |               |           | EF         | * | - | -  | -             | - | - | 1        | 2      |

| CLR dst            | $dst \leftarrow 00H$                                       | R             |           | B0         | - | - | -  | -             | - | - | 2        | 2      |

|                    |                                                            | IR            |           | B1         | - |   |    |               |   |   | 2        | 3      |

| COM dst            | $dst \leftarrow \sim dst$                                  | R             |           | 60         | - | * | *  | 0             | - | - | 2        | 2      |

|                    |                                                            | IR            |           | 61         | - |   |    |               |   |   | 2        | 3      |

| CP dst, src        | dst - src                                                  | r             | r         | A2         | * | * | *  | *             | - | - | 2        | 3      |

|                    |                                                            | r             | Ir        | A3         | - |   |    |               |   |   | 2        | 4      |

|                    |                                                            | R             | R         | A4         | - |   |    |               |   |   | 3        | 3      |

|                    |                                                            | R             | IR        | A5         | - |   |    |               |   |   | 3        | 4      |

|                    |                                                            | R             | IM        | A6         | - |   |    |               |   |   | 3        | 3      |

|                    |                                                            | IR            | IM        | A7         | - |   |    |               |   |   | 3        | 4      |

| CPC dst, src       | dst - src - C                                              | r             | r         | 1F A2      | * | * | *  | *             | - | - | 3        | 3      |

|                    |                                                            | r             | Ir        | 1F A3      | - |   |    |               |   |   | 3        | 4      |

|                    |                                                            | R             | R         | 1F A4      | - |   |    |               |   |   | 4        | 3      |

|                    |                                                            | R             | IR        | 1F A5      | - |   |    |               |   |   | 4        | 4      |

|                    |                                                            | R             | IM        | 1F A6      | - |   |    |               |   |   | 4        | 3      |

|                    |                                                            | IR            | IM        | 1F A7      | - |   |    |               |   |   | 4        | 4      |

| CPCX dst, src      | dst - src - C                                              | ER            | ER        | 1F A8      | * | * | *  | *             | - | - | 5        | 3      |

|                    |                                                            | ER            | IM        | 1F A9      | - |   |    |               |   |   | 5        | 3      |

| CPX dst, src       | dst - src                                                  | ER            | ER        | A8         | * | * | *  | *             | - | - | 4        | 3      |

|                    |                                                            | ER            | IM        | A9         | - |   |    |               |   |   | 4        | 3      |

| Flags Notation:    | * = Value is a function<br>- = Unaffected<br>X = Undefined | of the result | lt of the | operation. |   |   |    | et to<br>to 1 | 0 |   |          |        |

#### Table 126. eZ8 CPU Instruction Summary (Continued)

| Assembly        |                                                                         | Addres   | s Mode      | <b>Opcode</b> (s) |   |   | Fl         | ags           |   |   | Fotch | Instr. |

|-----------------|-------------------------------------------------------------------------|----------|-------------|-------------------|---|---|------------|---------------|---|---|-------|--------|

| Mnemonic        | Symbolic Operation                                                      | dst      | src         | (Hex)             | С | Z | S          | V             | D | Н |       | Cycles |

| POP dst         | $dst \leftarrow @SP$                                                    | R        |             | 50                | - | - | -          | -             | - | - | 2     | 2      |

|                 | $SP \leftarrow SP + 1$                                                  | IR       |             | 51                | - |   |            |               |   |   | 2     | 3      |

| POPX dst        | $dst \leftarrow @SP \\ SP \leftarrow SP + 1$                            | ER       |             | D8                | - | - | -          | -             | - | - | 3     | 2      |

| PUSH src        | $SP \leftarrow SP - 1$                                                  | R        |             | 70                | - | - | -          | -             | - | - | 2     | 2      |

|                 | $@$ SP $\leftarrow$ src                                                 | IR       |             | 71                | - |   |            |               |   |   | 2     | 3      |

| PUSHX src       | $SP \leftarrow SP - 1$<br>@SP \leftarrow src                            | ER       |             | C8                | - | - | -          | -             | - | - | 3     | 2      |

| RCF             | C ← 0                                                                   |          |             | CF                | 0 | - | -          | -             | - | - | 1     | 2      |

| RET             | $\begin{array}{l} PC \leftarrow @SP\\ SP \leftarrow SP + 2 \end{array}$ |          |             | AF                | - | - | -          | -             | - | - | 1     | 4      |

| RL dst          | C ← D7D6D5D4D3D2D1D0 ← dst                                              | R        |             | 90                | * | * | *          | *             | - | - | 2     | 2      |

|                 |                                                                         | IR       |             | 91                | - |   |            |               |   |   | 2     | 3      |

| RLC dst         |                                                                         | R        |             | 10                | * | * | *          | *             | - | - | 2     | 2      |

|                 | C ← D7 D6 D5 D4 D3 D2 D1 D0 ←<br>dst                                    | IR       |             | 11                | - |   |            |               |   |   | 2     | 3      |

| RR dst          |                                                                         | R        |             | E0                | * | * | *          | *             | - | - | 2     | 2      |

|                 | D7D6D5D4D3D2D1D0                                                        | IR       |             | E1                | - |   |            |               |   |   | 2     | 3      |

| RRC dst         | 「                                                                       | R        |             | C0                | * | * | *          | *             | - | - | 2     | 2      |

|                 | D7D6D5D4D3D2D1D0 C                                                      | IR       |             | C1                | - |   |            |               |   |   | 2     | 3      |

| Flags Notation: | * = Value is a function of<br>- = Unaffected<br>X = Undefined           | the resu | lt of the o | operation.        |   |   | Res<br>Set | et to<br>to 1 | 0 |   |       |        |

#### Table 126. eZ8 CPU Instruction Summary (Continued)

# Packaging

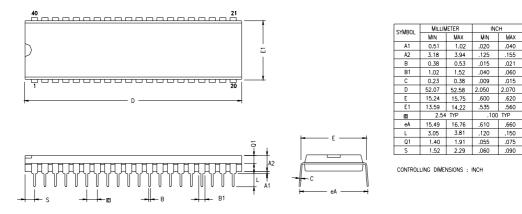

Figure 103 illustrates the 40-pin PDIP (plastic dual-inline package) available for the Z8F1601, Z8F2401, Z8F3201, Z8F4801, and Z8F6401 devices.

Figure 103. 40-Lead Plastic Dual-Inline Package (PDIP)

#### Z8F640x/Z8F480x/Z8F320x/Z8F240x/Z8F160x Z8 Encore!®

INCH

MIN

MAX

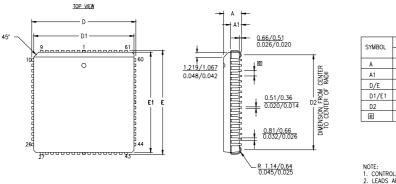

Figure 107 illustrates the 68-pin PLCC (plastic lead chip carrier) package available for the Z8F1602, Z8F2402, Z8F3202, Z8F4802, and Z8F6402 devices.

| A     | 4.32  | 4.57  | .170 | .180  |

|-------|-------|-------|------|-------|

| A1    | 2.43  | 2.92  | .095 | .115  |

| D/E   | 25.02 | 25.40 | .985 | 1.000 |

| D1/E1 | 24.13 | 24.33 | .950 | .958  |

| D2    | 22.86 | 23.62 | .900 | .930  |

| e     | 1.27  | BSC   | .050 | BSC   |

|       |       |       |      |       |

|       |       |       |      |       |

MAX

MILLIMETER

MIN

NOTE: 1. CONTROLLING DIVENSIONS : INCH. 2. LEADS ARE COPLANAR WITHIN 0.004 IN. RANGE. 3. DIVENSION : MM INCH.

Figure 107. 68-Lead Plastic Lead Chip Carrier Package (PLCC)

#### Z8F640x/Z8F480x/Z8F320x/Z8F240x/Z8F160x Z8 Encorel<sup>®</sup>

read watchpoint (21H) 161 step instruction (10H) 160 stuff instruction (11H) 160 write data memory (0CH) 159 write OCD control register (04H) 158 write program counter (06H) 158 write program memory (0AH) 159 write register (08H) 158 write watchpoint (20H) 161 on-chip debugger 5 on-chip debugger (OCD) 151 on-chip debugger signals 14 on-chip oscillator 165 one-shot mode 70 opcode map abbreviations 203 cell description 202 first 204 second after 1FH 205 OR 190 ordering information 211 **ORX 190** oscillator signals 14

## P

p 184 packaging LOFP 44 lead 207 64 lead 208 **PDIP 206** PLCC 44 lead 207 68 lead 209 **OFP 210** part number description 214 part selection guide 2 PC 185 **PDIP 206** peripheral AC and DC electrical characteristics 173 PHASE=0 timing (SPI) 103 PHASE=1 timing (SPI) 104 pin characteristics 15

PLCC 44 lead 207 68-lead 209 polarity 184 POP 189 pop using extended addressing 189 **POPX 189** port availability, device 33 port input timing (GPIO) 176 port output timing, GPIO 177 power supply signals 15 power-down, automatic (ADC) 133 power-on and voltage brown-out 173 power-on reset (POR) 27 problem description or suggestion 217 product information 216 program control instructions 190 program counter 185 program memory 18 **PUSH 189** push using extended addressing 189 PUSHX 189 PWM mode 70 PxADDR register 37 PxCTL register 38

## Q

QFP 210

## R

R 184 r 184 RA, register address 184 RCF 188, 189 receive 10-bit data format (I2C) 116 7-bit data transfer format (I2C) 115 IrDA data 97 receive interrupt 112 receiving UART data-DMA controller 83 receiving UART data-interrupt-driven method 82 receiving UART data-polled method 82

gated mode 64, 71 one-shot mode 58, 70 operating mode 58 PWM mode 61, 70 reading the timer count values 66 reload high and low byte registers 67 timer control register definitions 66 timer output signal operation 66 timers 0-3 control registers 70 high and low byte registers 66, 69 TM. TMX 188 tools, hardware and software 214 transmit IrDA data 96 transmit interrupt 112 transmitting UART data-polled method 80 transmitting UART data-interrupt-driven method 81 **TRAP 190**

## U

UART 4 architecture 78 asynchronous data format without/with parity 80 baud rate generator 85 baud rates table 93 control register definitions 86 controller signals 14 data format 79 interrupts 85 multiprocessor mode 84 receiving data using DMA controller 83 receiving data using interrupt-driven method 82 receiving data using the polled method 82 transmitting data using the interrupt-driven method 81 transmitting data using the polled method 80 x baud rate high and low registers 91 x control 0 and control 1 registers 89 x status 0 and status 1 registers 87 **UxBRH** register 91

UxBRL register 92 UxCTL0 register 89 UxCTL1 register 90 UxRXD register 87 UxSTAT0 register 87 UxSTAT1 register 89 UxTXD register 86

## V

vector 184 voltage brown-out reset (VBR) 27

## W

watch-dog timer approximate time-out delays 72, 73 CNTL 28 control register 75 electrical characteristics and timing 174 interrupt in normal operation 73 interrupt in stop mode 73 operation 72 refresh 73, 189 reload unlock sequence 74 reload upper, high and low registers 76 reset 28 reset in normal operation 74 reset in stop mode 74 time-out response 73 WDTCTL register 75 WDTH register 76 WDTL register 77 working register 184 working register pair 184 WTDU register 76

## X

X 184 XOR 190 XORX 190