Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                    |

| Number of I/O              | 46                                                            |

| Program Memory Size        | 48KB (48K x 8)                                                |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 4K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                     |

| Data Converters            | A/D 12x10b                                                    |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 64-LQFP                                                       |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f4802ar020ec00tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Table of Contents

| Introduction                       |

|------------------------------------|

| Features                           |

| Part Selection Guide               |

| Block Diagram                      |

| CPU and Peripheral Overview        |

| eZ8 CPU Features 3                 |

| General Purpose I/O 4              |

| Flash Controller                   |

| 10-Bit Analog-to-Digital Converter |

| UARTs                              |

| I <sup>2</sup> C                   |

| Serial Peripheral Interface        |

| Timers                             |

| Interrupt Controller 5             |

| Reset Controller                   |

| On-Chip Debugger 5                 |

| DMA Controller                     |

| Signal and Pin Descriptions        |

| Overview                           |

| Available Packages                 |

| Pin Configurations                 |

| Signal Descriptions                |

| Pin Characteristics                |

| Address Space                      |

| Overview                           |

| Register File                      |

| Program Memory                     |

| Data Memory                        |

| Register File Address Map0         |

| Reset and Stop Mode Recovery       |

| Overview                           |

| Reset Types                        |

| System and Short Resets            |

| Reset Sources                      |

| Power-On Reset                     |

| Voltage Brown-Out Reset            |

| Watch-Dog Timer Reset              |

| Option Bits                                                 |

|-------------------------------------------------------------|

| Overview                                                    |

| Operation                                                   |

| Option Bit Configuration By Reset                           |

| Option Bit Address Space                                    |

| Program Memory Address 0000H 149                            |

| Program Memory Address 0001H 150                            |

| On-Chip Debugger                                            |

| Overview                                                    |

| Architecture                                                |

| Operation                                                   |

| OCD Interface                                               |

| Debug Mode                                                  |

| OCD Data Format                                             |

| OCD Auto-Baud Detector/Generator                            |

| OCD Serial Errors 155                                       |

| Breakpoints                                                 |

| Watchpoints                                                 |

| Runtime Counter                                             |

| On-Chip Debugger Commands 156                               |

| On-Chip Debugger Control Register Definitions               |

| OCD Control Register 161                                    |

| OCD Status Register 162                                     |

| OCD Watchpoint Control Register                             |

| OCD Watchpoint Address Register                             |

| OCD Watchpoint Data Register                                |

| On-Chip Oscillator                                          |

| 20MHz Crystal Oscillator Operation                          |

| Electrical Characteristics                                  |

| Absolute Maximum Ratings 167                                |

| DC Characteristics                                          |

| AC Characteristics                                          |

| On-Chip Peripheral AC and DC Electrical Characteristics 173 |

| General Purpose I/O Port Input Data Sample Timing           |

| General Purpose I/O Port Output Timing 177                  |

| On-Chip Debugger Timing 178                                 |

| SPI Master Mode Timing 179                                  |

| SPI Slave Mode Timing 180                                   |

| I2C Timing                                                  |

| eZ8 CPU Instruction Set                                     |

| Assembly Language Programming Introduction                  |

### Braces

The curly braces, { }, indicate a single register or bus created by concatenating some combination of smaller registers, buses, or individual bits.

• Example: the 12-bit register address {0H, RP[7:4], R1[3:0]} is composed of a 4-bit hexadecimal value (0H) and two 4-bit register values taken from the Register Pointer (RP) and Working Register R1. 0H is the most significant nibble (4-bit value) of the 12-bit register, and R1[3:0] is the least significant nibble of the 12-bit register.

### Parentheses

The parentheses, ( ), indicate an indirect register address lookup.

• Example: (R1) is the memory location referenced by the address contained in the Working Register R1.

#### **Parentheses/Bracket Combinations**

The parentheses, (), indicate an indirect register address lookup and the square brackets, [], indicate a register or bus.

• *Example:* assume PC[15:0] contains the value 1234h. (PC[15:0]) then refers to the contents of the memory location at address 1234h.

#### Use of the Words Set, Reset and Clear

The word *set* implies that a register bit or a condition contains a logical 1. The words re*set* or *clear* imply that a register bit or a condition contains a logical 0. When either of these terms is followed by a number, the word *logical* may not be included; however, it is implied.

#### Notation for Bits and Similar Registers

A field of bits within a register is designated as: Register[*n*:*n*].

• Example: ADDR[15:0] refers to bits 15 through bit 0 of the Address.

#### Use of the Terms LSB, MSB, Isb, and msb

In this document, the terms *LSB* and *MSB*, when appearing in upper case, mean *least significant byte* and *most significant byte*, respectively. The lowercase forms, *lsb* and *msb*, mean *least significant bit* and *most significant bit*, respectively.

#### **Use of Initial Uppercase Letters**

Initial uppercase letters designate settings, modes, and conditions in general text.

- Example 1: Stop mode.

- Example 2: The receiver forces the SCL line to Low.

- The Master can generate a Stop condition to abort the transfer.

If the Timer reaches FFFFH, the timer rolls over to 0000H and continue counting.

The steps for configuring a timer for Compare mode and initiating the count are as follows:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for Compare mode.

- Set the prescale value.

- Set the initial logic level (High or Low) for the Timer Output alternate function, if desired.

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

- 4. If desired, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer and initiate counting.

In Compare mode, the system clock always provides the timer input. The Compare time is given by the following equation:

## Compare Mode Time (s) = (Compare Value – Start Value) × Prescale System Clock Frequency (Hz)

## **Gated Mode**

In Gated mode, the timer counts only when the Timer Input signal is in its active state (asserted), as determined by the TPOL bit in the Timer Control register. When the Timer Input signal is asserted, counting begins. A timer interrupt is generated when the Timer Input signal is deasserted or a timer reload occurs. To determine if a Timer Input signal deassertion generated the interrupt, read the associated GPIO input value and compare to the value stored in the TPOL bit.

The timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. When reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes (assuming the Timer Input signal is still asserted). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer reset.

The steps for configuring a timer for Gated mode and initiating the count are as follows:

- 1. Write to the Timer Control register to:

- Disable the timer

### **Capture mode**

0 = Count is captured on the rising edge of the Timer Input signal.

1 = Count is captured on the falling edge of the Timer Input signal.

#### **Compare mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### Gated mode

0 = Timer counts when the Timer Input signal is High (1) and interrupts are generated on the falling edge of the Timer Input.

1 = Timer counts when the Timer Input signal is Low (0) and interrupts are generated on the rising edge of the Timer Input.

#### Capture/Compare mode

0 = Counting is started on the first rising edge of the Timer Input signal. The current count is captured on subsequent rising edges of the Timer Input signal.

1 = Counting is started on the first falling edge of the Timer Input signal. The current count is captured on subsequent falling edges of the Timer Input signal.

#### PRES—Prescale value.

The timer input clock is divided by 2<sup>PRES</sup>, where PRES can be set from 0 to 7. The prescaler is reset each time the Timer is disabled. This insures proper clock division each time the Timer is restarted.

- 000 = Divide by 1

- 001 = Divide by 2

- 010 = Divide by 4

- 011 = Divide by 8

- 100 = Divide by 16

- 101 = Divide by 32

- 110 = Divide by 64

- 111 = Divide by 128

TMODE—Timer mode

- 000 =One-Shot mode

- 001 = Continuous mode

- 010 =Counter mode

- 011 = PWM mode

- 100 = Capture mode

- 101 = Compare mode

- 110 = Gated mode

- 111 = Capture/Compare mode

# Operation

When the Infrared Endec is enabled, the transmit data from the associated on-chip UART is encoded as digital signals in accordance with the IrDA standard and output to the infrared transceiver via the TXD pin. Likewise, data received from the infrared transceiver is passed to the Infrared Endec via the RXD pin, decoded by the Infrared Endec, and then passed to the UART. Communication is half-duplex, which means simultaneous data transmission and reception is not allowed.

The baud rate is set by the UART's Baud Rate Generator and supports IrDA standard baud rates from 9600 baud to 115.2 kbaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled to use the Infrared Endec. The Infrared Endec data rate is calculated using the following equation:

# Infrared Data Rate (bits/s) = $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

## **Transmitting IrDA Data**

The data to be transmitted using the infrared transceiver is first sent to the UART. The UART's transmit signal (TXD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drives the infrared transceiver. Each UART/Infrared data bit is 16-clocks wide. If the data to be transmitted is 1, the IR\_TXD signal remains low for the full 16-clock period. If the data to be transmitted is 0, a 3-clock high pulse is output following a 7-clock low period. After the 3-clock high pulse, a 6-clock low pulse is output to complete the full 16-clock data period. Figure 72 illustrates IrDA data transmission. When the Infrared Endec is enabled, the UART's TXD signal is internal to the Z8F640x family device while the IR\_TXD signal is output through the TXD pin.

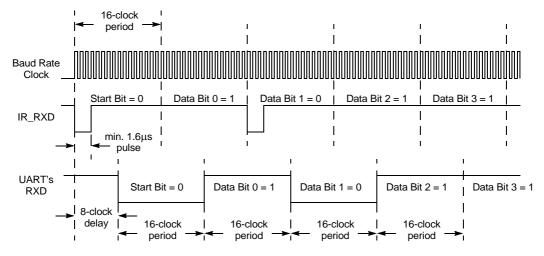

**Figure 73. Infrared Data Reception**

## Jitter

Because of the inherent sampling of the received IR\_RXD signal by the bit rate clock, some jitter can be expected on the first bit in any sequence of data. All subsequent bits in the received data stream are a fixed 16-clock periods wide.

# Infrared Encoder/Decoder Control Register Definitions

All Infrared Endec configuration and status information is set by the UART control registers as defined beginning on page 86.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART*x* Control 1 register to 1 to enable the Infrared Encoder/ Decoder *before* enabling the GPIO Port alternate function for the corresponding pin.

ZiLOG

# Serial Peripheral Interface

## Overview

The Serial Peripheral Interface<sup>™</sup> (SPI) is a synchronous interface allowing several SPItype devices to be interconnected. SPI-compatible devices include EEPROMs, Analog-to-Digital Converters, and ISDN devices. Features of the SPI include:

- Full-duplex, synchronous, character-oriented communication

- Four-wire interface

- Data transfers rates up to a maximum of one-fourth the system clock frequency

- Error detection

- Write and mode collision detection

- Dedicated Baud Rate Generator

# Architecture

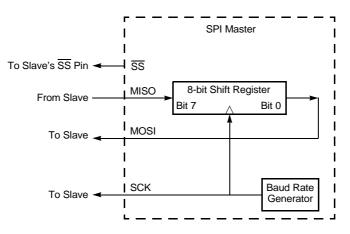

The SPI may be configured as either a Master (in single or multi-master systems) or a Slave as illustrated in Figures 74 through 76.

Figure 74. SPI Configured as a Master in a Single Master, Single Slave System

- 1. Software writes the I<sup>2</sup>C Data register with a 7-bit slave address followed by a 1 (read).

- 2. Software asserts the START bit of the I<sup>2</sup>C Control register.

- 3. Software asserts the NAK bit of the I<sup>2</sup>C Control register so that after the first byte of data has been read by the I<sup>2</sup>C Controller, a Not Acknowledge is sent to the I<sup>2</sup>C slave.

- 4. The I<sup>2</sup>C Controller sends the START condition.

- 5. The I<sup>2</sup>C Controller sends the address and read bit by the SDA signal.

- 6. The I<sup>2</sup>C slave sends an Acknowledge by pulling the SDA signal Low during the next high period of SCL.

- 7. The  $I^2C$  Controller reads the first byte of data from the  $I^2C$  slave.

- 8. The I<sup>2</sup>C Controller asserts the Receive interrupt.

- 9. Software responds by reading the  $I^2C$  Data register.

- 10. The  $I^2C$  Controller sends a NAK to the  $I^2C$  slave.

- 11. A NAK interrupt is generated by the I<sup>2</sup>C Controller.

- 12. Software responds by setting the STOP bit of the  $I^2C$  Control register.

- 13. A STOP condition is sent to the  $I^2C$  slave.

## Reading a Transaction with a 10-Bit Address

Figure 82 illustrates the receive format for a 10-bit addressed slave. The shaded regions indicate data transferred from the I<sup>2</sup>C Controller to slaves and unshaded regions indicate data transferred from the slaves to the I<sup>2</sup>C Controller.

| S | Slave Address | W=0 | А | Slave address | А | S | Slave Address | R=1 | А | Data | А | Data | Ā | Р |

|---|---------------|-----|---|---------------|---|---|---------------|-----|---|------|---|------|---|---|

|   | 1st 7 bits    |     |   | 2nd Byte      |   |   | 1st 7 bits    |     |   |      |   |      |   |   |

#### Figure 82. Receive Data Format for a 10-Bit Addressed Slave

The first seven bits transmitted in the first byte are 11110XX. The two bits XX are the two most-significant bits of the 10-bit address. The lowest bit of the first byte transferred is the write signal.

The data transfer format for a receive operation on a 10-bit addressed slave is as follows:

- 1. Software writes an address 11110B followed by the two address bits and a 0 (write).

- 2. Software asserts the START bit of the  $I^2C$  Control register.

- 3. The  $I^2C$  Controller sends the Start condition.

## **DMA Status Register**

The DMA Status register indicates the DMA channel that generated the interrupt and the ADC Analog Input that is currently undergoing conversion. Reads from this register reset the Interrupt Request Indicator bits (IRQA, IRQ1, and IRQ0) to 0. Therefore, software interrupt service routines that read this register must process all three interrupt sources from the DMA.

| Table 79. DMA_ADC Status Register (DMAA_STAT) |

|-----------------------------------------------|

|-----------------------------------------------|

| BITS  | 7 | 6    | 5      | 4 | 3        | 2    | 1    | 0    |

|-------|---|------|--------|---|----------|------|------|------|

| FIELD |   | CAD  | C[3:0] |   | Reserved | IRQA | IRQ1 | IRQ0 |

| RESET | 0 | 0    | 0      | 0 | 0        | 0    | 0    | 0    |

| R/W   | R | R    | R      | R | R        | R    | R    | R    |

| ADDR  |   | FBFH |        |   |          |      |      |      |

CADC[3:0]—Current ADC Analog Input

This field identifies the Analog Input that the ADC is currently converting.

Reserved

This bit is reserved and must be 0.

IRQA—DMA\_ADC Interrupt Request Indicator

This bit is automatically reset to 0 each time a read from this register occurs.

$0 = DMA\_ADC$  is not the source of the interrupt from the DMA Controller.

1 = DMA\_ADC completed transfer of data from the last ADC Analog Input and generated an interrupt.

IRQ1—DMA1 Interrupt Request Indicator

This bit is automatically reset to 0 each time a read from this register occurs.

0 = DMA1 is not the source of the interrupt from the DMA Controller.

1 = DMA1 completed transfer of data to/from the End Address and generated an interrupt.

IRQ0—DMA0 Interrupt Request Indicator

This bit is automatically reset to 0 each time a read from this register occurs.

0 = DMA0 is not the source of the interrupt from the DMA Controller.

1 = DMA0 completed transfer of data to/from the End Address and generated an interrupt.

ZILOG

# Analog-to-Digital Converter

# Overview

The Analog-to-Digital Converter (ADC) converts an analog input signal to a 10-bit binary number. The features of the sigma-delta ADC include:

- 12 analog input sources are multiplexed with general-purpose I/O ports

- Interrupt upon conversion complete

- Internal voltage reference generator

- Direct Memory Access (DMA) controller can automatically initiate data conversion and transfer of the data from 1 to 12 of the analog inputs.

# Architecture

Figure 83 illustrates the three major functional blocks (converter, analog multiplexer, and voltage reference generator) of the ADC. The ADC converts an analog input signal to its digital representation. The 12-input analog multiplexer selects one of the 12 analog input sources. The ADC requires an input reference voltage for the conversion. The voltage reference for the conversion may be input through the external VREF pin or generated internally by the voltage reference generator.

## ADC Data High Byte Register

The ADC Data High Byte register contains the upper eight bits of the 10-bit ADC output. During a conversion, this value is invalid. Access to the ADC Data High Byte register is read-only. The full 10-bit ADC result is given by {ADCD\_H[7:0], ADCD\_L[7:6]}.

| BITS  | 7    | 6      | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------|--------|---|---|---|---|---|---|

| FIELD |      | ADCD_H |   |   |   |   |   |   |

| RESET |      | X      |   |   |   |   |   |   |

| R/W   |      | R      |   |   |   |   |   |   |

| ADDR  | F72H |        |   |   |   |   |   |   |

#### Table 81. ADC Data High Byte Register (ADCD\_H)

ADCD\_H—ADC Data High Byte

This byte contains the upper eight bits of the 10-bit ADC output. These bits are not valid during a conversion. These bits are undefined after a Reset.

## ADC Data Low Bits Register

The ADC Data Low Bits register contains the lower two bits of the conversion value. During a conversion this value is invalid. Access to the ADC Data Low Bits register is readonly. The full 10-bit ADC result is given by {ADCD\_H[7:0], ADCD\_L[7:6]}.

| BITS  | 7      | 6 | 5 | 4  | 3  | 2 | 1 | 0 |  |

|-------|--------|---|---|----|----|---|---|---|--|

| FIELD | ADCD_L |   |   |    |    |   |   |   |  |

| RESET | Х      |   | Х |    |    |   |   |   |  |

| R/W   | I      | ર |   |    | I  | ર |   |   |  |

| ADDR  |        |   |   | F7 | 3Н |   |   |   |  |

Table 82. ADC Data Low Bits Register (ADCD\_L)

## ADCD\_L—ADC Data Low Bits

These are the least significant two bits of the 10-bit ADC output. During a conversion, this value is invalid. These bits are undefined after a Reset.

#### Reserved

These bits are reserved and are always undefined.

## Flash Code Protection Using the Option Bits

The FHSWP and FWP Option Bits combine to provide three levels of Flash Program Memory protection as listed in Table 84. Refer to the **Option Bits** chapter for more information.

| FHSWP  | FWP | Flash Code Protection Description                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0   | Programming and erasure disabled for all of Flash Program Memory. In<br>user code programming, Page Erase, and Mass Erase are all disabled. Mass<br>Erase is available through the On-Chip Debugger.                                                                                                                                                                                                                                       |

| 1      | 0   | Programming and Page Erase are enabled for the High Sector of the Flash<br>Program Memory only. The High Sector on the Z8F640x family device<br>contains 1KB to 4KB of Flash with addresses at the top of the available<br>Flash memory. Programming and Page Erase are disabled for the other<br>portions of the Flash Program Memory. Mass erase through user code is<br>disabled. Mass Erase is available through the On-Chip Debugger. |

| 0 or 1 | 1   | Programming, Page Erase, and Mass Erase are enabled for all of Flash<br>Program Memory.                                                                                                                                                                                                                                                                                                                                                    |

Table 84. Flash Code Protection Using the Option Bits

#### Flash Code Protection Using the Flash Controller

At Reset, the Flash Controller locks to prevent accidental program or erasure of the Flash memory. To program or erase the Flash memory, unlock the Flash Controller by making two consecutive writes to the Flash Control register with the values 73H and 8CH, sequentially. After unlocking the Flash Controller, the Flash can be programmed or erased. When the Flash Controller is unlocked, any value written to the Flash Control register locks the Flash Controller. Writing the Mass Erase or Page Erase commands executes the function before locking the Flash Controller.

## **Byte Programming**

When the Flash Controller is unlocked, all writes to Program Memory program a byte into the Flash. An erased Flash byte contains all 1's (FFH). The programming operation can only be used to change bits from 1 to 0. To change a Flash bit (or multiple bits) from 0 to 1 requires execution of either the Page Erase or Mass Erase commands.

Byte Programming can be accomplished using the On-Chip Debugger's Write Memory command or eZ8 CPU execution of the LDC or LDCI instructions. Refer to the eZ8 CPU User Manual for a description of the LDC and LDCI instructions. While the Flash Controller programs the Flash memory, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. To exit programming mode and lock the Flash, write any value to the Flash Control register, except the Mass Erase or Page Erase commands.

# **Option Bits**

## **Overview**

Option Bits allow user configuration of certain aspects of Z8F640x family device operation. The feature configuration data is stored in the Program Memory and read during Reset. The features available for control via the Option Bits are:

- Watch-Dog Timer time-out response selection-interrupt or Short Reset.

- Watch-Dog Timer enabled at Reset.

- The ability to prevent unwanted read access to user code in Program Memory.

- The ability to prevent accidental programming and erasure of all or a portion of the user code in Program Memory.

## Operation

## **Option Bit Configuration By Reset**

Each time the Option Bits are programmed or erased, the Z8F640x family device must be Reset for the change to take place. During any reset operation (System Reset, Short Reset, or Stop Mode Recovery), the Option Bits are automatically read from the Program Memory and written to Option Configuration registers. The Option Configuration registers control operation of the Z8F640x family device. Option Bit control of the Z8F640x family device is established before the device exits Reset and the eZ8 CPU begins code execution. The Option Configuration registers are not part of the Register File and are not accessible for read or write access.

## **Option Bit Address Space**

The first two bytes of Program Memory at addresses 0000H and 0001H are reserved for the user Option Bits. The byte at Program Memory address 0000H is used to configure user options. The byte at Program Memory address 0001H is reserved for future use and must be left in its unprogrammed state.

### FHSWP—Flash High Sector Write Protect FWP—Flash Write Protect These two Option Bits combine to provide 3 levels of Program Memory protection:

| FHSWP  | FWP | Description                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0   | Programming and erasure disabled for all of Program Memory.<br>Programming, Page Erase, and Mass Erase via User Code is disabled. Mass<br>Erase is available through the On-Chip Debugger.                                                                                                                                                                                                                                     |

| 1      | 0   | Programming and Page Erase are enabled for the High Sector of the<br>Program Memory only. The High Sector on the Z8F640x family device<br>contains 1KB to 4KB of Flash with addresses at the top of the available<br>Flash memory. Programming and Page Erase are disabled for the other<br>portions of the Program Memory. Mass erase through user code is disabled.<br>Mass Erase is available through the On-Chip Debugger. |

| 0 or 1 | 1   | Programming, Page Erase, and Mass Erase are enabled for all of Program Memory.                                                                                                                                                                                                                                                                                                                                                 |

## Program Memory Address 0001H

### Table 91. Options Bits at Program Memory Address 0001H

| BITS                                            | 7                    | 6   | 5   | 4    | 3     | 2   | 1   | 0   |

|-------------------------------------------------|----------------------|-----|-----|------|-------|-----|-----|-----|

| FIELD                                           |                      |     |     | Rese | erved |     |     |     |

| RESET                                           | U                    | U   | U   | U    | U     | U   | U   | U   |

| R/W                                             | R/W                  | R/W | R/W | R/W  | R/W   | R/W | R/W | R/W |

| ADDR                                            | Program Memory 0001H |     |     |      |       |     |     |     |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                      |     |     |      |       |     |     |     |

Reserved

These Option Bits are reserved for future use and must always be 1. This setting is the default for unprogrammed (erased) Flash.

If the OCD receives a Serial Break (nine or more continuous bits Low) the Auto-Baud Detector/Generator resets. The Auto-Baud Detector/Generator can then be reconfigured by sending 80H.

## **OCD Serial Errors**

The On-Chip Debugger can detect any of the following error conditions on the DBG pin:

- Serial Break (a minimum of nine continuous bits Low)

- Framing Error (received Stop bit is Low)

- Transmit Collision (OCD and host simultaneous transmission detected by the OCD)

When the OCD detects one of these errors, it aborts any command currently in progress, transmits a four character long Serial Break back to the host, and resets the Auto-Baud Detector/Generator. A Framing Error or Transmit Collision may be caused by the host sending a Serial Break to the OCD. Because of the open-drain nature of the interface, returning a Serial Break break back to the host only extends the length of the Serial Break if the host releases the Serial Break early.

The host should transmit a Serial Break on the DBG pin when first connecting to the Z8F640x family device or when recovering from an error. A Serial Break from the host resets the Auto-Baud Generator/Detector but does not reset the OCD Control register. A Serial Break leaves the Z8F640x family device in Debug mode if that is the current mode. The OCD is held in Reset until the end of the Serial Break when the DBG pin returns High. Because of the open-drain nature of the DBG pin, the host can send a Serial Break to the OCD even if the OCD is transmitting a character.

## **Breakpoints**

Execution Breakpoints are generated using the BRK instruction (opcode 00H). When the eZ8 CPU decodes a BRK instruction, it signals the On-Chip Debugger. If Breakpoints are enabled, the OCD enters Debug mode and idles the eZ8 CPU. If Breakpoints are not enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP.

## **Breakpoints in Flash Memory**

The BRK instruction is opcode 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a Breakpoint, write 00H to the desired address, overwriting the current instruction. To remove a Breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

## Watchpoints

The On-Chip Debugger can set one Watchpoint to cause a Debug Break. The Watchpoint identifies a single Register File address. The Watchpoint can be set to break on reads and/ or writes of the selected Register File address. Additionally, the Watchpoint can be configured to break only when a specific data value is read and/or written from the specified reg-

# **On-Chip Oscillator**

The Z8F640x family devices feature an on-chip oscillator for use with an external 1-20MHz crystal. This oscillator generates the primary system clock for the internal eZ8 CPU and the majority of the on-chip peripherals. Alternatively, the X<sub>IN</sub> input pin can also accept a CMOS-level clock input signal (32kHz-20MHz). If an external clock generator is used, the X<sub>OUT</sub> pin must be left unconnected. The Z8F640x family device does *not* contain in internal clock divider. The frequency of the signal on the X<sub>IN</sub> input pin determines the frequency of the system clock. The Z8F640x family device on-chip oscillator does not support external RC networks or ceramic resonators.

# 20MHz Crystal Oscillator Operation

Figure 90 illustrates a recommended configuration for connection with an external 20MHz, fundamental-mode, parallel-resonant crystal. Recommended crystal specifications are provided in Table 99. Resistor R<sub>1</sub> limits total power dissipation by the crystal. Printed circuit board layout should add no more than 4pF of stray capacitance to either the X<sub>IN</sub> or X<sub>OUT</sub> pins. If oscillation does not occur, reduce the values of capacitors C<sub>1</sub> and C<sub>2</sub> to decrease loading.

ZILOG

# eZ8 CPU Instruction Set

# Assembly Language Programming Introduction

The eZ8 CPU assembly language provides a means for writing an application program without having to be concerned with actual memory addresses or machine instruction formats. A program written in assembly language is called a source program. Assembly language allows the use of symbolic addresses to identify memory locations. It also allows mnemonic codes (opcodes and operands) to represent the instructions themselves. The opcodes identify the instruction while the operands represent memory locations, registers, or immediate data values.

Each assembly language program consists of a series of symbolic commands called statements. Each statement can contain labels, operations, operands and comments.

Labels can be assigned to a particular instruction step in a source program. The label identifies that step in the program as an entry point for use by other instructions.

The assembly language also includes assembler directives that supplement the machine instruction. The assembler directives, or pseudo-ops, are not translated into a machine instruction. Rather, the pseudo-ops are interpreted as directives that control or assist the assembly process.

The source program is processed (assembled) by the assembler to obtain a machine language program called the object code. The object code is executed by the eZ8 CPU. An example segment of an assembly language program is detailed in the following example.

## Assembly Language Source Program Example

| JP START      | ; Everything after the semicolon is a comment.                                                                                                                                                                         |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START:        | ; A label called "START". The first instruction (JP START) in this ; example causes program execution to jump to the point within the ; program where the START label occurs.                                          |

| LD R4, R7     | ; A Load (LD) instruction with two operands. The first operand,<br>; Working Register R4, is the destination. The second operand,<br>; Working Register R7, is the source. The contents of R7 is<br>; written into R4. |

| LD 234H, #%01 | ; Another Load (LD) instruction with two operands.<br>; The first operand, Extended Mode Register Address 234H,<br>; identifies the destination. The second operand, Immediate Data                                    |

| Notation | Description                    | Operand | Range                                                                                                                     |  |

|----------|--------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------|--|

| b        | Bit                            | b       | b represents a value from 0 to 7 (000B to 111B).                                                                          |  |

| сс       | Condition Code                 | _       | See Condition Codes overview in the eZ8 CPU User Manual.                                                                  |  |

| DA       | Direct Address                 | Addrs   | Addrs. represents a number in the range of 0000H to FFFFH                                                                 |  |

| ER       | Extended Addressing Register   | Reg     | Reg. represents a number in the range of 000H to FFFH                                                                     |  |

| IM       | Immediate Data                 | #Data   | Data is a number between 00H to FFH                                                                                       |  |

| Ir       | Indirect Working Register      | @Rn     | n = 0 - 15                                                                                                                |  |

| IR       | Indirect Register              | @Reg    | Reg. represents a number in the range of 00H to FFH                                                                       |  |

| Irr      | Indirect Working Register Pair | @RRp    | p = 0, 2, 4, 6, 8, 10, 12, or 14                                                                                          |  |

| IRR      | Indirect Register Pair         | @Reg    | Reg. represents an even number in the range 00H to FEH                                                                    |  |

| р        | Polarity                       | р       | Polarity is a single bit binary value of either 0B or 1B.                                                                 |  |

| r        | Working Register               | Rn      | n = 0 - 15                                                                                                                |  |

| R        | Register                       | Reg     | Reg. represents a number in the range of 00H to FFH                                                                       |  |

| RA       | Relative Address               | Х       | X represents an index in the range of $+127$ to $-128$ which is an offset relative to the address of the next instruction |  |

| rr       | Working Register Pair          | RRp     | p = 0, 2, 4, 6, 8, 10, 12, or 14                                                                                          |  |

| RR       | Register Pair                  | Reg     | Reg. represents an even number in the range of 00H to FEH                                                                 |  |

| Vector   | Vector Address                 | Vector  | Vector represents a number in the range of 00H to FFH                                                                     |  |

| X        | Indexed                        | #Index  | The register or register pair to be indexed is offset by<br>the signed Index value (#Index) in a +127 to -128<br>range.   |  |

### Table 115. Notational Shorthand

Table 116 contains additional symbols that are used throughout the Instruction Summary and Instruction Set Description sections.

| Abbreviation | Description                        | Abbreviation                                   | Description            |

|--------------|------------------------------------|------------------------------------------------|------------------------|

| b            | Bit position                       | IRR                                            | Indirect Register Pair |

| сс           | Condition code                     | р                                              | Polarity (0 or 1)      |

| Х            | 8-bit signed index or displacement | r                                              | 4-bit Working Register |

| DA           | Destination address                | R                                              | 8-bit register         |

| ER           | Extended Addressing register       | r1, R1, Ir1, Irr1, IR1, rr1,<br>RR1, IRR1, ER1 | Destination address    |

| IM           | Immediate data value               | r2, R2, Ir2, Irr2, IR2, rr2,<br>RR2, IRR2, ER2 | Source address         |

| Ir           | Indirect Working Register          | RA                                             | Relative               |

| IR           | Indirect register                  | rr                                             | Working Register Pair  |

| Irr          | Indirect Working Register Pair     | RR                                             | Register Pair          |

## Table 127. Opcode Map Abbreviations