Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                    |

| Number of I/O              | 60                                                            |

| Program Memory Size        | 48KB (48K x 8)                                                |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 4K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                     |

| Data Converters            | A/D 12x10b                                                    |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 80-BQFP                                                       |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f4803ft020ec00tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Timer Operating Modes                                          |

|----------------------------------------------------------------|

| Reading the Timer Count Values                                 |

| Timer Output Signal Operation                                  |

| Timer Control Register Definitions                             |

| Timer 0-3 High and Low Byte Registers                          |

| Timer Reload High and Low Byte Registers                       |

| Timer 0-3 PWM High and Low Byte Registers                      |

| Timer 0-3 Control Registers                                    |

| Watch-Dog Timer                                                |

| Overview                                                       |

| Operation                                                      |

| Watch-Dog Timer Refresh                                        |

| Watch-Dog Timer Time-Out Response                              |

| Watch-Dog Timer Reload Unlock Sequence                         |

| Watch-Dog Timer Control Register Definitions                   |

| Watch-Dog Timer Control Register                               |

| Watch-Dog Timer Reload Upper, High and Low Byte Registers . 76 |

| UART                                                           |

| Overview                                                       |

| Architecture                                                   |

| Operation                                                      |

| Data Format                                                    |

| Transmitting Data using the Polled Method                      |

| Transmitting Data using the Interrupt-Driven Method            |

| Receiving Data using the Polled Method                         |

| Receiving Data using the Interrupt-Driven Method               |

| Receiving Data using the Direct Memory Access                  |

| Controller (DMA)                                               |

| Multiprocessor (9-bit) Mode                                    |

| UART Interrupts                                                |

| UART Baud Rate Generator                                       |

| UART Control Register Definitions                              |

| UARTx Transmit Data Register                                   |

| UARTx Receive Data Register                                    |

| UARTx Status 0 and Status 1 Registers                          |

| UARTx Control 0 and Control 1 Registers                        |

| UARTx Baud Rate High and Low Byte Registers                    |

| Infrared Encoder/Decoder                                       |

| Overview                                                       |

| Architecture                                                   |

| Operation                                                      |

### Braces

The curly braces, { }, indicate a single register or bus created by concatenating some combination of smaller registers, buses, or individual bits.

• Example: the 12-bit register address {0H, RP[7:4], R1[3:0]} is composed of a 4-bit hexadecimal value (0H) and two 4-bit register values taken from the Register Pointer (RP) and Working Register R1. 0H is the most significant nibble (4-bit value) of the 12-bit register, and R1[3:0] is the least significant nibble of the 12-bit register.

### Parentheses

The parentheses, ( ), indicate an indirect register address lookup.

• Example: (R1) is the memory location referenced by the address contained in the Working Register R1.

### **Parentheses/Bracket Combinations**

The parentheses, (), indicate an indirect register address lookup and the square brackets, [], indicate a register or bus.

• *Example:* assume PC[15:0] contains the value 1234h. (PC[15:0]) then refers to the contents of the memory location at address 1234h.

### Use of the Words Set, Reset and Clear

The word *set* implies that a register bit or a condition contains a logical 1. The words re*set* or *clear* imply that a register bit or a condition contains a logical 0. When either of these terms is followed by a number, the word *logical* may not be included; however, it is implied.

### Notation for Bits and Similar Registers

A field of bits within a register is designated as: Register[*n*:*n*].

• Example: ADDR[15:0] refers to bits 15 through bit 0 of the Address.

### Use of the Terms LSB, MSB, Isb, and msb

In this document, the terms *LSB* and *MSB*, when appearing in upper case, mean *least significant byte* and *most significant byte*, respectively. The lowercase forms, *lsb* and *msb*, mean *least significant bit* and *most significant bit*, respectively.

### **Use of Initial Uppercase Letters**

Initial uppercase letters designate settings, modes, and conditions in general text.

- Example 1: Stop mode.

- Example 2: The receiver forces the SCL line to Low.

- The Master can generate a Stop condition to abort the transfer.

9

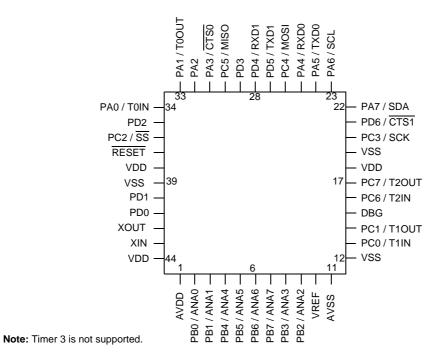

Figure 58. Z8Fxx01 in 44-Pin Low-Profile Quad Flat Package (LQFP)

## **External Pin Reset**

The  $\overline{\text{RESET}}$  pin has a Schmitt-triggered input and an internal pull-up. Once the  $\overline{\text{RESET}}$  pin is asserted, the device progresses through the Short Reset sequence. While the  $\overline{\text{RESET}}$  input pin is asserted Low, the Z8F640x family device continues to be held in the Reset state. If the  $\overline{\text{RESET}}$  pin is held Low beyond the Short Reset time-out, the device exits the Reset state immediately following  $\overline{\text{RESET}}$  pin deassertion. Following a Short Reset initiated by the external  $\overline{\text{RESET}}$  pin, the EXT status bit in the Watch-Dog Timer Control (WDTCTL) register is set to 1.

## Stop Mode Recovery

Stop mode is entered by execution of a STOP instruction by the eZ8 CPU. Refer to the **Low-Power Modes** chapter for detailed Stop mode information. During Stop Mode Recovery, the Z8F640x family device is held in reset for 514 cycles of the Watch-Dog Timer oscillator followed by 16 cycles of the system clock (crystal oscillator). Stop Mode Recovery does not affect any values in the Register File, including the Stack Pointer, Register Pointer, Flags and general-purpose RAM.

The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address. Following Stop Mode Recovery, the STOP bit in the Watch-Dog Timer Control Register is set to 1. Table 9 lists the Stop Mode Recovery sources and resulting actions. The text following provides more detailed information on each of the Stop Mode Recovery sources.

| <b>Operating Mode</b> | Stop Mode Recovery Source                                                      | Action                                                               |  |  |

|-----------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|

| Stop mode             | Watch-Dog Timer time-out<br>when configured for Reset                          | Stop Mode Recovery                                                   |  |  |

|                       | Watch-Dog Timer time-out<br>when configured for interrupt                      | Stop Mode Recovery followed by interrupt (in interrupts are enabled) |  |  |

|                       | Data transition on any GPIO Port pin<br>enabled as a Stop Mode Recovery source | Stop Mode Recovery                                                   |  |  |

## Stop Mode Recovery Using Watch-Dog Timer Time-Out

If the Watch-Dog Timer times out during Stop mode, the Z8F640x family device undergoes a STOP Mode Recovery sequence. In the Watch-Dog Timer Control register, the WDT and STOP bits are set to 1. If the Watch-Dog Timer is configured to generate an interrupt upon time-out and the device is configured to respond to interrupts, the Z8F640x family device services the Watch-Dog Timer interrupt request following the normal Stop Mode Recovery sequence.

of the port pin direction (input/output) is passed from the Port A-H Data Direction registers to the alternate function assigned to this pin. Table 11 lists the alternate functions associated with each port pin.

| Port   | Pin | Mnemonic     | Alternate Function Description                    |

|--------|-----|--------------|---------------------------------------------------|

| Port A | PA0 | TOIN         | Timer 0 Input                                     |

|        | PA1 | TOOUT        | Timer 0 Output                                    |

|        | PA2 | N/A          | No alternate function                             |

|        | PA3 | CTS0         | UART 0 Clear to Send                              |

|        | PA4 | RXD0 / IRRX0 | UART 0 / IrDA 0 Receive Data                      |

|        | PA5 | TXD0 / IRTX0 | UART 0 / IrDA 0 Transmit Data                     |

|        | PA6 | SCL          | I <sup>2</sup> C Clock (automatically open-drain) |

|        | PA7 | SDA          | I <sup>2</sup> C Data (automatically open-drain)  |

| Port B | PB0 | ANA0         | ADC Analog Input 0                                |

|        | PB1 | ANA1         | ADC Analog Input 1                                |

|        | PB2 | ANA2         | ADC Analog Input 2                                |

|        | PB3 | ANA3         | ADC Analog Input 3                                |

|        | PB4 | ANA4         | ADC Analog Input 4                                |

|        | PB5 | ANA5         | ADC Analog Input 5                                |

|        | PB6 | ANA6         | ADC Analog Input 6                                |

|        | PB7 | ANA7         | ADC Analog Input 7                                |

| Port C | PC0 | T1IN         | Timer 1 Input                                     |

|        | PC1 | T1OUT        | Timer 1 Output                                    |

|        | PC2 | SS           | SPI Slave Select                                  |

|        | PC3 | SCK          | SPI Serial Clock                                  |

|        | PC4 | MOSI         | SPI Master Out Slave In                           |

|        | PC5 | MISO         | SPI Master In Slave Out                           |

|        | PC6 | T2IN         | Timer 2 In                                        |

|        | PC7 | T2OUT        | Timer 2 Out (not available in 40-pin packages)    |

| Table 11 | . Port | Alternate | Function | Mapping |

|----------|--------|-----------|----------|---------|

|----------|--------|-----------|----------|---------|

| BITS  | 7      | 6                                                                             | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

|-------|--------|-------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|--|

| FIELD | PSMRE7 | PSMRE6                                                                        | PSMRE5 | PSMRE4 | PSMRE3 | PSMRE2 | PSMRE1 | PSMRE0 |  |  |

| RESET | 0      | 0                                                                             | 0      | 0      | 0      | 0      | 0      | 0      |  |  |

| R/W   | R/W    | R/W                                                                           | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |  |

| ADDR  |        | If 05H in Port A-H Address Register, accessible via Port A-H Control Register |        |        |        |        |        |        |  |  |

#### Table 19. Port A-H STOP Mode Recovery Source Enable Sub-Registers

PSMRE[7:0]—Port STOP Mode Recovery Source Enabled

0 = The Port pin is not configured as a STOP Mode Recovery source. Transitions on this pin during Stop mode do not initiate STOP Mode Recovery.

1 = The Port pin is configured as a STOP Mode Recovery source. Any logic transition on this pin during Stop mode initiates STOP Mode Recovery.

## Port A-H Input Data Registers

Reading from the Port A-H Input Data registers (Table 20) returns the sampled values from the corresponding port pins. The Port A-H Input Data registers are Read-only.

| BITS  | 7    | 6                                              | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|-------|------|------------------------------------------------|------|------|------|------|------|------|--|--|

| FIELD | PIN7 | PIN6                                           | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |  |  |

| RESET | Х    | Х                                              | Х    | Х    | Х    | Х    | Х    | Х    |  |  |

| R/W   | R    | R                                              | R    | R    | R    | R    | R    | R    |  |  |

| ADDR  |      | FD2H, FD6H, FDAH, FDEH, FE2H, FE6H, FEAH, FEEH |      |      |      |      |      |      |  |  |

Table 20. Port A-H Input Data Registers (PxIN)

PIN[7:0]—Port Input Data

Sampled data from the corresponding port pin input.

0 = Input data is logical 0 (Low).

1 = Input data is logical 1 (High).

- Configure the timer for Gated mode.

- Set the prescale value.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in Gated mode. After the first timer reset in Gated mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If desired, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

### Capture/Compare Mode

In Capture/Compare mode, the timer begins counting on the *first* external Timer Input transition. The desired transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent desired transition (after the first) of the Timer Input signal captures the current count value. The Capture value is written to the Timer PWM High and Low Byte Registers. When the Capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H, and counting resumes.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

The steps for configuring a timer for Capture/Compare mode and initiating the count are as follows:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for Capture/Compare mode.

- Set the prescale value.

- Set the Capture edge (rising or falling) for the Timer Input.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

- 4. If desired, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

written during counting, the 8-bit written value is placed in the counter (High or Low Byte) at the next clock edge. The counter continues counting from the new value.

BITS 7 6 5 4 3 2 1 0 TH FIELD 0 0 0 0 0 0 0 0 RESET R/W R/W R/W R/W R/W R/W R/W R/W R/W F00H, F08H, F10H, F18H ADDR

Table 38. Timer 0-3 High Byte Register (TxH)

Table 39>. Timer 0-3 Low Byte Register (TxL)

| BITS  | 7   | 6                      | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-------|-----|------------------------|-----|-----|-----|-----|-----|-----|--|--|

| FIELD |     | TL                     |     |     |     |     |     |     |  |  |

| RESET | 0   | 0                      | 0   | 0   | 0   | 0   | 0   | 1   |  |  |

| R/W   | R/W | R/W                    | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| ADDR  |     | F01H, F09H, F11H, F19H |     |     |     |     |     |     |  |  |

TH and TL—Timer High and Low Bytes

These 2 bytes, {TMRH[7:0], TMRL[7:0]}, contain the current 16-bit timer count value.

# **Timer Reload High and Low Byte Registers**

The Timer 0-3 Reload High and Low Byte (TxRH and TxRL) registers (Tables 40 and 41) store a 16-bit reload value, {TRH[7:0], TRL[7:0]}. Values written to the Timer Reload High Byte register are stored in a temporary holding register. When a write to the Timer Reload Low Byte register occurs, the temporary holding register value is written to the Timer High Byte register. This operation allows simultaneous updates of the 16-bit Timer Reload value.

In Compare mode, the Timer Reload High and Low Byte registers store the 16-bit Compare value.

In single-byte DMA transactions to the Timer Reload High Byte register, the temporary holding register is bypassed and the value is written directly to the register. If the DMA is

set to 2-byte transfers, the temporary holding register for the Timer Reload High Byte is not bypassed.

BITS 7 6 5 4 3 2 1 0 TRH FIELD 1 1 1 1 1 1 1 1 RESET R/W R/W R/W R/W R/W R/W R/W R/W R/W F02H, F0AH, F12H, F1AH ADDR

## Table 40. Timer 0-3 Reload High Byte Register (TxRH)

## Table 41. Timer 0-3 Reload Low Byte Register (TxRL)

| BITS  | 7   | 6                      | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-------|-----|------------------------|-----|-----|-----|-----|-----|-----|--|--|

| FIELD |     | TRL                    |     |     |     |     |     |     |  |  |

| RESET | 1   | 1                      | 1   | 1   | 1   | 1   | 1   | 1   |  |  |

| R/W   | R/W | R/W                    | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| ADDR  |     | F03H, F0BH, F13H, F1BH |     |     |     |     |     |     |  |  |

TRH and TRL-Timer Reload Register High and Low

These two bytes form the 16-bit Reload value, {TRH[7:0], TRL[7:0]}. This value is used to set the maximum count value which initiates a timer reload to 0001H. In Compare mode, these two byte form the 16-bit Compare value.

## **Timer 0-3 Control Registers**

The Timer 0-3 Control (TxCTL) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode.

BITS 7 4 3 2 1 0 6 5 TEN TPOL PRES TMODE FIELD 0 0 0 0 0 0 0 0 RESET R/W R/W R/W R/W R/W R/W R/W R/W R/W F07H, F0FH, F17H, F1FH ADDR

Table 44. Timer 0-3 Control Register (TxCTL)

TEN-Timer Enable

0 = Timer is disabled.

1 = Timer enabled to count.

TPOL-Timer Input/Output Polarity

Operation of this bit is a function of the current operating mode of the timer.

#### **One-Shot mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **Continuous mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

### **Counter mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **PWM mode**

0 = Timer Output is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload.

1 = Timer Output is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload.

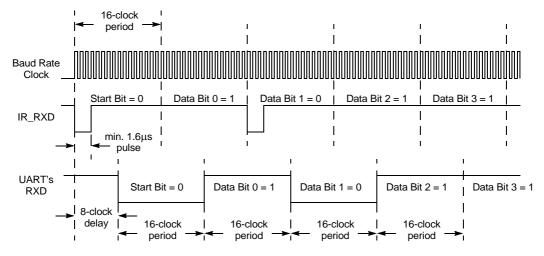

**Figure 73. Infrared Data Reception**

### Jitter

Because of the inherent sampling of the received IR\_RXD signal by the bit rate clock, some jitter can be expected on the first bit in any sequence of data. All subsequent bits in the received data stream are a fixed 16-clock periods wide.

# Infrared Encoder/Decoder Control Register Definitions

All Infrared Endec configuration and status information is set by the UART control registers as defined beginning on page 86.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART*x* Control 1 register to 1 to enable the Infrared Encoder/ Decoder *before* enabling the GPIO Port alternate function for the corresponding pin.

128

| BITS  | 7         | 6          | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------|-----------|------------|-----|-----|-----|-----|-----|-----|--|

| FIELD | DMA_START |            |     |     |     |     |     |     |  |

| RESET | Х         | Х          | Х   | Х   | Х   | Х   | Х   | Х   |  |

| R/W   | R/W       | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |  |

| ADDR  |           | FB3H, FHBH |     |     |     |     |     |     |  |

#### Table 74. DMAx Start/Current Address Low Byte Register (DMAxSTART)

DMA\_START—DMAx Start/Current Address Low

These bits, with the four lower bits of the DMA*x*\_H register, form the 12-bit Start/Current address. The full 12-bit address is given by {DMA\_START\_H[3:0], DMA\_START[7:0]}.

### DMAx End Address Low Byte Register

The DMAx End Address Low Byte register, in conjunction with the DMAx\_H register, forms a 12-bit End Address.

| BITS  | 7   | 6          | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-------|-----|------------|-----|-----|-----|-----|-----|-----|--|--|

| FIELD |     | DMA_END    |     |     |     |     |     |     |  |  |

| RESET | Х   | Х          | Х   | Х   | Х   | Х   | Х   | Х   |  |  |

| R/W   | R/W | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| ADDR  |     | FB4H, FBCH |     |     |     |     |     |     |  |  |

#### Table 75. DMAx End Address Low Byte Register (DMAxEND)

DMA\_END—DMAx End Address Low

These bits, with the four upper bits of the DMAx\_H register, form a 12-bit address. This address is the ending location of the DMAx transfer. The full 12-bit address is given by {DMA\_END\_H[3:0], DMA\_END[7:0]}.

## DMA\_ADC Address Register

The DMA\_ADC Address register points to a block of the Register File to store ADC conversion values as illustrated in Table 76. This register contains the seven most-significant bits of the 12-bit Register File addresses. The five least-significant bits are calculated from the ADC Analog Input number (5-bit base address is equal to twice the ADC Analog Input number). The 10-bit ADC conversion data is stored as two bytes with the most significant byte of the ADC data stored at the even numbered Register File address.

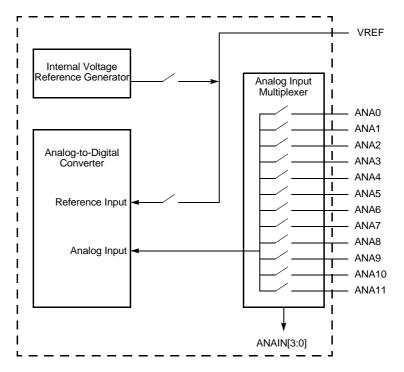

Figure 83. Analog-to-Digital Converter Block Diagram

# Operation

## **Automatic Power-Down**

If the ADC is idle (no conversions in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered-down. From this power-down state, the ADC requires 40 system clock cycles to power-up. The ADC powers up when a conversion is requested using the ADC Control register.

## **Single-Shot Conversion**

When configured for single-shot conversion, the ADC performs a single analog-to-digital conversion on the selected analog input channel. After completion of the conversion, the ADC shuts down. The steps for setting up the ADC and initiating a single-shot conversion are as follows:

# **Flash Control Register Definitions**

## **Flash Control Register**

The Flash Controller must be unlocked via the Flash Control register before programming or erasing the Flash memory. Writing the sequence 73H 8CH, sequentially, to the Flash Control register unlocks the Flash Controller. When the Flash Controller is unlocked, writing to the Flash Control register can initiate either Page Erase or Mass Erase of the Flash memory. Writing an invalid value or an invalid sequence returns the Flash Controller to its locked state. The Write-only Flash Control Register shares its Register File address with the Read-only Flash Status Register.

Table 85. Flash Control Register (FCTL)

| BITS  | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------|------|---|---|---|---|---|---|

| FIELD |      | FCMD |   |   |   |   |   |   |

| RESET | 0    | 0    | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W   | W    | W    | W | W | W | W | W | W |

| ADDR  | FF8H |      |   |   |   |   |   |   |

FCMD—Flash Command

73H = First unlock command.

8CH = Second unlock command.

95H = Page erase command (must be third command in sequence to initiate Page Erase).

63H = Mass erase command (must be third command in sequence to initiate Mass Erase).

zero). If the Z8F640x family device is not in Debug mode or if the Read Protect Option Bit is enabled, this command returns FFH for all the data values.

```

DEG <-- 09H

DEG <-- {4'h0,Register Address[11:8]

DEG <-- Register Address[7:0]

DEG <-- Size[7:0]

DEG --> 1-256 data bytes

```

• Write Program Memory (0AH)—The Write Program Memory command writes data to Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be written 1-65536 bytes at a time (65536 bytes can be written by setting size to zero). The on-chip Flash Controller must be written to and unlocked for the programming operation to occur. If the Flash Controller is not unlocked, the data is discarded. If the Z8F640x family device is not in Debug mode or if the Read Protect Option Bit is enabled, the data is discarded.

```

DBG <-- 0AH

DBG <-- Program Memory Address[15:8]

DBG <-- Program Memory Address[7:0]

DBG <-- Size[15:8]

DBG <-- Size[7:0]

DBG <-- 1-65536 data bytes

```

• **Read Program Memory (0BH)**—The Read Program Memory command reads data from Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be read 1-65536 bytes at a time (65536 bytes can be read by setting size to zero). If the Z8F640x family device is not in Debug mode or if the Read Protect Option Bit is enabled, this command returns FFH for the data.

```

DEG <-- 0BH

DEG <-- Program Memory Address[15:8]

DEG <-- Program Memory Address[7:0]

DEG <-- Size[15:8]

DEG <-- Size[7:0]

DEG --> 1-65536 data bytes

```

• Write Data Memory (0CH)—The Write Data Memory command writes data to Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be written 1-65536 bytes at a time (65536 bytes can be written by setting size to zero). If the Z8F640x family device is not in Debug mode or if the Read Protect Option Bit is enabled, the data is discarded.

```

DBG <-- 0CH

DBG <-- Data Memory Address[15:8]

DBG <-- Data Memory Address[7:0]

DBG <-- Size[15:8]

DBG <-- Size[7:0]

DBG <-- 1-65536 data bytes

```

Read Data Memory (0DH)—The Read Data Memory command reads from Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be read 1-65536 bytes at a time (65536 bytes can be read by setting size to zero). If the Z8F640x family device is not in Debug mode, this command returns FFH for the data.

```

DBG <-- ODH

DBG <-- Data Memory Address[15:8]

DBG <-- Data Memory Address[7:0]

DBG <-- Size[15:8]

DBG <-- Size[7:0]

DBG --> 1-65536 data bytes

```

• **Read Program Memory CRC (0EH)**—The Read Program Memory CRC command computes and returns the CRC (cyclic redundancy check) of Program Memory using the 16-bit CRC-CCITT polynomial. If the Z8F640x family device is not in Debug mode, this command returns FFFFH for the CRC value. Unlike most other OCD Read commands, there is a delay from issuing of the command until the OCD returns the data. The OCD reads the Program Memory, calculates the CRC value, and returns the result. The delay is a function of the Program Memory size and is approximately equal to the system clock period multiplied by the number of bytes in the Program Memory.

```

DBG <-- 0EH

DBG --> CRC[15:8]

DBG --> CRC[7:0]

```

• **Step Instruction (10H)**—The Step Instruction command steps one assembly instruction at the current Program Counter (PC) location. If the Z8F640x family device is not in Debug mode or the Read Protect Option Bit is enabled, the OCD ignores this command.

DBG <-- 10H

• **Stuff Instruction (11H)**—The Stuff Instruction command steps one assembly instruction and allows specification of the first byte of the instruction. The remaining 0-4 bytes of the instruction are read from Program Memory. This command is useful for stepping over instructions where the first byte of the instruction has been overwritten by a Breakpoint. If the Z8F640x family device is not in Debug mode or the Read Protect Option Bit is enabled, the OCD ignores this command.

```

DBG <-- 11H

DBG <-- opcode[7:0]

```

• Execute Instruction (12H)—The Execute Instruction command allows sending an entire instruction to be executed to the eZ8 CPU. This command can also step over Breakpoints. The number of bytes to send for the instruction depends on the opcode. If the Z8F640x family device is not in Debug mode or the Read Protect Option Bit is enabled, this command reads and discards one byte.

```

DBG <-- 12H

DBG <-- 1-5 byte opcode

```

|                                               | V <sub>I</sub><br>T <sub>A</sub> = | $_{\rm DD} = 3.0 - 3.0$<br>- 40 <sup>0</sup> C to 1 | .6V<br>05 <sup>0</sup> C |        |                                                                                                                                                                |  |

|-----------------------------------------------|------------------------------------|-----------------------------------------------------|--------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                                     | Minimum                            | Typical                                             | Maximum                  | Units  | Notes                                                                                                                                                          |  |

| Writes to Single Address Before<br>Next Erase | -                                  | -                                                   | 2                        |        |                                                                                                                                                                |  |

| Flash Row Program Time                        | _                                  | _                                                   | 8                        | ms     | Cumulative program time for<br>single row cannot exceed limit<br>before next erase. This parameter<br>is only an issue when bypassing<br>the Flash Controller. |  |

| Data Retention                                | 100                                | _                                                   | -                        | years  | 25 <sup>0</sup> C                                                                                                                                              |  |

| Endurance                                     | 10,000                             | _                                                   | -                        | cycles | Program / erase cycles                                                                                                                                         |  |

#### Table 104. Flash Memory Electrical Characteristics and Timing (Continued)

### Table 105. Watch-Dog Timer Electrical Characteristics and Timing

|                  |                          | $V_{DD} = 3.0 - 3.6V$<br>$T_A = -40^{0}$ C to $105^{0}$ C |         |         |       |            |

|------------------|--------------------------|-----------------------------------------------------------|---------|---------|-------|------------|

| Symbol           | Parameter                | Minimum                                                   | Typical | Maximum | Units | Conditions |

| F <sub>WDT</sub> | WDT Oscillator Frequency | 25                                                        | 50      | 100     | kHz   |            |

#### Table 106. Analog-to-Digital Converter Electrical Characteristics and Timing

|                                                                                                                       |                                    | $V_{DD} = 3.0 - 3.6V$<br>$T_A = -40^{0}$ C to $105^{0}$ C |         |         |       |                                                      |

|-----------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------------------------------------|---------|---------|-------|------------------------------------------------------|

| Symbol                                                                                                                | Parameter                          | Minimum                                                   | Typical | Maximum | Units | Conditions                                           |

|                                                                                                                       | Resolution                         | -                                                         | 10      | -       | bits  | External $V_{REF} = 3.0V$ ;<br>$R_S \ll 3.0 k\Omega$ |

|                                                                                                                       | Differential Nonlinearity<br>(DNL) | -1.0                                                      | _       | 1.0     | LSB   | External $V_{REF} = 3.0V$ ;<br>$R_S \ll 3.0 k\Omega$ |

|                                                                                                                       | Integral Nonlinearity (INL)        | -3.0                                                      | _       | 3.0     | LSB   | External $V_{REF} = 3.0V$ ;<br>$R_S \le 3.0 k\Omega$ |

|                                                                                                                       | DC Offset Error                    | -35                                                       | -       | 25      | mV    | 80-pin QFP and 64-pin LQFP packages.                 |

| <sup>1</sup> Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time. |                                    |                                                           |         |         |       |                                                      |

; value 01H, is the source. The value 01H is written into the

; Register at address 234H.

# Assembly Language Syntax

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. This binary format must be followed by users that prefer manual program coding or intend to implement their own assembler.

**Example 1**: If the contents of Registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

Table 113. Assembly Language Syntax Example 1

| Assembly Language Code | ADD | 43H, | 08H | (ADD dst, src) |

|------------------------|-----|------|-----|----------------|

| Object Code            | 04  | 08   | 43  | (OPC src, dst) |

**Example 2**: In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0 - 255 or, using Escaped Mode Addressing, a Working Register R0 - R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

Table 114. Assembly Language Syntax Example 2

| Assembly Language Code | ADD | 43H, | R8 | (ADD dst, src) |

|------------------------|-----|------|----|----------------|

| Object Code            | 04  | E8   | 43 | (OPC src, dst) |

See the device-specific Product Specification to determine the exact register file range available. The register file size varies, depending on the device type.

# eZ8 CPU Instruction Notation

In the eZ8 CPU Instruction Summary and Description sections, the operands, condition codes, status flags, and address modes are represented by a notational shorthand that is described in Table 115

## Z8F640x/Z8F480x/Z8F320x/Z8F240x/Z8F160x Z8 Encore!®

205

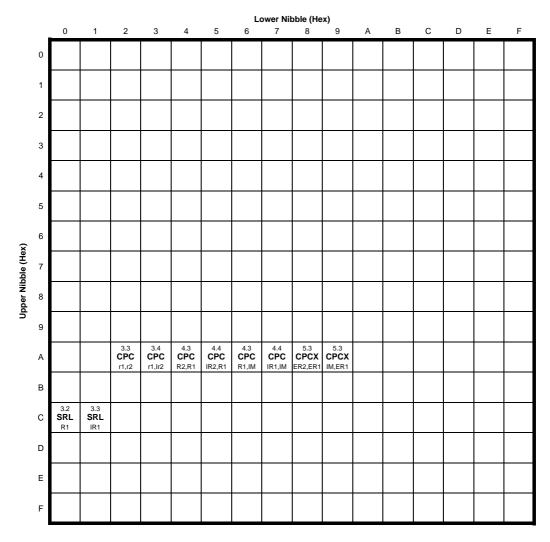

Figure 102. Second Opcode Map after 1FH

For valuable information about hardware and software development tools, visit the ZiLOG web site at <u>www.zilog.com</u>. The latest released version of ZDS can be downloaded from this site.

### **Part Number Description**

ZiLOG part numbers consist of a number of components, as indicated in the following examples:

| ZiLOG Base Products |                                     |  |  |  |

|---------------------|-------------------------------------|--|--|--|

| Z8                  | ZiLOG 8-bit microcontroller product |  |  |  |

| F6                  | Flash Memory                        |  |  |  |

| 64                  | Program Memory Size                 |  |  |  |

| 01                  | Device Number                       |  |  |  |

| А                   | Package                             |  |  |  |

| Ν                   | Pin Count                           |  |  |  |

| 020                 | Speed                               |  |  |  |

| S                   | Temperature Range                   |  |  |  |

| С                   | Environmental Flow                  |  |  |  |

| Packages                  | A = LQFP                                      |

|---------------------------|-----------------------------------------------|

| 0                         | S = SOIC                                      |

|                           | H = SSOP                                      |

|                           | P = PDIP                                      |

|                           | V = PLCC                                      |

|                           | $\mathbf{F} = \mathbf{Q}\mathbf{F}\mathbf{P}$ |

| Pin Count                 | H = 20 pins                                   |

|                           | J = 28 pins                                   |

|                           | M = 40 pins                                   |

|                           | N = 44 pins                                   |

|                           | R = 64 pins                                   |

|                           | S = 68 pins                                   |

|                           | T = 80 pins                                   |

| Speed                     | 020 = 20MHz                                   |

| Temperature               | $S = 0^{\circ}C$ to $+70^{\circ}C$            |

| •                         | $E = -40^{\circ}C$ to $+105^{\circ}C$         |

| <b>Environmental Flow</b> | C = Plastic-Standard                          |

Example: Part number Z8F06401AN020SC is an 8-bit microcontroller product in an LQFP package, using 44 pins, operating with a maximum 20MHz external clock frequency over a 0°C to +70°C temperature range and built using the Plastic-Standard environmental flow.