#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |

| Number of I/O              | 60                                                        |

| Program Memory Size        | 48KB (48K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 4K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | A/D 12x10b                                                |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 80-BQFP                                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f4803ft020sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

out, first set the TPOL bit in the Timer Control Register to the start value before beginning One-Shot mode. Then, after starting the timer, set TPOL to the opposite bit value.

The steps for configuring a timer for One-Shot mode and initiating the count are as follows:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for One-Shot mode.

- Set the prescale value.

- If using the Timer Output alternate function, set the initial output level (High or Low).

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If desired, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer and initiate counting.

In One-Shot mode, the system clock always provides the timer input. The timer period is given by the following equation:

## One-Shot Mode Time-Out Period (s) = (Reload Value – Start Value) × Prescale System Clock Frequency (Hz)

#### **Continuous Mode**

In Continuous mode, the timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) upon timer Reload.

The steps for configuring a timer for Continuous mode and initiating the count are as follows:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for Continuous mode.

- Set the prescale value.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control register to enable the timer.

- 7. Counting begins on the first appropriate transition of the Timer Input signal. No interrupt is generated by this first edge.

In Capture/Compare mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) = (Capture Value – Start Value) × Prescale System Clock Frequency (Hz)

#### **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte register is read, the contents of the Timer Low Byte register are placed in a holding register. A subsequent read from the Timer Low Byte register returns the value in the holding register. This operation allows accurate reads of the full 16-bit timer count value while enabled. When the timers are not enabled, a read from the Timer Low Byte register returns the actual value in the counter.

#### **Timer Output Signal Operation**

Timer Output is a GPIO Port pin alternate function. Generally, the Timer Output is toggled every time the counter is reloaded.

## **Timer Control Register Definitions**

Timers 0–2 are available in all packages. Timer 3 is available only in the 64-, 68- and 80-pin packages.

#### Timer 0-3 High and Low Byte Registers

The Timer 0-3 High and Low Byte (TxH and TxL) registers (Tables 38 and 39) contain the current 16-bit timer count value. When the timer is enabled, a read from TxH causes the value in TxL to be stored in a temporary holding register. A read from TMRL always returns this temporary register when the timers are enabled. When the timer is disabled, reads from the TMRL reads the register directly.

Writing to the Timer High and Low Byte registers while the timer is enabled is not recommended. There are no temporary holding registers available for write operations, so simultaneous 16-bit writes are not possible. If either the Timer High or Low Byte registers are

## **Timer 0-3 Control Registers**

The Timer 0-3 Control (TxCTL) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode.

BITS 7 4 3 2 1 0 6 5 TEN TPOL PRES TMODE FIELD 0 0 0 0 0 0 0 0 RESET R/W R/W R/W R/W R/W R/W R/W R/W R/W F07H, F0FH, F17H, F1FH ADDR

Table 44. Timer 0-3 Control Register (TxCTL)

TEN-Timer Enable

0 = Timer is disabled.

1 = Timer enabled to count.

TPOL-Timer Input/Output Polarity

Operation of this bit is a function of the current operating mode of the timer.

#### **One-Shot mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **Continuous mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **Counter mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **PWM mode**

0 = Timer Output is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload.

1 = Timer Output is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload.

information on approximate time-out delays for the minimum and maximum WDT reload values.

Table 45. Watch-Dog Timer Approximate Time-Out Delays

| WDT Reload Value | WDT Reload Value | * *    | te Time-Out Delay<br>WDT oscillator frequency) |

|------------------|------------------|--------|------------------------------------------------|

| (Hex)            | ex) (Decimal)    |        | Description                                    |

| 000004           | 4                | 80µs   | Minimum time-out delay                         |

| FFFFFF           | 16,777,215       | 335.5s | Maximum time-out delay                         |

#### Watch-Dog Timer Refresh

When first enabled, the Watch-Dog Timer is loaded with the value in the Watch-Dog Timer Reload registers. The Watch-Dog Timer then counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the downcounter to be reloaded with the WDT Reload value stored in the Watch-Dog Timer Reload registers. Counting resumes following the reload operation.

When the Z8F640x family device is operating in Debug Mode (via the On-Chip Debugger), the Watch-Dog Timer is continuously refreshed to prevent spurious Watch-Dog Timer time-outs.

### Watch-Dog Timer Time-Out Response

The Watch-Dog Timer times out when the counter reaches 000000H. A time-out of the Watch-Dog Timer generates either an interrupt or a Short Reset. The WDT\_RES Option Bit determines the time-out response of the Watch-Dog Timer. Refer to the **Option Bits** chapter for information regarding programming of the WDT\_RES Option Bit.

#### WDT Interrupt in Normal Operation

If configured to generate an interrupt when a time-out occurs, the Watch-Dog Timer issues an interrupt request to the interrupt controller and sets the WDT status bit in the Watch-Dog Timer Control register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watch-Dog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watch-Dog Timer counter rolls over to its maximum value of FFFFFH and continues counting. The Watch-Dog Timer counter is not automatically returned to its Reload Value.

#### WDT Interrupt in Stop Mode

If configured to generate an interrupt when a time-out occurs and the Z8F640x family device is in STOP mode, the Watch-Dog Timer automatically initiates a STOP Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Watch-Dog Timer Control register are set to 1 following WDT time-out in STOP

mode. Refer to the **Reset and Stop Mode Recovery** chapter for more information on STOP Mode Recovery.

If interrupts are enabled, following completion of the Stop Mode Recovery the eZ8 CPU responds to the interrupt request by fetching the Watch-Dog Timer interrupt vector and executing code from the vector address.

#### WDT Reset in Normal Operation

If configured to generate a Reset when a time-out occurs, the Watch-Dog Timer forces the Z8F640x family device into the Short Reset state. The WDT status bit in the Watch-Dog Timer Control register is set to 1. Refer to the **Reset and Stop Mode Recovery** chapter for more information on Short Reset.

#### WDT Reset in Stop Mode

If configured to generate a Reset when a time-out occurs and the Z8F640x family device is in STOP mode, the Watch-Dog Timer initiates a Stop Mode Recovery. Both the WDT status bit and the STOP bit in the Watch-Dog Timer Control register are set to 1 following WDT time-out in STOP mode. Refer to the **Reset and Stop Mode Recovery** chapter for more information.

#### Watch-Dog Timer Reload Unlock Sequence

Writing the unlock sequence to the Watch-Dog Timer Control register (WDTCTL) unlocks the three Watch-Dog Timer Reload Byte registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL register address produce no effect on the bits in the WDTCTL register. The locking mechanism prevents spurious writes to the Reload registers. The follow sequence is required to unlock the Watch-Dog Timer Reload Byte registers (WDTU, WDTH, and WDTL) for write access.

- 1. Write 55H to the Watch-Dog Timer Control register (WDTCTL)

- 2. Write AAH to the Watch-Dog Timer Control register (WDTCTL)

- 3. Write the Watch-Dog Timer Reload Upper Byte register (WDTU)

- 4. Write the Watch-Dog Timer Reload High Byte register (WDTH)

- 5. Write the Watch-Dog Timer Reload Low Byte register (WDTL)

All three Watch-Dog Timer Reload registers must be written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur, unless the sequence is restarted. The value in the Watch-Dog Timer Reload registers is loaded into the counter when the Watch-Dog Timer is first enabled and every time a WDT instruction is executed.

0 = No parity error has occurred.

1 = A parity error has occurred.

#### OE—Overrun Error

This bit indicates that an overrun error has occurred. An overrun occurs when new data is received and the UART Receive Data register has not been read. If the RDA bit is reset to 0, then reading the UART Receive Data register clears this bit.

0 = No overrun error occurred.

1 = An overrun error occurred.

FE—Framing Error

This bit indicates that a framing error (no Stop bit following data reception) was detected. Reading the UART Receive Data register clears this bit.

0 = No framing error occurred.

1 = A framing error occurred.

#### BRKD—Break Detect

This bit indicates that a break occurred. If the data bits, parity/multiprocessor bit, and Stop bit(s) are all zeros then this bit is set to 1. Reading the UART Receive Data register clears this bit.

0 = No break occurred.

1 = A break occurred.

#### TDRE—Transmitter Data Register Empty

This bit indicates that the UART Transmit Data register is empty and ready for additional data. Writing to the UART Transmit Data register resets this bit.

0 = Do not write to the UART Transmit Data register.

1 = The UART Transmit Data register is ready to receive an additional byte to be transmitted.

#### TXE—Transmitter Empty

This bit indicates that the transmit shift register is empty and character transmission is finished.

0 = Data is currently transmitting.

1 = Transmission is complete.

CTS—CTS signal

When this bit is read it returns the level of the  $\overline{\text{CTS}}$  signal.

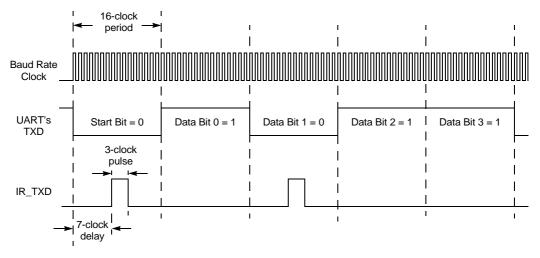

Figure 72. Infrared Data Transmission

#### **Receiving IrDA Data**

Data received from the infrared transceiver via the IR\_RXD signal through the RXD pin is decoded by the Infrared Endec and passed to the UART. The UART's baud rate clock is used by the Infrared Endec to generate the demodulated signal (RXD) that drives the UART. Each UART/Infrared data bit is 16-clocks wide. Figure 73 illustrates data reception. When the Infrared Endec is enabled, the UART's RXD signal is internal to the Z8F640x family device while the IR\_RXD signal is received through the RXD pin.

99

ZiLOG

# Serial Peripheral Interface

## Overview

The Serial Peripheral Interface<sup>™</sup> (SPI) is a synchronous interface allowing several SPItype devices to be interconnected. SPI-compatible devices include EEPROMs, Analog-to-Digital Converters, and ISDN devices. Features of the SPI include:

- Full-duplex, synchronous, character-oriented communication

- Four-wire interface

- Data transfers rates up to a maximum of one-fourth the system clock frequency

- Error detection

- Write and mode collision detection

- Dedicated Baud Rate Generator

## Architecture

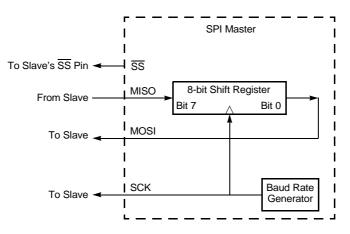

The SPI may be configured as either a Master (in single or multi-master systems) or a Slave as illustrated in Figures 74 through 76.

Figure 74. SPI Configured as a Master in a Single Master, Single Slave System

#### START-Send Start Condition

This bit sends the Start condition. Once asserted, it is cleared by the I<sup>2</sup>C Controller after it sends the START condition or by deasserting the IEN bit. After this bit is set, the Start condition is sent if there is data in the I<sup>2</sup>C Data or I<sup>2</sup>C Shift register. If there is no data in one of these registers, the I<sup>2</sup>C Controller waits until data is loaded. If this bit is set while the I<sup>2</sup>C Controller is shifting out data, it generates a START condition after the byte shifts and the acknowledge phase completed. If the STOP bit is also set, it also waits until the STOP condition is sent before the START condition. If this bit is 1, it cannot be cleared to 0 by writing to the register. This bit clears when the I<sup>2</sup>C is disabled.

#### STOP-Send Stop Condition

This bit causes the  $I^2C$  Controller to issue a Stop condition after the byte in the  $I^2C$  Shift register has completed transmission or after a byte has been received in a receive operation. Once set, this bit is reset by the  $I^2C$  Controller after a Stop condition has been sent or by deasserting the IEN bit. If this bit is 1, it cannot be cleared to 0 by writing to the register. This bit clears when the  $I^2C$  is disabled.

#### BIRQ-Baud Rate Generator Interrupt Request

This bit causes an interrupt to occur every time the baud rate generator counts down to zero. This bit allows the  $I^2C$  Controller to be used as an additional counter when it is not being used elsewhere. This bit must only be set when the  $I^2C$  Controller is disabled.

#### TXI-Enable TDRE interrupts

This bit enables interrupts when the I<sup>2</sup>C Data register is empty on the I<sup>2</sup>C Controller.

#### NAK—Send NAK

This bit sends a Not Acknowledge condition after the next byte of data has been read from the  $I^2C$  slave. Once asserted, it is deasserted after a Not Acknowledge is sent or the IEN bit is deasserted.

#### FLUSH-Flush Data

Setting this bit to 1 clears the I<sup>2</sup>C Data register and sets the TDRE bit to 1. This bit allows flushing of the I<sup>2</sup>C Data register when an NAK is received after the data has been sent to the I<sup>2</sup>C Data register. Reading this bit always returns 0.

### FILTEN—I<sup>2</sup>C Signal Filter Enable

Setting this bit to 1 enables low-pass digital filters on the SDA and SCL input signals. These filters reject any input pulse with periods less than a full system clock cycle. The filters introduce a 3-system clock cycle latency on the inputs.

## Configuring DMA0 and DMA1 for Data Transfer

Follow these steps to configure and enable DMA0 or DMA1:

- 1. Write to the DMAx I/O Address register to set the Register File address identifying the on-chip peripheral control register. The upper nibble of the 12-bit address for on-chip peripheral control registers is always FH. The full address is {FH, DMAx\_IO[7:0]}

- 2. Determine the 12-bit Start and End Register File addresses. The 12-bit Start Address is given by {DMAx\_H[3:0], DMA\_START[7:0]}. The 12-bit End Address is given by {DMAx\_H[7:4], DMA\_END[7:0]}.

- 3. Write the Start and End Register File address high nibbles to the DMAx End/Start Address High Nibble register.

- 4. Write the lower byte of the Start Address to the DMAx Start/Current Address register.

- 5. Write the lower byte of the End Address to the DMAx End Address register.

- 6. Write to the DMAx Control register to complete the following:

- Select loop or single-pass mode operation

- Select the data transfer direction (either from the Register File RAM to the onchip peripheral control register; or from the on-chip peripheral control register to the Register File RAM)

- Enable the DMAx interrupt request, if desired

- Select Word or Byte mode

- Select the DMAx request trigger

- Enable the DMAx channel

#### **DMA\_ADC** Operation

DMA\_ADC transfers data from the ADC to the Register File. The sequence of operations in a DMA\_ADC data transfer is:

- 1. ADC completes conversion on the current ADC input channel and signals the DMA controller that two-bytes of ADC data are ready for transfer.

- 2. DMA\_ADC requests control of the system bus (address and data) from the eZ8 CPU.

- 3. After the eZ8 CPU acknowledges the bus request, DMA\_ADC transfers the two-byte ADC output value to the Register File and then returns system bus control back to the eZ8 CPU.

- 4. If the current ADC Analog Input is the highest numbered input to be converted:

- DMA\_ADC resets the ADC Analog Input number to 0 and initiates data conversion on ADC Analog Input 0.

- If configured to generate an interrupt, DMA\_ADC sends an interrupt request to the Interrupt Controller

## Flash Operation Timing Using the Flash Frequency Registers

Before performing either a program or erase operation on the Flash memory, the user must first configure the Flash Frequency High and Low Byte registers. The Flash Frequency registers allow programming and erasure of the Flash with system clock frequencies ranging from 32KHz (32768Hz) through 20MHz.

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz). This value is calculated using the following equation:.

FFREQ[15:0] = System Clock Frequency (Hz) 1000

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 32KHz (32768Hz) or above 20MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to insure proper operation of the Z8F640x family device.

### Flash Code Protection Against External Access

The user code contained within the Z8F640x family device's Flash memory can be protected against external access via the On-Chip Debugger. Programming the RP Option Bit prevents reading of the user code through the On-Chip Debugger. Refer to the **Option Bits** chapter and the **On-Chip Debugger** chapter for more information.

### Flash Code Protection Against Accidental Program and Erasure

The Z8F640x family device provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by a combination of the Option bits and the locking mechanism of the Flash Controller.

157

| Debug Command           | Command Byte | Enabled when NOT in Debug mode? | Disabled by<br>Read Protect Option Bit |

|-------------------------|--------------|---------------------------------|----------------------------------------|

| Write Program Memory    | 0AH          | -                               | Disabled                               |

| Read Program Memory     | 0BH          | -                               | Disabled                               |

| Write Data Memory       | 0CH          | -                               | Yes                                    |

| Read Data Memory        | 0DH          | -                               | -                                      |

| Read Program Memory CRC | 0EH          | -                               | -                                      |

| Reserved                | 0FH          | -                               | -                                      |

| Step Instruction        | 10H          | -                               | Disabled                               |

| Stuff Instruction       | 11H          | -                               | Disabled                               |

| Execute Instruction     | 12H          | -                               | Disabled                               |

| Reserved                | 13H - 1FH    | -                               | -                                      |

| Write Watchpoint        | 20H          | -                               | Disabled                               |

| Read Watchpoint         | 21H          | -                               | -                                      |

| Reserved                | 22H - FFH    | -                               | -                                      |

#### **Table 93. On-Chip Debugger Commands**

In the following bulleted list of OCD Commands, data and commands sent from the host to the On-Chip Debugger are identified by 'DBG <-- Command/Data'. Data sent from the On-Chip Debugger back to the host is identified by 'DBG --> Data'

Read OCD Revision (00H)—The Read OCD Revision command is used to determine the version of the On-Chip Debugger. If OCD commands are added, removed, or changed, this revision number changes.

```

DEG <-- 00H

DEG --> OCDREV[15:8] (Major revision number)

DEG --> OCDREV[7:0] (Minor revision number)

```

• **Read OCD Status Register (02H)**—The Read OCD Status Register command is used to read the OCDSTAT register.

```

DBG <-- 02H

DBG --> OCDSTAT[7:0]

```

• **Read Runtime Counter (03H)**—The Runtime Counter is used to count Z8 Encore! system clock cycles in between Breakpoints. The 16-bit Runtime Counter counts up from 0000H and stops at the maximum count of FFFFH. The Runtime Counter is overwritten during the Write Memory, Read Memory, Write Register, Read Register, Read Memory CRC, Step Instruction, Stuff Instruction, and Execute Instruction commands.

## **On-Chip Oscillator**

The Z8F640x family devices feature an on-chip oscillator for use with an external 1-20MHz crystal. This oscillator generates the primary system clock for the internal eZ8 CPU and the majority of the on-chip peripherals. Alternatively, the X<sub>IN</sub> input pin can also accept a CMOS-level clock input signal (32kHz-20MHz). If an external clock generator is used, the X<sub>OUT</sub> pin must be left unconnected. The Z8F640x family device does *not* contain in internal clock divider. The frequency of the signal on the X<sub>IN</sub> input pin determines the frequency of the system clock. The Z8F640x family device on-chip oscillator does not support external RC networks or ceramic resonators.

## 20MHz Crystal Oscillator Operation

Figure 90 illustrates a recommended configuration for connection with an external 20MHz, fundamental-mode, parallel-resonant crystal. Recommended crystal specifications are provided in Table 99. Resistor R<sub>1</sub> limits total power dissipation by the crystal. Printed circuit board layout should add no more than 4pF of stray capacitance to either the X<sub>IN</sub> or X<sub>OUT</sub> pins. If oscillation does not occur, reduce the values of capacitors C<sub>1</sub> and C<sub>2</sub> to decrease loading.

180

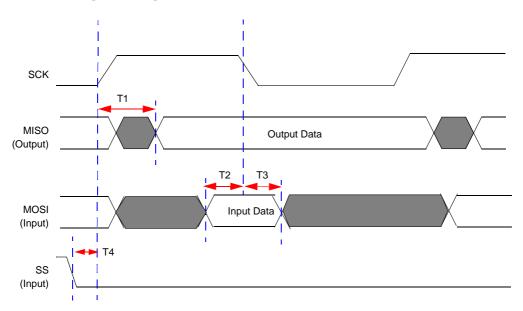

## **SPI Slave Mode Timing**

Figure 97 and Table 111 provide timing information for the SPI slave mode pins. Timing is shown with SCK rising edge used to source MISO output data, SCK falling edge used to sample MOSI input data.

#### Figure 97. SPI Slave Mode Timing

Table 111. SPI Slave Mode Timing

|                |                                                | Dela              | Delay (ns)                     |  |  |  |

|----------------|------------------------------------------------|-------------------|--------------------------------|--|--|--|

| Parameter      | Abbreviation                                   | Minimum           | Maximum                        |  |  |  |

| T <sub>1</sub> | SCK (transmit edge) to MISO output Valid Delay | 2 * Xin<br>period | 3 * Xin<br>period + 20<br>nsec |  |  |  |

| T <sub>2</sub> | MOSI input to SCK (receive edge) Setup Time    | 0                 |                                |  |  |  |

| T <sub>3</sub> | MOSI input to SCK (receive edge) Hold Time     | 3 * Xin<br>period |                                |  |  |  |

| T <sub>4</sub> | SS input assertion to SCK setup                | 1 * Xin<br>period |                                |  |  |  |

## **Opcode** Maps

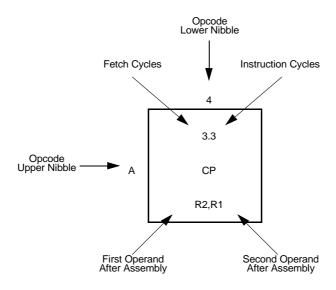

Figures 101 and 102 provide information on each of the eZ8 CPU instructions. A description of the opcode map data and the abbreviations are provided in Figure 100 and Table 127.

Figure 100. Opcode Map Cell Description

| Abbreviation | Description                        | Abbreviation                                   | Description            |

|--------------|------------------------------------|------------------------------------------------|------------------------|

| b            | Bit position                       | IRR                                            | Indirect Register Pair |

| сс           | Condition code                     | р                                              | Polarity (0 or 1)      |

| Х            | 8-bit signed index or displacement | r                                              | 4-bit Working Register |

| DA           | Destination address                | R                                              | 8-bit register         |

| ER           | Extended Addressing register       | r1, R1, Ir1, Irr1, IR1, rr1,<br>RR1, IRR1, ER1 | Destination address    |

| IM           | Immediate data value               | r2, R2, Ir2, Irr2, IR2, rr2,<br>RR2, IRR2, ER2 | Source address         |

| Ir           | Indirect Working Register          | RA                                             | Relative               |

| IR           | Indirect register                  | rr                                             | Working Register Pair  |

| Irr          | Indirect Working Register Pair     | RR                                             | Register Pair          |

## Table 127. Opcode Map Abbreviations

## Z8F640x/Z8F480x/Z8F320x/Z8F240x/Z8F160x Z8 Encore!®

204

|                           |                          |                     |                                  |                                     |                                     |                                  | Le                                  | ower Nil                       | ble (He                | x)                    |                     |                   |                    |                           |                  |                          |

|---------------------------|--------------------------|---------------------|----------------------------------|-------------------------------------|-------------------------------------|----------------------------------|-------------------------------------|--------------------------------|------------------------|-----------------------|---------------------|-------------------|--------------------|---------------------------|------------------|--------------------------|

|                           | 0                        | 1                   | 2                                | 3                                   | 4                                   | 5                                | 6                                   | 7                              | 8                      | 9                     | А                   | В                 | С                  | D                         | Е                | F                        |

| 0                         | 1.2<br>BRK               | 2.2<br>SRP<br>IM    | 2.3<br>ADD<br>r1,r2              | 2.4<br>ADD<br>r1,lr2                | 3.3<br>ADD<br>R2,R1                 | 3.4<br>ADD<br>IR2,R1             | 3.3<br>ADD<br>R1,IM                 | 3.4<br>ADD<br>IR1,IM           | 4.3<br>ADDX<br>ER2,ER1 | 4.3<br>ADDX<br>IM,ER1 | 2.3<br>DJNZ<br>r1,X | 2.2<br>JR<br>cc,X | 2.2<br>LD<br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br>INC<br>r1 | 1.2<br>NOP               |

| 1                         | 2.2<br>RLC<br>R1         | 2.3<br>RLC<br>IR1   | 2.3<br>ADC<br>r1,r2              | 2.4<br>ADC<br>r1,lr2                | 3.3<br>ADC<br>R2,R1                 | 3.4<br>ADC<br>IR2,R1             | 3.3<br>ADC<br>R1,IM                 | 3.4<br>ADC<br>IR1,IM           | 4.3<br>ADCX<br>ER2,ER1 | 4.3<br>ADCX<br>IM,ER1 |                     |                   |                    |                           |                  | See 2nd<br>Opcode<br>Map |

| 2                         | 2.2<br>INC<br>R1         | 2.3<br>INC<br>IR1   | 2.3<br>SUB<br>r1,r2              | 2.4<br>SUB<br>r1,lr2                | 3.3<br>SUB<br>R2,R1                 | 3.4<br>SUB<br>IR2,R1             | 3.3<br>SUB<br>R1,IM                 | 3.4<br>SUB<br>IR1,IM           | 4.3<br>SUBX<br>ER2,ER1 | 4.3<br>SUBX<br>IM,ER1 |                     |                   |                    |                           |                  |                          |

| 3                         | 2.2<br>DEC<br>R1         | 2.3<br>DEC<br>IR1   | 2.3<br>SBC<br>r1,r2              | 2.4<br>SBC<br>r1,lr2                | 3.3<br>SBC<br>R2,R1                 | 3.4<br>SBC<br>IR2,R1             | 3.3<br>SBC<br>R1,IM                 | 3.4<br>SBC<br>IR1,IM           | 4.3<br>SBCX<br>ER2,ER1 | 4.3<br>SBCX           |                     |                   |                    |                           |                  |                          |

| 4                         | 2.2<br>DA<br>R1          | 2.3<br>DA<br>IR1    | 2.3<br>OR<br>r1,r2               | 2.4<br>OR<br>r1,lr2                 | 3.3<br>OR                           | 3.4<br>OR<br>IR2,R1              | 3.3<br>OR                           | 3.4<br>OR<br>IR1,IM            | 4.3<br>ORX<br>ER2,ER1  | 4.3<br>ORX<br>IM,ER1  |                     |                   |                    |                           |                  |                          |

| 5                         | 2.2<br>POP               | 2.3<br>POP<br>IR1   | 2.3<br>AND<br>r1,r2              | 2.4<br>AND<br>r1,lr2                | R2,R1<br>3.3<br><b>AND</b><br>R2,R1 | 3.4<br>AND<br>IR2,R1             | R1,IM<br>3.3<br><b>AND</b><br>R1,IM | 3.4<br>AND<br>IR1,IM           | 4.3<br>ANDX<br>ER2,ER1 | 4.3<br>ANDX<br>IM,ER1 |                     |                   |                    |                           |                  | 1.2<br>WDT               |

| 6                         | R1<br>2.2<br>COM<br>R1   | 2.3<br>COM<br>IR1   | 2.3<br>TCM<br>r1,r2              | 2.4<br>TCM<br>r1,lr2                | 3.3<br>TCM<br>R2,R1                 | 3.4<br>TCM<br>IR2,R1             | 3.3<br>TCM<br>R1,IM                 | 3.4<br>TCM<br>IR1,IM           | 4.3<br>TCMX<br>ER2,ER1 | 4.3<br>TCMX<br>IM,ER1 |                     |                   |                    |                           |                  | STOP                     |

| XeH) ol                   | 2.2<br>PUSH              | 2.3<br>PUSH<br>IR2  | 2.3<br>TM                        | 2.4<br>TM                           | 3.3<br>TM                           | 3.4<br>TM                        | 3.3<br>TM                           | 3.4<br>TM                      | 4.3<br>TMX             | 4.3<br>TMX            |                     |                   |                    |                           |                  | 1.2<br>HALT              |

| Upper Nibble (Hex)<br>8 2 | R2<br>2.5<br>DECW<br>RR1 | 2.6<br>DECW<br>IRR1 | r1,r2<br>2.5<br>LDE              | r1,lr2<br>2.9<br>LDEI               | 82,R1<br>3.2<br>LDX                 | 3.3<br>LDX                       | 81,IM<br>3.4<br>LDX                 | 3.5<br>LDX                     | 3.4<br>LDX             | 3.4<br>LDX            |                     |                   |                    |                           |                  | 1.2<br>DI                |

| <b>1</b><br>9             | 2.2<br>RL<br>R1          | 2.3<br>RL<br>IR1    | r1,Irr2<br>2.5<br>LDE<br>r2,Irr1 | 1r1,1rr2<br>2.9<br>LDEI<br>1r2,1rr1 | r1,ER2<br>3.2<br>LDX<br>r2,ER1      | 1r1,ER2<br>3.3<br>LDX<br>Ir2,ER1 | 3.4<br>LDX                          | 3.5<br>LDX<br>IR2,IRR1         | r1,rr2,X<br>3.3<br>LEA | 3.5<br>LEA            |                     |                   |                    |                           |                  | 1.2<br>El                |

| A                         | 2.5<br>INCW              | 2.6<br>INCW         | 2.3<br>CP                        | 2.4<br>CP                           | 3.3<br>CP                           | 3.4<br>CP                        | 3.3<br>CP                           | 3.4<br>CP                      | r1,r2,X<br>4.3<br>CPX  | 4.3<br>CPX            |                     |                   |                    |                           |                  | 1.4<br>RET               |

| В                         | 2.2<br>CLR               | 2.3<br>CLR<br>IR1   | r1,r2<br>2.3<br>XOR              | r1,lr2<br>2.4<br>XOR                | 82,R1<br>3.3<br>XOR                 | 3.4<br>XOR                       | 81,IM<br>3.3<br><b>XOR</b>          | 3.4<br>XOR                     | 4.3<br>XORX            | 4.3<br>XORX           |                     |                   |                    |                           |                  | 1.5<br>IRET              |

| С                         | R1<br>2.2<br>RRC<br>R1   | 2.3<br>RRC<br>IR1   | r1,r2<br>2.5<br>LDC<br>r1,lrr2   | r1,lr2<br>2.9<br>LDCI<br>lr1,lrr2   | R2,R1<br>2.3<br>JP<br>IRR1          | 2.9<br>LDC                       | R1,IM                               | IR1,IM<br>3.3<br>LD<br>r1,r2,X | 3.2<br>PUSHX<br>ER2    | IM,ER1                |                     |                   |                    |                           |                  | 1.2<br>RCF               |

| D                         | 2.2<br>SRA<br>R1         | 2.3<br>SRA<br>IR1   | 2.5<br>LDC<br>r2,lrr1            | 2.9<br>LDCI<br>Ir2,Irr1             | 2.6                                 | Ir1,Irr2<br>2.2<br>BSWAP<br>R1   | 3.3<br>CALL<br>DA                   | 3.4<br>LD<br>r2,r1,X           | 3.2<br>POPX<br>ER1     |                       |                     |                   |                    |                           |                  | 1.2<br>SCF               |

| E                         | 2.2<br>RR                | 2.3<br>RR<br>IR1    | 2.2<br>BIT                       | 2.3<br>LD                           | 3.2<br>LD<br>R2,R1                  | 3.3<br>LD<br>IR2,R1              | 3.2<br>LD<br>R1,IM                  | 3.3<br>LD<br>IR1,IM            | 4.2<br>LDX<br>ER2,ER1  | 4.2<br>LDX<br>IM,ER1  |                     |                   |                    |                           |                  | 1.2<br>CCF               |

| F                         | R1<br>2.2<br>SWAP<br>R1  | 2.3<br>SWAP<br>IR1  | p,b,r1<br>2.6<br>TRAP<br>Vector  | r1,lr2<br>2.3<br>LD<br>lr1,r2       | 2.8<br>MULT<br>RR1                  | 3.3<br>LD<br>R2,IR1              | 3.3<br>BTJ                          | 3.4<br>BTJ<br>p,b,lr1,X        | EKZ,EK1                | IIVI,EK1              | ┥┥                  | V                 |                    |                           |                  |                          |

Figure 101. First Opcode Map

# **Ordering Information**

| Part                                              | Flash<br>KB (Bytes) | RAM<br>KB (Bytes) | Max. Speed<br>(MHz) | Temp<br>( <sup>0</sup> C) | Voltage<br>(V) | Package | Part Number    |  |  |  |  |

|---------------------------------------------------|---------------------|-------------------|---------------------|---------------------------|----------------|---------|----------------|--|--|--|--|

| Z8 Encore!® with 16KB Flash, Standard Temperature |                     |                   |                     |                           |                |         |                |  |  |  |  |

| Z8 Encore!®                                       | 16 (16,384)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PDIP-40 | Z8F1601PM020SC |  |  |  |  |

| Z8 Encore!®                                       | 16 (16,384)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-44 | Z8F1601AN020SC |  |  |  |  |

| Z8 Encore!®                                       | 16 (16,384)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-44 | Z8F1601VN020SC |  |  |  |  |

| Z8 Encore!®                                       | 16 (16,384)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-64 | Z8F1602AR020SC |  |  |  |  |

| Z8 Encore!®                                       | 16 (16,384)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-68 | Z8F1602VS020SC |  |  |  |  |

| Z8 Encore!®                                       | with 24KB           | Flash, Stand      | lard Tempera        | ture                      |                |         |                |  |  |  |  |

| Z8 Encore!®                                       | 24 (24,576)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PDIP-40 | Z8F2401PM020SC |  |  |  |  |

| Z8 Encore!®                                       | 24 (24,576)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-44 | Z8F2401AN020SC |  |  |  |  |

| Z8 Encore!®                                       | 24 (24,576)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-44 | Z8F2401VN020SC |  |  |  |  |

| Z8 Encore!®                                       | 24 (24,576)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-64 | Z8F2402AR020SC |  |  |  |  |

| Z8 Encore!®                                       | 24 (24,576)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-68 | Z8F2402VS020SC |  |  |  |  |

| Z8 Encore!®                                       | with 32KB           | Flash, Stand      | lard Tempera        | ture                      |                |         |                |  |  |  |  |

| Z8 Encore!®                                       | 32 (32,768)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PDIP-40 | Z8F3201PM020SC |  |  |  |  |

| Z8 Encore!®                                       | 32 (32,768)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-44 | Z8F3201AN020SC |  |  |  |  |

| Z8 Encore!®                                       | 32 (32,768)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-44 | Z8F3201VN020SC |  |  |  |  |

| Z8 Encore!®                                       | 32 (32,768)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-64 | Z8F3202AR020SC |  |  |  |  |

| Z8 Encore!®                                       | 32 (32,768)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-68 | Z8F3202VS020SC |  |  |  |  |

| Z8 Encore!®                                       | with 48KB           | Flash, Stand      | ard Temperat        | ure                       |                |         |                |  |  |  |  |

| Z8 Encore!®                                       | 48 (49,152)         | 4 (4096)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PDIP-40 | Z8F4801PM020SC |  |  |  |  |

| Z8 Encore!®                                       | 48 (49,152)         | 4 (4096)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-44 | Z8F4801AN020SC |  |  |  |  |

| Z8 Encore!®                                       | 48 (49,152)         | 4 (4096)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-44 | Z8F4801VN020SC |  |  |  |  |

| Z8 Encore!®                                       | 48 (49,152)         | 4 (4096)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-64 | Z8F4802AR020SC |  |  |  |  |

| Z8 Encore!®                                       | 48 (49,152)         | 4 (4096)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-68 | Z8F4802VS020SC |  |  |  |  |

| Z8 Encore!®                                       | 48 (49,152)         | 4 (4096)          | 20                  | 0 to +70                  | 3.0 - 3.6      | QFP-80  | Z8F4803FT020SC |  |  |  |  |

#### Table 128. Ordering Information

## **Problem Description or Suggestion**

Provide a complete description of the problem or your suggestion. If you are reporting a specific problem, include all steps leading up to the occurrence of the problem. Attach additional pages as necessary.

cc 184 CCF 189 characteristics, electrical 167 clear 189 clock phase (SPI) 102 **CLR 189** COM 190 compare 71 compare - extended addressing 187 compare mode 71 compare with carry 187 compare with carry - extended addressing 187 complement 190 complement carry flag 188, 189 condition code 184 continuous assertion interrupt sources 47 continuous conversion (ADC) 134 continuous mode 70 control register definition, UART 86 control register, I2C 119 counter modes 70 CP 187 CPC 187 **CPCX 187** CPU and peripheral overview 3 CPU control instructions 189 CPX 187 customer feedback form 216 customer information 216 customer service 213

## D

DA 184, 187 data memory 19 data register, I2C 118 DC characteristics 169 debugger, on-chip 151 DEC 187 decimal adjust 187 decrement 187 decrement and jump non-zero 190 decrement word 187 DECW 187 destination operand 185 device, port availability 33 DI 189 direct address 184 direct memory access controller 122 disable interrupts 189 **DJNZ 190** DMA address high nibble register 126 configuring for DMA\_ADC data transfer 124 confiigurting DMA0-1 data transfer 123 control of ADC 135 control register 124 control register definitions 124 controller 5 DMA ADC address register 128 DMA\_ADC control register 130 DMA ADC operation 123 end address low byte register 128 I/O address register 125 operation 122 start/current address low byte register 127 status register 131 DMAA\_STAT register 131 DMAACTL register 130 DMAxCTL register 124 DMAxEND register 128 DMAxH register 126 DMAxI/O address (DMAxIO) 126 DMAxIO register 126 DMAxSTART register 128 document number description 215 dst 185

## E

EI 189 electrical characteristics 167 ADC 174 flash memory and timing 173 GPIO input data sample timing 176 watch-dog timer 174 enable interrupt 189 ER 184