#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                    |

| Number of I/O              | 60                                                            |

| Program Memory Size        | 48KB (48K x 8)                                                |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 4K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                     |

| Data Converters            | A/D 12x10b                                                    |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | 0°C ~ 70°C (TA)                                               |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 80-BQFP                                                       |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f4803ft020sc00tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Use of All Uppercase Letters**

The use of all uppercase letters designates the names of states and commands.

- Example 1: The bus is considered BUSY after the Start condition.

- Example 2: A START command triggers the processing of the initialization sequence.

### **Bit Numbering**

Bits are numbered from 0 to n-1 where n indicates the total number of bits. For example, the 8 bits of a register are numbered from 0 to 7.

### Safeguards

It is important that all users understand the following safety terms, which are defined here.

Indicates a procedure or file may become corrupted if the user does not follow directions.

### Trademarks

ZiLOG, eZ8, Z8 Encore!, and Z8 are trademarks of <u>ZiLOG, Inc.</u> in the U.S.A. and other countries. All other trademarks are the property of their respective corporations.

8

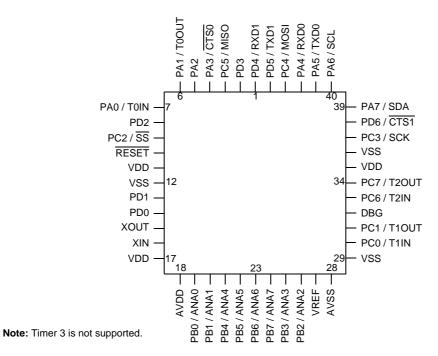

Figure 57. Z8Fxx01 in 44-Pin Plastic Leaded Chip Carrier (PLCC)

| Address (Hex) | <b>Register Description</b> | Mnemonic | Reset (Hex) | Page # |

|---------------|-----------------------------|----------|-------------|--------|

| FCE           | Interrupt Port Select       | IRQPS    | 00          | 55     |

| FCF           | Interrupt Control           | IRQCTL   | 00          | 56     |

| GPIO Port A   |                             |          |             |        |

| FD0           | Port A Address              | PAADDR   | 00          | 37     |

| FD1           | Port A Control              | PACTL    | 00          | 38     |

| FD2           | Port A Input Data           | PAIN     | XX          | 42     |

| FD3           | Port A Output Data          | PAOUT    | 00          | 43     |

| GPIO Port B   |                             |          |             |        |

| FD4           | Port B Address              | PBADDR   | 00          | 37     |

| FD5           | Port B Control              | PBCTL    | 00          | 38     |

| FD6           | Port B Input Data           | PBIN     | XX          | 42     |

| FD7           | Port B Output Data          | PBOUT    | 00          | 43     |

| GPIO Port C   | -                           |          |             |        |

| FD8           | Port C Address              | PCADDR   | 00          | 37     |

| FD9           | Port C Control              | PCCTL    | 00          | 38     |

| FDA           | Port C Input Data           | PCIN     | XX          | 42     |

| FDB           | Port C Output Data          | PCOUT    | 00          | 43     |

| GPIO Port D   | Ĩ                           |          |             |        |

| FDC           | Port D Address              | PDADDR   | 00          | 37     |

| FDD           | Port D Control              | PDCTL    | 00          | 38     |

| FDE           | Port D Input Data           | PDIN     | XX          | 42     |

| FDF           | Port D Output Data          | PDOUT    | 00          | 43     |

| GPIO Port E   | Ĩ                           |          |             |        |

| FE0           | Port E Address              | PEADDR   | 00          | 37     |

| FE1           | Port E Control              | PECTL    | 00          | 38     |

| FE2           | Port E Input Data           | PEIN     | XX          | 42     |

| FE3           | Port E Output Data          | PEOUT    | 00          | 43     |

| GPIO Port F   | ×                           |          |             |        |

| FE4           | Port F Address              | PFADDR   | 00          | 37     |

| FE5           | Port F Control              | PFCTL    | 00          | 38     |

| FE6           | Port F Input Data           | PFIN     | XX          | 42     |

| FE7           | Port F Output Data          | PFOUT    | 00          | 43     |

| GPIO Port G   | 1                           |          |             |        |

| FE8           | Port G Address              | PGADDR   | 00          | 37     |

| FE9           | Port G Control              | PGCTL    | 00          | 38     |

| FEA           | Port G Input Data           | PGIN     | XX          | 42     |

| FEB           | Port G Output Data          | PGOUT    | 00          | 43     |

| GPIO Port H   |                             |          |             |        |

| FEC           | Port H Address              | PHADDR   | 00          | 37     |

| XX=Undefined  | 1 011 11 / 1001000          | THEDR    |             | 51     |

### Table 6. Register File Address Map (Continued)

### System and Short Resets

During a System Reset, the Z8F640x family device is held in Reset for 514 cycles of the Watch-Dog Timer oscillator followed by 16 cycles of the system clock (crystal oscillator). A Short Reset differs from a System Reset only in the number of Watch-Dog Timer oscillator cycles required to exit Reset. A Short Reset requires only 66 Watch-Dog Timer oscillator cycles. Unless specifically stated otherwise, System Reset and Short Reset are referred to collectively as Reset.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watch-Dog Timer oscillator continue to run. The system clock begins operating following the Watch-Dog Timer oscillator cycle count. The eZ8 CPU and on-chip peripherals remain idle through the 16 cycles of the system clock.

Upon Reset, control registers within the Register File that have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer, and Flags) and general-purpose RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

### **Reset Sources**

Table 8 lists the reset sources and type of Reset as a function of the Z8F640x family device operating mode. The text following provides more detailed information on the individual Reset sources. Please note that Power-On Reset / Voltage Brown-Out events always have priority over all other possible reset sources to insure a full system reset occurs.

| <b>Operating Mode</b> | Reset Source                                             | Reset Type                                                          |  |  |

|-----------------------|----------------------------------------------------------|---------------------------------------------------------------------|--|--|

| Normal or Halt modes  | Power-On Reset / Voltage Brown-Out                       | System Reset                                                        |  |  |

|                       | Watch-Dog Timer time-out<br>when configured for Reset    | Short Reset                                                         |  |  |

|                       | RESET pin assertion                                      | Short Reset                                                         |  |  |

|                       | On-Chip Debugger initiated Reset<br>(OCDCTL[1] set to 1) | System Reset except the On-Chip Debugger is unaffected by the reset |  |  |

| Stop mode             | Power-On Reset / Voltage Brown-Out                       | System Reset                                                        |  |  |

|                       | RESET pin assertion                                      | System Reset                                                        |  |  |

|                       | DBG pin driven Low                                       | System Reset                                                        |  |  |

Table 8. Reset Sources and Resulting Reset Type

### Port A-H Data Direction Sub-Registers

The Port A-H Data Direction sub-register is accessed through the Port A-H Control register by writing 01H to the Port A-H Address register (Table 15).

Table 15. Port A-H Data Direction Sub-Registers

| BITS  | 7   | 6                                                                             | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-------|-----|-------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|--|--|--|

| FIELD | DD7 | DD6                                                                           | DD5 | DD4 | DD3 | DD2 | DD1 | DD0 |  |  |  |

| RESET | 1   | 1                                                                             | 1   | 1   | 1   | 1   | 1   | 1   |  |  |  |

| R/W   | R/W | R/W         R/W         R/W         R/W         R/W         R/W               |     |     |     |     |     |     |  |  |  |

| ADDR  |     | If 01H in Port A-H Address Register, accessible via Port A-H Control Register |     |     |     |     |     |     |  |  |  |

#### DD[7:0]—Data Direction

These bits control the direction of the associated port pin. Port Alternate Function operation overrides the Data Direction register setting.

0 =Output. Data in the Port A-H Output Data register is driven onto the port pin. 1 =Input. The port pin is sampled and the value written into the Port A-H Input Data Register. The output driver is tri-stated.

#### Port A-H Alternate Function Sub-Registers

The Port A-H Alternate Function sub-register (Table 16) is accessed through the Port A-H Control register by writing 02H to the Port A-H Address register. The Port A-H Alternate Function sub-registers select the alternate functions for the selected pins. Refer to the **GPIO Alternate Functions** section to determine the alternate function associated with each port pin.

**Caution:** Do not enable alternate function for GPIO port pins which do not have an associated alternate function. Failure to follow this guideline may result in unpredictable operation.

| BITS  | 7   | 6                                                                             | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-------|-----|-------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|--|--|--|

| FIELD | AF7 | AF6                                                                           | AF5 | AF4 | AF3 | AF2 | AF1 | AF0 |  |  |  |

| RESET | 0   | 0                                                                             | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

| R/W   | R/W | R/W         R/W         R/W         R/W         R/W         R/W               |     |     |     |     |     |     |  |  |  |

| ADDR  |     | If 02H in Port A-H Address Register, accessible via Port A-H Control Register |     |     |     |     |     |     |  |  |  |

Table 16. Port A-H Alternate Function Sub-Registers

### Port A-H Output Data Register

The Port A-H Output Data register (Table 21) writes output data to the pins.

BITS 7 6 5 4 3 2 1 0 POUT7 POUT6 POUT5 POUT4 POUT3 POUT2 POUT1 POUT0 FIELD 0 0 0 0 0 0 0 0 RESET R/W R/W R/W R/W R/W R/W R/W R/W R/W FD3H, FD7H, FDBH, FDFH, FE3H, FE7H, FEBH, FEFH ADDR

#### Table 21. Port A-H Output Data Register (PxOUT)

#### POUT[7:0]—Port Output Data

These bits contain the data to be driven out from the port pins. The values are only driven if the corresponding pin is configured as an output and the pin is not configured for alternate function operation.

0 =Drive a logical 0 (Low).

1= Drive a logical 1 (High). High value is not driven if the drain has been disabled by setting the corresponding Port Output Control register bit to 1.

Interrupt Port Select register selects between Port A and Port D for the individual interrupts.

| BITS  | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|-------|------|------|------|------|------|------|------|------|--|--|

| FIELD | IES7 | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |  |  |

| RESET | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |  |  |

| R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |  |  |

| ADDR  |      | FCDH |      |      |      |      |      |      |  |  |

Table 35. Interrupt Edge Select Register (IRQES)

IES*x*—Interrupt Edge Select *x*

where *x* indicates the specific GPIO Port pin number (0 through 7). The pulse width should be greater than 1 system clock to guarantee capture of the edge triggered interrupt. 0 = An interrupt request is generated on the falling edge of the PA*x*/PD*x* input. 1 = An interrupt request is generated on the rising edge of the PA*x*/PD*x* input.

### **Interrupt Port Select Register**

The Port Select (IRQPS) register (Table 36) determines the port pin that generates the PAx/PDx interrupts. This register allows either Port A or Port D pins to be used as interrupts. The Interrupt Edge Select register controls the active interrupt edge.

| BITS  | 7     | 6     | 5                   | 4     | 3     | 2     | 1     | 0     |  |  |  |

|-------|-------|-------|---------------------|-------|-------|-------|-------|-------|--|--|--|

| FIELD | PAD7S | PAD6S | PAD5S               | PAD4S | PAD3S | PAD2S | PAD1S | PAD0S |  |  |  |

| RESET | 0     | 0     | 0                   | 0     | 0     | 0     | 0     | 0     |  |  |  |

| R/W   | R/W   | R/W   | R/W R/W R/W R/W R/W |       |       |       |       |       |  |  |  |

| ADDR  |       | FCEH  |                     |       |       |       |       |       |  |  |  |

Table 36. Interrupt Port Select Register (IRQPS)

PADxS—PAx/PDx Selection

0 = PAx is used for the interrupt for PAx/PDx interrupt request.

1 = PDx is used for the interrupt for PAx/PDx interrupt request.

where *x* indicates the specific GPIO Port pin number (0 through 7).

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control register to enable the timer.

- 7. Counting begins on the first appropriate transition of the Timer Input signal. No interrupt is generated by this first edge.

In Capture/Compare mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) = (Capture Value – Start Value) × Prescale System Clock Frequency (Hz)

#### **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte register is read, the contents of the Timer Low Byte register are placed in a holding register. A subsequent read from the Timer Low Byte register returns the value in the holding register. This operation allows accurate reads of the full 16-bit timer count value while enabled. When the timers are not enabled, a read from the Timer Low Byte register returns the actual value in the counter.

#### **Timer Output Signal Operation**

Timer Output is a GPIO Port pin alternate function. Generally, the Timer Output is toggled every time the counter is reloaded.

### **Timer Control Register Definitions**

Timers 0–2 are available in all packages. Timer 3 is available only in the 64-, 68- and 80-pin packages.

#### Timer 0-3 High and Low Byte Registers

The Timer 0-3 High and Low Byte (TxH and TxL) registers (Tables 38 and 39) contain the current 16-bit timer count value. When the timer is enabled, a read from TxH causes the value in TxL to be stored in a temporary holding register. A read from TMRL always returns this temporary register when the timers are enabled. When the timer is disabled, reads from the TMRL reads the register directly.

Writing to the Timer High and Low Byte registers while the timer is enabled is not recommended. There are no temporary holding registers available for write operations, so simultaneous 16-bit writes are not possible. If either the Timer High or Low Byte registers are

set to 2-byte transfers, the temporary holding register for the Timer Reload High Byte is not bypassed.

BITS 7 6 5 4 3 2 1 0 TRH FIELD 1 1 1 1 1 1 1 1 RESET R/W R/W R/W R/W R/W R/W R/W R/W R/W F02H, F0AH, F12H, F1AH ADDR

### Table 40. Timer 0-3 Reload High Byte Register (TxRH)

### Table 41. Timer 0-3 Reload Low Byte Register (TxRL)

| BITS  | 7   | 6                                                               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|-------|-----|-----------------------------------------------------------------|---|---|---|---|---|---|--|--|--|--|

| FIELD |     | TRL                                                             |   |   |   |   |   |   |  |  |  |  |

| RESET | 1   | 1                                                               | 1 | 1 | 1 | 1 | 1 | 1 |  |  |  |  |

| R/W   | R/W | R/W         R/W         R/W         R/W         R/W         R/W |   |   |   |   |   |   |  |  |  |  |

| ADDR  |     | F03H, F0BH, F13H, F1BH                                          |   |   |   |   |   |   |  |  |  |  |

TRH and TRL-Timer Reload Register High and Low

These two bytes form the 16-bit Reload value, {TRH[7:0], TRL[7:0]}. This value is used to set the maximum count value which initiates a timer reload to 0001H. In Compare mode, these two byte form the 16-bit Compare value.

mode. Refer to the **Reset and Stop Mode Recovery** chapter for more information on STOP Mode Recovery.

If interrupts are enabled, following completion of the Stop Mode Recovery the eZ8 CPU responds to the interrupt request by fetching the Watch-Dog Timer interrupt vector and executing code from the vector address.

#### WDT Reset in Normal Operation

If configured to generate a Reset when a time-out occurs, the Watch-Dog Timer forces the Z8F640x family device into the Short Reset state. The WDT status bit in the Watch-Dog Timer Control register is set to 1. Refer to the **Reset and Stop Mode Recovery** chapter for more information on Short Reset.

#### WDT Reset in Stop Mode

If configured to generate a Reset when a time-out occurs and the Z8F640x family device is in STOP mode, the Watch-Dog Timer initiates a Stop Mode Recovery. Both the WDT status bit and the STOP bit in the Watch-Dog Timer Control register are set to 1 following WDT time-out in STOP mode. Refer to the **Reset and Stop Mode Recovery** chapter for more information.

#### Watch-Dog Timer Reload Unlock Sequence

Writing the unlock sequence to the Watch-Dog Timer Control register (WDTCTL) unlocks the three Watch-Dog Timer Reload Byte registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL register address produce no effect on the bits in the WDTCTL register. The locking mechanism prevents spurious writes to the Reload registers. The follow sequence is required to unlock the Watch-Dog Timer Reload Byte registers (WDTU, WDTH, and WDTL) for write access.

- 1. Write 55H to the Watch-Dog Timer Control register (WDTCTL)

- 2. Write AAH to the Watch-Dog Timer Control register (WDTCTL)

- 3. Write the Watch-Dog Timer Reload Upper Byte register (WDTU)

- 4. Write the Watch-Dog Timer Reload High Byte register (WDTH)

- 5. Write the Watch-Dog Timer Reload Low Byte register (WDTL)

All three Watch-Dog Timer Reload registers must be written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur, unless the sequence is restarted. The value in the Watch-Dog Timer Reload registers is loaded into the counter when the Watch-Dog Timer is first enabled and every time a WDT instruction is executed.

- 7. Write to the UART Control 0 register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if desired, and select either even or odd parity.

- 8. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data reception. When the UART Receiver interrupt is detected, the associated interrupt service routine (ISR) should perform the following:

- 9. Check the UART Status 0 register to determine the source of the interrupt error, break, or received data.

- 10. If the interrupt was due to data available, read the data from the UART Receive Data register. If operating in Multiprocessor (9-bit) mode, first read the Multiprocessor Receive flag (MPRX) to determine if the data was directed to this UART before reading the data.

- 11. Clear the UART Receiver interrupt in the applicable Interrupt Request register.

- 12. Execute the IRET instruction to return from the interrupt-service routine and await more data.

### Receiving Data using the Direct Memory Access Controller (DMA)

The DMA and UART can coordinate automatic data transfer from the UART Receive Data register to general-purpose Register File RAM. This reduces the eZ8 CPU processing overhead required to support UART data reception. The UART Receiver interrupt must then only notify the eZ8 CPU of error conditions. Follow these steps to configure the UART and DMA for automatic data handling:

- 1. Write to the DMA control registers to configure the DMA to transfer data from the UART Receive Data register to general-purpose Register File RAM.

- 2. Write to the UART Baud Rate High and Low Byte registers to set the desired baud rate.

- 3. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 4. Write to the Interrupt control registers to enable the UART Receiver interrupt and set the desired priority.

- 5. Write to the UART Control 1 register to:

- Enable Multiprocessor (9-bit) mode functions, if desired.

- Disable the UART interrupt for received data by clearing  $\overline{\text{RDAIRQ}}$  to 0.

3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BIRQ bit in the UART*x* Control 1 register to 1.

## **UART Control Register Definitions**

The UART control registers support both the UARTs and the associated Infrared Encoder/ Decoders. For more information on the infrared operation, refer to the **Infrared Encoder/ Decoder** chapter on page 95.

### UARTx Transmit Data Register

Data bytes written to the UART*x* Transmit Data register (Table 50) are shifted out on the TXD*x* pin. The Write-only UART*x* Transmit Data register shares a Register File address with the Read-only UART*x* Receive Data register.

| BITS  | 7   | 6             | 5 | 4       | 3       | 2 | 1 | 0 |  |  |  |

|-------|-----|---------------|---|---------|---------|---|---|---|--|--|--|

| FIELD | TXD |               |   |         |         |   |   |   |  |  |  |

| RESET | Х   | Х             | Х | Х       | Х       | Х | Х | Х |  |  |  |

| R/W   | W   | W W W W W W W |   |         |         |   |   |   |  |  |  |

| ADDR  |     |               |   | F40H ar | nd F48H |   |   |   |  |  |  |

Table 50. UARTx Transmit Data Register (UxTXD)

TXD—Transmit Data

UART transmitter data byte to be shifted out through the TXD*x* pin.

| 10.0 MHz System | ı Clock     |             |        | 5.5296 MHz Syst | em Clock    |             |       |

|-----------------|-------------|-------------|--------|-----------------|-------------|-------------|-------|

| Desired Rate    | BRG Divisor | Actual Rate | Error  | Desired Rate    | BRG Divisor | Actual Rate | Error |

| (kHz)           | (Decimal)   | (kHz)       | (%)    | (kHz)           | (Decimal)   | (kHz)       | (%)   |

| 1250.0          | N/A         | N/A         | N/A    | 1250.0          | N/A         | N/A         | N/A   |

| 625.0           | 1           | 625.0       | 0.00   | 625.0           | N/A         | N/A         | N/A   |

| 250.0           | 3           | 208.33      | -16.67 | 250.0           | 1           | 345.6       | 38.24 |

| 115.2           | 5           | 125.0       | 8.51   | 115.2           | 3           | 115.2       | 0.00  |

| 57.6            | 11          | 56.8        | -1.36  | 57.6            | 6           | 57.6        | 0.00  |

| 38.4            | 16          | 39.1        | 1.73   | 38.4            | 9           | 38.4        | 0.00  |

| 19.2            | 33          | 18.9        | 0.16   | 19.2            | 18          | 19.2        | 0.00  |

| 9.60            | 65          | 9.62        | 0.16   | 9.60            | 36          | 9.60        | 0.00  |

| 4.80            | 130         | 4.81        | 0.16   | 4.80            | 72          | 4.80        | 0.00  |

| 2.40            | 260         | 2.40        | -0.03  | 2.40            | 144         | 2.40        | 0.00  |

| 1.20            | 521         | 1.20        | -0.03  | 1.20            | 288         | 1.20        | 0.00  |

| 0.60            | 1042        | 0.60        | -0.03  | 0.60            | 576         | 0.60        | 0.00  |

| 0.30            | 2083        | 0.30        | 0.02   | 0.30            | 1152        | 0.30        | 0.00  |

#### Table 58. UART Baud Rates (Continued)

#### 3.579545 MHz System Clock

| Desired Rate | BRG Divisor | Actual Rate | Error  | Desired Rate | BRG Divisor | Actual Rate | Error |  |

|--------------|-------------|-------------|--------|--------------|-------------|-------------|-------|--|

| (kHz)        | (Decimal)   | (kHz)       | (%)    | (kHz)        | (Decimal)   | (kHz)       | (%)   |  |

| 1250.0       | N/A         | N/A         | N/A    | 1250.0       | N/A         | N/A         | N/A   |  |

| 625.0        | N/A         | N/A         | N/A    | 625.0        | N/A         | N/A         | N/A   |  |

| 250.0        | 1           | 223.72      | -10.51 | 250.0        | N/A         | N/A         | N/A   |  |

| 115.2        | 2           | 111.9       | -2.90  | 115.2        | 1           | 115.2       | 0.00  |  |

| 57.6         | 4           | 55.9        | -2.90  | 57.6         | 2           | 57.6        | 0.00  |  |

| 38.4         | 6           | 37.3        | -2.90  | 38.4         | 3           | 38.4        | 0.00  |  |

| 19.2         | 12          | 18.6        | -2.90  | 19.2         | 6           | 19.2        | 0.00  |  |

| 9.60         | 23          | 9.73        | 1.32   | 9.60         | 12          | 9.60        | 0.00  |  |

| 4.80         | 47          | 4.76        | -0.83  | 4.80         | 24          | 4.80        | 0.00  |  |

| 2.40         | 93          | 2.41        | 0.23   | 2.40         | 48          | 2.40        | 0.00  |  |

| 1.20         | 186         | 1.20        | 0.23   | 1.20         | 96          | 1.20        | 0.00  |  |

| 0.60         | 373         | 0.60        | -0.04  | 0.60         | 192         | 0.60        | 0.00  |  |

| 0.30         | 746         | 0.30        | -0.04  | 0.30         | 384         | 0.30        | 0.00  |  |

|              |             |             |        | -            |             |             |       |  |

1.8432 MHz System Clock

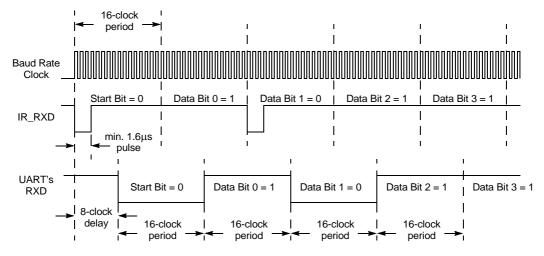

**Figure 73. Infrared Data Reception**

### Jitter

Because of the inherent sampling of the received IR\_RXD signal by the bit rate clock, some jitter can be expected on the first bit in any sequence of data. All subsequent bits in the received data stream are a fixed 16-clock periods wide.

## Infrared Encoder/Decoder Control Register Definitions

All Infrared Endec configuration and status information is set by the UART control registers as defined beginning on page 86.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART*x* Control 1 register to 1 to enable the Infrared Encoder/ Decoder *before* enabling the GPIO Port alternate function for the corresponding pin.

### **SPI Control Register**

The SPI Control register configures the SPI for transmit and receive operations.

| BITS  | 7    | 6    | 5    | 4     | 3      | 2   | 1    | 0     |  |  |

|-------|------|------|------|-------|--------|-----|------|-------|--|--|

| FIELD | IRQE | STR  | BIRQ | PHASE | CLKPOL | WOR | MMEN | SPIEN |  |  |

| RESET | 0    | 0    | 0    | 0     | 0      | 0   | 0    | 0     |  |  |

| R/W   | R/W  | R/W  | R/W  | R/W   | R/W    | R/W | R/W  | R/W   |  |  |

| ADDR  |      | F61H |      |       |        |     |      |       |  |  |

#### Table 61. SPI Control Register (SPICTL)

IRQE—Interrupt Request Enable

0 = SPI interrupts are disabled. No interrupt requests are sent to the Interrupt Controller.

1 = SPI interrupts are enabled. Interrupt requests are sent to the Interrupt Controller.

STR—Start an SPI Interrupt Request

0 = No effect.

1 = Setting this bit to 1 also sets the IRQ bit in the SPI Status register to 1. Setting this bit forces the SPI to send an interrupt request to the Interrupt Control. This bit can be used by software for a function similar to transmit buffer empty in a UART.

#### BIRQ—BRG Timer Interrupt Request

If the SPI is enabled, this bit has no effect. If the SPI is disabled:

0 = The Baud Rate Generator timer function is disabled.

1 = The Baud Rate Generator timer function and time-out interrupt are enabled.

PHASE—Phase Select

Sets the phase relationship of the data to the clock. Refer to the **SPI Clock Phase and Polarity Control** section for more information on operation of the PHASE bit.

CLKPOL—Clock Polarity

0 = SCK idles Low (0).

1 = SCK idle High (1).

WOR—Wire-OR (Open-Drain) Mode Enabled

0 = SPI signal pins not configured for open-drain.

1 = All four SPI signal pins (SCK,  $\overline{SS}$ , MISO, MOSI) configured for open-drain function. This setting is typically used for multi-master and/or multi-slave configurations.

MMEN-SPI Master Mode Enable

0 = SPI configured in Slave mode.

1 = SPI configured in Master mode.

Read Data Memory (0DH)—The Read Data Memory command reads from Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be read 1-65536 bytes at a time (65536 bytes can be read by setting size to zero). If the Z8F640x family device is not in Debug mode, this command returns FFH for the data.

```

DBG <-- ODH

DBG <-- Data Memory Address[15:8]

DBG <-- Data Memory Address[7:0]

DBG <-- Size[15:8]

DBG <-- Size[7:0]

DBG --> 1-65536 data bytes

```

• **Read Program Memory CRC (0EH)**—The Read Program Memory CRC command computes and returns the CRC (cyclic redundancy check) of Program Memory using the 16-bit CRC-CCITT polynomial. If the Z8F640x family device is not in Debug mode, this command returns FFFFH for the CRC value. Unlike most other OCD Read commands, there is a delay from issuing of the command until the OCD returns the data. The OCD reads the Program Memory, calculates the CRC value, and returns the result. The delay is a function of the Program Memory size and is approximately equal to the system clock period multiplied by the number of bytes in the Program Memory.

```

DBG <-- 0EH

DBG --> CRC[15:8]

DBG --> CRC[7:0]

```

• **Step Instruction (10H)**—The Step Instruction command steps one assembly instruction at the current Program Counter (PC) location. If the Z8F640x family device is not in Debug mode or the Read Protect Option Bit is enabled, the OCD ignores this command.

DBG <-- 10H

• **Stuff Instruction (11H)**—The Stuff Instruction command steps one assembly instruction and allows specification of the first byte of the instruction. The remaining 0-4 bytes of the instruction are read from Program Memory. This command is useful for stepping over instructions where the first byte of the instruction has been overwritten by a Breakpoint. If the Z8F640x family device is not in Debug mode or the Read Protect Option Bit is enabled, the OCD ignores this command.

```

DBG <-- 11H

DBG <-- opcode[7:0]

```

• Execute Instruction (12H)—The Execute Instruction command allows sending an entire instruction to be executed to the eZ8 CPU. This command can also step over Breakpoints. The number of bytes to send for the instruction depends on the opcode. If the Z8F640x family device is not in Debug mode or the Read Protect Option Bit is enabled, this command reads and discards one byte.

```

DBG <-- 12H

DBG <-- 1-5 byte opcode

```

179

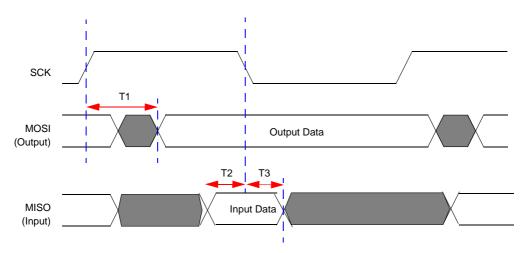

### **SPI Master Mode Timing**

Figure 96 and Table 110 provide timing information for SPI Master mode pins. Timing is shown with SCK rising edge used to source MOSI output data, SCK falling edge used to sample MISO input data. Timing on the SS output pin(s) is controlled by software.

Figure 96. SPI Master Mode Timing

| Table | 110. | SPI | Master | Mode | Timing |

|-------|------|-----|--------|------|--------|

|-------|------|-----|--------|------|--------|

|                |                                             | Delay (ns) |         |  |

|----------------|---------------------------------------------|------------|---------|--|

| Parameter      | Abbreviation                                | Minimum    | Maximum |  |

| T <sub>1</sub> | SCK Rise to MOSI output Valid Delay         | -5         | +5      |  |

| T <sub>2</sub> | MISO input to SCK (receive edge) Setup Time | 20         |         |  |

| T <sub>3</sub> | MISO input to SCK (receive edge) Hold Time  | 0          |         |  |

; value 01H, is the source. The value 01H is written into the

; Register at address 234H.

## Assembly Language Syntax

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. This binary format must be followed by users that prefer manual program coding or intend to implement their own assembler.

**Example 1**: If the contents of Registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

Table 113. Assembly Language Syntax Example 1

| Assembly Language Code | ADD | 43H, | 08H | (ADD dst, src) |

|------------------------|-----|------|-----|----------------|

| Object Code            | 04  | 08   | 43  | (OPC src, dst) |

**Example 2**: In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0 - 255 or, using Escaped Mode Addressing, a Working Register R0 - R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

Table 114. Assembly Language Syntax Example 2

| Assembly Language Code | ADD | 43H, | R8 | (ADD dst, src) |

|------------------------|-----|------|----|----------------|

| Object Code            | 04  | E8   | 43 | (OPC src, dst) |

See the device-specific Product Specification to determine the exact register file range available. The register file size varies, depending on the device type.

## eZ8 CPU Instruction Notation

In the eZ8 CPU Instruction Summary and Description sections, the operands, condition codes, status flags, and address modes are represented by a notational shorthand that is described in Table 115

**RRC** 191 **SBC 188** SCF 188, 189 **SRA 191** SRL 191 **SRP 189 STOP 189 SUB 188 SUBX 188 SWAP 191 TCM 188 TCMX 188** TM 188 TMX 188 **TRAP 190** watch-dog timer refresh 189 XOR 190 **XORX 190** instructions, eZ8 classes of 187 interrupt control register 56 interrupt controller 5, 44 architecture 44 interrupt assertion types 47 interrupt vectors and priority 47 operation 46 register definitions 48 interrupt edge select register 54 interrupt port select register 55 interrupt request 0 register 48 interrupt request 1 register 49 interrupt request 2 register 50 interrupt return 190 interrupt vector listing 44 interrupts not acknowledge 112 receive 112 SPI 105 transmit 112 UART 85 introduction 1 IR 184 Ir 184 IrDA architecture 95

block diagram 95 control register definitions 98 jitter 98 operation 96 receiving data 97 transmitting data 96 IRET 190 IRQ0 enable high and low bit registers 51 IRQ1 enable high and low bit registers 52 IRQ2 enable high and low bit registers 53 IRR 184 Irr 184

# J

jitter 98 JP 190 jump, conditional, relative, and relative conditional 190

## L

LD 189 LDC 189 LDCI 188, 189 LDE 189 LDEI 188, 189 LDX 189 LEA 189 load 189 load constant 188 load constant to/from program memory 189 load constant with auto-increment addresses 189 load effective address 189 load external data 189 load external data to/from data memory and autoincrement addresses 188 load external to/from data memory and auto-increment addresses 189 load instructions 189 load using extended addressing 189 logical AND 190 logical AND/extended addressing 190 logical exclusive OR 190

SDA and SCL (IrDA) signals 111 second opcode map after 1FH 205 serial clock 101 serial peripheral interface (SPI) 99 set carry flag 188, 189 set register pointer 189 shift right arithmetic 191 shift right logical 191 signal descriptions 13 single assertion (pulse) interrupt sources 47 single-shot conversion (ADC) 133 SIO 5 slave data transfer formats (I2C) 114 slave select 102 software trap 190 source operand 185 SP 185 SPI architecture 99 baud rate generator 105 baud rate high and low byte register 110 clock phase 102 configured as slave 100 control register 107 control register definitions 106 data register 106 error detection 105 interrupts 105 mode fault error 105 mode register 109 multi-master operation 104 operation 100 overrun error 105 signals 101 single master, multiple slave system 100 single master, single slave system 99 status register 108 timing, PHASE = 0.103timing, PHASE=1 104 SPI controller signals 13 SPI mode (SPIMODE) 109 SPIBRH register 110 SPIBRL register 110 SPICTL register 107

SPIDATA register 106 SPIMODE register 109 SPISTAT register 108 SRA 191 src 185 SRL 191 **SRP 189** SS, SPI signal 101 stack pointer 185 status register, I2C 118 **STOP 189** stop mode 31, 189 stop mode recovery sources 29 using a GPIO port pin transition 30 using watch-dog timer time-out 29 **SUB 188** subtract 188 subtract - extended addressing 188 subtract with carry 188 subtract with carry - extended addressing 188 **SUBX 188 SWAP 191** swap nibbles 191 symbols, additional 185 system and short resets 26

# Т

TCM 188 TCMX 188 technical support 213 test complement under mask 188 test under mask 188 timer signals 14 timers 5, 57 architecture 57 block diagram 58 capture mode 62, 71 compare mode 63, 71 compare mode 63, 71 continuous mode 59, 70 counter mode 60 counter modes 70