Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |  |  |  |

|----------------------------|-----------------------------------------------------------|--|--|--|

| Core Processor             | eZ8                                                       |  |  |  |

| Core Size                  | 8-Bit                                                     |  |  |  |

| Speed                      | 20MHz                                                     |  |  |  |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |  |  |  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                |  |  |  |

| Number of I/O              | 46                                                        |  |  |  |

| Program Memory Size        | 64KB (64K x 8)                                            |  |  |  |

| Program Memory Type        | FLASH                                                     |  |  |  |

| EEPROM Size                | -                                                         |  |  |  |

| RAM Size                   | 4K x 8                                                    |  |  |  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |  |  |  |

| Data Converters            | A/D 12x10b                                                |  |  |  |

| Oscillator Type            | Internal                                                  |  |  |  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |  |  |  |

| Mounting Type              | Surface Mount                                             |  |  |  |

| Package / Case             | 64-LQFP                                                   |  |  |  |

| Supplier Device Package    | -                                                         |  |  |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f6402ar020ec |  |  |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| DMA_ADC Operation                                            | 123 |

|--------------------------------------------------------------|-----|

| Configuring DMA_ADC for Data Transfer                        | 124 |

| DMA Control Register Definitions                             | 124 |

| DMAx Control Register                                        | 124 |

| DMAx I/O Address Register                                    | 125 |

| DMAx Address High Nibble Register                            | 126 |

| DMAx Start/Current Address Low Byte Register                 | 127 |

| DMAx End Address Low Byte Register                           | 128 |

| DMA_ADC Address Register                                     | 128 |

| DMA_ADC Control Register                                     | 130 |

| DMA Status Register                                          | 131 |

| Analog-to-Digital Converter                                  | 132 |

| Overview                                                     | 132 |

| Architecture                                                 | 132 |

| Operation                                                    | 133 |

| Automatic Power-Down                                         | 133 |

| Single-Shot Conversion                                       | 133 |

| Continuous Conversion                                        | 134 |

| DMA Control of the ADC                                       | 135 |

| ADC Control Register Definitions                             | 135 |

| ADC Control Register                                         | 135 |

| ADC Data High Byte Register                                  |     |

| ADC Data Low Bits Register                                   | 137 |

| Flash Memory                                                 | 138 |

| Overview                                                     | 138 |

| Operation                                                    | 139 |

| Flash Operation Timing Using the Flash Frequency Registers   | 141 |

| Flash Code Protection Against External Access                |     |

| Flash Code Protection Against Accidental Program and Erasure | 141 |

| Byte Programming                                             | 142 |

| Page Erase                                                   | 143 |

| Mass Erase                                                   | 143 |

| Flash Controller Bypass                                      | 143 |

| Flash Control Register Definitions                           | 144 |

| Flash Control Register                                       | 144 |

| Flash Status Register                                        |     |

| Flash Page Select Register                                   |     |

| Flash Frequency High and Low Byte Registers                  | 147 |

#### Braces

The curly braces, { }, indicate a single register or bus created by concatenating some combination of smaller registers, buses, or individual bits.

• Example: the 12-bit register address {0H, RP[7:4], R1[3:0]} is composed of a 4-bit hexadecimal value (0H) and two 4-bit register values taken from the Register Pointer (RP) and Working Register R1. 0H is the most significant nibble (4-bit value) of the 12-bit register, and R1[3:0] is the least significant nibble of the 12-bit register.

#### Parentheses

The parentheses, ( ), indicate an indirect register address lookup.

• Example: (R1) is the memory location referenced by the address contained in the Working Register R1.

#### **Parentheses/Bracket Combinations**

The parentheses, (), indicate an indirect register address lookup and the square brackets, [], indicate a register or bus.

• *Example:* assume PC[15:0] contains the value 1234h. (PC[15:0]) then refers to the contents of the memory location at address 1234h.

#### Use of the Words Set, Reset and Clear

The word *set* implies that a register bit or a condition contains a logical 1. The words re*set* or *clear* imply that a register bit or a condition contains a logical 0. When either of these terms is followed by a number, the word *logical* may not be included; however, it is implied.

#### Notation for Bits and Similar Registers

A field of bits within a register is designated as: Register[*n*:*n*].

• Example: ADDR[15:0] refers to bits 15 through bit 0 of the Address.

#### Use of the Terms LSB, MSB, Isb, and msb

In this document, the terms *LSB* and *MSB*, when appearing in upper case, mean *least significant byte* and *most significant byte*, respectively. The lowercase forms, *lsb* and *msb*, mean *least significant bit* and *most significant bit*, respectively.

#### **Use of Initial Uppercase Letters**

Initial uppercase letters designate settings, modes, and conditions in general text.

- Example 1: Stop mode.

- Example 2: The receiver forces the SCL line to Low.

- The Master can generate a Stop condition to abort the transfer.

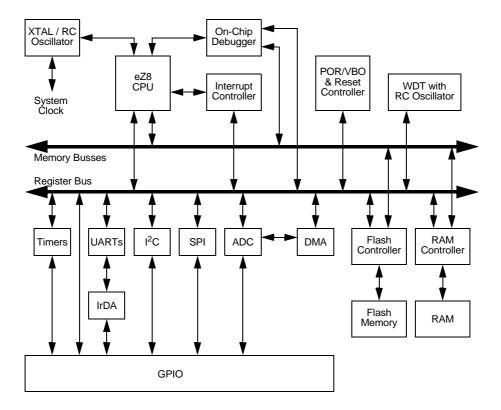

# **Block Diagram**

Figure 55 illustrates the block diagram of the architecture of the Z8 Encore!<sup>TM.</sup>

# **CPU and Peripheral Overview**

# eZ8 CPU Features

The eZ8, ZiLOG's latest 8-bit Central Processing Unit (CPU), meets the continuing demand for faster and more code-efficient microcontrollers. The eZ8 CPU executes a superset of the original Z8 instruction set. The eZ8 CPU features include:

Direct register-to-register architecture allows each register to function as an accumulator, improving execution time and decreasing the required program memory

- Software stack allows much greater depth in subroutine calls and interrupts than hardware stacks

- Compatible with existing Z8 code

- Expanded internal Register File allows access of up to 4KB

- New instructions improve execution efficiency for code developed using higher-level programming languages, including C

- Pipelined instruction fetch and execution

- New instructions for improved performance including BIT, BSWAP, BTJ, CPC, LDC, LDCI, LEA, MULT, and SRL

- New instructions support 12-bit linear addressing of the Register File

- Up to 10 MIPS operation

- C-Compiler friendly

- 2-9 clock cycles per instruction

For more information regarding the eZ8 CPU, refer to the *eZ8 CPU User Manual* available for download at <u>www.zilog.com</u>.

#### **General Purpose I/O**

The Z8 Encore!<sup>®</sup> features seven 8-bit ports (Ports A-G) and one 4-bit port (Port H) for general purpose I/O (GPIO). Each pin is individually programmable.

#### Flash Controller

The Flash Controller programs and erases the Flash memory.

#### 10-Bit Analog-to-Digital Converter

The Analog-to-Digital Converter (ADC) converts an analog input signal to a 10-bit binary number. The ADC accepts inputs from up to 12 different analog input sources.

#### UARTs

Each UART is full-duplex and capable of handling asynchronous data transfers. The UARTs support 8- and 9-bit data modes and selectable parity.

# l<sup>2</sup>C

The inter-integrated circuit  $(I^2C^{\circledast})$  controller makes the Z8 Encore!<sup>®</sup> compatible with the  $I^2C$  protocol. The  $I^2C$  controller consists of two bidirectional bus lines, a serial data (SDA) line and a serial clock (SCL) line.

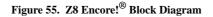

9

Figure 58. Z8Fxx01 in 44-Pin Low-Profile Quad Flat Package (LQFP)

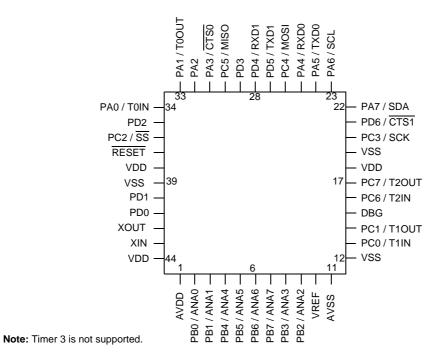

#### **Power-On Reset**

The Z8F640x family products contain an internal Power-On Reset (POR) circuit. The POR circuit monitors the supply voltage and holds the device in the Reset state until the supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold ( $V_{POR}$ ), the POR Counter is enabled and counts 514 cycles of the Watch-Dog Timer oscillator. After the POR counter times out, the XTAL Counter is enabled to count a total of 16 system clock pulses. The Z8F640x family device is held in the Reset state until both the POR Counter and XTAL counter have timed out. After the device exits the Power-On Reset state, the eZ8 CPU fetches the Reset vector. Following Power-On Reset, the POR status bit in the Watch-Dog Timer Control (WDTCTL) register is set to 1.

Figure 62 illustrates Power-On Reset operation. Refer to the **Electrical Characteristics** chapter for the POR threshold voltage ( $V_{POR}$ ).

Figure 62. Power-On Reset Operation (not to scale)

## Voltage Brown-Out Reset

The devices in the Z8F640x family provide low Voltage Brown-Out (VBO) protection. The VBO circuit senses when the supply voltage drops to an unsafe level (below the VBO

# Low-Power Modes

# **Overview**

The Z8F640x family products contain power-saving features. The highest level of power reduction is provided by Stop mode. The next level of power reduction is provided by the Halt mode.

# Stop Mode

Execution of the eZ8 CPU's STOP instruction places the Z8F640x family device into Stop mode. In Stop mode, the operating characteristics are:

- Primary crystal oscillator is stopped

- System clock is stopped

- eZ8 CPU is stopped

- Program counter (PC) stops incrementing

- Watch-Dog Timer's internal RC oscillator continues to operate

- If enabled, the Watch-Dog Timer continues to operate

- All other on-chip peripherals are idle

To minimize current in Stop mode, all GPIO pins that are configured as digital inputs must be driven to one of the supply rails ( $V_{CC}$  or GND). The Z8F640x family device can be brought out of Stop mode using Stop Mode Recovery. For more information on STOP Mode Recovery refer to the **Reset and Stop Mode Recovery** chapter.

## **Halt Mode**

Execution of the eZ8 CPU's HALT instruction places the Z8F640x family device into Halt mode. In Halt mode, the operating characteristics are:

- Primary crystal oscillator is enabled and continues to operate

- System clock is enabled and continues to operate

- eZ8 CPU is idle

- Program counter (PC) stops incrementing

| Port   | Pin     | Mnemonic     | Alternate Function Description                         |

|--------|---------|--------------|--------------------------------------------------------|

| Port D | PD0     | T3IN         | Timer 3 In (not available in 40- and 44-pin packages)  |

|        | PD1     | T3OUT        | Timer 3 Out (not available in 40- and 44-pin packages) |

|        | PD2     | N/A          | No alternate function                                  |

|        | PD3     | N/A          | No alternate function                                  |

|        | PD4     | RXD1 / IRRX1 | UART 1 / IrDA 1 Receive Data                           |

|        | PD5     | TXD1 / IRTX1 | UART 1 / IrDA 1 Transmit Data                          |

|        | PD6     | CTS1         | UART 1 Clear to Send                                   |

|        | PD7     | RCOUT        | Watch-Dog Timer RC Oscillator Output                   |

| Port E | PE[7:0] | N/A          | No alternate functions                                 |

| Port F | PF[7:0] | N/A          | No alternate functions                                 |

| Port G | PG[7:0] | N/A          | No alternate functions                                 |

| Port H | PH0     | ANA8         | ADC Analog Input 8                                     |

|        | PH1     | ANA9         | ADC Analog Input 9                                     |

|        | PH2     | ANA10        | ADC Analog Input 10                                    |

|        | PH3     | ANA11        | ADC Analog Input 11                                    |

Table 11. Port Alternate Function Mapping (Continued)

# **GPIO Interrupts**

Many of the GPIO port pins can be used as interrupt sources. Some port pins may be configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupts generate an interrupt when any edge occurs (both rising and falling). Refer to the **Interrupt Controller** chapter for more information on interrupts using the GPIO pins.

# **GPIO Control Register Definitions**

Four registers for each Port provide access to GPIO control, input data, and output data. Table 12 lists these Port registers. Use the Port A-H Address and Control registers together to provide access to sub-registers for Port configuration and control.

| BITS  | 7     | 6      | 5      | 4      | 3     | 2     | 1     | 0     |

|-------|-------|--------|--------|--------|-------|-------|-------|-------|

| FIELD | T3ENH | U1RENH | UITENH | DMAENH | C3ENH | C2ENH | C1ENH | C0ENH |

| RESET | 0     | 0      | 0      | 0      | 0     | 0     | 0     | 0     |

| R/W   | R/W   | R/W    | R/W    | R/W    | R/W   | R/W   | R/W   | R/W   |

| ADDR  |       |        |        | FC     | 7H    |       |       |       |

Table 33. IRQ2 Enable High Bit Register (IRQ2ENH)

T3ENH—Timer 3 Interrupt Request Enable High Bit U1RENH—UART 1 Receive Interrupt Request Enable High Bit U1TENH—UART 1 Transmit Interrupt Request Enable High Bit DMAENH—DMA Interrupt Request Enable High Bit C3ENH—Port C3 Interrupt Request Enable High Bit C2ENH—Port C2 Interrupt Request Enable High Bit C1ENH—Port C1 Interrupt Request Enable High Bit C0ENH—Port C0 Interrupt Request Enable High Bit

Table 34. IRQ2 Enable Low Bit Register (IRQ2ENL)

| BITS  | 7     | 6      | 5      | 4      | 3     | 2     | 1     | 0     |  |

|-------|-------|--------|--------|--------|-------|-------|-------|-------|--|

| FIELD | T3ENL | U1RENL | UITENL | DMAENL | C3ENL | C2ENL | C1ENL | C0ENL |  |

| RESET | 0     | 0      | 0      | 0      | 0     | 0     | 0     | 0     |  |

| R/W   | R/W   | R/W    | R/W    | R/W    | R/W   | R/W   | R/W   | R/W   |  |

| ADDR  |       | FC8H   |        |        |       |       |       |       |  |

T3ENL—Timer 3 Interrupt Request Enable Low Bit

U1RENL-UART 1 Receive Interrupt Request Enable Low Bit

U1TENL-UART 1 Transmit Interrupt Request Enable Low Bit

DMAENL—DMA Interrupt Request Enable Low Bit

C3ENL—Port C3 Interrupt Request Enable Low Bit

C2ENL—Port C2 Interrupt Request Enable Low Bit

C1ENL—Port C1 Interrupt Request Enable Low Bit

COENL-Port CO Interrupt Request Enable Low Bit

# Interrupt Edge Select Register

The Interrupt Edge Select (IRQES) register (Table 35) determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port input pin. The

- Configure the timer for Gated mode.

- Set the prescale value.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in Gated mode. After the first timer reset in Gated mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If desired, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

#### Capture/Compare Mode

In Capture/Compare mode, the timer begins counting on the *first* external Timer Input transition. The desired transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent desired transition (after the first) of the Timer Input signal captures the current count value. The Capture value is written to the Timer PWM High and Low Byte Registers. When the Capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H, and counting resumes.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

The steps for configuring a timer for Capture/Compare mode and initiating the count are as follows:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for Capture/Compare mode.

- Set the prescale value.

- Set the Capture edge (rising or falling) for the Timer Input.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

- 4. If desired, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

# **Timer 0-3 Control Registers**

The Timer 0-3 Control (TxCTL) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode.

BITS 7 4 3 2 1 0 6 5 TEN TPOL PRES TMODE FIELD 0 0 0 0 0 0 0 0 RESET R/W R/W R/W R/W R/W R/W R/W R/W R/W F07H, F0FH, F17H, F1FH ADDR

Table 44. Timer 0-3 Control Register (TxCTL)

TEN-Timer Enable

0 = Timer is disabled.

1 = Timer enabled to count.

TPOL-Timer Input/Output Polarity

Operation of this bit is a function of the current operating mode of the timer.

#### **One-Shot mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **Continuous mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **Counter mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **PWM mode**

0 = Timer Output is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload.

1 = Timer Output is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload.

Reserved These bits are reserved and must be 0.

# Watch-Dog Timer Reload Upper, High and Low Byte Registers

The Watch-Dog Timer Reload Upper, High and Low Byte (WDTU, WDTH, WDTL) registers (Tables 47 through 49) form the 24-bit reload value that is loaded into the Watch-Dog Timer when a WDT instruction executes. The 24-bit reload value is {WDTU[7:0], WDTH[7:0], WDTL[7:0]. Writing to these registers sets the desired Reload Value. Reading from these registers returns the current Watch-Dog Timer count value.

The 24-bit WDT Reload Value must not be set to a value less than 000004H or unpredictable behavior may result.

| BITS      | 7              | 6            | 5            | 4             | 3             | 2             | 1    | 0    |  |

|-----------|----------------|--------------|--------------|---------------|---------------|---------------|------|------|--|

| FIELD     | WDTU           |              |              |               |               |               |      |      |  |

| RESET     | 1              | 1            | 1            | 1             | 1             | 1             | 1    | 1    |  |

| R/W       | R/W*           | R/W*         | R/W*         | R/W*          | R/W*          | R/W*          | R/W* | R/W* |  |

| ADDR      |                | FF1H         |              |               |               |               |      |      |  |

| R/W* - Re | ad returns the | e current WD | T count valu | e. Write sets | the desired R | Reload Value. |      |      |  |

#### Table 47. Watch-Dog Timer Reload Upper Byte Register (WDTU)

#### WDTU-WDT Reload Upper Byte

Most significant byte (MSB), Bits[23:16], of the 24-bit WDT reload value.

Table 48. Watch-Dog Timer Reload High Byte Register (WDTH)

|           | ě              |              | •••          | 0             |               |              |      |      |  |

|-----------|----------------|--------------|--------------|---------------|---------------|--------------|------|------|--|

| BITS      | 7              | 6            | 5            | 4             | 3             | 2            | 1    | 0    |  |

| FIELD     |                | WDTH         |              |               |               |              |      |      |  |

| RESET     | 1              | 1            | 1            | 1             | 1             | 1            | 1    | 1    |  |

| R/W       | R/W*           | R/W*         | R/W*         | R/W*          | R/W*          | R/W*         | R/W* | R/W* |  |

| ADDR      | FF2H           |              |              |               |               |              |      |      |  |

| R/W* - Re | ad returns the | e current WD | T count valu | e. Write sets | the desired R | eload Value. |      |      |  |

WDTH—WDT Reload High Byte

# I<sup>2</sup>C Controller

# **Overview**

The I<sup>2</sup>C Controller makes the Z8F640x family device bus-compatible with the I<sup>2</sup>C<sup>TM</sup> protocol. The I<sup>2</sup>C Controller consists of two bidirectional bus lines—a serial data signal (SDA) and a serial clock signal (SCL). Features of the I<sup>2</sup>C Controller include:

- Transmit and Receive Operation in Master mode

- Maximum data rate of 400kbit/sec

- 7- and 10-bit Addressing Modes for Slaves

- Unrestricted Number of Data Bytes Transmitted per Transfer

The I<sup>2</sup>C Controller in the Z8F640x family device does not operate in Slave mode.

# Operation

The I<sup>2</sup>C Controller operates in Master mode to transmit and receive data. Only a single master is supported. Arbitration between two masters must be accomplished in software. I<sup>2</sup>C supports the following operations:

- Master transmits to a 7-bit slave

- Master transmits to a 10-bit slave

- Master receives from a 7-bit slave

- Master receives from a 10-bit slave

## SDA and SCL Signals

$I^2C$  sends all addresses, data and acknowledge signals over the SDA line, most-significant bit first. SCL is the common clock for the  $I^2C$  Controller. When the SDA and SCL pin alternate functions are selected for their respective GPIO ports, the pins are automatically configured for open-drain operation.

The master  $(I^2C)$  is responsible for driving the SCL clock signal, although the clock signal can become skewed by a slow slave device. During the high period of the clock, the slave pulls the SCL signal Low to suspend the transaction. When the slave has released the line, the  $I^2C$  Controller continues the transaction. All data is transferred in bytes and there is no

- Set CONT to 1 to select continuous conversion.

- Write to VREF to enable or disable the internal voltage reference generator.

- Set CEN to 1 to start the conversions.

- 3. When the first conversion in continuous operation is complete (after 5129 system clock cycles, plus the 40 cycles for power-up, if necessary), the ADC control logic performs the following operations:

- CEN resets to 0 to indicate the first conversion is complete. CEN remains 0 for all subsequent conversions in continuous operation.

- An interrupt request is sent to the Interrupt Controller to indicate the *first* conversion is complete. An interrupt request is not sent for subsequent conversions in continuous operation.

- 4. Thereafter, the ADC writes a new 10-bit data result to {ADCD\_H[7:0], ADCD\_L[7:6]} every 256 system clock cycles.

- 5. To disable continuous conversion, clear the CONT bit in the ADC Control register to 0.

## **DMA Control of the ADC**

The Direct Memory Access (DMA) Controller can control operation of the ADC including analog input selection and conversion enable. For more information on the DMA and configuring for ADC operations refer to the **Direct Memory Access Controller** chapter.

# **ADC Control Register Definitions**

## **ADC Control Register**

The ADC Control register selects the analog input channel and initiates the analog-to-digital conversion.

| BITS  | 7   | 6        | 5    | 4    | 3          | 2 | 1 | 0 |  |  |

|-------|-----|----------|------|------|------------|---|---|---|--|--|

| FIELD | CEN | Reserved | VREF | CONT | ANAIN[3:0] |   |   |   |  |  |

| RESET | 0   | 0        | 0    | 0    | 0000       |   |   |   |  |  |

| R/W   | R/W | R/W      | R/W  | R/W  | R/W        |   |   |   |  |  |

| ADDR  |     | F70H     |      |      |            |   |   |   |  |  |

| Table 80. | ADC | Control | Register | (ADCCTL) |

|-----------|-----|---------|----------|----------|

|-----------|-----|---------|----------|----------|

CEN—Conversion Enable

0 = Conversion is complete. Writing a 0 produces no effect. The ADC automatically clears

# **Flash Status Register**

The Flash Status register indicates the current state of the Flash Controller. This register can be read at any time. The Read-only Flash Status Register shares its Register File address with the Write-only Flash Control Register.

| BITS  | 7    | 6     | 5 | 4 | 3 | 2    | 1 | 0 |  |

|-------|------|-------|---|---|---|------|---|---|--|

| FIELD | Rese | erved |   |   |   | STAT |   |   |  |

| RESET | 0    | 0     | 0 | 0 | 0 | 0    | 0 | 0 |  |

| R/W   | R    | R     | R | R | R | R    | R | R |  |

| ADDR  |      | FF8H  |   |   |   |      |   |   |  |

Reserved

These bits are reserved and must be 0.

FSTAT—Flash Controller Status

000000 = Flash Controller locked.

000001 = First unlock command received.

000010 = Flash Controller unlocked (second unlock command received).

001xxx = Program operation in progress.

010xxx = Page erase operation in progress.

100xxx = Mass erase operation in progress.

156

ister. When the Watchpoint event occurs, the Z8F640x family device enters Debug mode and the DBGMODE bit in the OCDCTL register becomes 1.

## **Runtime Counter**

The On-Chip Debugger contains a 16-bit Runtime Counter. It counts system clock cycles between Breakpoints. The counter starts counting when the On-Chip Debugger leaves Debug mode and stops counting when it enters Debug mode again or when it reaches the maximum count of FFFFH.

# **On-Chip Debugger Commands**

The host communicates to the On-Chip Debugger by sending OCD commands using the DBG interface. During normal operation of the Z8F640x family device, only a subset of the OCD commands are available. In Debug mode, all OCD commands become available unless the user code and control registers are protected by programming the Read Protect Option Bit (RP). The Read Protect Option Bit prevents the code in memory from being read out of the Z8F640x family device. When this option is enabled, several of the OCD commands are disabled. Table 93 contains a summary of the On-Chip Debugger commands. Each OCD command is described in further detail in the bulleted list following Table 93. Table 93 indicates those commands that operate when the Z8F640x family device is not in Debug mode (normal operation) and those commands that are disabled by programming the Read Protect Option Bit.

| Debug Command              | Command Byte | Enabled when NOT in Debug mode? | Disabled by<br>Read Protect Option Bit                                                                                                                                    |

|----------------------------|--------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read OCD Revision          | 00H          | Yes                             | -                                                                                                                                                                         |

| Reserved                   | 01H          | -                               | -                                                                                                                                                                         |

| Read OCD Status Register   | 02H          | Yes                             | -                                                                                                                                                                         |

| Read Runtime Counter       | 03H          | -                               | -                                                                                                                                                                         |

| Write OCD Control Register | 04H          | Yes                             | Cannot clear DBGMODE bit                                                                                                                                                  |

| Read OCD Control Register  | 05H          | Yes                             | -                                                                                                                                                                         |

| Write Program Counter      | 06H          | -                               | Disabled                                                                                                                                                                  |

| Read Program Counter       | 07H          | -                               | Disabled                                                                                                                                                                  |

| Write Register             | 08H          | -                               | Only writes of the Flash Memory Control<br>registers are allowed. Additionally, only the<br>Mass Erase command is allowed to be<br>written to the Flash Control register. |

| Read Register              | 09H          | -                               | Disabled                                                                                                                                                                  |

#### Table 93. On-Chip Debugger Commands

RPEN—Read Protect Option Bit Enabled 0 = The Read Protect Option Bit is disabled (1). 0 = The Read Protect Option Bit is enabled (0), disabling many OCD commands. Reserved

These bits are always 0.

# **OCD Watchpoint Control Register**

The OCD Watchpoint Control register is used to configure the debug Watchpoint.

Table 96. OCD Watchpoint Control/Address (WPTCTL)

| BITS  | 7   | 6   | 5    | 4        | 3             | 2   | 1   | 0   |  |  |

|-------|-----|-----|------|----------|---------------|-----|-----|-----|--|--|

| FIELD | WPW | WPR | WPDM | Reserved | WPTADDR[11:8] |     |     |     |  |  |

| RESET | 0   | 0   | 0    | 0        | 0             | 0   | 0   | 0   |  |  |

| R/W   | R/W | R/W | R/W  | R/W      | R/W           | R/W | R/W | R/W |  |  |

WPW-Watchpoint Break on Write

This bit cannot be set if the Read Protect Option Bit is enabled.

0 = Watchpoint Break on Register File write is disabled.

1 = Watchpoint Break on Register File write is enabled.

WPR-Watchpoint Break on Read

This bit cannot be set if the Read Protect Option Bit is enabled.

0 = Watchpoint Break on Register File read is disabled.

1 = Watchpoint Break on Register File write is enabled.

#### WPDM-Watchpoint Data Match

If this bit is set, then the Watchpoint only generates a Debug Break if the data being read or written matches the specified Watchpoint data. Either the WPR and/or WPW bits must also be set for this bit to affect operation. This bit cannot be set if the Read Protect Option Bit is enabled.

0 = Watchpoint Break on read and/or write does not require a data match.

1 = Watchpoint Break on read and/or write requires a data match.

Reserved

This bit is reserved and must be 0.

RADDR[11:8]—Register address

These bits specify the upper 4 bits of the Register File address to match when generating a Watchpoint Debug Break. The full 12-bit Register File address is given by {WPTCTL3:0], WPTADDR[7:0]}.

194

| Assembly        |                                                                                                                   | Addres       | Address Mode Opcode(s) |            | Flags |   |            |      | - Fetch Instr. |   |        |   |

|-----------------|-------------------------------------------------------------------------------------------------------------------|--------------|------------------------|------------|-------|---|------------|------|----------------|---|--------|---|

| Mnemonic        | Symbolic Operation                                                                                                | dst          | src                    | (Hex)      | С     | Z | S          | V    | D              | Н | Cycles |   |

| DA dst          | $dst \leftarrow DA(dst)$                                                                                          | R            |                        | 40         | *     | * | *          | Х    | -              | - | 2      | 2 |

|                 |                                                                                                                   | IR           |                        | 41         | -     |   |            |      |                |   | 2      | 3 |

| DEC dst         | $dst \leftarrow dst - 1$                                                                                          | R            |                        | 30         | -     | * | *          | *    | -              | - | 2      | 2 |

|                 |                                                                                                                   | IR           |                        | 31         | -     |   |            |      |                |   | 2      | 3 |

| DECW dst        | $dst \leftarrow dst - 1$                                                                                          | RR           |                        | 80         | -     | * | *          | *    | -              | - | 2      | 5 |

|                 |                                                                                                                   | IRR          |                        | 81         | -     |   |            |      |                |   | 2      | 6 |

| DI              | $IRQCTL[7] \leftarrow 0$                                                                                          |              |                        | 8F         | -     | - | -          | -    | -              | - | 1      | 2 |

| DJNZ dst, RA    | $dst \leftarrow dst - 1$<br>if $dst \neq 0$<br>PC \leftarrow PC + X                                               | r            |                        | 0A-FA      | -     | - | -          | -    | -              | - | 2      | 3 |

| EI              | $IRQCTL[7] \leftarrow 1$                                                                                          |              |                        | 9F         | -     | - | -          | -    | -              | - | 1      | 2 |

| HALT            | Halt Mode                                                                                                         |              |                        | 7F         | -     | - | -          | -    | -              | - | 1      | 2 |

| INC dst         | $dst \leftarrow dst + 1$                                                                                          | R            |                        | 20         | -     | * | *          | *    | -              | - | 2      | 2 |

|                 |                                                                                                                   | IR           |                        | 21         | -     |   |            |      |                |   | 2      | 3 |

|                 |                                                                                                                   | r            |                        | 0E-FE      | -     |   |            |      |                |   | 1      | 2 |

| INCW dst        | $dst \leftarrow dst + 1$                                                                                          | RR           |                        | A0         | -     | * | *          | *    | -              | - | 2      | 5 |

|                 |                                                                                                                   | IRR          |                        | A1         | -     |   |            |      |                |   | 2      | 6 |

| IRET            | $FLAGS \leftarrow @SP$ $SP \leftarrow SP + 1$ $PC \leftarrow @SP$ $SP \leftarrow SP + 2$ $IRQCTL[7] \leftarrow 1$ |              |                        | BF         | *     | * | *          | *    | *              | * | 1      | 5 |

| JP dst          | $PC \leftarrow dst$                                                                                               | DA           |                        | 8D         | -     | - | -          | -    | -              | - | 3      | 2 |

|                 |                                                                                                                   | IRR          |                        | C4         | -     |   |            |      |                |   | 2      | 3 |

| JP cc, dst      | if cc is true<br>PC ← dst                                                                                         | DA           |                        | 0D-FD      | -     | - | -          | -    | -              | - | 3      | 2 |

| JR dst          | $\text{PC} \leftarrow \text{PC} + \text{X}$                                                                       | DA           |                        | 8B         | -     | - | -          | -    | -              | - | 2      | 2 |

| JR cc, dst      | if cc is true<br>PC $\leftarrow$ PC + X                                                                           | DA           |                        | 0B-FB      | -     | - | -          | -    | -              | - | 2      | 2 |

| Flags Notation: | * = Value is a function<br>- = Unaffected<br>X = Undefined                                                        | of the resul | t of the               | operation. |       |   | Res<br>Set | to 1 | 0              |   |        |   |

## Table 126. eZ8 CPU Instruction Summary (Continued)

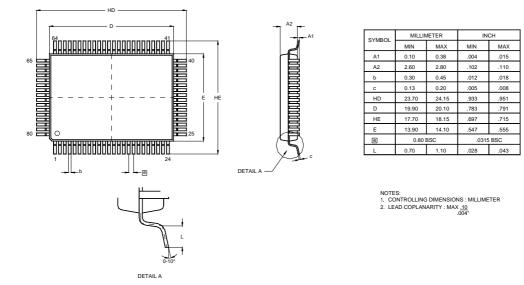

Figure 108 illustrates the 80-pin QFP (quad flat package) available for the Z8F4803 and Z8F6403 devices.

Figure 108. 80-Lead Quad-Flat Package (QFP)

| Part                                                          | Flash<br>KB (Bytes) | RAM<br>KB (Bytes) | Max. Speed<br>(MHz) | Temp<br>( <sup>0</sup> C) | Voltage<br>(V) | Package | Part Number    |  |  |  |

|---------------------------------------------------------------|---------------------|-------------------|---------------------|---------------------------|----------------|---------|----------------|--|--|--|

| Z8 Encore! with 64KB Flash, Standard Temperature              |                     |                   |                     |                           |                |         |                |  |  |  |

| Z8 Encore!®                                                   | 64 (65,536)         | 4 (4096)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PDIP-40 | Z8F6401PM020SC |  |  |  |

| Z8 Encore!®                                                   | 64 (65,536)         | 4 (4096)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-44 | Z8F6401AN020SC |  |  |  |

| Z8 Encore!®                                                   | 64 (65,536)         | 4 (4096)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-44 | Z8F6401VN020SC |  |  |  |

| Z8 Encore!®                                                   | 64 (65,536)         | 4 (4096)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-64 | Z8F6402AR020SC |  |  |  |

| Z8 Encore!®                                                   | 64 (65,536)         | 4 (4096)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-68 | Z8F6402VS020SC |  |  |  |

| Z8 Encore!®                                                   | 64 (65,536)         | 4 (4096)          | 20                  | 0 to +70                  | 3.0 - 3.6      | QFP-80  | Z8F6403FT020SC |  |  |  |

| Z8 Encore! <sup>®</sup> with 16KB Flash, Extended Temperature |                     |                   |                     |                           |                |         |                |  |  |  |

| Z8 Encore!®                                                   | 16 (16,384)         | 2 (2048)          | 20                  | -40 to +105               | 3.0 - 3.6      | PDIP-40 | Z8F1601PM020EC |  |  |  |

| Z8 Encore!®                                                   | 16 (16,384)         | 2 (2048)          | 20                  | -40 to +105               | 3.0 - 3.6      | LQFP-44 | Z8F1601AN020EC |  |  |  |

| Z8 Encore!®                                                   | 16 (16,384)         | 2 (2048)          | 20                  | -40 to +105               | 3.0 - 3.6      | PLCC-44 | Z8F1601VN020EC |  |  |  |

| Z8 Encore!®                                                   | 16 (16,384)         | 2 (2048)          | 20                  | -40 to +105               | 3.0 - 3.6      | LQFP-64 | Z8F1602AR020EC |  |  |  |

| Z8 Encore!®                                                   | 16 (16,384)         | 2 (2048)          | 20                  | -40 to +105               | 3.0 - 3.6      | PLCC-68 | Z8F1602VS020EC |  |  |  |

| Z8 Encore!®                                                   | with 24KB           | Flash, Exter      | nded Temper         | ature                     |                |         |                |  |  |  |

| Z8 Encore!®                                                   | 24 (24,576)         | 2 (2048)          | 20                  | -40 to +105               | 3.0 - 3.6      | PDIP-40 | Z8F2401PM020EC |  |  |  |

| Z8 Encore!®                                                   | 24 (24,576)         | 2 (2048)          | 20                  | -40 to +105               | 3.0 - 3.6      | LQFP-44 | Z8F2401AN020EC |  |  |  |

| Z8 Encore!®                                                   | 24 (24,576)         | 2 (2048)          | 20                  | -40 to +105               | 3.0 - 3.6      | PLCC-44 | Z8F2401VN020EC |  |  |  |

| Z8 Encore!®                                                   | 24 (24,576)         | 2 (2048)          | 20                  | -40 to +105               | 3.0 - 3.6      | LQFP-64 | Z8F2402AR020EC |  |  |  |

| Z8 Encore!®                                                   | 24 (24,576)         | 2 (2048)          | 20                  | -40 to +105               | 3.0 - 3.6      | PLCC-68 | Z8F2402VS020EC |  |  |  |

| Z8 Encore! with 32KB Flash, Extended Temperature              |                     |                   |                     |                           |                |         |                |  |  |  |

| Z8 Encore!®                                                   | 32 (32,768)         | 2 (2048)          | 20                  | -40 to +105               | 3.0 - 3.6      | PDIP-40 | Z8F3201PM020EC |  |  |  |

| Z8 Encore!®                                                   | 32 (32,768)         | 2 (2048)          | 20                  | -40 to +105               | 3.0 - 3.6      | LQFP-44 | Z8F3201AN020EC |  |  |  |

| Z8 Encore!®                                                   | 32 (32,768)         | 2 (2048)          | 20                  | -40 to +105               | 3.0 - 3.6      | PLCC-44 | Z8F3201VN020EC |  |  |  |

| Z8 Encore!®                                                   | 32 (32,768)         | 2 (2048)          | 20                  | -40 to +105               | 3.0 - 3.6      | LQFP-64 | Z8F3202AR020EC |  |  |  |

| Z8 Encore!®                                                   | 32 (32,768)         | 2 (2048)          | 20                  | -40 to +105               | 3.0 - 3.6      | PLCC-68 | Z8F3202VS020EC |  |  |  |

## Table 128. Ordering Information (Continued)

212