# E·XFL

#### Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Detai | ls |

|-------|----|

|       |    |

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                    |

| Number of I/O              | 46                                                            |

| Program Memory Size        | 64KB (64K x 8)                                                |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 4K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                     |

| Data Converters            | A/D 12x10b                                                    |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 68-LCC (J-Lead)                                               |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f6402vs020ec00tr |

|                            |                                                               |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table of Contents

| Introduction                       |

|------------------------------------|

| Features                           |

| Part Selection Guide               |

| Block Diagram                      |

| CPU and Peripheral Overview        |

| eZ8 CPU Features 3                 |

| General Purpose I/O 4              |

| Flash Controller                   |

| 10-Bit Analog-to-Digital Converter |

| UARTs                              |

| I <sup>2</sup> C                   |

| Serial Peripheral Interface        |

| Timers                             |

| Interrupt Controller 5             |

| Reset Controller                   |

| On-Chip Debugger 5                 |

| DMA Controller                     |

| Signal and Pin Descriptions        |

| Overview                           |

| Available Packages                 |

| Pin Configurations                 |

| Signal Descriptions                |

| Pin Characteristics                |

| Address Space                      |

| Overview                           |

| Register File                      |

| Program Memory                     |

| Data Memory                        |

| Register File Address Map0         |

| Reset and Stop Mode Recovery       |

| Overview                           |

| Reset Types                        |

| System and Short Resets            |

| Reset Sources                      |

| Power-On Reset                     |

| Voltage Brown-Out Reset            |

| Watch-Dog Timer Reset              |

## Introduction

The Z8 Encore!<sup>®</sup> MCU family of products are the first in a line of ZiLOG microcontroller products based upon the new 8-bit eZ8 CPU. The Z8F640x/Z8F480x/Z8F320x/Z8F240x/Z8F160x products are referred to collectively as either Z8 Encore!<sup>®</sup> or the Z8F640x family. The Z8F640x family of products introduce Flash memory to ZiLOG's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8 CPU is upward compatible with existing Z8 instructions. The rich peripheral set of the Z8F640x family makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices, and sensors.

## Features

- eZ8 CPU, 20 MHz operation

- 12-channel, 10-bit analog-to-digital converter (ADC)

- 3-channel DMA

- Up to 64KB Flash memory with in-circuit programming capability

- Up to 4KB register RAM

- Serial communication protocols

- Serial Peripheral Interface

- I<sup>2</sup>C

- Two full-duplex 9-bit UARTs

- 24 interrupts with programmable priority

- Three or four 16-bit timers with capture, compare, and PWM capability

- Single-pin On-Chip Debugger

- Two Infrared Data Association (IrDA)-compliant infrared encoder/decoders integrated with the UARTs

- Watch-Dog Timer (WDT) with internal RC oscillator

- Up to 60 I/O pins

- Voltage Brown-out Protection (VBO)

### **Power-On Reset**

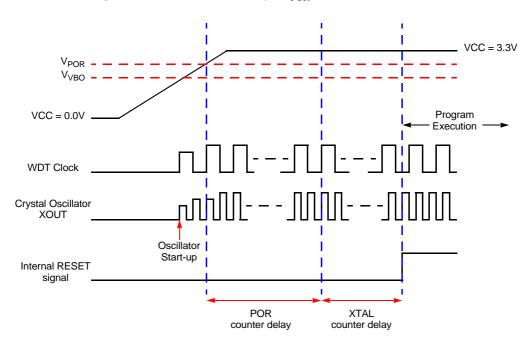

The Z8F640x family products contain an internal Power-On Reset (POR) circuit. The POR circuit monitors the supply voltage and holds the device in the Reset state until the supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold ( $V_{POR}$ ), the POR Counter is enabled and counts 514 cycles of the Watch-Dog Timer oscillator. After the POR counter times out, the XTAL Counter is enabled to count a total of 16 system clock pulses. The Z8F640x family device is held in the Reset state until both the POR Counter and XTAL counter have timed out. After the device exits the Power-On Reset state, the eZ8 CPU fetches the Reset vector. Following Power-On Reset, the POR status bit in the Watch-Dog Timer Control (WDTCTL) register is set to 1.

Figure 62 illustrates Power-On Reset operation. Refer to the **Electrical Characteristics** chapter for the POR threshold voltage ( $V_{POR}$ ).

Figure 62. Power-On Reset Operation (not to scale)

## Voltage Brown-Out Reset

The devices in the Z8F640x family provide low Voltage Brown-Out (VBO) protection. The VBO circuit senses when the supply voltage drops to an unsafe level (below the VBO

### **Interrupt Request 2 Register**

The Interrupt Request 2 (IRQ2) register (Table 25) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 1 register to determine if any interrupt requests are pending.

Table 25. Interrupt Request 2 Register (IRQ2)

| BITS  | 7   | 6     | 5     | 4    | 3    | 2    | 1    | 0    |  |  |  |

|-------|-----|-------|-------|------|------|------|------|------|--|--|--|

| FIELD | T3I | U1RXI | UITXI | DMAI | PC3I | PC2I | PC1I | PC0I |  |  |  |

| RESET | 0   | 0     | 0     | 0    | 0    | 0    | 0    | 0    |  |  |  |

| R/W   | R/W | R/W   | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  |  |  |  |

| ADDR  |     | FC6H  |       |      |      |      |      |      |  |  |  |

T3I—Timer 3 Interrupt Request

- 0 = No interrupt request is pending for Timer 3.

- 1 = An interrupt request from Timer 3 is awaiting service.

U1RXI—UART 1 Receive Interrupt Request

- 0 = No interrupt request is pending for the UART1 receiver.

- 1 = An interrupt request from UART1 receiver is awaiting service.

- U1TXI-UART 1 Transmit Interrupt Request

- 0 = No interrupt request is pending for the UART 1 transmitter.

- 1 = An interrupt request from the UART 1 transmitter is awaiting service.

DMAI—DMA Interrupt Request

- 0 = No interrupt request is pending for the DMA.

- 1 = An interrupt request from the DMA is awaiting service.

PCxI—Port C Pin x Interrupt Request

- 0 = No interrupt request is pending for GPIO Port C pin *x*.

- 1 = An interrupt request from GPIO Port C pin x is awaiting service.

where *x* indicates the specific GPIO Port C pin number (0 through 3).

written during counting, the 8-bit written value is placed in the counter (High or Low Byte) at the next clock edge. The counter continues counting from the new value.

BITS 7 6 5 4 3 2 1 0 TH FIELD 0 0 0 0 0 0 0 0 RESET R/W R/W R/W R/W R/W R/W R/W R/W R/W F00H, F08H, F10H, F18H ADDR

Table 38. Timer 0-3 High Byte Register (TxH)

Table 39>. Timer 0-3 Low Byte Register (TxL)

| BITS  | 7   | 6                                                               | 5 | 4           | 3          | 2 | 1 | 0 |  |  |  |  |

|-------|-----|-----------------------------------------------------------------|---|-------------|------------|---|---|---|--|--|--|--|

| FIELD |     | TL                                                              |   |             |            |   |   |   |  |  |  |  |

| RESET | 0   | 0                                                               | 0 | 0           | 0          | 0 | 0 | 1 |  |  |  |  |

| R/W   | R/W | R/W         R/W         R/W         R/W         R/W         R/W |   |             |            |   |   |   |  |  |  |  |

| ADDR  |     |                                                                 |   | F01H, F09H, | F11H, F19H |   |   |   |  |  |  |  |

TH and TL—Timer High and Low Bytes

These 2 bytes, {TMRH[7:0], TMRL[7:0]}, contain the current 16-bit timer count value.

## **Timer Reload High and Low Byte Registers**

The Timer 0-3 Reload High and Low Byte (TxRH and TxRL) registers (Tables 40 and 41) store a 16-bit reload value, {TRH[7:0], TRL[7:0]}. Values written to the Timer Reload High Byte register are stored in a temporary holding register. When a write to the Timer Reload Low Byte register occurs, the temporary holding register value is written to the Timer High Byte register. This operation allows simultaneous updates of the 16-bit Timer Reload value.

In Compare mode, the Timer Reload High and Low Byte registers store the 16-bit Compare value.

In single-byte DMA transactions to the Timer Reload High Byte register, the temporary holding register is bypassed and the value is written directly to the register. If the DMA is

## **Timer 0-3 Control Registers**

The Timer 0-3 Control (TxCTL) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode.

BITS 7 4 3 2 1 0 6 5 TEN TPOL PRES TMODE FIELD 0 0 0 0 0 0 0 0 RESET R/W R/W R/W R/W R/W R/W R/W R/W R/W F07H, F0FH, F17H, F1FH ADDR

Table 44. Timer 0-3 Control Register (TxCTL)

TEN-Timer Enable

0 = Timer is disabled.

1 = Timer enabled to count.

TPOL-Timer Input/Output Polarity

Operation of this bit is a function of the current operating mode of the timer.

#### **One-Shot mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **Continuous mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **Counter mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **PWM mode**

0 = Timer Output is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload.

1 = Timer Output is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload.

Reserved These bits are reserved and must be 0.

## Watch-Dog Timer Reload Upper, High and Low Byte Registers

The Watch-Dog Timer Reload Upper, High and Low Byte (WDTU, WDTH, WDTL) registers (Tables 47 through 49) form the 24-bit reload value that is loaded into the Watch-Dog Timer when a WDT instruction executes. The 24-bit reload value is {WDTU[7:0], WDTH[7:0], WDTL[7:0]. Writing to these registers sets the desired Reload Value. Reading from these registers returns the current Watch-Dog Timer count value.

The 24-bit WDT Reload Value must not be set to a value less than 000004H or unpredictable behavior may result.

| BITS      | 7              | 6            | 5            | 4             | 3             | 2             | 1    | 0    |  |  |  |  |

|-----------|----------------|--------------|--------------|---------------|---------------|---------------|------|------|--|--|--|--|

| FIELD     | WDTU           |              |              |               |               |               |      |      |  |  |  |  |

| RESET     | 1              | 1            | 1            | 1             | 1             | 1             | 1    | 1    |  |  |  |  |

| R/W       | R/W*           | R/W*         | R/W*         | R/W*          | R/W*          | R/W*          | R/W* | R/W* |  |  |  |  |

| ADDR      | ADDR FF1H      |              |              |               |               |               |      |      |  |  |  |  |

| R/W* - Re | ad returns the | e current WD | T count valu | e. Write sets | the desired R | Reload Value. |      |      |  |  |  |  |

Table 47. Watch-Dog Timer Reload Upper Byte Register (WDTU)

## WDTU-WDT Reload Upper Byte

Most significant byte (MSB), Bits[23:16], of the 24-bit WDT reload value.

Table 48. Watch-Dog Timer Reload High Byte Register (WDTH)

| BITS      | 7              | 6            | 5            | 4             | 3             | 2            | 1    | 0    |  |  |  |

|-----------|----------------|--------------|--------------|---------------|---------------|--------------|------|------|--|--|--|

| DIIS      | /              | U            | 5            | -             | 5             | 4            | L    | U    |  |  |  |

| FIELD     | WDTH           |              |              |               |               |              |      |      |  |  |  |

| RESET     | 1              | 1            | 1            | 1             | 1             | 1            | 1    | 1    |  |  |  |

| R/W       | R/W*           | R/W*         | R/W*         | R/W*          | R/W*          | R/W*         | R/W* | R/W* |  |  |  |

| ADDR FF2H |                |              |              |               |               |              |      |      |  |  |  |

| R/W* - Re | ad returns the | e current WD | T count valu | e. Write sets | the desired R | eload Value. |      |      |  |  |  |

WDTH—WDT Reload High Byte

#### START-Send Start Condition

This bit sends the Start condition. Once asserted, it is cleared by the I<sup>2</sup>C Controller after it sends the START condition or by deasserting the IEN bit. After this bit is set, the Start condition is sent if there is data in the I<sup>2</sup>C Data or I<sup>2</sup>C Shift register. If there is no data in one of these registers, the I<sup>2</sup>C Controller waits until data is loaded. If this bit is set while the I<sup>2</sup>C Controller is shifting out data, it generates a START condition after the byte shifts and the acknowledge phase completed. If the STOP bit is also set, it also waits until the STOP condition is sent before the START condition. If this bit is 1, it cannot be cleared to 0 by writing to the register. This bit clears when the I<sup>2</sup>C is disabled.

#### STOP-Send Stop Condition

This bit causes the  $I^2C$  Controller to issue a Stop condition after the byte in the  $I^2C$  Shift register has completed transmission or after a byte has been received in a receive operation. Once set, this bit is reset by the  $I^2C$  Controller after a Stop condition has been sent or by deasserting the IEN bit. If this bit is 1, it cannot be cleared to 0 by writing to the register. This bit clears when the  $I^2C$  is disabled.

#### BIRQ-Baud Rate Generator Interrupt Request

This bit causes an interrupt to occur every time the baud rate generator counts down to zero. This bit allows the  $I^2C$  Controller to be used as an additional counter when it is not being used elsewhere. This bit must only be set when the  $I^2C$  Controller is disabled.

#### TXI-Enable TDRE interrupts

This bit enables interrupts when the I<sup>2</sup>C Data register is empty on the I<sup>2</sup>C Controller.

#### NAK—Send NAK

This bit sends a Not Acknowledge condition after the next byte of data has been read from the  $I^2C$  slave. Once asserted, it is deasserted after a Not Acknowledge is sent or the IEN bit is deasserted.

#### FLUSH-Flush Data

Setting this bit to 1 clears the I<sup>2</sup>C Data register and sets the TDRE bit to 1. This bit allows flushing of the I<sup>2</sup>C Data register when an NAK is received after the data has been sent to the I<sup>2</sup>C Data register. Reading this bit always returns 0.

## FILTEN—I<sup>2</sup>C Signal Filter Enable

Setting this bit to 1 enables low-pass digital filters on the SDA and SCL input signals. These filters reject any input pulse with periods less than a full system clock cycle. The filters introduce a 3-system clock cycle latency on the inputs.

1 = DMAx is enabled and initiates a data transfer upon receipt of a request from the trigger source.

#### DLE—DMAx Loop Enable

0 = DMAx reloads the original Start Address and is then disabled after the End Address data is transferred.

1 = DMAx, after the End Address data is transferred, reloads the original Start Address and continues operating.

DDIR—DMAx Data Transfer Direction

0 =Register File  $\rightarrow$  on-chip peripheral control register.

1 = on-chip peripheral control register  $\rightarrow$  Register File.

IRQEN—DMAx Interrupt Enable

0 = DMAx does not generate any interrupts.

1 = DMAx generates an interrupt when the End Address data is transferred.

WSEL-Word Select

0 = DMAx transfers a single byte per request.

1 = DMAx transfers a two-byte word per request. The address for the on-chip peripheral control register must be an even address.

#### RSS-Request Trigger Source Select

The Request Trigger Source Select field determines the peripheral that can initiate a DMA request transfer. The corresponding interrupts do not need to be enabled within the Interrupt Controller to initiate a DMA transfer. However, if the Request Trigger Source can enable or disable the interrupt request sent to the Interrupt Controller, the interrupt request must be enabled within the Request Trigger Source block.

- 000 = Timer 0.

- 001 = Timer 1.

- 010 = Timer 2.

- 011 = Timer 3.

100 = DMA0 Control register: UART0 Received Data register contains valid data. DMA1 Control register: UART0 Transmit Data register empty.

101 = DMA0 Control register: UART1 Received Data register contains valid data. DMA1 Control register: UART1 Transmit Data register empty.

110 = DMA0 Control register: I<sup>2</sup>C Receiver Interrupt. DMA1 Control register: I<sup>2</sup>C Transmitter Interrupt register empty.

111 = Reserved.

## DMAx I/O Address Register

The DMAx I/O Address register contains the low byte of the on-chip peripheral address for data transfer. The full 12-bit Register File address is given by {FH, DMAx\_IO[7:0]}.

132

ZILOG

## Analog-to-Digital Converter

## Overview

The Analog-to-Digital Converter (ADC) converts an analog input signal to a 10-bit binary number. The features of the sigma-delta ADC include:

- 12 analog input sources are multiplexed with general-purpose I/O ports

- Interrupt upon conversion complete

- Internal voltage reference generator

- Direct Memory Access (DMA) controller can automatically initiate data conversion and transfer of the data from 1 to 12 of the analog inputs.

## Architecture

Figure 83 illustrates the three major functional blocks (converter, analog multiplexer, and voltage reference generator) of the ADC. The ADC converts an analog input signal to its digital representation. The 12-input analog multiplexer selects one of the 12 analog input sources. The ADC requires an input reference voltage for the conversion. The voltage reference for the conversion may be input through the external VREF pin or generated internally by the voltage reference generator.

## Flash Memory

## **Overview**

The Z8F640x family features up to 64KB (65,536 bytes) of non-volatile Flash memory with read/write/erase capability. The Flash Memory can be programmed and erased in-circuit by either user code or through the On-Chip Debugger.

The Flash memory array is arranged in pages with 512 bytes per page. The 512-byte page is the minimum Flash block size that can be erased. Each page is divided into 8 rows of 64 bytes. The Flash memory also contains a High Sector that can be enabled for writes and erase separately from the rest of the Flash array. The first 2 bytes of the Flash Program memory are used as Option Bits. Refer to the **Option Bits** chapter for more information on their operation.

Table 83 describes the Flash memory configuration for each device in the Z8F640x family. Figure 84 illustrates the Flash memory arrangement.

| Part Number | Flash Size<br>KB (Bytes) | Flash<br>Pages | Program Memory<br>Addresses | Flash High Sector Size<br>KB (Bytes) | High Sector<br>Addresses |

|-------------|--------------------------|----------------|-----------------------------|--------------------------------------|--------------------------|

| Z8F160x     | 16 (16,384)              | 32             | 0000H - 3FFFH               | 1 (1024)                             | 3C00H - 3FFFH            |

| Z8F240x     | 24 (24,576)              | 48             | 0000H - 5FFFH               | 2 (2048)                             | 5800H - 5FFFH            |

| Z8F320x     | 32 (32,768)              | 64             | 0000H - 7FFFH               | 2 (2048)                             | 7800H - 7FFFH            |

| Z8F480x     | 48 (49,152)              | 96             | 0000H - BFFFH               | 4 (4096)                             | B000H - BFFFH            |

| Z8F640x     | 64 (65,536)              | 128            | 0000H - FFFFH               | 8 (8192)                             | E000H - FFFFH            |

#### Table 83. Z8F640x family Flash Memory Configurations

## Flash Page Select Register

The Flash Page Select register is used to select one of the 128 available Flash memory pages to be erased in a Page Erase operation. Each Flash Page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory having addresses with the most significant 7-bits given by FPS [6:0] are erased (all bytes written to FFH).

Table 87. Flash Page Select Register (FPS)

| BITS  | 7        | 6   | 5                       | 4  | 3  | 2 | 1 | 0 |  |  |  |

|-------|----------|-----|-------------------------|----|----|---|---|---|--|--|--|

| FIELD | Reserved |     | PAGE                    |    |    |   |   |   |  |  |  |

| RESET | 0        | 0   | 0                       | 0  | 0  | 0 | 0 | 0 |  |  |  |

| R/W   | R/W      | R/W | R/W R/W R/W R/W R/W R/W |    |    |   |   |   |  |  |  |

| ADDR  |          |     |                         | FF | 9H |   |   |   |  |  |  |

Reserved This bit is reserved and must be 0.

PAGE—Page Select

This 7-bit field identifies the Flash memory page for Page Erase operation. Program Memory Address[15:9] = PAGE[6:0]

## Operation

## **OCD** Interface

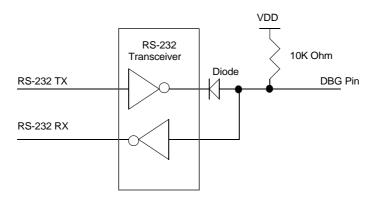

The On-Chip Debugger uses the DBG pin for communication with an external host. This one-pin interface is a bi-directional open-drain interface that transmits and receives data. Data transmission is half-duplex, in that transmit and receive cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin can interface the Z8F640x family device to the serial port of a host PC using minimal external hardware.Two different methods for connecting the DBG pin to an RS-232 interface are depicted in Figures 87 and 88.

## Caution:

For operation of the On-Chip Debugger, *all* power pins (VDD and AVDD) must be supplied with power, and *all* ground pins (VSS and AVSS) must be properly grounded.

The DBG pin is open-drain and must always be connected to  $V_{DD}$  through an external pull-up resistor to ensure proper operation.

Figure 87. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (1)

## **AC Characteristics**

The section provides information on the AC characteristics and timing of the Z8 Encore!<sup>TM</sup>. All AC timing information assumes a standard load of 50pF on all outputs.

## Table 102. AC Characteristics

|                     |                              | $V_{DD} = 3.0 - 3.6V$<br>$T_A = -40^{\circ}C \text{ to } 105^{\circ}C$ |         |       |                                                                                                       |  |

|---------------------|------------------------------|------------------------------------------------------------------------|---------|-------|-------------------------------------------------------------------------------------------------------|--|

| Symbol              | Parameter                    | Minimum                                                                | Maximum | Units | Conditions                                                                                            |  |

| F <sub>sysclk</sub> | System Clock Frequency       | -                                                                      | 20.0    | MHz   | Read-only from Flash memory.                                                                          |  |

|                     |                              | 0.032768                                                               | 20.0    | MHz   | Program or erasure of the Flash memory.                                                               |  |

| F <sub>XTAL</sub>   | Crystal Oscillator Frequency | 1.0                                                                    | 20.0    | MHz   | System clock frequencies below<br>the crystal oscillator minimum<br>require an external clock driver. |  |

| T <sub>XIN</sub>    | System Clock Period          | 50                                                                     | -       | ns    | $T_{CLK} = 1/F_{sysclk}$                                                                              |  |

| T <sub>XINH</sub>   | System Clock High Time       | 20                                                                     | 30      | ns    | T <sub>CLK</sub> = 50ns                                                                               |  |

| T <sub>XINL</sub>   | System Clock Low Time        | 20                                                                     | 30      | ns    | T <sub>CLK</sub> = 50ns                                                                               |  |

| T <sub>XINR</sub>   | System Clock Rise Time       | -                                                                      | 3       | ns    | T <sub>CLK</sub> = 50ns                                                                               |  |

| T <sub>XINF</sub>   | System Clock Fall Time       | -                                                                      | 3       | ns    | T <sub>CLK</sub> = 50ns                                                                               |  |

|                                               | $V_{DD} = 3.0 - 3.6V$<br>$T_A = -40^{\circ}C \text{ to } 105^{\circ}C$ |         |         |        |                                                                                                                                                                |

|-----------------------------------------------|------------------------------------------------------------------------|---------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                     | Minimum                                                                | Typical | Maximum | Units  | Notes                                                                                                                                                          |

| Writes to Single Address Before<br>Next Erase | -                                                                      | -       | 2       |        |                                                                                                                                                                |

| Flash Row Program Time                        | _                                                                      | _       | 8       | ms     | Cumulative program time for<br>single row cannot exceed limit<br>before next erase. This parameter<br>is only an issue when bypassing<br>the Flash Controller. |

| Data Retention                                | 100                                                                    | _       | -       | years  | 25 <sup>0</sup> C                                                                                                                                              |

| Endurance                                     | 10,000                                                                 | _       | -       | cycles | Program / erase cycles                                                                                                                                         |

#### Table 104. Flash Memory Electrical Characteristics and Timing (Continued)

### Table 105. Watch-Dog Timer Electrical Characteristics and Timing

|                  |                          | $V_{DD} = 3.0 - 3.6V$<br>$T_A = -40^{0}$ C to $105^{0}$ C |         |         |       |            |

|------------------|--------------------------|-----------------------------------------------------------|---------|---------|-------|------------|

| Symbol           | Parameter                | Minimum                                                   | Typical | Maximum | Units | Conditions |

| F <sub>WDT</sub> | WDT Oscillator Frequency | 25                                                        | 50      | 100     | kHz   |            |

#### Table 106. Analog-to-Digital Converter Electrical Characteristics and Timing

|                     |                                    | $V_{DD} = 3.0 - 3.6V$<br>$T_A = -40^{\circ}C \text{ to } 105^{\circ}C$ |              |                |          |                                                      |

|---------------------|------------------------------------|------------------------------------------------------------------------|--------------|----------------|----------|------------------------------------------------------|

| Symbol              | Parameter                          | Minimum                                                                | Typical      | Maximum        | Units    | Conditions                                           |

|                     | Resolution                         | -                                                                      | 10           | -              | bits     | External $V_{REF} = 3.0V$ ;<br>$R_S \le 3.0 k\Omega$ |

|                     | Differential Nonlinearity<br>(DNL) | -1.0                                                                   | _            | 1.0            | LSB      | External $V_{REF} = 3.0V$ ;<br>$R_S \ll 3.0 k\Omega$ |

|                     | Integral Nonlinearity (INL)        | -3.0                                                                   | _            | 3.0            | LSB      | External $V_{REF} = 3.0V$ ;<br>$R_S \le 3.0 k\Omega$ |

|                     | DC Offset Error                    | -35                                                                    | -            | 25             | mV       | 80-pin QFP and 64-pin LQFP packages.                 |

| <sup>1</sup> Analog | source impedance affects the A     | DC offset v                                                            | oltage (beca | ause of pin le | akage) a | nd input settling time.                              |

### Table 116. Additional Symbols

| Symbol | Definition                |

|--------|---------------------------|

| dst    | Destination Operand       |

| src    | Source Operand            |

| @      | Indirect Address Prefix   |

| SP     | Stack Pointer             |

| PC     | Program Counter           |

| FLAGS  | Flags Register            |

| RP     | Register Pointer          |

| #      | Immediate Operand Prefix  |

| В      | Binary Number Suffix      |

| %      | Hexadecimal Number Prefix |

| Н      | Hexadecimal Number Suffix |

|        |                           |

Assignment of a value is indicated by an arrow. For example,

$dst \leftarrow dst + src$

indicates the source data is added to the destination data and the result is stored in the destination location.

| Mnemonic | Operands | Instruction             |

|----------|----------|-------------------------|

| CCF      | —        | Complement Carry Flag   |

| DI       | —        | Disable Interrupts      |

| EI       | _        | Enable Interrupts       |

| HALT     | _        | Halt Mode               |

| NOP      | _        | No Operation            |

| RCF      | —        | Reset Carry Flag        |

| SCF      | _        | Set Carry Flag          |

| SRP      | src      | Set Register Pointer    |

| STOP     | —        | Stop Mode               |

| WDT      | _        | Watch-Dog Timer Refresh |

#### **Table 121. CPU Control Instructions**

### Table 122. Load Instructions

| Mnemonic | Operands    | Instruction                                                            |

|----------|-------------|------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                  |

| LD       | dst, src    | Load                                                                   |

| LDC      | dst, src    | Load Constant to/from Program Memory                                   |

| LDCI     | dst, src    | Load Constant to/from Program Memory and Auto-Increment<br>Addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                 |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-Increment<br>Addresses |

| LDX      | dst, src    | Load using Extended Addressing                                         |

| LEA      | dst, X(src) | Load Effective Address                                                 |

| POP      | dst         | Рор                                                                    |

| POPX     | dst         | Pop using Extended Addressing                                          |

| PUSH     | src         | Push                                                                   |

| PUSHX    | src         | Push using Extended Addressing                                         |

## Packaging

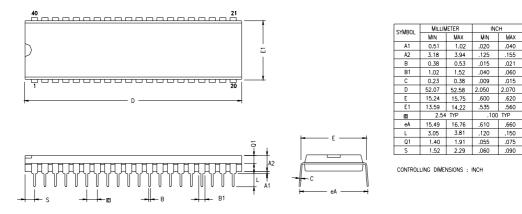

Figure 103 illustrates the 40-pin PDIP (plastic dual-inline package) available for the Z8F1601, Z8F2401, Z8F3201, Z8F4801, and Z8F6401 devices.

Figure 103. 40-Lead Plastic Dual-Inline Package (PDIP)

### Z8F640x/Z8F480x/Z8F320x/Z8F240x/Z8F160x Z8 Encore!®

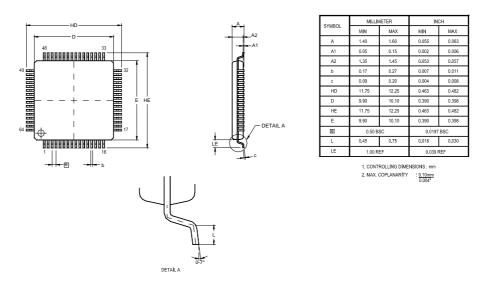

Figure 105 illustrates the 64-pin LQFP (low-profile quad flat package) available for the Z8F1602, Z8F2402, Z8F3202, Z8F4802, and Z8F6402 devices.

Figure 106. 64-Lead Low-Profile Quad Flat Package (LQFP)

## **Customer Feedback Form**

## The Z8 Encore!™ Product Specification

If you experience any problems while operating this product, or if you note any inaccuracies while reading this Product Specification, please copy and complete this form, then mail or fax it to ZiLOG (see *Return Information*, below). We also welcome your suggestions!

## **Customer Information**

| Name           | Country |

|----------------|---------|

| Company        | Phone   |

| Address        | Fax     |

| City/State/Zip | E-Mail  |

## **Product Information**

| Part #, Serial #, Board Fab #, or Rev. # |  |  |

|------------------------------------------|--|--|

| Software Version                         |  |  |

| Document Number                          |  |  |

| Host Computer Description/Type           |  |  |

## **Return Information**

ZiLOG 532 Race Street San Jose, CA 95126 Fax: (408) 558-8536 Email: tools@zilog.com