#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                    |

| Number of I/O              | 60                                                            |

| Program Memory Size        | 64KB (64K x 8)                                                |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 4K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                     |

| Data Converters            | A/D 12x10b                                                    |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | 0°C ~ 70°C (TA)                                               |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 80-BQFP                                                       |

| Supplier Device Package    | •                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f6403ft020sc00tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Option Bits                                                 |

|-------------------------------------------------------------|

| Overview                                                    |

| Operation                                                   |

| Option Bit Configuration By Reset                           |

| Option Bit Address Space                                    |

| Program Memory Address 0000H 149                            |

| Program Memory Address 0001H 150                            |

| On-Chip Debugger                                            |

| Overview                                                    |

| Architecture                                                |

| Operation                                                   |

| OCD Interface                                               |

| Debug Mode                                                  |

| OCD Data Format                                             |

| OCD Auto-Baud Detector/Generator                            |

| OCD Serial Errors 155                                       |

| Breakpoints                                                 |

| Watchpoints                                                 |

| Runtime Counter                                             |

| On-Chip Debugger Commands 156                               |

| On-Chip Debugger Control Register Definitions               |

| OCD Control Register 161                                    |

| OCD Status Register 162                                     |

| OCD Watchpoint Control Register                             |

| OCD Watchpoint Address Register                             |

| OCD Watchpoint Data Register                                |

| On-Chip Oscillator                                          |

| 20MHz Crystal Oscillator Operation                          |

| Electrical Characteristics                                  |

| Absolute Maximum Ratings 167                                |

| DC Characteristics                                          |

| AC Characteristics                                          |

| On-Chip Peripheral AC and DC Electrical Characteristics 173 |

| General Purpose I/O Port Input Data Sample Timing           |

| General Purpose I/O Port Output Timing 177                  |

| On-Chip Debugger Timing 178                                 |

| SPI Master Mode Timing 179                                  |

| SPI Slave Mode Timing 180                                   |

| I2C Timing                                                  |

| eZ8 CPU Instruction Set                                     |

| Assembly Language Programming Introduction                  |

## **Serial Peripheral Interface**

The serial peripheral interface (SPI) allows the Z8 Encore!<sup>®</sup> to exchange data between other peripheral devices such as EEPROMs, A/D converters and ISDN devices. The SPI is a full-duplex, synchronous, character-oriented channel that supports a four-wire interface.

## Timers

Up to four 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in One-Shot, Continuous, Gated, Capture, Compare, Capture and Compare, and PWM modes. Only 3 timers (Timers 0-2) are available in the 40- and 44-pin packages.

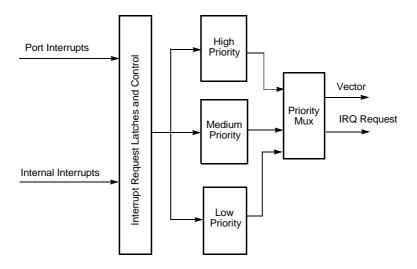

## Interrupt Controller

The Z8F640x family products support up to 24 interrupts. These interrupts consist of 12 internal and 12 general-purpose I/O pins. The interrupts have 3 levels of programmable interrupt priority.

## **Reset Controller**

The Z8F640x family can be reset using the RESET pin, power-on reset, Watch-Dog Timer (WDT), Stop mode exit, or Voltage Brown-Out (VBO) warning signal.

## **On-Chip Debugger**

The Z8 Encore!<sup>®</sup> features an integrated On-Chip Debugger (OCD). The OCD provides a rich set of debugging capabilities, such as reading and writing registers, programming the Flash, setting breakpoints and executing code. A single-pin interface provides communication to the OCD.

## **DMA Controller**

The Z8F640x family features three channels of DMA. Two of the channels are for register RAM to and from I/O operations. The third channel automatically controls the transfer of data from the ADC to the memory.

| Address (Hex)   | <b>Register Description</b>        | Mnemonic  | Reset (Hex) | Page # |

|-----------------|------------------------------------|-----------|-------------|--------|

| F62             | SPI Status                         | SPISTAT   | 01          | 108    |

| F63             | SPI Mode                           | SPIMODE   | 00          | 109    |

| F64-F65         | Reserved                           |           | XX          |        |

| F66             | SPI Baud Rate High Byte            | SPIBRH    | FF          | 110    |

| F67             | SPI Baud Rate Low Byte             | SPIBRL    | FF          | 110    |

| F68-F69         | Reserved                           | —         | XX          |        |

| Analog-to-Digit | al Converter (ADC)                 |           |             |        |

| F70             | ADC Control                        | ADCCTL    | 20          | 135    |

| F71             | Reserved                           |           | XX          |        |

| F72             | ADC Data High Byte                 | ADCD_H    | XX          | 137    |

| F73             | ADC Data Low Bits                  | ADCD_L    | XX          | 137    |

| F74-FAF         | Reserved                           | _         | XX          |        |

| DMA 0           |                                    |           |             |        |

| FB0             | DMA0 Control                       | DMA0CTL   | 00          | 124    |

| FB1             | DMA0 I/O Address                   | DMA0IO    | XX          | 125    |

| FB2             | DMA0 End/Start Address High Nibble | DMA0H     | XX          | 126    |

| FB3             | DMA0 Start Address Low Byte        | DMA0START | XX          | 127    |

| FB4             | DMA0 End Address Low Byte          | DMA0END   | XX          | 128    |

| DMA 1           |                                    |           |             |        |

| FB8             | DMA1 Control                       | DMA1CTL   | 00          | 124    |

| FB9             | DMA1 I/O Address                   | DMA1IO    | XX          | 125    |

| FBA             | DMA1 End/Start Address High Nibble | DMA1H     | XX          | 126    |

| FBB             | DMA1 Start Address Low Byte        | DMA1START | XX          | 127    |

| FBC             | DMA1 End Address Low Byte          | DMA1END   | XX          | 128    |

| DMA ADC         |                                    |           |             |        |

| FBD             | DMA_ADC Address                    | DMAA_ADDR | XX          | 128    |

| FBE             | DMA_ADC Control                    | DMAACTL   | 00          | 130    |

| FBF             | DMA_ADC Status                     | DMAASTAT  | 00          | 131    |

| Interrupt Conti | oller                              |           |             |        |

| FC0             | Interrupt Request 0                | IRQ0      | 00          | 48     |

| FC1             | IRQ0 Enable High Bit               | IRQ0ENH   | 00          | 51     |

| FC2             | IRQ0 Enable Low Bit                | IRQ0ENL   | 00          | 51     |

| FC3             | Interrupt Request 1                | IRQ1      | 00          | 49     |

| FC4             | IRQ1 Enable High Bit               | IRQIENH   | 00          | 52     |

| FC5             | IRQ1 Enable Low Bit                | IRQIENL   | 00          | 52     |

| FC6             | Interrupt Request 2                | IRQ2      | 00          | 50     |

| FC7             | IRQ2 Enable High Bit               | IRQ2ENH   | 00          | 53     |

| FC8             | IRQ2 Enable Low Bit                | IRQ2ENL   | 00          | 53     |

| FC9-FCC         | Reserved                           | _         | XX          |        |

| FCD             | Interrupt Edge Select              | IRQES     | 00          | 54     |

## Table 6. Register File Address Map (Continued)

| Address (Hex) | Register Description                  | Mnemonic | Reset (Hex) | Page #           |

|---------------|---------------------------------------|----------|-------------|------------------|

| FED           | Port H Control                        | PHCTL    | 00          | 38               |

| FEE           | Port H Input Data                     | PHIN     | XX          | 42               |

| FEF           | Port H Output Data                    | PHOUT    | 00          | 43               |

| Watch-Dog Tim | ner (WDT)                             |          |             |                  |

| FF0           | Watch-Dog Timer Control               | WDTCTL   | XXX00000b   | 75               |

| FF1           | Watch-Dog Timer Reload Upper Byte     | WDTU     | FF          | 76               |

| FF2           | Watch-Dog Timer Reload High Byte      | WDTH     | FF          | 76               |

| FF3           | Watch-Dog Timer Reload Low Byte       | WDTL     | FF          | 76               |

| FF4FF7        | Reserved                              | —        | XX          |                  |

| Flash Memory  | Controller                            |          |             |                  |

| FF8           | Flash Control                         | FCTL     | 00          | 144              |

| FF8           | Flash Status                          | FSTAT    | 00          | 145              |

| FF9           | Flash Page Select                     | FPS      | 00          | 146              |

| FFA           | Flash Programming Frequency High Byte | FFREQH   | 00          | 147              |

| FFB           | Flash Programming Frequency Low Byte  | FFREQL   | 00          | 147              |

| eZ8 CPU       |                                       |          |             |                  |

| FFC           | Flags                                 | _        | XX          | Refer to the eZ8 |

| FFD           | Register Pointer                      | RP       | XX          | CPU User         |

| FFE           | Stack Pointer High Byte               | SPH      | XX          | Manual           |

| FFF           | Stack Pointer Low Byte                | SPL      | XX          |                  |

| XX=Undefined  |                                       |          |             |                  |

## Table 6. Register File Address Map (Continued)

24

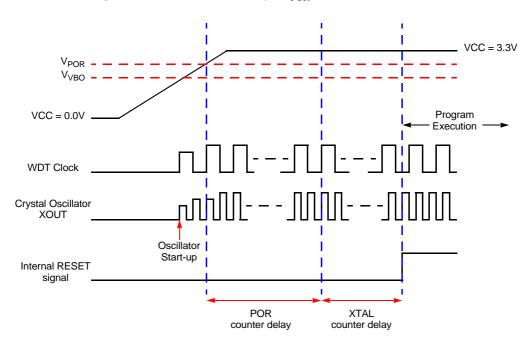

## **Power-On Reset**

The Z8F640x family products contain an internal Power-On Reset (POR) circuit. The POR circuit monitors the supply voltage and holds the device in the Reset state until the supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold ( $V_{POR}$ ), the POR Counter is enabled and counts 514 cycles of the Watch-Dog Timer oscillator. After the POR counter times out, the XTAL Counter is enabled to count a total of 16 system clock pulses. The Z8F640x family device is held in the Reset state until both the POR Counter and XTAL counter have timed out. After the device exits the Power-On Reset state, the eZ8 CPU fetches the Reset vector. Following Power-On Reset, the POR status bit in the Watch-Dog Timer Control (WDTCTL) register is set to 1.

Figure 62 illustrates Power-On Reset operation. Refer to the **Electrical Characteristics** chapter for the POR threshold voltage ( $V_{POR}$ ).

Figure 62. Power-On Reset Operation (not to scale)

## Voltage Brown-Out Reset

The devices in the Z8F640x family provide low Voltage Brown-Out (VBO) protection. The VBO circuit senses when the supply voltage drops to an unsafe level (below the VBO

# Architecture

Figure 65 illustrates a block diagram of the interrupt controller.

Figure 65. Interrupt Controller Block Diagram

# Operation

## **Master Interrupt Enable**

The master interrupt enable bit (IRQE) in the Interrupt Control register globally enables and disables interrupts.

Interrupts are globally enabled by any of the following actions:

- Execution of an EI (Enable Interrupt) instruction

- Execution of an IRET (Return from Interrupt) instruction

- Writing a 1 to the IRQE bit in the Interrupt Control register

Interrupts are globally disabled by any of the following actions:

- Execution of a DI (Disable Interrupt) instruction

- eZ8 CPU acknowledgement of an interrupt service request from the interrupt controller

- Writing a 0 to the IRQE bit in the Interrupt Control register

- Reset

# **Interrupt Control Register Definitions**

For all interrupts other than the Watch-Dog Timer interrupt, the interrupt control registers enable individual interrupts, set interrupt priorities, and indicate interrupt requests.

## Interrupt Request 0 Register

The Interrupt Request 0 (IRQ0) register (Table 23) stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 0 register to determine if any interrupt requests are pending

| BITS  | 7   | 6    | 5   | 4     | 3     | 2    | 1    | 0    |  |  |

|-------|-----|------|-----|-------|-------|------|------|------|--|--|

| FIELD | T2I | T1I  | TOI | U0RXI | U0TXI | I2CI | SPII | ADCI |  |  |

| RESET | 0   | 0    | 0   | 0     | 0     | 0    | 0    | 0    |  |  |

| R/W   | R/W | R/W  | R/W | R/W   | R/W   | R/W  | R/W  | R/W  |  |  |

| ADDR  |     | FC0H |     |       |       |      |      |      |  |  |

Table 23. Interrupt Request 0 Register (IRQ0)

T2I—Timer 2 Interrupt Request

0 = No interrupt request is pending for Timer 2.

1 = An interrupt request from Timer 2 is awaiting service.

T1I-Timer 1 Interrupt Request

0 = No interrupt request is pending for Timer 1.

1 = An interrupt request from Timer 1 is awaiting service.

T0I-Timer 0 Interrupt Request

0 = No interrupt request is pending for Timer 0.

1 = An interrupt request from Timer 0 is awaiting service.

U0RXI—UART 0 Receiver Interrupt Request

0 = No interrupt request is pending for the UART 0 receiver.

1 = An interrupt request from the UART 0 receiver is awaiting service.

U0TXI-UART 0 Transmitter Interrupt Request

0 = No interrupt request is pending for the UART 0 transmitter.

1 = An interrupt request from the UART 0 transmitter is awaiting service.

| BITS  | 7     | 6      | 5      | 4      | 3     | 2     | 1     | 0     |  |  |  |

|-------|-------|--------|--------|--------|-------|-------|-------|-------|--|--|--|

| FIELD | T3ENH | U1RENH | UITENH | DMAENH | C3ENH | C2ENH | C1ENH | C0ENH |  |  |  |

| RESET | 0     | 0      | 0      | 0      | 0     | 0     | 0     | 0     |  |  |  |

| R/W   | R/W   | R/W    | R/W    | R/W    | R/W   | R/W   | R/W   | R/W   |  |  |  |

| ADDR  |       | FC7H   |        |        |       |       |       |       |  |  |  |

Table 33. IRQ2 Enable High Bit Register (IRQ2ENH)

T3ENH—Timer 3 Interrupt Request Enable High Bit U1RENH—UART 1 Receive Interrupt Request Enable High Bit U1TENH—UART 1 Transmit Interrupt Request Enable High Bit DMAENH—DMA Interrupt Request Enable High Bit C3ENH—Port C3 Interrupt Request Enable High Bit C2ENH—Port C2 Interrupt Request Enable High Bit C1ENH—Port C1 Interrupt Request Enable High Bit C0ENH—Port C0 Interrupt Request Enable High Bit

Table 34. IRQ2 Enable Low Bit Register (IRQ2ENL)

| BITS  | 7     | 6      | 5      | 4      | 3     | 2     | 1     | 0     |  |

|-------|-------|--------|--------|--------|-------|-------|-------|-------|--|

| FIELD | T3ENL | U1RENL | UITENL | DMAENL | C3ENL | C2ENL | C1ENL | C0ENL |  |

| RESET | 0     | 0      | 0      | 0      | 0     | 0     | 0     | 0     |  |

| R/W   | R/W   | R/W    | R/W    | R/W    | R/W   | R/W   | R/W   | R/W   |  |

| ADDR  | FC8H  |        |        |        |       |       |       |       |  |

T3ENL—Timer 3 Interrupt Request Enable Low Bit

U1RENL-UART 1 Receive Interrupt Request Enable Low Bit

U1TENL-UART 1 Transmit Interrupt Request Enable Low Bit

DMAENL—DMA Interrupt Request Enable Low Bit

C3ENL—Port C3 Interrupt Request Enable Low Bit

C2ENL—Port C2 Interrupt Request Enable Low Bit

C1ENL—Port C1 Interrupt Request Enable Low Bit

COENL-Port CO Interrupt Request Enable Low Bit

## Interrupt Edge Select Register

The Interrupt Edge Select (IRQES) register (Table 35) determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port input pin. The

- Select either the rising edge or falling edge of the Timer Input signal for the count. This also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function does not have to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in Counter mode. After the first timer Reload in Counter mode, counting always begins at the reset value of 0001H. Generally, in Counter mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If desired, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control register to enable the timer.

In Counter mode, the number of Timer Input transitions since the timer start is given by the following equation:

#### Counter Mode Timer Input Transitions = Current Count Value – Start Value

#### **PWM Mode**

In PWM mode, the timer outputs a Pulse-Width Modulator (PWM) output signal through a GPIO Port pin. The timer input is the system clock. The timer first counts up to the 16bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the Reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control register is set to 1, the Timer Output signal begins as a High (1) and then transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the Reload value and is reset to 0001H.

If the TPOL bit in the Timer Control register is set to 0, the Timer Output signal begins as a Low (0) and then transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the Reload value and is reset to 0001H.

The steps for configuring a timer for PWM mode and initiating the PWM operation are as follows:

1. Write to the Timer Control register to:

69

## Timer 0-3 PWM High and Low Byte Registers

The Timer 0-3 PWM High and Low Byte (TxPWMH and TxPWML) registers (Tables 42 and 43) are used for Pulse-Width Modulator (PWM) operations. These registers also store the Capture values for the Capture and Capture/Compare modes.

| BITS  | 7    | 6                      | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-------|------|------------------------|-----|-----|-----|-----|-----|-----|--|--|

| FIELD | PWMH |                        |     |     |     |     |     |     |  |  |

| RESET | 0    | 0                      | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

| R/W   | R/W  | R/W                    | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| ADDR  |      | F04H, F0CH, F14H, F1CH |     |     |     |     |     |     |  |  |

#### Table 42. Timer 0-3 PWM High Byte Register (TxPWMH)

#### Table 43. Timer 0-3 PWM Low Byte Register (TxPWML)

| BITS  | 7    | 6                      | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-------|------|------------------------|-----|-----|-----|-----|-----|-----|--|--|

| FIELD | PWML |                        |     |     |     |     |     |     |  |  |

| RESET | 0    | 0                      | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

| R/W   | R/W  | R/W                    | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| ADDR  |      | F05H, F0DH, F15H, F1DH |     |     |     |     |     |     |  |  |

PWMH and PWML—Pulse-Width Modulator High and Low Bytes

These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output value is set by the TPOL bit in the Timer Control Register (TxCTL) register.

The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operating in Capture or Capture/Compare modes.

received a byte of data. When active, this bit causes the  $I^2C$  Controller to generate an interrupt. This bit is cleared by reading the  $I^2C$  Data register.

#### ACK—Acknowledge

This bit indicates the status of the Acknowledge for the last byte transmitted or received. When set, this bit indicates that an Acknowledge was received for the last byte transmitted or received.

#### 10B-10-Bit Address

This bit indicates whether a 10- or 7-bit address is being transmitted. After the START bit is set, if the five most-significant bits of the address are 11110B, this bit is set. When set, it is reset once the first byte of the address has been sent.

#### RD—Read

This bit indicates the direction of transfer of the data. It is active high during a read. The status of this bit is determined by the least-significant bit of the  $I^2C$  Shift register after the START bit is set.

TAS—Transmit Address State

This bit is active high while the address is being shifted out of the I<sup>2</sup>C Shift register.

DSS—Data Shift State

This bit is active high while data is being transmitted to or from the I<sup>2</sup>C Shift register.

#### NCKI-NACK Interrupt

This bit is set high when a Not Acknowledge condition is received or sent and neither the START nor the STOP bit is active. When set, this bit generates an interrupt that can only be cleared by setting the START or STOP bit, allowing the user to specify whether he wants to perform a STOP or a repeated START.

# I<sup>2</sup>C Control Register

The I<sup>2</sup>C Control register enables the I<sup>2</sup>C operation.

| BITS  | 7    | 6     | 5    | 4    | 3   | 2   | 1     | 0      |  |

|-------|------|-------|------|------|-----|-----|-------|--------|--|

| FIELD | IEN  | START | STOP | BIRQ | TXI | NAK | FLUSH | FILTEN |  |

| RESET | 0    | 0     | 0    | 0    | 0   | 0   | 0     | 0      |  |

| R/W   | R/W  | R/W   | R/W  | R/W  | R/W | R/W | R/W   | R/W    |  |

| ADDR  | F52H |       |      |      |     |     |       |        |  |

Table 68. I<sup>2</sup>C Control Register (I2CCTL)

IEN-I<sup>2</sup>C Enable

This bit enables the I<sup>2</sup>C transmitter and receiver.

If the current ADC Analog Input is not the highest numbered input to be converted, DMA\_ADC initiates data conversion in the next higher numbered ADC Analog Input.

# Configuring DMA\_ADC for Data Transfer

Follow these steps to configure and enable DMA\_ADC:

- 1. Write the DMA\_ADC Address register with the 7 most-significant bits of the Register File address for data transfers.

- 2. Write to the DMA\_ADC Control register to complete the following:

- Enable the DMA\_ADC interrupt request, if desired

- Select the number of ADC Analog Inputs to convert

- Enable the DMA\_ADC channel

**Caution:** When using the DMA\_ADC to perform conversions on multiple ADC inputs and the ADC\_IN field in the DMA\_ADC Control Register is greater than 000b, the Analog-to-Digital Converter must be configured for Single-Shot mode.

Continuous mode operation of the ADC can **only** be used in conjunction with DMA\_ADC if the ADC\_IN field in the DMA\_ADC Control Register is reset to 000b to enable conversion on ADC Analog Input 0 only.

# **DMA Control Register Definitions**

## DMAx Control Register

The DMAx Control register is used to enable and select the mode of operation for DMAx.

| BITS  | 7          | 6   | 5    | 4     | 3    | 2   | 1   | 0   |  |

|-------|------------|-----|------|-------|------|-----|-----|-----|--|

| FIELD | DEN        | DLE | DDIR | IRQEN | WSEL | RSS |     |     |  |

| RESET | 0          | 0   | 0    | 0     | 0    | 0   | 0   | 0   |  |

| R/W   | R/W        | R/W | R/W  | R/W   | R/W  | R/W | R/W | R/W |  |

| ADDR  | FB0H, FB8H |     |      |       |      |     |     |     |  |

Table 71. DMAx Control Register (DMAxCTL)

DEN—DMAx Enable

0 = DMAx is disabled and data transfer requests are disregarded.

## DMA\_ADC Control Register

The DMA\_ADC Control register enables and sets options (DMA enable and interrupt enable) for ADC operation.

| BITS  | 7    | 6     | 5    | 4     | 3      | 2   | 1   | 0   |  |

|-------|------|-------|------|-------|--------|-----|-----|-----|--|

| FIELD | DAEN | IRQEN | Rese | erved | ADC_IN |     |     |     |  |

| RESET | 0    | 0     | 0    | 0     | 0      | 0   | 0   | 0   |  |

| R/W   | R/W  | R/W   | R/W  | R/W   | R/W    | R/W | R/W | R/W |  |

| ADDR  | FBEH |       |      |       |        |     |     |     |  |

Table 78. DMA\_ADC Control Register (DMAACTL)

DAEN-DMA\_ADC Enable

$0 = DMA\_ADC$  is disabled and the ADC Analog Input Number (ADC\_IN) is reset to 0. 1 = DMA\\_ADC is enabled.

\_\_\_\_\_

IRQEN—Interrupt Enable

$0 = DMA\_ADC$  does not generate any interrupts.

1 = DMA\_ADC generates an interrupt after transferring data from the last ADC Analog Input specified by the ADC\_IN field.

Reserved

These bits are reserved and must be 0.

ADC\_IN—ADC Analog Input Number

These bits set the number of ADC Analog Inputs to be used in the continuous update (data conversion followed by DMA data transfer). The conversion always begins with ADC Analog Input 0 and then progresses sequentially through the other selected ADC Analog Inputs.

0000 = ADC Analog Input 0 updated.

0001 = ADC Analog Inputs 0-1 updated.

0010 = ADC Analog Inputs 0-2 updated.

0011 = ADC Analog Inputs 0-3 updated.

0100 = ADC Analog Inputs 0-4 updated.

0101 = ADC Analog Inputs 0-5 updated.

0110 = ADC Analog Inputs 0-6 updated.

0111 = ADC Analog Inputs 0-7 updated.

1000 = ADC Analog Inputs 0-8 updated.

1001 = ADC Analog Inputs 0-9 updated.

1010 = ADC Analog Inputs 0-10 updated.

1011 = ADC Analog Inputs 0-11 updated.

1100-1111 = Reserved.

## ADC Data High Byte Register

The ADC Data High Byte register contains the upper eight bits of the 10-bit ADC output. During a conversion, this value is invalid. Access to the ADC Data High Byte register is read-only. The full 10-bit ADC result is given by {ADCD\_H[7:0], ADCD\_L[7:6]}.

| BITS  | 7 | 6      | 5 | 4  | 3  | 2 1 |  |  |  |  |  |  |

|-------|---|--------|---|----|----|-----|--|--|--|--|--|--|

| FIELD |   | ADCD_H |   |    |    |     |  |  |  |  |  |  |

| RESET |   | Х      |   |    |    |     |  |  |  |  |  |  |

| R/W   |   | R      |   |    |    |     |  |  |  |  |  |  |

| ADDR  |   |        |   | F7 | 2H |     |  |  |  |  |  |  |

#### Table 81. ADC Data High Byte Register (ADCD\_H)

ADCD\_H—ADC Data High Byte

This byte contains the upper eight bits of the 10-bit ADC output. These bits are not valid during a conversion. These bits are undefined after a Reset.

## ADC Data Low Bits Register

The ADC Data Low Bits register contains the lower two bits of the conversion value. During a conversion this value is invalid. Access to the ADC Data Low Bits register is readonly. The full 10-bit ADC result is given by {ADCD\_H[7:0], ADCD\_L[7:6]}.

| BITS  | 7   | 6    | 5        | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|-----|------|----------|---|---|---|---|---|--|--|--|

| FIELD | ADC | D_L  | Reserved |   |   |   |   |   |  |  |  |

| RESET | 2   | K    | Х        |   |   |   |   |   |  |  |  |

| R/W   | I   | ર    | R        |   |   |   |   |   |  |  |  |

| ADDR  |     | F73H |          |   |   |   |   |   |  |  |  |

Table 82. ADC Data Low Bits Register (ADCD\_L)

## ADCD\_L—ADC Data Low Bits

These are the least significant two bits of the 10-bit ADC output. During a conversion, this value is invalid. These bits are undefined after a Reset.

#### Reserved

These bits are reserved and are always undefined.

## Flash Code Protection Using the Option Bits

The FHSWP and FWP Option Bits combine to provide three levels of Flash Program Memory protection as listed in Table 84. Refer to the **Option Bits** chapter for more information.

| FHSWP  | FWP | Flash Code Protection Description                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0   | Programming and erasure disabled for all of Flash Program Memory. In<br>user code programming, Page Erase, and Mass Erase are all disabled. Mass<br>Erase is available through the On-Chip Debugger.                                                                                                                                                                                                                                       |

| 1      | 0   | Programming and Page Erase are enabled for the High Sector of the Flash<br>Program Memory only. The High Sector on the Z8F640x family device<br>contains 1KB to 4KB of Flash with addresses at the top of the available<br>Flash memory. Programming and Page Erase are disabled for the other<br>portions of the Flash Program Memory. Mass erase through user code is<br>disabled. Mass Erase is available through the On-Chip Debugger. |

| 0 or 1 | 1   | Programming, Page Erase, and Mass Erase are enabled for all of Flash<br>Program Memory.                                                                                                                                                                                                                                                                                                                                                    |

Table 84. Flash Code Protection Using the Option Bits

#### Flash Code Protection Using the Flash Controller

At Reset, the Flash Controller locks to prevent accidental program or erasure of the Flash memory. To program or erase the Flash memory, unlock the Flash Controller by making two consecutive writes to the Flash Control register with the values 73H and 8CH, sequentially. After unlocking the Flash Controller, the Flash can be programmed or erased. When the Flash Controller is unlocked, any value written to the Flash Control register locks the Flash Controller. Writing the Mass Erase or Page Erase commands executes the function before locking the Flash Controller.

## **Byte Programming**

When the Flash Controller is unlocked, all writes to Program Memory program a byte into the Flash. An erased Flash byte contains all 1's (FFH). The programming operation can only be used to change bits from 1 to 0. To change a Flash bit (or multiple bits) from 0 to 1 requires execution of either the Page Erase or Mass Erase commands.

Byte Programming can be accomplished using the On-Chip Debugger's Write Memory command or eZ8 CPU execution of the LDC or LDCI instructions. Refer to the eZ8 CPU User Manual for a description of the LDC and LDCI instructions. While the Flash Controller programs the Flash memory, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. To exit programming mode and lock the Flash, write any value to the Flash Control register, except the Mass Erase or Page Erase commands.

```

DBG <-- 03H

DBG --> RuntimeCounter[15:8]

DBG --> RuntimeCounter[7:0]

```

• Write OCD Control Register (04H)—The Write OCD Control Register command writes the data that follows to the OCDCTL register. When the Read Protect Option Bit is enabled, the DBGMODE bit (OCDCTL[7]) can only be set to 1, it cannot be cleared to 0 and the only method of putting the Z8F640x family device back into normal operating mode is to reset the device.

```

DBG <-- 04H

DBG <-- OCDCTL[7:0]

```

• **Read OCD Control Register (05H)**—The Read OCD Control Register command reads the value of the OCDCTL register.

```

DBG <-- 05H

DBG --> OCDCTL[7:0]

```

• Write Program Counter (06H)—The Write Program Counter command writes the data that follows to the eZ8 CPU's Program Counter (PC). If the Z8F640x family device is not in Debug mode or if the Read Protect Option Bit is enabled, the Program Counter (PC) values are discarded.

```

DBG <-- 06H

DBG <-- ProgramCounter[15:8]

DBG <-- ProgramCounter[7:0]

```

• **Read Program Counter (07H)**—The Read Program Counter command reads the value in the eZ8 CPU's Program Counter (PC). If the Z8F640x family device is not in Debug mode or if the Read Protect Option Bit is enabled, this command returns FFFFH.

```

DEG <-- 07H

DEG --> ProgramCounter[15:8]

DEG --> ProgramCounter[7:0]

```

• Write Register (08H)—The Write Register command writes data to the Register File. Data can be written 1-256 bytes at a time (256 bytes can be written by setting size to zero). If the Z8F640x family device is not in Debug mode, the address and data values are discarded. If the Read Protect Option Bit is enabled, then only writes to the Flash Control Registers are allowed and all other register write data values are discarded.

```

DBG <-- 08H

DBG <-- {4'h0,Register Address[11:8]}

DBG <-- Register Address[7:0]

DBG <-- Size[7:0]

DBG <-- 1-256 data bytes

```

• **Read Register (09H)**—The Read Register command reads data from the Register File. Data can be read 1-256 bytes at a time (256 bytes can be read by setting size to

184

| Notation | Description                    | Operand | Range                                                                                                                     |

|----------|--------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------|

| b        | Bit                            | b       | b represents a value from 0 to 7 (000B to 111B).                                                                          |

| сс       | Condition Code                 | —       | See Condition Codes overview in the eZ8 CPU User Manual.                                                                  |

| DA       | Direct Address                 | Addrs   | Addrs. represents a number in the range of 0000H to FFFFH                                                                 |

| ER       | Extended Addressing Register   | Reg     | Reg. represents a number in the range of 000H to FFFH                                                                     |

| IM       | Immediate Data                 | #Data   | Data is a number between 00H to FFH                                                                                       |

| Ir       | Indirect Working Register      | @Rn     | n = 0 - 15                                                                                                                |

| IR       | Indirect Register              | @Reg    | Reg. represents a number in the range of 00H to FFH                                                                       |

| Irr      | Indirect Working Register Pair | @RRp    | p = 0, 2, 4, 6, 8, 10, 12, or 14                                                                                          |

| IRR      | Indirect Register Pair         | @Reg    | Reg. represents an even number in the range 00H to FEH                                                                    |

| p        | Polarity                       | р       | Polarity is a single bit binary value of either 0B or 1B.                                                                 |

| r        | Working Register               | Rn      | n = 0 - 15                                                                                                                |

| R        | Register                       | Reg     | Reg. represents a number in the range of 00H to FFH                                                                       |

| RA       | Relative Address               | Х       | X represents an index in the range of $+127$ to $-128$ which is an offset relative to the address of the next instruction |

| rr       | Working Register Pair          | RRp     | p = 0, 2, 4, 6, 8, 10, 12, or 14                                                                                          |

| RR       | Register Pair                  | Reg     | Reg. represents an even number in the range of 00H to FEH                                                                 |

| Vector   | Vector Address                 | Vector  | Vector represents a number in the range of 00H to FFH                                                                     |

| X        | Indexed                        | #Index  | The register or register pair to be indexed is offset by<br>the signed Index value (#Index) in a +127 to -128<br>range.   |

### Table 115. Notational Shorthand

Table 116 contains additional symbols that are used throughout the Instruction Summary and Instruction Set Description sections.

## **Table 123. Logical Instructions**

| Mnemonic | Operands | Instruction                                    |

|----------|----------|------------------------------------------------|

| AND      | dst, src | Logical AND                                    |

| ANDX     | dst, src | Logical AND using Extended Addressing          |

| СОМ      | dst      | Complement                                     |

| OR       | dst, src | Logical OR                                     |

| ORX      | dst, src | Logical OR using Extended Addressing           |

| XOR      | dst, src | Logical Exclusive OR                           |

| XORX     | dst, src | Logical Exclusive OR using Extended Addressing |

Table 124. Program Control Instructions

| Mnemonic | Operands        | Instruction                   |  |  |  |  |

|----------|-----------------|-------------------------------|--|--|--|--|

| BRK      | _               | On-Chip Debugger Break        |  |  |  |  |

| BTJ      | p, bit, src, DA | Bit Test and Jump             |  |  |  |  |

| BTJNZ    | bit, src, DA    | Bit Test and Jump if Non-Zero |  |  |  |  |

| BTJZ     | bit, src, DA    | Bit Test and Jump if Zero     |  |  |  |  |

| CALL dst |                 | Call Procedure                |  |  |  |  |

| DJNZ     | dst, src, RA    | Decrement and Jump Non-Zero   |  |  |  |  |

| IRET     | _               | Interrupt Return              |  |  |  |  |

| JP       | dst             | Jump                          |  |  |  |  |

| JP cc    | dst             | Jump Conditional              |  |  |  |  |

| JR       | DA              | Jump Relative                 |  |  |  |  |

| JR cc    | DA              | Jump Relative Conditional     |  |  |  |  |

| RET      | _               | Return                        |  |  |  |  |

| TRAP     | vector          | Software Trap                 |  |  |  |  |

200

| Assembly        |                                                              | Address Mode |           | <b>Opcode</b> (s) | Flags |   |   |               |   | Fetch | Instr. |        |

|-----------------|--------------------------------------------------------------|--------------|-----------|-------------------|-------|---|---|---------------|---|-------|--------|--------|

| Mnemonic        | Symbolic Operation                                           | dst          | src       | (Hex)             |       | Z | S | V             | D | H     |        | Cycles |

| XOR dst, src    | $dst \leftarrow dst \ XOR \ src$                             | r            | r         | B2                | -     | * | * | 0             | - | -     | 2      | 3      |

|                 |                                                              | r            | Ir        | B3                | •     |   |   |               |   |       | 2      | 4      |

|                 |                                                              | R            | R         | B4                | •     |   |   |               |   |       | 3      | 3      |

|                 |                                                              | R            | IR        | B5                | •     |   |   |               |   |       | 3      | 4      |

|                 |                                                              | R            | IM        | B6                | •     |   |   |               |   |       | 3      | 3      |

|                 |                                                              | IR           | IM        | B7                | •     |   |   |               |   |       | 3      | 4      |

| XORX dst, src   | $dst \leftarrow dst \ XOR \ src$                             | ER           | ER        | B8                | -     | * | * | 0             | - | -     | 4      | 3      |

|                 |                                                              | ER           | IM        | B9                | •     |   |   |               |   |       | 4      | 3      |

| Flags Notation: | * = Value is a function o<br>- = Unaffected<br>X = Undefined | f the resu   | lt of the | operation.        |       |   |   | et to<br>to 1 | 0 |       |        |        |

## Table 126. eZ8 CPU Instruction Summary (Continued)

# **Ordering Information**

| Part        | Flash<br>KB (Bytes) | RAM<br>KB (Bytes) | Max. Speed<br>(MHz) | Temp<br>( <sup>0</sup> C) | Voltage<br>(V) | Package | Part Number    |

|-------------|---------------------|-------------------|---------------------|---------------------------|----------------|---------|----------------|

| Z8 Encore!® | with 16KB           | Flash, Stand      | lard Tempera        | ture                      |                |         |                |

| Z8 Encore!® | 16 (16,384)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PDIP-40 | Z8F1601PM020SC |

| Z8 Encore!® | 16 (16,384)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-44 | Z8F1601AN020SC |

| Z8 Encore!® | 16 (16,384)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-44 | Z8F1601VN020SC |

| Z8 Encore!® | 16 (16,384)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-64 | Z8F1602AR020SC |

| Z8 Encore!® | 16 (16,384)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-68 | Z8F1602VS020SC |

| Z8 Encore!® | with 24KB           | Flash, Stand      | lard Tempera        | ture                      |                |         |                |

| Z8 Encore!® | 24 (24,576)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PDIP-40 | Z8F2401PM020SC |

| Z8 Encore!® | 24 (24,576)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-44 | Z8F2401AN020SC |

| Z8 Encore!® | 24 (24,576)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-44 | Z8F2401VN020SC |

| Z8 Encore!® | 24 (24,576)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-64 | Z8F2402AR020SC |

| Z8 Encore!® | 24 (24,576)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-68 | Z8F2402VS020SC |

| Z8 Encore!® | with 32KB           | Flash, Stand      | lard Tempera        | ture                      |                |         |                |

| Z8 Encore!® | 32 (32,768)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PDIP-40 | Z8F3201PM020SC |

| Z8 Encore!® | 32 (32,768)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-44 | Z8F3201AN020SC |

| Z8 Encore!® | 32 (32,768)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-44 | Z8F3201VN020SC |

| Z8 Encore!® | 32 (32,768)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-64 | Z8F3202AR020SC |

| Z8 Encore!® | 32 (32,768)         | 2 (2048)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-68 | Z8F3202VS020SC |

| Z8 Encore!® | with 48KB           | Flash, Stand      | ard Temperat        | ure                       |                |         |                |

| Z8 Encore!® | 48 (49,152)         | 4 (4096)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PDIP-40 | Z8F4801PM020SC |

| Z8 Encore!® | 48 (49,152)         | 4 (4096)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-44 | Z8F4801AN020SC |

| Z8 Encore!® | 48 (49,152)         | 4 (4096)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-44 | Z8F4801VN020SC |

| Z8 Encore!® | 48 (49,152)         | 4 (4096)          | 20                  | 0 to +70                  | 3.0 - 3.6      | LQFP-64 | Z8F4802AR020SC |

| Z8 Encore!® | 48 (49,152)         | 4 (4096)          | 20                  | 0 to +70                  | 3.0 - 3.6      | PLCC-68 | Z8F4802VS020SC |

| Z8 Encore!® | 48 (49,152)         | 4 (4096)          | 20                  | 0 to +70                  | 3.0 - 3.6      | QFP-80  | Z8F4803FT020SC |

#### Table 128. Ordering Information