Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20 MIPS                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 30                                                                            |

| Program Memory Size        | 24KB (8K x 24)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 1K x 8                                                                        |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 13x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8x8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f3014-20e-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### CORE REGISTER MAP<sup>(1)</sup> (CONTINUED) **TABLE 3-3:**

| IADEL J- | J. U              |        |                   |        | (00)   |        | -0,    |        |         |                     |       |        |        |       | -     | -     |       |                     |

|----------|-------------------|--------|-------------------|--------|--------|--------|--------|--------|---------|---------------------|-------|--------|--------|-------|-------|-------|-------|---------------------|

| SFR Name | Address<br>(Home) | Bit 15 | Bit 14            | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8   | Bit 7               | Bit 6 | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset State         |

| CORCON   | 0044              | —      |                   | —      | US     | EDT    | DL2    | DL1    | DL0     | SATA                | SATB  | SATDW  | ACCSAT | IPL3  | PSV   | RND   | IF    | 0000 0000 0010 0000 |

| MODCON   | 0046              | XMODEN | YMODEN            | _      | _      |        | BWN    | 1<3:0> |         |                     | YWI   | M<3:0> |        |       | XWM<  | :3:0> |       | 0000 0000 0000 0000 |

| XMODSRT  | 0048              |        | XS<15:1> 0 1      |        |        |        |        |        |         | uuuu uuuu uuuu uuu0 |       |        |        |       |       |       |       |                     |

| XMODEND  | 004A              |        | XE<15:1> 1        |        |        |        |        |        |         | uuuu uuuu uuul      |       |        |        |       |       |       |       |                     |

| YMODSRT  | 004C              |        |                   |        |        |        |        | YS     | S<15:1> |                     |       |        |        |       |       |       | 0     | uuuu uuuu uuuu uuu0 |

| YMODEND  | 004E              |        | YE<15:1> 1        |        |        |        |        |        |         | uuuu uuuu uuul      |       |        |        |       |       |       |       |                     |

| XBREV    | 0050              | BREN   | 3REN XB<14:0>     |        |        |        |        |        |         | uuuu uuuu uuuu uuuu |       |        |        |       |       |       |       |                     |

| DISICNT  | 0052              | _      | — — DISICNT<13:0> |        |        |        |        |        |         | 0000 0000 0000 0000 |       |        |        |       |       |       |       |                     |

Legend:

u = uninitialized bit; — = unimplemented bit, read as '0'

Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

NOTES:

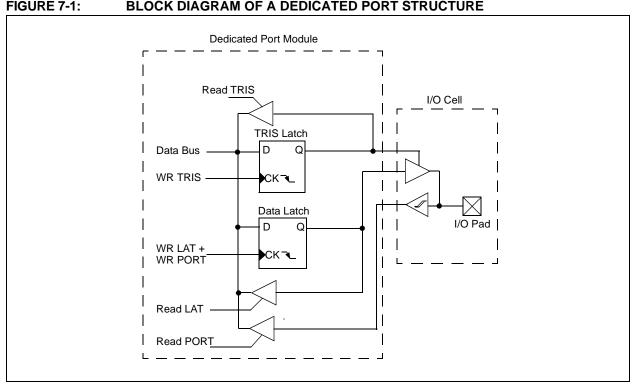

#### 7.0 I/O PORTS

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU. peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

All of the device pins (except VDD, VSS, MCLR and OSC1/CLKI) are shared between the peripherals and the parallel I/O ports.

All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

#### 7.1 Parallel I/O (PIO) Ports

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have three registers directly associated with the operation of the port pin. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset.

Reads from the latch (LATx), read the latch. Writes to the latch, write the latch (LATx). Reads from the port (PORTx), read the port pins and writes to the port pins, write the latch (LATx).

Any bit and its associated data and control registers that are not valid for a particular device are disabled, which means the corresponding LATx and TRISx registers and the port pin read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs. An example is the INT4 pin.

A Parallel I/O (PIO) port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pad cell. Figure 7-2 shows how ports are shared with other peripherals and the associated I/O cell (pad) to which they are connected. Table 7-1 shows the formats of the registers for the shared ports, PORTB through PORTF.

Note: The actual bits in use vary between devices.

FIGURE 7-1: **BLOCK DIAGRAM OF A DEDICATED PORT STRUCTURE**

### TABLE 7-2: INPUT CHANGE NOTIFICATION REGISTER MAP FOR dsPIC30F3014/4013 DEVICES (BITS 15-0)<sup>(1)</sup>

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1   | Bit 0  | Reset State         |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|---------|---------|--------|---------------------|

| CNEN1       | 00C0  | _      | _      | _      | _      | _      | _      | —     | _     | CN7IE  | CN6IE  | CN5IE  | CN4IE  | CN3IE  | CN2IE   | CN1IE   | CN0IE  | 0000 0000 0000 0000 |

| CNEN2       | 00C2  | -      | —      | -      | -      | -      |        | Ι     | _     | _      | _      |        | _      | -      | CN18IE  | CN17IE  |        | 0000 0000 0000 0000 |

| CNPU1       | 00C4  | -      | —      | -      | -      | -      |        | Ι     | _     | CN7PUE | CN6PUE | CN5PUE | CN4PUE | CN3PUE | CN2PUE  | CN1PUE  | CN0PUE | 0000 0000 0000 0000 |

| CNPU2       | 00C6  | _      | —      | _      | _      | _      | _      | _     | —     | -      |        | _      |        | _      | CN18PUE | CN17PUE | _      | 0000 0000 0000 0000 |

Legend: — = unimplemented bit, read as '0'

Note 1: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

NOTES:

#### 9.1 Timer Gate Operation

The 16-bit timer can be placed in the Gated Time Accumulation mode. This mode allows the internal TCY to increment the respective timer when the gate input signal (T1CK pin) is asserted high. Control bit, TGATE (T1CON<6>), must be set to enable this mode. The timer must be enabled (TON = 1) and the timer clock source set to internal (TCS = 0).

When the CPU goes into the Idle mode, the timer stops incrementing unless TSIDL = 0. If TSIDL = 1, the timer resumes the incrementing sequence upon termination of the CPU Idle mode.

#### 9.2 Timer Prescaler

The input clock (Fosc/4 or external clock) to the 16-bit Timer has a prescale option of 1:1, 1:8, 1:64 and 1:256, selected by control bits, TCKPS<1:0> (T1CON<5:4>). The prescaler counter is cleared when any of the following occurs:

- a write to the TMR1 register

- a write to the T1CON register

- device Reset, such as POR and BOR

However, if the timer is disabled (TON = 0), then the timer prescaler cannot be reset since the prescaler clock is halted.

TMR1 is not cleared when T1CON is written. It is cleared by writing to the TMR1 register.

#### 9.3 Timer Operation During Sleep Mode

During CPU Sleep mode, the timer operates if:

- The timer module is enabled (TON = 1) and

- The timer clock source is selected as external (TCS = 1) and

- The TSYNC bit (T1CON<2>) is asserted to a logic '0' which defines the external clock source as asynchronous.

When all three conditions are true, the timer continues to count up to the Period register and is reset to 0x0000.

When a match between the timer and the Period register occurs, an interrupt can be generated if the respective timer interrupt enable bit is asserted.

#### 9.4 Timer Interrupt

The 16-bit timer has the ability to generate an interrupton-period match. When the timer count matches the Period register, the T1IF bit is asserted and an interrupt is generated, if enabled. The T1IF bit must be cleared in software. The Timer Interrupt Flag, T1IF, is located in the IFS0 Control register in the interrupt controller.

When the Gated Time Accumulation mode is enabled, an interrupt is also generated on the falling edge of the gate signal (at the end of the accumulation cycle). Enabling an interrupt is accomplished via the respective timer interrupt enable bit, T1IE. The timer interrupt enable bit is located in the IEC0 Control register in the interrupt controller.

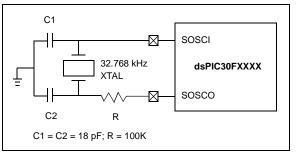

#### 9.5 Real-Time Clock

Timer1, when operating in Real-Time Clock (RTC) mode, provides time of day and event time-stamping capabilities. Key operational features of the RTC are:

- Operation from 32 kHz LP oscillator

- 8-bit prescaler

- Low power

- Real-Time Clock interrupts

These operating modes are determined by setting the appropriate bit(s) in the T1CON Control register.

#### RECOMMENDED COMPONENTS FOR TIMER1 LP OSCILLATOR RTC

### 9.5.1 RTC OSCILLATOR OPERATION

When the TON = 1, TCS = 1 and TGATE = 0, the timer increments on the rising edge of the 32 kHz LP oscillator output signal, up to the value specified in the Period register and is then reset to '0'.

The TSYNC bit must be asserted to a logic '0' (Asynchronous mode) for correct operation.

Enabling LPOSCEN (OSCCON<1>) disables the normal Timer and Counter modes and enable a timer carry-out wake-up event.

When the CPU enters Sleep mode, the RTC continues to operate, provided the 32 kHz external crystal oscillator is active and the control bits have not been changed. The TSIDL bit should be cleared to '0' in order for RTC to continue operation in Idle mode.

#### 9.5.2 RTC INTERRUPTS

When an interrupt event occurs, the respective interrupt flag, T1IF, is asserted and an interrupt is generated, if enabled. The T1IF bit must be cleared in software. The respective Timer Interrupt Flag, T1IF, is located in the IFS0 register in the interrupt controller.

Enabling an interrupt is accomplished via the respective timer interrupt enable bit, T1IE. The timer interrupt enable bit is located in the IEC0 Control register in the interrupt controller.

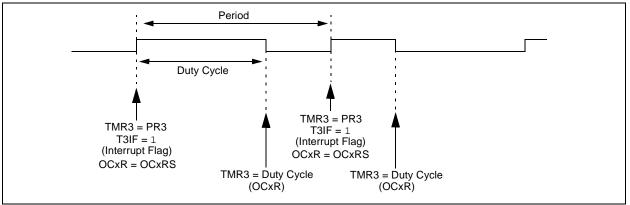

#### 13.4.2 PWM PERIOD

The PWM period is specified by writing to the PRx register. The PWM period can be calculated using Equation 13-1.

#### EQUATION 13-1:

$PWM \text{ period } = [(PRx) + 1] \bullet 4 \bullet \text{Tosc} \bullet$ (TMRx prescale value)

PWM frequency is defined as 1/[PWM period].

When the selected TMRx is equal to its respective Period register, PRx, the following four events occur on the next increment cycle:

- TMRx is cleared.

- The OCx pin is set.

- Exception 1: If PWM duty cycle is 0x0000, the OCx pin remains low.

- Exception 2: If duty cycle is greater than PRx, the pin remains high.

- The PWM duty cycle is latched from OCxRS into OCxR.

- The corresponding timer interrupt flag is set.

See Figure 13-2 for key PWM period comparisons. Timer3 is referred to in Figure 13-2 for clarity.

#### FIGURE 13-2: PWM OUTPUT TIMING

#### 15.3 Slave Select Synchronization

The SSx pin allows a Synchronous Slave mode. The SPI must be configured in SPI Slave mode with SSx pin control enabled (SSEN = 1). When the SSx pin is low, transmission and reception are enabled and the SDOx pin is driven. When SSx pin goes high, the SDOx pin is no longer driven. Also, the SPI module is resynchronized, and all counters/control circuitry are reset. Therefore, when the SSx pin is asserted low again, transmission/reception begins at the MSb even if SSx had been deasserted in the middle of a transmit/ receive.

#### 15.4 SPI Operation During CPU Sleep Mode

During Sleep mode, the SPI module is shut down. If the CPU enters Sleep mode while an SPI transaction is in progress, then the transmission and reception is aborted.

The transmitter and receiver stop in Sleep mode. However, register contents are not affected by entering or exiting Sleep mode.

#### 15.5 SPI Operation During CPU Idle Mode

When the device enters Idle mode, all clock sources remain functional. The SPISIDL bit (SPIxSTAT<13>) determines if the SPI module stops or continues on Idle. If SPISIDL = 0, the module continues to operate when the CPU enters Idle mode. If SPISIDL = 1, the module stops when the CPU enters Idle mode.

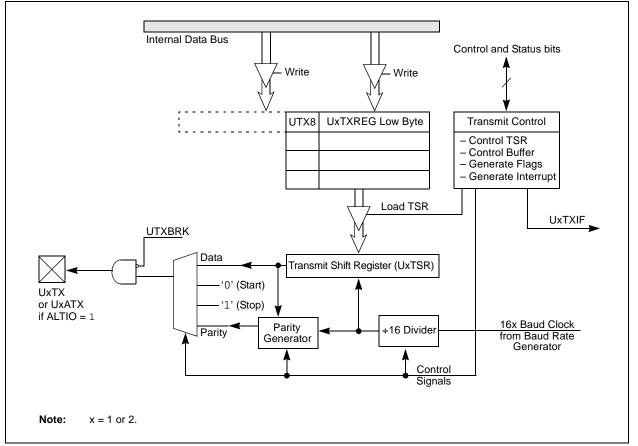

### 16.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART) MODULE

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

This section describes the Universal Asynchronous Receiver/Transmitter Communications module.

#### 16.1 UART Module Overview

The key features of the UART module are:

- Full-duplex, 8 or 9-bit data communication

- Even, odd or no parity options (for 8-bit data)

- · One or two Stop bits

- Fully integrated Baud Rate Generator with 16-bit prescaler

- Baud rates range from 38 bps to 1.875 Mbps at a 30 MHz instruction rate

- 4-word deep transmit data buffer

- 4-word deep receive data buffer

- Parity, framing and buffer overrun error detection

- Support for interrupt only on address detect (9th bit = 1)

- Separate transmit and receive interrupts

- Loopback mode for diagnostic support

- Two choices of TX/RX pins on UART1 module

#### FIGURE 16-1: UART TRANSMITTER BLOCK DIAGRAM

#### Bit 15 Bit 13 Bit 12 Bit 10 Bit 8 SFR Name Addr. Bit 14 Bit 11 Bit 9 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Reset State C1TX1B1 Transmit Buffer 1 Byte 1 Transmit Buffer 1 Byte 0 0356 C1TX1B2 0358 Transmit Buffer 1 Byte 3 Transmit Buffer 1 Byte 2 uuuu uuuu uuuu uuuu C1TX1B3 035A Transmit Buffer 1 Byte 5 Transmit Buffer 1 Byte 4 uuuu uuuu uuuu C1TX1B4 035C Transmit Buffer 1 Byte 7 Transmit Buffer 1 Byte 6 uuuu uuuu uuuu TXABT TXLARB TXERR C1TX1CON 035E \_ \_ TXREQ TXPRI<1:0> 0000 0000 0000 0000 \_ \_ C1TX0SID 0360 Transmit Buffer 0 Standard Identifier<10:6> \_ \_ \_ Transmit Buffer 0 Standard Identifier <5:0> SRR TXIDE uuuu u000 uuuu uuuu C1TX0EID 0362 Transmit Buffer 0 Extended Identifier <17:14> Transmit Buffer 0 Extended Identifier<13:6> \_ \_ \_ uuuu 0000 uuuu uuuu C1TX0DLC 0364 Transmit Buffer 0 Extended Identifier<5:0> TXRTR TXRB1 TXRB0 DLC<3:0> \_ \_ uuuu uuuu uuuu u000 C1TX0B1 0366 Transmit Buffer 0 Byte 0 Transmit Buffer 0 Byte 1 uuuu uuuu uuuu uuuu C1TX0B2 0368 Transmit Buffer 0 Byte 3 Transmit Buffer 0 Byte 2 uuuu uuuu uuuu C1TX0B3 036A Transmit Buffer 0 Byte 5 Transmit Buffer 0 Byte 4 uuuu uuuu uuuu C1TX0B4 036C Transmit Buffer 0 Byte 7 Transmit Buffer 0 Byte 6 uuuu uuuu uuuu uuuu TXABT TXLARB TXERR TXPRI<1:0> C1TX0CON 036E \_ \_\_\_\_ \_ TXREQ \_\_\_\_ 0000 0000 0000 0000 \_ \_ C1RX1SID 0370 Receive Buffer 1 Standard Identifier<10:0> SRR RXIDE 000u uuuu uuuu uuuu \_\_\_\_ C1RX1EID 0372 Receive Buffer 1 Extended Identifier <17:6> \_ \_ \_ \_ 0000 uuuu uuuu uuuu RXRTR RXRB1 RXRB0 DLC<3:0> C1RX1DLC 0374 Receive Buffer 1 Extended Identifier<5:0> uuuu uuuu 000u uuuu C1RX1B1 0376 Receive Buffer 1 Byte 1 Receive Buffer 1 Byte 0 101101 101011 101010 101001 C1RX1B2 0378 Receive Buffer 1 Byte 3 Receive Buffer 1 Byte 2 uuuu uuuu uuuu uuuu C1RX1B3 037A Receive Buffer 1 Byte 5 Receive Buffer 1 Byte 4 uuuu uuuu uuuu uuuu C1RX1B4 037C Receive Buffer 1 Byte 7 Receive Buffer 1 Byte 6 uuuu uuuu uuuu uuuu C1RX1CON 037E \_ RXFUL RXRTRRO FIL HIT<2.0> 0000 0000 0000 0000 \_ C1RX0SID 0380 \_ Receive Buffer 0 Standard Identifier<10:0> SRR RXIDE 000u uuuu uuuu uuuu \_ \_ C1RX0EID 0382 Receive Buffer 0 Extended Identifier<17:6> \_ 0000 uuuu uuuu uuuu RXRTR RXRB1 DLC<3:0> C1RX0DLC 0384 Receive Buffer 0 Extended Identifier<5:0> \_ \_ RXRB0 uuuu uuuu 000u uuuu C1RX0B1 0386 Receive Buffer 0 Byte 1 Receive Buffer 0 Byte 0 uuuu uuuu uuuu uuuu C1RX0B2 0388 Receive Buffer 0 Byte 3 Receive Buffer 0 Byte 2 uuuu uuuu uuuu uuuu C1RX0B3 038A Receive Buffer 0 Byte 5 Receive Buffer 0 Byte 4 uuuu uuuu uuuu uuuu C1RX0B4 038C Receive Buffer 0 Byte 7 Receive Buffer 0 Byte 6 uuuu uuuu uuuu RXRTRRO DBEN JTOFF FILHITO C1RX0CON 038F RXFUI \_ 0000 0000 0000 0000 \_ C1CTRL 0390 CANCAP \_ CSIDL ABAT CANCKS REQOP<2:0> OPMODE<2:0> \_ ICODE<2:0> 0000 0100 1000 0000 C1CFG1 0392 \_ \_ \_ \_ \_ \_ \_ SJW<1:0> BRP<5:0> 0000 0000 0000 0000 C1CFG2 SEG2PHTS SEG1PH<2:0> PRSEG<2.0> 0394 \_ WAKFIL \_ \_ \_ SEG2PH<2:0> SAM 0u00 0uuu uuuu uuuu C1INTF 0396 RX00VR RX10VR тхво TXEP RXEP TXWAR RXWAR EWARN IVRIF WAKIF ERRIF TX2IF TX1IF TX0IF RX1IF RX0IF 0000 0000 0000 0000 C1INTE 0398 ERRIE TX2IE TX1IE TX0IE RX1IE RX0IE 0000 0000 0000 0000 IVRIE WAKIE \_ \_ \_ \_\_\_\_ \_ C1EC 039A TERRCNT<7:0> RERRCNT<7:0> 0000 0000 0000 0000

## TABLE 17-1: dsPIC30F4013 CAN1 REGISTER MAP<sup>(1)</sup> (CONTINUED)

Legend: u = uninitialized bit; — = unimplemented bit, read as '0'

**Note** 1: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

dsPIC30F3014/401;

#### TABLE 20-1: OSCILLATOR OPERATING MODES

| Oscillator Mode | Description                                                                       |

|-----------------|-----------------------------------------------------------------------------------|

| XTL             | 400 kHz-4 MHz crystal on OSC1:OSC2                                                |

| хт              | 4 MHz-10 MHz crystal on OSC1:OSC2                                                 |

| XT w/PLL 4x     | 4 MHz-10 MHz crystal on OSC1:OSC2, 4x PLL enabled                                 |

| XT w/PLL 8x     | 4 MHz-10 MHz crystal on OSC1:OSC2, 8x PLL enabled                                 |

| XT w/PLL 16x    | 4 MHz-7.5 MHz crystal on OSC1:OSC2, 16x PLL enabled <sup>(1)</sup>                |

| LP              | 32 kHz crystal on SOSCO:SOSCI <sup>(2)</sup>                                      |

| HS              | 10 MHz-25 MHz crystal                                                             |

| HS/2 w/PLL 4x   | 10 MHz-20 MHz crystal, divide by 2, 4x PLL enabled                                |

| HS/2 w/PLL 8x   | 10 MHz-20 MHz crystal, divide by 2, 8x PLL enabled                                |

| HS/2 w/PLL 16x  | 10 MHz-15 MHz crystal, divide by 2, 16x PLL enabled                               |

| HS/3 w/PLL 4x   | 12 MHz-25 MHz crystal, divide by 3, 4x PLL enabled                                |

| HS/3 w/PLL 8x   | 12 MHz-25 MHz crystal, divide by 3, 8x PLL enabled                                |

| HS/3 w/PLL 16x  | 12 MHz-22.5 MHz crystal, divide by 3, 16x PLL enabled                             |

| EC              | External clock input (0-40 MHz)                                                   |

| ECIO            | External clock input (0-40 MHz), OSC2 pin is I/O                                  |

| EC w/PLL 4x     | External clock input (4-10 MHz), OSC2 pin is I/O, 4x PLL enabled <sup>(1)</sup>   |

| EC w/PLL 8x     | External clock input (4-10 MHz), OSC2 pin is I/O, 8x PLL enabled <sup>(1)</sup>   |

| EC w/PLL 16x    | External clock input (4-7.5 MHz), OSC2 pin is I/O, 16x PLL enabled <sup>(1)</sup> |

| ERC             | External RC oscillator, OSC2 pin is Fosc/4 output <sup>(3)</sup>                  |

| ERCIO           | External RC oscillator, OSC2 pin is I/O <sup>(3)</sup>                            |

| FRC             | 7.37 MHz internal RC oscillator                                                   |

| FRC w/PLL 4x    | 7.37 MHz Internal RC oscillator, 4x PLL enabled                                   |

| FRC w/PLL 8x    | 7.37 MHz Internal RC oscillator, 8x PLL enabled                                   |

| FRC w/PLL 16x   | 7.37 MHz Internal RC oscillator, 16x PLL enabled                                  |

| LPRC            | 512 kHz internal RC oscillator                                                    |

Note 1: dsPIC30F maximum operating frequency of 120 MHz must be met.

2: LP oscillator can be conveniently shared as system clock, as well as Real-Time Clock for Timer1.

3: Requires external R and C. Frequency operation up to 4 MHz.

#### REGISTER 20-2: OSCTUN: FRC OSCILLATOR TUNING REGISTER

|                                   | 20-2. 0001 |                                 |                 |                                    |                      |        |       |  |  |  |  |

|-----------------------------------|------------|---------------------------------|-----------------|------------------------------------|----------------------|--------|-------|--|--|--|--|

| U-0                               | U-0        | U-0                             | U-0             | U-0                                | U-0                  | U-0    | U-0   |  |  |  |  |

| —                                 | —          | —                               | —               | —                                  | —                    | —      | _     |  |  |  |  |

| bit 15                            |            |                                 |                 |                                    |                      |        | bit   |  |  |  |  |

|                                   |            |                                 |                 |                                    |                      |        |       |  |  |  |  |

| U-0                               | U-0        | U-0                             | U-0             | R/W-0                              | R/W-0                | R/W-0  | R/W-0 |  |  |  |  |

| _                                 | —          |                                 | —               |                                    | TUI                  | N<3:0> |       |  |  |  |  |

| bit 7                             |            |                                 |                 |                                    |                      |        | bit ( |  |  |  |  |

|                                   |            |                                 |                 |                                    |                      |        |       |  |  |  |  |

| Legend:                           |            |                                 |                 |                                    |                      |        |       |  |  |  |  |

| R = Readable bit W = Writable bit |            |                                 | oit             | U = Unimplemented bit, read as '0' |                      |        |       |  |  |  |  |

| -n = Value at                     | POR        | '1' = Bit is set                |                 | '0' = Bit is cle                   | '0' = Bit is cleared |        | nown  |  |  |  |  |

|                                   |            | minal 7.37 MHz<br>mum frequency | •               |                                    |                      |        |       |  |  |  |  |

|                                   | 0001 =     | er frequency, os                | cillator is rur | nning at calibrat                  | ed frequency         |        |       |  |  |  |  |

|                                   |            |                                 |                 |                                    |                      |        |       |  |  |  |  |

- 1001 =

- 1000 = Minimum frequency

# 20.4.1.1 POR with Long Crystal Start-up Time (with FSCM Enabled)

The oscillator start-up circuitry is not linked to the POR circuitry. Some crystal circuits (especially low-frequency crystals) have a relatively long start-up time. Therefore, one or more of the following conditions is possible after the POR timer and the PWRT have expired:

- The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer has not expired (if a crystal oscillator is used).

- The PLL has not achieved a LOCK (if PLL is used).

If the FSCM is enabled and one of the above conditions is true, a clock failure trap occurs. The device automatically switches to the FRC oscillator and the user can switch to the desired crystal oscillator in the trap ISR.

#### 20.4.1.2 Operating without FSCM and PWRT

If the FSCM is disabled and the Power-up Timer (PWRT) is also disabled, then the device exits rapidly from Reset on power-up. If the clock source is FRC, LPRC, ERC or EC, it will be active immediately.

If the FSCM is disabled and the system clock has not started, the device will be in a frozen state at the Reset vector until the system clock starts. From the user's perspective, the device appears to be in Reset until a system clock is available.

#### 20.4.2 BOR: PROGRAMMABLE BROWN-OUT RESET

The BOR (Brown-out Reset) module is based on an internal voltage reference circuit. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (i.e., missing portions of the AC cycle waveform due to bad power transmission lines, or voltage sags due to excessive current draw when a large inductive load is turned on).

The BOR module allows selection of one of the following voltage trip points (see Table 23-11):

- 2.6V-2.71V

- 4.1V-4.4V

- 4.58V-4.73V

Note: The BOR voltage trip points indicated here are nominal values provided for design guidance only. Refer to the Electrical Specifications in the specific device data sheet for BOR voltage limit specifications. A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source based on the device Configuration bit values (FOS<2:0> and FPR<4:0>). Furthermore, if an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, then the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the POR time-out (TPOR) and the PWRT time-out (TPWRT) are applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM = 100  $\mu$ s is applied. The total delay in this case is (TPOR + TFSCM).

The BOR status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit, if enabled, continues to operate while in Sleep or Idle modes and resets the device should VDD fall below the BOR threshold voltage.

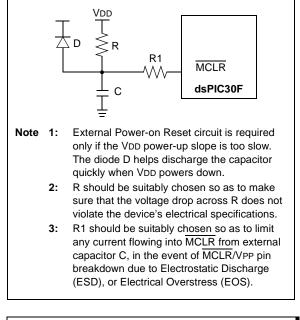

#### FIGURE 20-6: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

Note: Dedicated supervisory devices, such as the MCP1XX and MCP8XX, may also be used as an external Power-on Reset circuit.

#### 20.5 Watchdog Timer (WDT)

#### 20.5.1 WATCHDOG TIMER OPERATION

The primary function of the Watchdog Timer (WDT) is to reset the processor in the event of a software malfunction. The WDT is a free-running timer that runs off an on-chip RC oscillator, requiring no external component. Therefore, the WDT timer continues to operate even if the main processor clock (e.g., the crystal oscillator) fails.

#### 20.5.2 ENABLING AND DISABLING THE WDT

The Watchdog Timer can be "Enabled" or "Disabled" only through a Configuration bit (FWDTEN) in the Configuration register, FWDT.

Setting FWDTEN = 1 enables the Watchdog Timer. The enabling is done when programming the device. By default, after chip erase, FWDTEN bit = 1. Any device programmer capable of programming dsPIC30F devices allows programming of this and other Configuration bits.

If enabled, the WDT increments until it overflows or "times out". A WDT time-out forces a device Reset (except during Sleep). To prevent a WDT time-out, the user must clear the Watchdog Timer using a CLRWDT instruction.

If a WDT times out during Sleep, the device wakes up. The WDTO bit in the RCON register is cleared to indicate a wake-up resulting from a WDT time-out.

Setting FWDTEN = 0 allows user software to enable/ disable the Watchdog Timer via the SWDTEN (RCON<5>) control bit.

#### 20.6 Low-Voltage Detect

The Low-Voltage Detect (LVD) module is used to detect when the VDD of the device drops below a threshold value, VLVD, which is determined by the LVDL<3:0> bits (RCON<11:8>) and is thus user programmable. The internal voltage reference circuitry requires a nominal amount of time to stabilize, and the BGST bit (RCON<13>) indicates when the voltage reference has stabilized.

In some devices, the LVD threshold voltage may be applied externally on the LVDIN pin.

The LVD module is enabled by setting the LVDEN bit (RCON<12>).

#### 20.7 Power-Saving Modes

There are two power-saving states that can be entered through the execution of a special instruction, PWRSAV; these are Sleep and Idle.

The format of the PWRSAV instruction is as follows:

$\ensuremath{\texttt{PWRSAV}}$  cparameter>, where 'parameter' defines Idle or Sleep mode.

#### 20.7.1 SLEEP MODE

In Sleep mode, the clock to the CPU and peripherals is shut down. If an on-chip oscillator is being used, it is shut down.

The Fail-Safe Clock Monitor is not functional during Sleep since there is no clock to monitor. However, the LPRC clock remains active if WDT is operational during Sleep.

The brown-out protection circuit and the Low-Voltage Detect (LVD) circuit, if enabled, remains functional during Sleep.

The processor wakes up from Sleep if at least one of the following conditions has occurred:

- any interrupt that is individually enabled and meets the required priority level

- any Reset (POR, BOR and MCLR)

- WDT time-out

On waking up from Sleep mode, the processor restarts the same clock that was active prior to entry into Sleep mode. When clock switching is enabled, bits, COSC<2:0>, determine the oscillator source to be used on wake-up. If clock switch is disabled, then there is only one system clock.

**Note:** If a POR or BOR occurred, the selection of the oscillator is based on the FOS<2:0> and FPR<4:0> Configuration bits.

If the clock source is an oscillator, the clock to the device is held off until OST times out (indicating a stable oscillator). If PLL is used, the system clock is held off until LOCK = 1 (indicating that the PLL is stable). In either case, TPOR, TLOCK and TPWRT delays are applied.

If EC, FRC, LPRC or ERC oscillators are used, then a delay of TPOR (~ 10  $\mu$ s) is applied. This is the smallest delay possible on wake-up from Sleep.

Moreover, if the LP oscillator was active during Sleep and LP is the oscillator used on wake-up, then the startup delay is equal to TPOR. PWRT delay and OST timer delay are not applied. In order to have the smallest possible start-up delay when waking up from Sleep, one of these faster wake-up options should be selected before entering Sleep.

#### TABLE 21-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Base<br>Instr<br># | Assembly<br>Mnemoni<br>c |        | Assembly Syntax | Description                           | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|--------------------------|--------|-----------------|---------------------------------------|---------------|----------------|--------------------------|

| 66                 | RRNC                     | RRNC   | f               | f = Rotate Right (No Carry) f         | 1             | 1              | N,Z                      |

|                    |                          | RRNC   | f,WREG          | WREG = Rotate Right (No Carry) f      | 1             | 1              | N,Z                      |

|                    |                          | RRNC   | Ws,Wd           | Wd = Rotate Right (No Carry) Ws       | 1             | 1              | N,Z                      |

| 67                 | SAC                      | SAC    | Acc,#Slit4,Wdo  | Store Accumulator                     | 1             | 1              | None                     |

|                    |                          | SAC.R  | Acc,#Slit4,Wdo  | Store Rounded Accumulator             | 1             | 1              | None                     |

| 68                 | SE                       | SE     | Ws,Wnd          | Wnd = Sign-Extended Ws                | 1             | 1              | C,N,Z                    |

| 69                 | SETM                     | SETM   | f               | f = 0xFFFF                            | 1             | 1              | None                     |

|                    |                          | SETM   | WREG            | WREG = 0xFFFF                         | 1             | 1              | None                     |

|                    |                          | SETM   | Ws              | Ws = 0xFFFF                           | 1             | 1              | None                     |

| 70 SFTAC           | SFTAC                    | SFTAC  | Acc,Wn          | Arithmetic Shift Accumulator by (Wn)  | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                          | SFTAC  | Acc,#Slit6      | Arithmetic Shift Accumulator by Slit6 | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 71                 | SL                       | SL     | f               | f = Left Shift f                      | 1             | 1              | C,N,OV,Z                 |

|                    |                          | SL     | f,WREG          | WREG = Left Shift f                   | 1             | 1              | C,N,OV,Z                 |

|                    |                          | SL     | Ws,Wd           | Wd = Left Shift Ws                    | 1             | 1              | C,N,OV,Z                 |

|                    |                          | SL     | Wb,Wns,Wnd      | Wnd = Left Shift Wb by Wns            | 1             | 1              | N,Z                      |

|                    |                          | SL     | Wb,#lit5,Wnd    | Wnd = Left Shift Wb by lit5           | 1             | 1              | N,Z                      |

| 72                 | SUB                      | SUB    | Асс             | Subtract Accumulators                 | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                          | SUB    | f               | f = f - WREG                          | 1             | 1              | C,DC,N,OV,Z              |

|                    |                          | SUB    | f,WREG          | WREG = f – WREG                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                          | SUB    | #lit10,Wn       | Wn = Wn - Iit10                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                          | SUB    | Wb,Ws,Wd        | Wd = Wb – Ws                          | 1             | 1              | C,DC,N,OV,Z              |

|                    |                          | SUB    | Wb,#lit5,Wd     | Wd = Wb - lit5                        | 1             | 1              | C,DC,N,OV,Z              |

| 73                 | SUBB                     | SUBB   | f               | $f = f - WREG - (\overline{C})$       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                          | SUBB   | f,WREG          | WREG = $f - WREG - (\overline{C})$    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                          | SUBB   | #lit10,Wn       | $Wn = Wn - Iit10 - (\overline{C})$    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                          | SUBB   | Wb,Ws,Wd        | $Wd = Wb - Ws - (\overline{C})$       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                          | SUBB   | Wb,#lit5,Wd     | $Wd = Wb - lit5 - (\overline{C})$     | 1             | 1              | C,DC,N,OV,Z              |

| 74                 | SUBR                     | SUBR   | f               | f = WREG – f                          | 1             | 1              | C,DC,N,OV,Z              |

|                    |                          | SUBR   | f,WREG          | WREG = WREG– f                        | 1             | 1              | C,DC,N,OV,Z              |

|                    |                          | SUBR   | Wb,Ws,Wd        | Wd = Ws - Wb                          | 1             | 1              | C,DC,N,OV,Z              |

|                    |                          | SUBR   | Wb,#lit5,Wd     | Wd = lit5 – Wb                        | 1             | 1              | C,DC,N,OV,Z              |

| 75                 | SUBBR                    | SUBBR  | f               | $f = WREG - f - (\overline{C})$       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                          | SUBBR  | f,WREG          | WREG = WREG – f – $(\overline{C})$    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                          | SUBBR  | Wb,Ws,Wd        | $Wd = Ws - Wb - (\overline{C})$       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                          | SUBBR  | Wb,#lit5,Wd     | $Wd = lit5 - Wb - (\overline{C})$     | 1             | 1              | C,DC,N,OV,Z              |

| 76                 | SWAP                     | SWAP.b | Wn              | Wn = Nibble Swap Wn                   | 1             | 1              | None                     |

|                    |                          | SWAP   | Wn              | Wn = Byte Swap Wn                     | 1             | 1              | None                     |

| 77                 | TBLRDH                   | TBLRDH | Ws,Wd           | Read Prog<23:16> to Wd<7:0>           | 1             | 2              | None                     |

| 78                 | TBLRDL                   | TBLRDL | Ws,Wd           | Read Prog<15:0> to Wd                 | 1             | 2              | None                     |

| 79                 | TBLWTH                   | TBLWTH | Ws,Wd           | Write Ws<7:0> to Prog<23:16>          | 1             | 2              | None                     |

| 80                 | TBLWTL                   | TBLWTL | Ws,Wd           | Write Ws to Prog<15:0>                | 1             | 2              | None                     |

| 81                 | ULNK                     | ULNK   |                 | Unlink Frame Pointer                  | 1             | 1              | None                     |

| 82                 | XOR                      | XOR    | f               | f = f .XOR. WREG                      | 1             | 1              | N,Z                      |

|                    |                          | XOR    | f,WREG          | WREG = f .XOR. WREG                   | 1             | 1              | N,Z                      |

|                    |                          | XOR    | #lit10,Wn       | Wd = lit10 .XOR. Wd                   | 1             | 1              | N,Z                      |

|                    |                          | XOR    | Wb,Ws,Wd        | Wd = Wb .XOR. Ws                      | 1             | 1              | N,Z                      |

|                    |                          | XOR    | Wb,#lit5,Wd     | Wd = Wb .XOR. lit5                    | 1             | 1              | N,Z                      |

| 83                 | ZE                       | ZE     | Ws,Wnd          | Wnd = Zero-Extend Ws                  | 1             | 1              | C,Z,N                    |

#### TABLE 23-23: TYPE B TIMER (TIMER2 AND TIMER4) EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |           |                                           |                                                                |      | Standard Operating Conditions: 2.5V to 5.5V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |     |         |       |                               |  |  |  |

|--------------------|-----------|-------------------------------------------|----------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|-------|-------------------------------|--|--|--|

| Param<br>No.       | Symbol    | Characte                                  | eristic                                                        |      | Min                                                                                                                                                                                                  | Тур | Max     | Units | Conditions                    |  |  |  |

| TB10               | TtxH      | TxCK High Time                            | Synchronous,<br>no prescaler<br>Synchronous,<br>with prescaler |      | 0.5 Tcy + 20                                                                                                                                                                                         |     | —       | ns    | Must also meet parameter TB15 |  |  |  |

|                    |           |                                           |                                                                |      | 10                                                                                                                                                                                                   |     |         | ns    |                               |  |  |  |

| TB11               | TtxL      | TxCK Low Time                             | Synchronous,<br>no prescaler                                   |      | 0.5 TCY + 20                                                                                                                                                                                         |     |         | ns    | Must also meet parameter TB15 |  |  |  |

|                    |           |                                           | Synchro<br>with pres                                           |      | 10                                                                                                                                                                                                   |     | —       | ns    |                               |  |  |  |

| TB15               | TtxP      | TxCK Input Period                         | Synchro<br>no presc                                            |      | Tcy + 10                                                                                                                                                                                             |     | _       | ns    | N = prescale<br>value         |  |  |  |

|                    |           |                                           | Synchronous, with prescaler                                    |      | Greater of:<br>20 ns or<br>(TCY + 40)/N                                                                                                                                                              |     |         |       | (1, 8, 64, 256)               |  |  |  |

| TB20               | TCKEXTMRL | Delay from Externa<br>Edge to Timer Incre |                                                                | lock | 0.5 TCY                                                                                                                                                                                              |     | 1.5 TCY | —     |                               |  |  |  |

**Note 1:** Timer2 and Timer4 are Type B.

#### TABLE 23-24: TYPE C TIMER (TIMER3 AND TIMER5) EXTERNAL CLOCK TIMING REQUIREMENTS

| АС СНА       | RACTERIST | īcs                                       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |                                         |     |            |       |                               |

|--------------|-----------|-------------------------------------------|------------------------------------------------------|------|-----------------------------------------|-----|------------|-------|-------------------------------|

| Param<br>No. | Symbol    | Characte                                  | eristic                                              |      | Min                                     | Тур | Max        | Units | Conditions                    |

| TC10         | TtxH      | TxCK High Time                            | Synchro                                              | nous | 0.5 TCY + 20                            |     |            | ns    | Must also meet parameter TC15 |

| TC11         | TtxL      | TxCK Low Time                             | Synchro                                              | nous | 0.5 TCY + 20                            |     | _          | ns    | Must also meet parameter TC15 |

| TC15         | TtxP      | TxCK Input Period                         | Synchronous,<br>no prescaler                         |      | Tcy + 10                                |     | _          | ns    | N = prescale<br>value         |

|              |           |                                           | Synchro<br>with pres                                 |      | Greater of:<br>20 ns or<br>(TCY + 40)/N |     |            |       | (1, 8, 64, 256)               |

| TC20         | TCKEXTMRL | Delay from Externa<br>Edge to Timer Incre |                                                      | lock | 0.5 TCY                                 | _   | 1.5<br>Тсү | _     |                               |

Note 1: Timer3 and Timer5 are Type C.

### APPENDIX A: REVISION HISTORY

#### Revision D (June 2006)

Previous versions of this data sheet contained Advance or Preliminary Information. They were distributed with incomplete characterization data.

This revision reflects these changes:

- Revised I<sup>2</sup>C Slave Addresses (see Table 14-1)

- Updated example for ADC Conversion Clock selection (see Section 19.0 "12-bit Analog-to-Digital Converter (ADC) Module")

- Base instruction CP1 eliminated from instruction set (seeTable 21-2)

- Revised electrical characteristics:

- Operating Current (IDD) Specifications (see Table 23-5)

- Idle Current (IIDLE) Specifications (see Table 23-6)

- Power-down Current (IPD) Specifications (see Table 23-7)

- I/O pin Input Specifications (see Table 23-8)

- Brown Out Reset (BOR) Specifications (see Table 23-11)

- Watchdog Timer time-out limits (see Table 23-20)

### Revision E (January 2007)

This revision includes updates to the packaging diagrams.

### **Revision F (April 2008)**

This revision reflects these updates:

- Added FUSE Configuration Register (FICD) details (see Section 20.8 "Device Configuration Registers" and Table 20-8)

- Added Note 2 in Device Configuration Registers table (Table 20-8)

- Removed erroneous statement regarding generation of CAN receive errors (see Section 17.4.5 "Receive Errors")

- Updated ADC Conversion Clock and Sampling Rate Calculation (see Example 19-1). Minimum TAD is 334 nsec.

- Updated details related to the Input Change Notification module:

- Updated last sentence in the first paragraph of Section 7.3 "Input Change Notification Module"

- Updated Table 7-2

- Removed Table 7-3, Table 7-4, and Table 7-5

- Electrical Specifications:

- Resolved TBD values for parameters DO10, DO16, DO20, and DO26 (see Table 23-9)

- 10-bit High-Speed ADC tPDU timing parameter (time to stabilize) has been updated from 20 µs typical to 20 µs maximum (see Table 23-38)

- Parameter OS65 (Internal RC Accuracy) has been expanded to reflect multiple Min and Max values for different temperatures (see Table 23-18)

- Parameter DC12 (RAM Data Retention Voltage) has been updated to include a Min value (see Table 23-4)

- Parameter D134 (Erase/Write Cycle Time) has been updated to include Min and Max values and the Typ value has been removed (see Table 23-12)

- Removed parameters OS62 (Internal FRC Jitter) and OS64 (Internal FRC Drift) and Note 2 from AC Characteristics (see Table 23-17)

- Parameter OS63 (Internal FRC Accuracy) has been expanded to reflect multiple Min and Max values for different temperatures (see Table 23-17)

- Removed parameters DC27a, DC27b, DC47a, and DC47b (references to IDD, 20 MIPs @ 3.3V) in Table 23-5 and Table 23-6

- Removed parameters CS77 and CS78 (references to TRACL and TFACL @ 3.3V) in Table 23-29

- Updated Min and Max values and Conditions for parameter SY11 and updated Min, Typ, and Max values and Conditions for parameter SY20 (see Table 23-20)

- Additional minor corrections throughout the document

## Revision G (November 2010)

This revision includes minor typographical and formatting changes throughout the data sheet text.

The major changes are referenced by their respective section in Table A-1.

#### TABLE A-1: MAJOR SECTION UPDATES

| Section Name                                             | Update Description                                                                                                                                                        |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-Bit Digital<br>Signal Controllers" | Added Note 1 to all QFN pin diagrams (see "Pin Diagrams").                                                                                                                |

| Section 1.0 "Device Overview"                            | Removed the "DCI" peripheral block from the dsPIC30F3014 Block Diagram (see Figure 1-1).                                                                                  |

|                                                          | Updated the Pinout I/O Descriptions for AVDD and AVSS (see Table 1-1).                                                                                                    |

| Section 20.0 "System Integration"                        | Added a note on OSCTUN functionality in <b>Section 20.2.5</b> "Fast RC Oscillator (FRC)".                                                                                 |

|                                                          | Updated the operating frequencies for the following Oscillator Operating Modes (see Table 20-1):                                                                          |

|                                                          | • XTL                                                                                                                                                                     |

|                                                          | <ul> <li>XT w/PLL 16x</li> <li>HS/2 w/PLL 4x, 8x, and 16x</li> </ul>                                                                                                      |

|                                                          | <ul> <li>HS/3 w/PLL 4x, 8x, and 16x</li> <li>EC w/PLL 4x, 8x, and 16x</li> </ul>                                                                                          |

| Section 23.0 "Electrical<br>Characteristics"             | Updated the maximum value for parameter DI19 and the minimum value for parameter DI29 in the I/O Pin Input Specifications (see Table 23-8).                               |

|                                                          | Removed parameter D136 and updated the minimum, typical, maximum, and conditions for parameters D122 and D134 in the Program and EEPROM specifications (see Table 23-12). |

| Sleep155                                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power-up Timer                                                                                                                                                                                                             |

| Timing Requirements187                                                                                                                                                                                                     |

| Program Address Space25                                                                                                                                                                                                    |

| Construction26                                                                                                                                                                                                             |

| Data Access from Program Memory                                                                                                                                                                                            |

| Using Program Space Visibility                                                                                                                                                                                             |

| Data Access From Program Memory                                                                                                                                                                                            |

| Using Table Instructions27                                                                                                                                                                                                 |

| Data Access from, Address Generation26                                                                                                                                                                                     |

| Data Space Window into Operation                                                                                                                                                                                           |

| Data Table Access (Isw)27                                                                                                                                                                                                  |

| Data Table Access (MSB)28                                                                                                                                                                                                  |

| dsPIC30F3014 Memory Map25                                                                                                                                                                                                  |

| dsPIC30F4013 Memory Map25                                                                                                                                                                                                  |

| Table Instructions                                                                                                                                                                                                         |

|                                                                                                                                                                                                                            |

| TBLRDH                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                            |

| TBLRDH27                                                                                                                                                                                                                   |

| TBLRDH                                                                                                                                                                                                                     |

| TBLRDH27TBLRDL27TBLWTH27TBLWTL27Program and EEPROM Characteristics180Program Counter16Programmable141Programmer's Model16Diagram17                                                                                         |

| TBLRDH.27TBLRDL27TBLWTH27TBLWTL27Program and EEPROM Characteristics180Program Counter.16Programmable.141Programmer's Model.16Diagram17Programming Operations45                                                             |

| TBLRDH.27TBLRDL27TBLWTH27TBLWTL27Program and EEPROM Characteristics180Program Counter.16Programmable141Programmer's Model16Diagram17Programming Operations45Algorithm for Program Flash45                                  |

| TBLRDH.27TBLRDL27TBLWTH27TBLWTL27Program and EEPROM Characteristics180Program Counter.16Programmable141Programmer's Model16Diagram17Programming Operations45Algorithm for Program Flash45Erasing a Row of Program Memory45 |

### R

| Reader Response                  | 226 |

|----------------------------------|-----|

| Registers                        |     |

| OSCCON (Oscillator Control)      | 147 |

| OSCTUN (Oscillator Tuning)       | 149 |

| Reset                            |     |

| BOR, Programmable                | 153 |

| Brown-out Reset (BOR)            | 141 |

| Oscillator Start-up Timer (OST)  | 141 |

| POR                              |     |

| Operating without FSCM and PWRT  | 153 |

| With Long Crystal Start-up Time  | 153 |

| POR (Power-on Reset)             |     |

| Power-on Reset (POR)             | 141 |

| Power-up Timer (PWRT)            |     |

| Reset Sequence                   | 61  |

| Reset Sources                    | 61  |

| Reset Sources                    |     |

| Brown-out Reset (BOR)            | 61  |

| Illegal Instruction Trap         | 61  |

| Trap Lockout                     | 61  |

| Uninitialized W Register Trap    | 61  |

| Watchdog Time-out                | 61  |

| Reset Timing Requirements        | 187 |

| Revision History                 | 217 |

| Run-Time Self-Programming (RTSP) |     |

| S                                |     |

| Simple Capture Event Mode                 |     |

|-------------------------------------------|-----|

| Buffer Operation                          |     |

| Hall Sensor Mode                          |     |

| Prescaler                                 | 81  |

| Timer2 and Timer3 Selection Mode          |     |

| Simple OCx/PWM Mode Timing Requirements . | 191 |

| Simple Output Compare Match Mode 86                              |

|------------------------------------------------------------------|

| Simple PWM Mode 86                                               |

| Input Pin Fault Protection 86                                    |

| Period 87                                                        |

| Software Simulator (MPLAB SIM) 169                               |

| Software Stack Pointer, Frame Pointer 16                         |

| CALL Stack Frame 33                                              |

| SPI Module                                                       |

| Framed SPI Support 100                                           |

| Operating Function Description                                   |

| Operation During CPU Idle Mode 101                               |

| Operation During CPU Sleep Mode                                  |

| SDOx Disable 99                                                  |

| Slave Select Synchronization 101                                 |

| SPI1 Register Map 102                                            |

| Timing Requirements                                              |

| Master Mode (CKE = 0) 196                                        |

| Master Mode (CKE = 1) 197                                        |

| Slave Mode (CKE = 0) 198                                         |

| Slave Mode (CKE = 1) 200                                         |

| Word and Byte Communication 99                                   |

| Status Bits, Their Significance and the Initialization Condition |

| for RCON Register, Case 1 154                                    |

| Status Bits, Their Significance and the Initialization Condition |

| for RCON Register, Case 2 154                                    |

| STATUS Register 16                                               |

| Symbols Used in Opcode Descriptions 160                          |

| System Integration 141                                           |

| Register Map 158                                                 |

|                                                                  |

#### т

| Table Instruction Operation Summary    | 43  |

|----------------------------------------|-----|

| Temperature and Voltage Specifications |     |

| AC                                     | 181 |

| DC                                     | 172 |

| Timer1 Module                          | 67  |

| 16-Bit Asynchronous Counter Mode       | 67  |

| 16-Bit Synchronous Counter Mode        | 67  |

| 16-Bit Timer Mode                      | 67  |

| Gate Operation                         | 68  |

| Interrupt                              | 68  |

| Operation During Sleep Mode            | 68  |

| Prescaler                              | 68  |

| Real-Time Clock                        |     |

| Interrupts                             | 68  |

| Oscillator Operation                   | 68  |

| Register Map                           |     |

| Timer2 and Timer3 Selection Mode       | 85  |

| Timer2/3 Module                        | 71  |

| 16-Bit Timer Mode                      |     |

| 32-Bit Synchronous Counter Mode        | 71  |

| 32-Bit Timer Mode                      | 71  |

| ADC Event Trigger                      | 74  |

| Gate Operation                         | 74  |

| Interrupt                              | 74  |

| Operation During Sleep Mode            | 74  |

| Register Map                           |     |

| Timer Prescaler                        |     |

| Timer4/5 Module                        |     |

| Register Map                           |     |

| Timing Diagrams                        |     |

| A/D Conversion                         |     |

| Low-Speed (ASAM = 0, SSRC = 000)       | 208 |

| Band Gap Start-up Time                 |     |

| Brown-out Reset Characteristics        |     |

| CAN Bit                                | -   |

|                                        | -   |