Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20 MIPS                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 30                                                                            |

| Program Memory Size        | 24KB (8K x 24)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 1K x 8                                                                        |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 13x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-TQFP                                                                       |

| Supplier Device Package    | 44-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f3014-20e-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

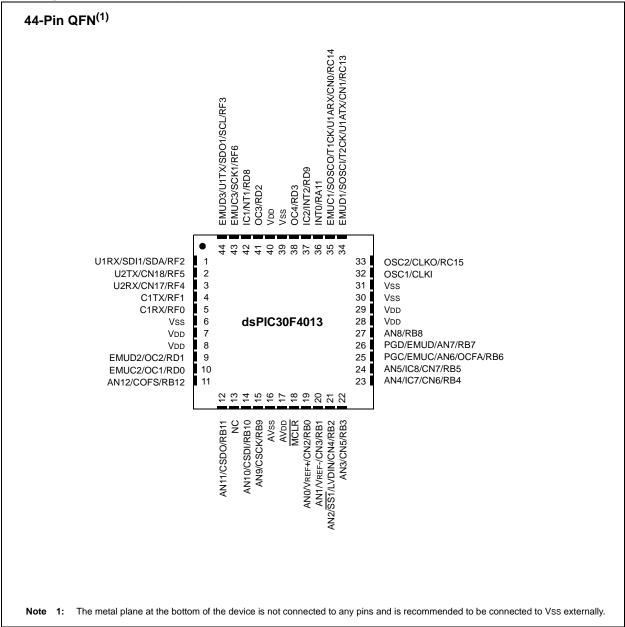

## Pin Diagrams (Continued)

## dsPIC30F3014/4013

NOTES:

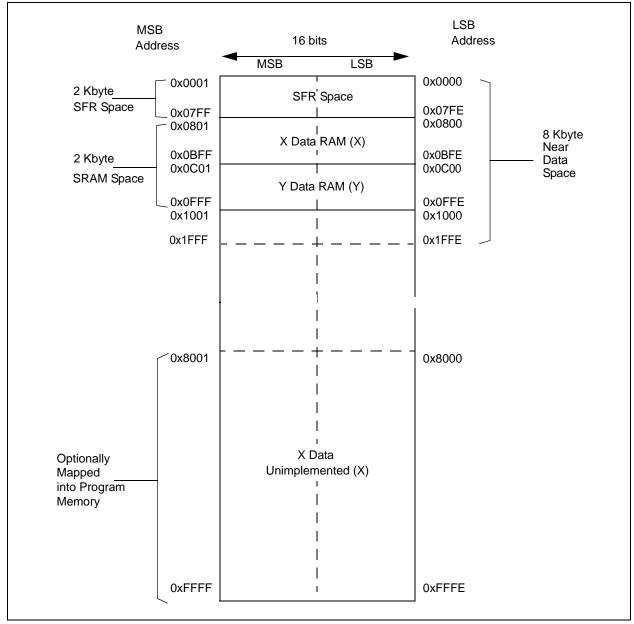

## 3.2 Data Address Space

The core has two data spaces. The data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths.

#### 3.2.1 DATA SPACE MEMORY MAP

The data space memory is split into two blocks, X and Y data space. A key element of this architecture is that Y space is a subset of X space, and is fully contained within X space. In order to provide an apparent Linear Addressing space, X and Y spaces have contiguous addresses.

When executing any instruction other than one of the MAC class of instructions, the X block consists of the 64-Kbyte data address space (including all Y addresses). When executing one of the MAC class of instructions, the X block consists of the 64-Kbyte data address space excluding the Y address block (for data reads only). In other words, all other instructions regard the entire data memory as one composite address space. The MAC class instructions extract the Y address space from data space and address it using EAs sourced from W10 and W11. The remaining X data space is addressed using W8 and W9. Both address spaces are concurrently accessed only with the MAC class instructions.

The data space memory map is shown in Figure 3-7.

#### FIGURE 3-7: dsPIC30F3014/dsPIC30F4013 DATA SPACE MEMORY MAP

## 8.0 INTERRUPTS

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

The dsPIC30F sensor and general purpose families have up to 41 interrupt sources and 4 processor exceptions (traps) which must be arbitrated based on a priority scheme.

The CPU is responsible for reading the Interrupt Vector Table (IVT) and transferring the address contained in the interrupt vector to the program counter. The interrupt vector is transferred from the program data bus into the program counter via a 24-bit wide multiplexer on the input of the program counter.

The Interrupt Vector Table (IVT) and Alternate Interrupt Vector Table (AIVT) are placed near the beginning of program memory (0x000004). The IVT and AIVT are shown in Figure 8-1.

The interrupt controller is responsible for preprocessing the interrupts and processor exceptions prior to them being presented to the processor core. The peripheral interrupts and traps are enabled, prioritized and controlled using centralized Special Function Registers:

- IFS0<15:0>, IFS1<15:0>, IFS2<15:0> All interrupt request flags are maintained in these three registers. The flags are set by their respective peripherals or external signals and they are cleared via software.

- IEC0<15:0>, IEC1<15:0>, IEC2<15:0> All interrupt enable control bits are maintained in these three registers. These control bits are used to individually enable interrupts from the peripherals or external signals.

- IPC0<15:0>... IPC10<7:0> The user-assignable priority level associated with each of these 41 interrupts is held centrally in these eleven registers.

- IPL<3:0>

The current CPU priority level is explicitly stored in the IPL bits. IPL<3> is present in the CORCON register, whereas IPL<2:0> are present in the STATUS register (SR) in the processor core.

- INTCON1<15:0>, INTCON2<15:0> Global interrupt control functions are derived from these two registers. INTCON1 contains the control and status flags for the processor exceptions. The INTCON2 register controls the external interrupt request signal behavior and the use of the alternate vector table.

- **Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

All interrupt sources can be user-assigned to one of 7 priority levels, 1 through 7, via the IPCx registers. Each interrupt source is associated with an interrupt vector, as shown in Table 8-1. Levels 7 and 1 represent the highest and lowest maskable priorities, respectively.

**Note:** Assigning a priority level of '0' to an interrupt source is equivalent to disabling that interrupt.

If the NSTDIS bit (INTCON1<15>) is set, nesting of interrupts is prevented. Thus, if an interrupt is currently being serviced, processing of a new interrupt is prevented even if the new interrupt is of higher priority than the one currently being serviced.

Note: The IPL bits become read-only whenever the NSTDIS bit has been set to '1'.

Certain interrupts have specialized control bits for features like edge or level triggered interrupts, interrupt-on-change, etc. Control of these features remains within the peripheral module which generates the interrupt.

The DISI instruction can be used to disable the processing of interrupts of priorities 6 and lower for a certain number of instructions, during which the DISI bit (INTCON2<14>) remains set.

When an interrupt is serviced, the PC is loaded with the address stored in the vector location in program memory that corresponds to the interrupt. There are 63 different vectors within the IVT (refer to Table 8-1) These vectors are contained in locations 0x000004 through 0x0000FE of program memory (refer to Table 8-1). These locations contain 24-bit addresses. In order to preserve robustness, an address error trap takes place should the PC attempt to fetch any of these words during normal execution. This prevents execution of random data as a result of accidentally decrementing a PC into vector space, accidentally mapping a data space address into vector space or the PC rolling over to 0x000000 after reaching the end of implemented program memory space. Execution of a GOTO instruction to this vector space also generates an address error trap.

## 8.5 Alternate Vector Table

In program memory, the Interrupt Vector Table (IVT) is followed by the Alternate Interrupt Vector Table (AIVT), as shown in Figure 8-1. Access to the alternate vector table is provided by the ALTIVT bit in the INTCON2 register. If the ALTIVT bit is set, all interrupt and exception processes use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors. The AIVT supports emulation and debugging efforts by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time.

If the AIVT is not required, the program memory allocated to the AIVT may be used for other purposes. AIVT is not a protected section and may be freely programmed by the user.

#### 8.6 Fast Context Saving

A context saving option is available using shadow registers. Shadow registers are provided for the DC, N, OV, Z and C bits in SR, and the registers, W0 through W3. The shadows are only one level deep. The shadow registers are accessible using the PUSH.S and POP.S instructions only.

When the processor vectors to an interrupt, the PUSH.S instruction can be used to store the current value of the aforementioned registers into their respective shadow registers.

If an ISR of a certain priority uses the PUSH.S and POP.S instructions for fast context saving, then a higher priority ISR should not include the same instructions. Users must save the key registers in software during a lower priority interrupt if the higher priority ISR uses fast context saving.

### 8.7 External Interrupt Requests

The interrupt controller supports up to five external interrupt request signals, INTO-INT4. These inputs are edge sensitive; they require a low-to-high or a high-to-low transition to generate an interrupt request. The INTCON2 register has three bits, INTOEP-INT2EP, that select the polarity of the edge detection circuitry.

## 8.8 Wake-up from Sleep and Idle

The interrupt controller may be used to wake-up the processor from either Sleep or Idle mode, if Sleep or Idle mode is active when the interrupt is generated.

If an enabled interrupt request of sufficient priority is received by the interrupt controller, then the standard interrupt request is presented to the processor. At the same time, the processor wakes up from Sleep or Idle and begins execution of the Interrupt Service Routine (ISR) needed to process the interrupt request.

# dsPIC30F3014/4013

## dsPIC30F3014/4013

NOTES:

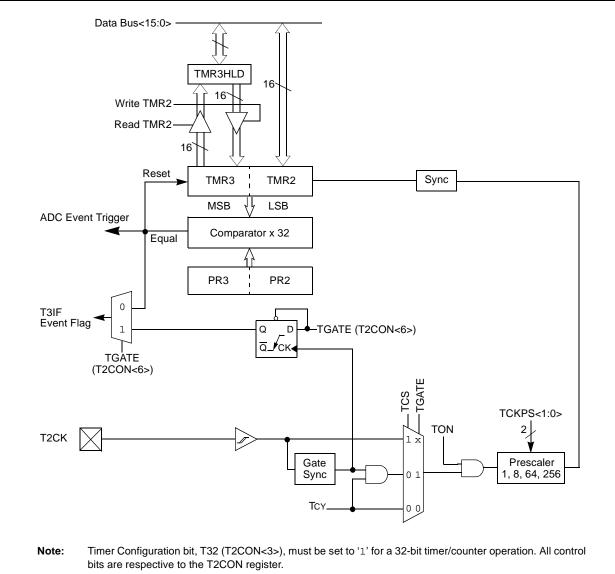

#### 13.4.2 PWM PERIOD

The PWM period is specified by writing to the PRx register. The PWM period can be calculated using Equation 13-1.

### EQUATION 13-1:

$PWM \text{ period } = [(PRx) + 1] \bullet 4 \bullet \text{Tosc} \bullet$ (TMRx prescale value)

PWM frequency is defined as 1/[PWM period].

When the selected TMRx is equal to its respective Period register, PRx, the following four events occur on the next increment cycle:

- TMRx is cleared.

- The OCx pin is set.

- Exception 1: If PWM duty cycle is 0x0000, the OCx pin remains low.

- Exception 2: If duty cycle is greater than PRx, the pin remains high.

- The PWM duty cycle is latched from OCxRS into OCxR.

- The corresponding timer interrupt flag is set.

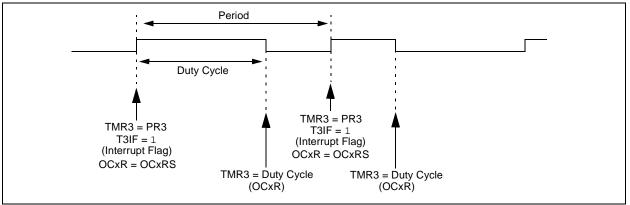

See Figure 13-2 for key PWM period comparisons. Timer3 is referred to in Figure 13-2 for clarity.

### FIGURE 13-2: PWM OUTPUT TIMING

## 14.4.2 10-BIT MODE SLAVE RECEPTION

Once addressed, the master can generate a Repeated Start, reset the high byte of the address and set the R\_W bit without generating a Stop bit, thus initiating a slave transmit operation.

## 14.5 Automatic Clock Stretch

In the Slave modes, the module can synchronize buffer reads and write to the master device by clock stretching.

#### 14.5.1 TRANSMIT CLOCK STRETCHING

Both 10-Bit and 7-Bit Transmit modes implement clock stretching by asserting the SCLREL bit after the falling edge of the ninth clock, if the TBF bit is cleared, indicating the buffer is empty.

In Slave Transmit modes, clock stretching is always performed irrespective of the STREN bit.

Clock synchronization takes place following the ninth clock of the transmit sequence. If the device samples an ACK on the falling edge of the ninth clock and if the TBF bit is still clear, then the SCLREL bit is automatically cleared. The SCLREL being cleared to '0' asserts the SCL line low. The user's ISR must set the SCLREL bit before transmission is allowed to continue. By holding the SCL line low, the user has time to service the ISR and load the contents of the I2CTRN before the master device can initiate another transmit sequence.

- Note 1: If the user loads the contents of I2CTRN, setting the TBF bit before the falling edge of the ninth clock, the SCLREL bit is not be cleared and clock stretching does not occur.

- **2:** The SCLREL bit can be set in software, regardless of the state of the TBF bit.

#### 14.5.2 RECEIVE CLOCK STRETCHING

The STREN bit in the I2CCON register can be used to enable clock stretching in Slave Receive mode. When the STREN bit is set, the SCL pin is held low at the end of each data receive sequence.

#### 14.5.3 CLOCK STRETCHING DURING 7-BIT ADDRESSING (STREN = 1)

When the STREN bit is set in Slave Receive mode, the SCL line is held low when the buffer register is full. The method for stretching the SCL output is the same for both 7 and 10-Bit Addressing modes.

Clock stretching takes place following the ninth clock of the receive sequence. <u>On</u> the falling edge of the ninth clock at the end of the ACK sequence, if the RBF bit is set, the SCLREL bit is automatically cleared, forcing the SCL output to be held low. The user's ISR must set the SCLREL bit before reception is allowed to continue. By holding the SCL line low, the user has time to service the ISR and read the contents of the I2CRCV before the master device can initiate another receive sequence. This prevents buffer overruns from occurring.

- Note 1: If the user reads the contents of the I2CRCV, clearing the RBF bit before the falling edge of the ninth clock, the SCLREL bit is not cleared and clock stretching does not occur.

- 2: The SCLREL bit can be set in software regardless of the state of the RBF bit. The user should be careful to clear the RBF bit in the ISR before the next receive sequence in order to prevent an overflow condition.

#### 14.5.4 CLOCK STRETCHING DURING 10-BIT ADDRESSING (STREN = 1)

Clock stretching takes place automatically during the addressing sequence. Because this module has a register for the entire address, it is not necessary for the protocol to wait for the address to be updated.

After the address phase is complete, clock stretching occurs on each data receive or transmit sequence, as described earlier.

## 14.6 Software Controlled Clock Stretching (STREN = 1)

When the STREN bit is '1', the SCLREL bit can be cleared by software to allow software to control the clock stretching. Program logic synchronizes writes to the SCLREL bit with the SCL clock. Clearing the SCLREL bit does not assert the SCL output until the module detects a falling edge on the SCL output and SCL is sampled low. If the SCLREL bit is cleared by the user while the SCL line has been sampled low, the SCL output is asserted (held low). The SCL output remains low until the SCLREL bit is set and all other devices on the I<sup>2</sup>C bus have deasserted SCL. This ensures that a write to the SCLREL bit does not violate the minimum high time requirement for SCL.

If the STREN bit is '0', a software write to the SCLREL bit is disregarded and has no effect on the SCLREL bit.

## 14.7 Interrupts

The I<sup>2</sup>C module generates two interrupt flags, MI2CIF (I<sup>2</sup>C Master Interrupt Flag) and SI2CIF (I<sup>2</sup>C Slave Interrupt Flag). The MI2CIF interrupt flag is activated on completion of a master message event. The SI2CIF interrupt flag is activated on detection of a message directed to the slave.

## 14.8 Slope Control

The I<sup>2</sup>C standard requires slope control on the SDA and SCL signals for Fast mode (400 kHz). The control bit, DISSLW, enables the user to disable slew rate control if desired. It is necessary to disable the slew rate control for 1 MHz mode.

## 14.9 IPMI Support

The control bit, IPMIEN, enables the module to support Intelligent Peripheral Management Interface (IPMI). When this bit is set, the module accepts and acts upon all addresses.

#### 14.10 General Call Address Support

The general call address can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledgement.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all '0's with R\_W = 0.

The general call address is recognized when the General Call Enable (GCEN) bit is set (I2CCON<7> = 1). Following a Start bit detection, 8 bits are shifted into I2CRSR and the address is compared with I2CADD, and is also compared with the general call address which is fixed in hardware.

If a general call address match occurs, the I2CRSR is transferred to the I2CRCV after the eighth clock, the RBF flag is set and on the falling edge of the ninth bit (ACK bit), the Master Event Interrupt Flag (MI2CIF) is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the I2CRCV to determine if the address was device-specific or a general call address.

## 14.11 I<sup>2</sup>C Master Support

As a master device, six operations are supported:

- Assert a Start condition on SDA and SCL.

- Assert a Restart condition on SDA and SCL.

- Write to the I2CTRN register initiating transmission of data/address.

- Generate a Stop condition on SDA and SCL.

- Configure the I<sup>2</sup>C port to receive data.

- Generate an ACK condition at the end of a received byte of data.

## 14.12 I<sup>2</sup>C Master Operation

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus is not released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the data direction bit. In this case, the data direction bit ( $R_W$ ) is logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an ACK bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the data direction bit. In this case, the data direction bit (R\_W) is logic '1'. Thus, the first byte transmitted is a 7-bit slave address, followed by a '1' to indicate the receive bit. Serial data is received via SDA while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an ACK bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

#### 14.12.1 I<sup>2</sup>C MASTER TRANSMISSION

Transmission of a data byte, a 7-bit address or the second half of a 10-bit address, is accomplished by simply writing a value to I2CTRN register. The user should only write to I2CTRN when the module is in a Wait state. This action sets the Buffer Full Flag (TBF) and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/ data is shifted out onto the SDA pin after the falling edge of SCL is asserted. The Transmit Status Flag, TRSTAT (I2CSTAT<14>), indicates that a master transmit is in progress.

# dsPIC30F3014/4013

#### REGISTER 20-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

Reset after FSCM switches the oscillator to (Group 1) FRC.

bit 5 LOCK: PLL Lock Status bit (read-only) 1 = Indicates that PLL is in lock 0 = Indicates that PLL is out of lock (or disabled) Reset on POR or BOR. Reset when a valid clock switching sequence is initiated. Set when PLL lock is achieved after a PLL start. Reset when lock is lost. Read zero when PLL is not selected as a system clock bit 4 Unimplemented: Read as '0' bit 3 CF: Clock Fail Detect bit (read/clearable by application) 1 = FSCM has detected clock failure 0 = FSCM has NOT detected clock failure Reset on POR or BOR. Reset when a valid clock switching sequence is initiated. Set when clock fail detected bit 2 Unimplemented: Read as '0' bit 1 LPOSCEN: 32 kHz Secondary (LP) Oscillator Enable bit 1 = Secondary oscillator is enabled 0 = Secondary oscillator is disabled Reset on POR or BOR. **OSWEN:** Oscillator Switch Enable bit bit 0 1 = Request oscillator switch to selection specified by NOSC<2:0> bits 0 = Oscillator switch is complete Reset on POR or BOR. Reset after a successful clock switch. Reset after a redundant clock switch.

## 23.1 DC Characteristics

#### TABLE 23-1: OPERATING MIPS vs. VOLTAGE

| Voo Benge | Tomp Dongo     | Max MIPS        |                 |  |  |

|-----------|----------------|-----------------|-----------------|--|--|

| VDD Range | Temp Range     | dsPIC30FXXX-30I | dsPIC30FXXX-20E |  |  |

| 4.5-5.5V  | -40°C to 85°C  | 30              | —               |  |  |

| 4.5-5.5V  | -40°C to 125°C | —               | 20              |  |  |

| 3.0-3.6V  | -40°C to 85°C  | 15              | —               |  |  |

| 3.0-3.6V  | -40°C to 125°C | —               | 10              |  |  |

| 2.5-3.0V  | -40°C to 85°C  | 10              | —               |  |  |

#### TABLE 23-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                       | Symbol         | Min         | Тур         | Max  | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|-------------|------|------|

| dsPIC30F3014-30I                                                                                                                                             |                |             |             |      |      |

| dsPIC30F4013-30I                                                                                                                                             |                |             |             |      |      |

| Operating Junction Temperature Range                                                                                                                         | Τ <sub>J</sub> | -40         |             | +125 | °C   |

| Operating Ambient Temperature Range                                                                                                                          | T <sub>A</sub> | -40         |             | +85  | °C   |

| dsPIC30F3014-20E<br>dsPIC30F4013-20E                                                                                                                         |                |             |             |      |      |

| Operating Junction Temperature Range                                                                                                                         | Τ <sub>J</sub> | -40         |             | +150 | °C   |

| Operating Ambient Temperature Range                                                                                                                          | T <sub>A</sub> | -40         |             | +125 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$P_{INT} = V_{DD} \times (I_{DD} - \Sigma I_{OH})$                                                 | PD             | PINT + PI/O |             |      | W    |

| I/O Pin power dissipation:<br>$P_{\text{I/O}} = \sum (\{ V_{\text{DD}} - V_{\text{OH}} \} \times I_{\text{OH}}) + \sum (V_{\text{OL}} \times I_{\text{OL}})$ |                |             |             |      |      |

| Maximum Allowed Power Dissipation                                                                                                                            | PDMAX          | (           | TJ — TA)/θ. | IA   | W    |

#### TABLE 23-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                      | Symbol | Тур | Max  | Unit | Notes |

|-----------------------------------------------------|--------|-----|------|------|-------|

| Package Thermal Resistance, 40-pin DIP (P)          | θJA    |     | 47   | °C/W | 1     |

| Package Thermal Resistance, 44-pin TQFP (10x10x1mm) | θJA    | —   | 39.3 | °C/W | 1     |

| Package Thermal Resistance, 44-pin QFN              | θJA    | -   | 27.8 | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-ja ( $\theta$ JA) numbers are achieved by package simulations.

#### TABLE 23-11: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS |        |                                  | Standard Oper<br>(unless otherw<br>Operating temp | ise state | <b>ed)</b><br>-40°C ≤ | ≤ Ta ≤ +8 | 5°C for | Industrial<br>r Extended |

|--------------------|--------|----------------------------------|---------------------------------------------------|-----------|-----------------------|-----------|---------|--------------------------|

| Param<br>No.       | Symbol | Character                        | istic                                             | Min       | Typ <sup>(1)</sup>    | Max       | Units   | Conditions               |

| BO10               | VBOR   | BOR Voltage on VDD<br>Transition | BORV = 11 <sup>(3)</sup>                          |           |                       |           | V       | Not in operating range   |

|                    |        | High-to-Low <sup>(2)</sup>       | BORV = 10                                         | 2.6       | _                     | 2.71      | V       |                          |

|                    |        |                                  | BORV = 01                                         | 4.1       | _                     | 4.4       | V       |                          |

|                    |        |                                  | BORV = 00                                         | 4.58      | —                     | 4.73      | V       |                          |

| BO15               | VBHYS  |                                  | •                                                 |           | 5                     |           | mV      |                          |

Note 1: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: These parameters are characterized but not tested in manufacturing.

**3:** '11' values not in usable operating range.

#### TABLE 23-12: DC CHARACTERISTICS: PROGRAM AND EEPROM

| DC CHARACTERISTICS |        |                                     |      |                    | ise state | ed)<br>-40°C : | s: 2.5V to 5.5V<br>≤ TA ≤ +85°C for Industrial<br>≤ TA ≤ +125°C for Extended |  |

|--------------------|--------|-------------------------------------|------|--------------------|-----------|----------------|------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                      | Min  | Typ <sup>(1)</sup> | Max       | Units          | Conditions                                                                   |  |

|                    |        | Data EEPROM Memory <sup>(2)</sup>   |      |                    |           |                |                                                                              |  |

| D120               | ED     | Byte Endurance                      | 100K | 1M                 | —         | E/W            | $-40^{\circ}C \le TA \le +85^{\circ}C$                                       |  |

| D121               | Vdrw   | VDD for Read/Write                  | Vmin | _                  | 5.5       | V              | Using EECON to read/write<br>VMIN = Minimum operating<br>voltage             |  |

| D122               | TDEW   | Erase/Write Cycle Time              | 0.8  | 2                  | 2.6       | ms             | RTSP                                                                         |  |

| D123               | Tretd  | Characteristic Retention            | 40   | 100                | —         | Year           | Provided no other specifications are violated                                |  |

| D124               | IDEW   | IDD During Programming              |      | 10                 | 30        | mA             | Row Erase                                                                    |  |

|                    |        | Program Flash Memory <sup>(2)</sup> |      |                    |           |                |                                                                              |  |

| D130               | Eр     | Cell Endurance                      | 10K  | 100K               | —         | E/W            | $-40^{\circ}C \le TA \le +85^{\circ}C$                                       |  |

| D131               | Vpr    | VDD for Read                        | VMIN | _                  | 5.5       | V              | VміN = Minimum operating<br>voltage                                          |  |

| D132               | VEB    | VDD for Bulk Erase                  | 4.5  |                    | 5.5       | V              |                                                                              |  |

| D133               | VPEW   | VDD for Erase/Write                 | 3.0  |                    | 5.5       | V              |                                                                              |  |

| D134               | TPEW   | Erase/Write Cycle Time              | 0.8  | 2                  | 2.6       | ms             | RTSP                                                                         |  |

| D135               | Tretd  | Characteristic Retention            | 40   | 100                | —         | Year           | Provided no other specifications are violated                                |  |

| D137               | IPEW   | IDD During Programming              | —    | 10                 | 30        | mA             | Row Erase                                                                    |  |

| D138               | IEB    | IDD During Programming              | —    | 10                 | 30        | mA             | Bulk Erase                                                                   |  |

Note 1: Data in "Typ" column is at 5V, 25°C unless otherwise stated.

2: These parameters are characterized but not tested in manufacturing.

## 23.2 AC Characteristics and Timing Parameters

The information contained in this section defines dsPIC30F AC characteristics and timing parameters.

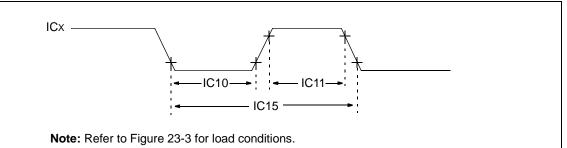

#### **FIGURE 23-9: INPUT CAPTURE (CAPx) TIMING CHARACTERISTICS**

#### TABLE 23-25: INPUT CAPTURE TIMING REQUIREMENTS

| AC CHARACTERISTICS                                |         |                       | Standard Operat<br>(unless otherwis<br>Operating temper | e stated)<br>ature -40°C ≤ TA | 2.5V to 5.5 <sup>°</sup><br>\ ≤ +85°C fo<br>\ ≤ +125°C | or Industr |                                  |

|---------------------------------------------------|---------|-----------------------|---------------------------------------------------------|-------------------------------|--------------------------------------------------------|------------|----------------------------------|

| Param<br>No. Symbol Characteristic <sup>(1)</sup> |         |                       | ristic <sup>(1)</sup>                                   | Min                           | Max                                                    | Units      | Conditions                       |

| IC10                                              | TccL    | ICx Input Low Time    | No prescaler                                            | 0.5 TCY + 20                  | _                                                      | ns         |                                  |

|                                                   |         |                       | With prescaler                                          | 10                            | _                                                      | ns         |                                  |

| IC11                                              | TccH    | ICx Input High Time   | No prescaler                                            | 0.5 TCY + 20                  | _                                                      | ns         |                                  |

|                                                   |         |                       | With prescaler                                          | 10                            | _                                                      | ns         |                                  |

| IC15                                              | TccP    | ICx Input Period      |                                                         | (2 TCY + 40)/N                | _                                                      | ns         | N = prescale<br>value (1, 4, 16) |

| Note 1:                                           | These p | arameters are charact | erized but not teste                                    | d in manufacturing            | g.                                                     | •          |                                  |

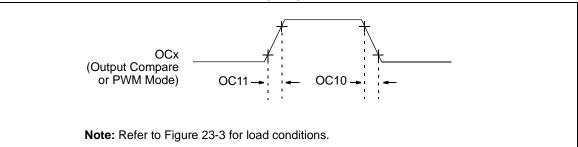

#### FIGURE 23-10: **OUTPUT COMPARE MODULE (OCx) TIMING CHARACTERISTICS**

#### TABLE 23-26: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}\mbox{C} \leq \mbox{Ta} \leq +85^{\circ}\mbox{C for Industrial} \\ & -40^{\circ}\mbox{C} \leq \mbox{Ta} \leq +125^{\circ}\mbox{C for Extended} \end{array}$ |                    |     |       |                    |  |

|--------------------|--------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup> | Min                                                                                                                                                                                                                                                                                                               | Тур <sup>(2)</sup> | Мах | Units | Conditions         |  |

| OC10               | TccF   | OCx Output Fall Time          | —                                                                                                                                                                                                                                                                                                                 | —                  | _   | ns    | See Parameter DO32 |  |

| OC11               | TccR   | OCx Output Rise Time          | _                                                                                                                                                                                                                                                                                                                 | —                  |     | ns    | See Parameter DO31 |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

| TABLE 23-34: 1 | l <sup>2</sup> C™ BUS DATA 1 | <b>FIMING REQUIREMENTS</b> | (MASTER MODE) ( | CONTINUED) |

|----------------|------------------------------|----------------------------|-----------------|------------|

|----------------|------------------------------|----------------------------|-----------------|------------|

| AC CHA       | ARACTER | ISTICS                       |                           | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |       |                        |  |  |

|--------------|---------|------------------------------|---------------------------|------------------------------------------------------|------|-------|------------------------|--|--|

| Param<br>No. | Symbol  | Charac                       | teristic                  | Min <sup>(1)</sup>                                   | Max  | Units | Conditions             |  |  |

| IM21         | TR:SCL  | SDA and SCL                  | 100 kHz mode              | —                                                    | 1000 | ns    | CB is specified to be  |  |  |

|              |         | Rise Time                    | 400 kHz mode              | 20 + 0.1 Св                                          | 300  | ns    | from 10 to 400 pF      |  |  |

|              |         |                              | 1 MHz mode <sup>(2)</sup> | —                                                    | 300  | ns    |                        |  |  |

| IM25         | TSU:DAT | Data Input                   | 100 kHz mode              | 250                                                  |      | ns    |                        |  |  |

|              |         | Setup Time                   | 400 kHz mode              | 100                                                  |      | ns    |                        |  |  |

|              |         |                              | 1 MHz mode <sup>(2)</sup> | —                                                    | —    | ns    |                        |  |  |

| IM26         | THD:DAT | Data Input                   | 100 kHz mode              | 0                                                    |      | ns    |                        |  |  |

|              |         | Hold Time                    | 400 kHz mode              | 0                                                    | 0.9  | μs    |                        |  |  |

|              |         |                              | 1 MHz mode <sup>(2)</sup> | —                                                    | —    | ns    |                        |  |  |

| IM30         | TSU:STA | Start Condition              | 100 kHz mode              | Tcy/2 (BRG + 1)                                      | _    | μs    | Only relevant for      |  |  |

|              |         | Setup Time                   | 400 kHz mode              | Tcy/2 (BRG + 1)                                      | _    | μs    | Repeated Start         |  |  |

|              |         |                              | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                      | _    | μs    | condition              |  |  |

| IM31         | THD:STA | Start Condition<br>Hold Time | 100 kHz mode              | Tcy/2 (BRG + 1)                                      |      | μs    | After this period, the |  |  |

|              |         |                              | 400 kHz mode              | Tcy/2 (BRG + 1)                                      | _    | μs    | first clock pulse is   |  |  |

|              |         |                              | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                      | _    | μs    | generated              |  |  |

| IM33         | TSU:STO | Stop Condition               | 100 kHz mode              | Tcy/2 (BRG + 1)                                      |      | μs    |                        |  |  |

|              |         | Setup Time                   | 400 kHz mode              | Tcy/2 (BRG + 1)                                      | _    | μs    |                        |  |  |

|              |         |                              | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                      | —    | μs    |                        |  |  |

| IM34         | THD:STO | Stop Condition               | 100 kHz mode              | Tcy/2 (BRG + 1)                                      | —    | ns    |                        |  |  |

|              |         | Hold Time                    | 400 kHz mode              | Tcy/2 (BRG + 1)                                      | —    | ns    |                        |  |  |

|              |         |                              | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                      | —    | ns    |                        |  |  |

| IM40         | TAA:SCL | Output Valid                 | 100 kHz mode              | —                                                    | 3500 | ns    |                        |  |  |

|              |         | From Clock                   | 400 kHz mode              |                                                      | 1000 | ns    |                        |  |  |

|              |         |                              | 1 MHz mode <sup>(2)</sup> | _                                                    | —    | ns    |                        |  |  |

| IM45         | TBF:SDA | Bus Free Time                | 100 kHz mode              | 4.7                                                  |      | μS    | Time the bus must be   |  |  |

|              |         |                              | 400 kHz mode              | 1.3                                                  | _    | μs    | free before a new      |  |  |

|              |         |                              | 1 MHz mode <sup>(2)</sup> | _                                                    |      | μS    | transmission can start |  |  |

| IM50         | Св      | Bus Capacitive L             | oading                    | —                                                    | 400  | pF    |                        |  |  |

Note 1: BRG is the value of the I<sup>2</sup>C Baud Rate Generator. Refer to Section 21. "Inter-Integrated Circuit™ (I<sup>2</sup>C)" in the "dsPIC30F Family Reference Manual" (DS70046).

**2:** Maximum pin capacitance = 10 pF for all  $I^2C$  pins (for 1 MHz mode only).

## 24.0 PACKAGING INFORMATION

## 24.1 Package Marking Information

## 40-Lead PDIP

#### 44-Lead TQFP

#### 44-Lead QFN

## Example

#### Example

#### Example

| Leger | d: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|-------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note: | be carrie                                 | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>s for customer-specific information.                                                                                                                                                                                              |

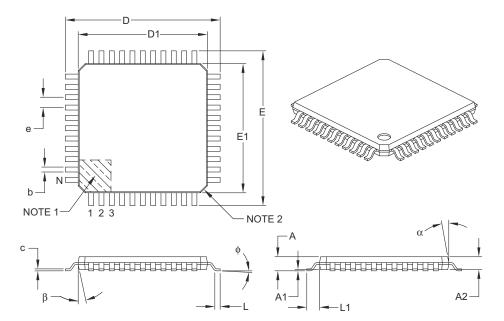

### 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS  |             |           |      |  |

|--------------------------|--------------|-------------|-----------|------|--|

| Dimer                    | nsion Limits | MIN         | NOM       | MAX  |  |

| Number of Leads          | Ν            |             | 44        |      |  |

| Lead Pitch               | е            |             | 0.80 BSC  |      |  |

| Overall Height           | А            | -           | -         | 1.20 |  |

| Molded Package Thickness | A2           | 0.95        | 1.00      | 1.05 |  |

| Standoff                 | A1           | 0.05        | -         | 0.15 |  |

| Foot Length              | L            | 0.45        | 0.60      | 0.75 |  |

| Footprint                | L1           | 1.00 REF    |           |      |  |

| Foot Angle               | φ            | 0°          | 3.5°      | 7°   |  |

| Overall Width            | E            |             | 12.00 BSC |      |  |

| Overall Length           | D            |             | 12.00 BSC |      |  |

| Molded Package Width     | E1           |             | 10.00 BSC |      |  |

| Molded Package Length    | D1           |             | 10.00 BSC |      |  |

| Lead Thickness           | С            | 0.09        | -         | 0.20 |  |

| Lead Width               | b            | 0.30        | 0.37      | 0.45 |  |

| Mold Draft Angle Top     | α            | 11° 12° 13° |           |      |  |

| Mold Draft Angle Bottom  | β            | 11°         | 12°       | 13°  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B

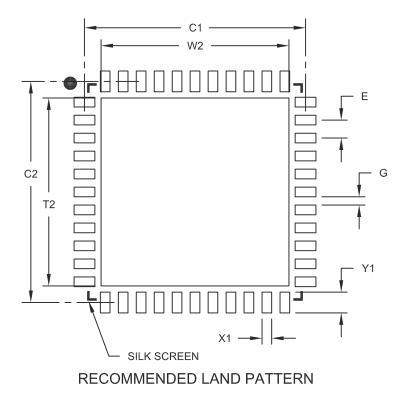

## 44-Lead Plastic Quad Flat, No Lead Package (ML) – 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                      |    | MILLIMETERS |      |      |

|----------------------------|----|-------------|------|------|

| Dimension Limits           |    | MIN         | NOM  | MAX  |

| Contact Pitch              | E  | 0.65 BSC    |      |      |

| Optional Center Pad Width  | W2 |             |      | 6.80 |

| Optional Center Pad Length | T2 |             |      | 6.80 |

| Contact Pad Spacing        | C1 |             | 8.00 |      |

| Contact Pad Spacing        | C2 |             | 8.00 |      |

| Contact Pad Width (X44)    | X1 |             |      | 0.35 |

| Contact Pad Length (X44)   | Y1 |             |      | 0.80 |

| Distance Between Pads      | G  | 0.25        |      |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103A

## **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

**Malaysia - Kuala Lumpur** Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-6578-300 Fax: 886-3-6578-370

**Taiwan - Kaohsiung** Tel: 886-7-213-7830 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

08/04/10