#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

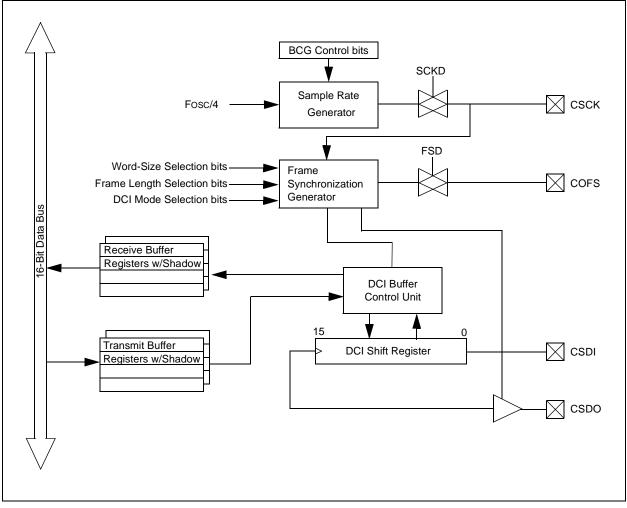

#### Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                        |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 20 MIPS                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 30                                                                           |

| Program Memory Size        | 24KB (8K x 24)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 13x12b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Through Hole                                                                 |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                     |

| Supplier Device Package    | 40-PDIP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f3014-20i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

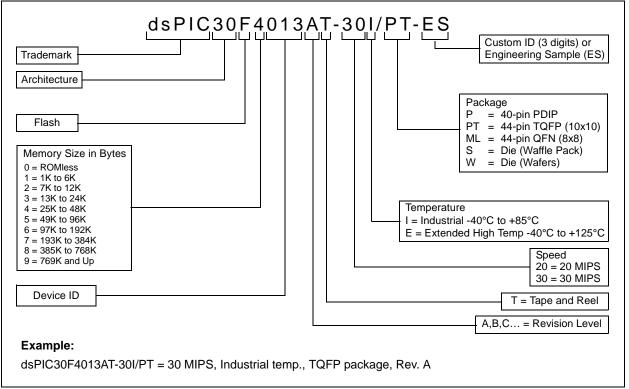

## FIGURE 7-2: BLOCK DIAGRAM OF A SHARED PORT STRUCTURE

## 7.2 Configuring Analog Port Pins

The use of the ADPCFG and TRIS registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) is converted.

When the PORT register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin that is defined as a digital input (including the ANx pins) may cause the input buffer to consume current that exceeds the device specifications.

#### 7.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

#### EXAMPLE 7-1: PORT WRITE/READ EXAMPLE

| MOV 0xFF00, W0  | ; Configure PORTB<15:8>         |

|-----------------|---------------------------------|

|                 | ; as inputs                     |

| MOV W0, TRISB   | ; and PORTB<7:0> as outputs     |

| NOP             | ; additional instruction        |

|                 | cycle                           |

| BTSS PORTB, #11 | ; bit test RB11 and skip if set |

|                 |                                 |

## 8.0 INTERRUPTS

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

The dsPIC30F sensor and general purpose families have up to 41 interrupt sources and 4 processor exceptions (traps) which must be arbitrated based on a priority scheme.

The CPU is responsible for reading the Interrupt Vector Table (IVT) and transferring the address contained in the interrupt vector to the program counter. The interrupt vector is transferred from the program data bus into the program counter via a 24-bit wide multiplexer on the input of the program counter.

The Interrupt Vector Table (IVT) and Alternate Interrupt Vector Table (AIVT) are placed near the beginning of program memory (0x000004). The IVT and AIVT are shown in Figure 8-1.

The interrupt controller is responsible for preprocessing the interrupts and processor exceptions prior to them being presented to the processor core. The peripheral interrupts and traps are enabled, prioritized and controlled using centralized Special Function Registers:

- IFS0<15:0>, IFS1<15:0>, IFS2<15:0> All interrupt request flags are maintained in these three registers. The flags are set by their respective peripherals or external signals and they are cleared via software.

- IEC0<15:0>, IEC1<15:0>, IEC2<15:0> All interrupt enable control bits are maintained in these three registers. These control bits are used to individually enable interrupts from the peripherals or external signals.

- IPC0<15:0>... IPC10<7:0> The user-assignable priority level associated with each of these 41 interrupts is held centrally in these eleven registers.

- IPL<3:0>

The current CPU priority level is explicitly stored in the IPL bits. IPL<3> is present in the CORCON register, whereas IPL<2:0> are present in the STATUS register (SR) in the processor core.

- INTCON1<15:0>, INTCON2<15:0> Global interrupt control functions are derived from these two registers. INTCON1 contains the control and status flags for the processor exceptions. The INTCON2 register controls the external interrupt request signal behavior and the use of the alternate vector table.

- **Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

All interrupt sources can be user-assigned to one of 7 priority levels, 1 through 7, via the IPCx registers. Each interrupt source is associated with an interrupt vector, as shown in Table 8-1. Levels 7 and 1 represent the highest and lowest maskable priorities, respectively.

**Note:** Assigning a priority level of '0' to an interrupt source is equivalent to disabling that interrupt.

If the NSTDIS bit (INTCON1<15>) is set, nesting of interrupts is prevented. Thus, if an interrupt is currently being serviced, processing of a new interrupt is prevented even if the new interrupt is of higher priority than the one currently being serviced.

Note: The IPL bits become read-only whenever the NSTDIS bit has been set to '1'.

Certain interrupts have specialized control bits for features like edge or level triggered interrupts, interrupt-on-change, etc. Control of these features remains within the peripheral module which generates the interrupt.

The DISI instruction can be used to disable the processing of interrupts of priorities 6 and lower for a certain number of instructions, during which the DISI bit (INTCON2<14>) remains set.

When an interrupt is serviced, the PC is loaded with the address stored in the vector location in program memory that corresponds to the interrupt. There are 63 different vectors within the IVT (refer to Table 8-1) These vectors are contained in locations 0x000004 through 0x0000FE of program memory (refer to Table 8-1). These locations contain 24-bit addresses. In order to preserve robustness, an address error trap takes place should the PC attempt to fetch any of these words during normal execution. This prevents execution of random data as a result of accidentally decrementing a PC into vector space, accidentally mapping a data space address into vector space or the PC rolling over to 0x000000 after reaching the end of implemented program memory space. Execution of a GOTO instruction to this vector space also generates an address error trap.

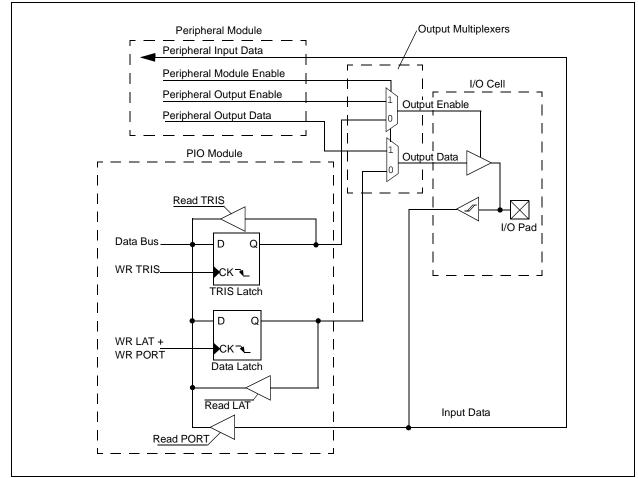

## 12.0 INPUT CAPTURE MODULE

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

This section describes the input capture module and associated operational modes. The features provided by this module are useful in applications requiring frequency (period) and pulse measurement. Figure 12-1 depicts a block diagram of the input capture module. Input capture is useful for such modes as:

- Frequency/Period/Pulse Measurements

- · Additional Sources of External Interrupts

The key operational features of the input capture module are:

- Simple Capture Event mode

- Timer2 and Timer3 mode selection

- · Interrupt on input capture event

These operating modes are determined by setting the appropriate bits in the ICxCON register (where x = 1,2,...,N). The dsPIC DSC devices contain up to 8 capture channels (i.e., the maximum value of N is 8). The dsPIC30F3014 device contains 2 capture channels while the dsPIC30F4013 device contains 4 capture channels.

## 12.1 Simple Capture Event Mode

The simple capture events in the dsPIC30F product family are:

- Capture every falling edge

- Capture every rising edge

- Capture every 4th rising edge

- · Capture every 16th rising edge

- · Capture every rising and falling edge

These simple Input Capture modes are configured by setting the appropriate bits, ICM<2:0> (ICxCON<2:0>).

#### 12.1.1 CAPTURE PRESCALER

There are four input capture prescaler settings specified by bits, ICM<2:0> (ICxCON<2:0>). Whenever the capture channel is turned off, the prescaler counter is cleared. In addition, any Reset clears the prescaler counter.

#### FIGURE 12-1: INPUT CAPTURE MODE BLOCK DIAGRAM

#### 13.2 Simple Output Compare Match Mode

When control bits, OCM<2:0> (OCxCON<2:0>) = 001, 010 or 011, the selected output compare channel is configured for one of three simple Output Compare Match modes:

- Compare forces I/O pin low

- Compare forces I/O pin high

- Compare toggles I/O pin

The OCxR register is used in these modes. The OCxR register is loaded with a value and is compared to the selected incrementing timer count. When a compare occurs, one of these Compare Match modes occurs. If the counter resets to zero before reaching the value in OCxR, the state of the OCx pin remains unchanged.

## 13.3 Dual Output Compare Match Mode

When control bits, OCM<2:0> (OCxCON<2:0>) = 100 or 101, the selected output compare channel is configured for one of two Dual Output Compare modes, which are:

- Single Output Pulse mode

- Continuous Output Pulse mode

#### 13.3.1 SINGLE PULSE MODE

For the user to configure the module for the generation of a single output pulse, the following steps are required (assuming timer is off):

- Determine instruction cycle time, Tcy.

- Calculate desired pulse width value based on TCY.

- Calculate time to Start pulse from timer start value of 0x0000.

- Write pulse-width start and stop times into OCxR and OCxRS Compare registers (x denotes channel 1, 2, ...,N).

- Set Timer Period register to value equal to or greater than value in OCxRS Compare register.

- Set OCM<2:0> = 100.

- Enable timer, TON (TxCON<15>) = 1.

To initiate another single pulse, issue another write to set OCM<2:0> = 100.

### 13.3.2 CONTINUOUS PULSE MODE

For the user to configure the module for the generation of a continuous stream of output pulses, the following steps are required:

- Determine instruction cycle time, Tcy.

- Calculate desired pulse value based on Tcy.

- Calculate timer to Start pulse width from timer start value of 0x0000.

- Write pulse-width Start and Stop times into OCxR and OCxRS (x denotes channel 1, 2, ...,N) Compare registers, respectively.

- Set Timer Period register to value equal to or greater than value in OCxRS Compare register.

- Set OCM<2:0> = 101.

- Enable timer, TON (TxCON<15>) = 1.

### 13.4 Simple PWM Mode

When control bits, OCM<2:0> (OCxCON<2:0>) = 110 or 111, the selected output compare channel is configured for the PWM mode of operation. When configured for the PWM mode of operation, OCxR is the main latch (read-only) and OCxRS is the secondary latch. This enables glitchless PWM transitions.

The user must perform the following steps in order to configure the output compare module for PWM operation:

- 1. Set the PWM period by writing to the appropriate Period register.

- 2. Set the PWM duty cycle by writing to the OCxRS register.

- 3. Configure the output compare module for PWM operation.

- 4. Set the TMRx prescale value and enable the timer, TON (TxCON<15>) = 1.

#### 13.4.1 INPUT PIN FAULT PROTECTION FOR PWM

When control bits, OCM<2:0> (OCxCON<2:0>) = 111, the selected output compare channel is again configured for the PWM mode of operation with the additional feature of input Fault protection. While in this mode, if a logic '0' is detected on the OCFA/B pin, the respective PWM output pin is placed in the high-impedance input state. The OCFLT bit (OCxCON<4>) indicates whether a Fault condition has occurred. This state is maintained until both of the following events have occurred:

- The external Fault condition has been removed.

- The PWM mode has been re-enabled by writing to the appropriate control bits.

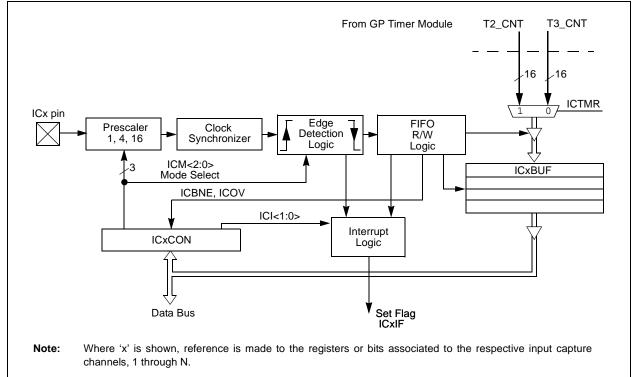

## 18.3 DCI Module Operation

#### 18.3.1 MODULE ENABLE

The DCI module is enabled or disabled by setting/ clearing the DCIEN control bit in the DCICON1 SFR. Clearing the DCIEN control bit has the effect of resetting the module. In particular, all counters associated with CSCK generation, Frame Sync, and the DCI buffer control unit are reset.

The DCI clocks are shut down when the DCIEN bit is cleared.

When enabled, the DCI controls the data direction for the four I/O pins associated with the module. The port, LAT and TRIS register values for these I/O pins are overridden by the DCI module when the DCIEN bit is set.

It is also possible to override the CSCK pin separately when the bit clock generator is enabled. This permits the bit clock generator to operate without enabling the rest of the DCI module.

## 18.3.2 WORD-SIZE SELECTION BITS

The WS<3:0> word-size selection bits in the DCICON2 SFR determine the number of bits in each DCI data word. Essentially, the WS<3:0> bits determine the counting period for a 4-bit counter clocked from the CSCK signal.

Any data length, up to 16 bits, may be selected. The value loaded into the WS<3:0> bits is one less the desired word length. For example, a 16-bit data word size is selected when WS<3:0> = 1111.

| Note: | These WS<3:0> control bits are used only<br>in the Multichannel and I <sup>2</sup> S modes. These |

|-------|---------------------------------------------------------------------------------------------------|

|       | bits have no effect in AC-Link mode since<br>the data slot sizes are fixed by the protocol.       |

#### 18.3.3 FRAME SYNC GENERATOR

The Frame Sync generator (COFSG) is a 4-bit counter that sets the frame length in data words. The Frame Sync generator is incremented each time the word-size counter is reset (refer to **Section 18.3.2** "**Word-Size Selection Bits**"). The period for the Frame Synchronization generator is set by writing the COFSG<3:0> control bits in the DCICON2 SFR. The COFSG period in clock cycles is determined by the following formula:

## EQUATION 18-1: COFSG PERIOD

Frame Length = Word Length • (FSG Value + 1)

Frame lengths, up to 16 data words, may be selected. The frame length in CSCK periods can vary up to a maximum of 256 depending on the word size that is selected.

| Note: | The COFSG control bits have no effect in |

|-------|------------------------------------------|

|       | AC-Link mode since the frame length is   |

|       | set to 256 CSCK periods by the protocol. |

#### 18.3.4 FRAME SYNC MODE CONTROL BITS

The type of Frame Sync signal is selected using the Frame Synchronization mode control bits (COFSM<1:0>) in the DCICON1 SFR. The following operating modes can be selected:

- Multichannel mode

- I<sup>2</sup>S mode

- AC-Link mode (16-bit)

- AC-Link mode (20-bit)

The operation of the COFSM control bits depends on whether the DCI module generates the Frame Sync signal as a master device, or receives the Frame Sync signal as a slave device.

The master device in a DSP/Codec pair is the device that generates the Frame Sync signal. The Frame Sync signal initiates data transfers on the CSDI and CSDO pins and usually has the same frequency as the data sample rate (COFS).

The DCI module is a Frame Sync master if the COFSD control bit is cleared and is a Frame Sync slave if the COFSD control bit is set.

#### 18.3.5 MASTER FRAME SYNC OPERATION

When the DCI module is operating as a Frame Sync master device (COFSD = 0), the COFSM mode bits determine the type of Frame Sync pulse that is generated by the Frame Sync generator logic.

A new COFS signal is generated when the Frame Sync generator resets to '0'.

In the Multichannel mode, the Frame Sync pulse is driven high for the CSCK period to initiate a data transfer. The number of CSCK cycles between successive Frame Sync pulses depends on the word size and Frame Sync generator control bits. A timing diagram for the Frame Sync signal in Multichannel mode is shown in Figure 18-2.

In the AC-Link mode of operation, the Frame Sync signal has a fixed period and duty cycle. The AC-Link Frame Sync signal is high for 16 CSCK cycles and is low for 240 CSCK cycles. A timing diagram with the timing details at the start of an AC-Link frame is shown in Figure 18-3.

In the  $I^2S$  mode, a Frame Sync signal having a 50% duty cycle is generated. The period of the  $I^2S$  Frame Sync signal in CSCK cycles is determined by the word

| IADLE       | 19-2. | ADC    |           |        | <b>LEGISI</b> |        | - • •                              |       |        |       |          |             |                     |       |                     |       |       |                     |

|-------------|-------|--------|-----------|--------|---------------|--------|------------------------------------|-------|--------|-------|----------|-------------|---------------------|-------|---------------------|-------|-------|---------------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14    | Bit 13 | Bit 12        | Bit 11 | Bit 10                             | Bit 9 | Bit 8  | Bit 7 | Bit 6    | Bit 5       | Bit 4               | Bit 3 | Bit 2               | Bit 1 | Bit 0 | Reset State         |

| ADCBUF0     | 0280  | -      | —         | —      | —             |        |                                    |       |        |       | ADC Dat  | ta Buffer 0 |                     |       |                     |       |       | 0000 uuuu uuuu uuuu |

| ADCBUF1     | 0282  | _      | _         | _      | _             |        |                                    |       |        |       | ADC Dat  | ta Buffer 1 |                     |       |                     |       |       | 0000 uuuu uuuu uuuu |

| ADCBUF2     | 0284  | _      |           | —      | —             |        |                                    |       |        |       | ADC Dat  | ta Buffer 2 |                     |       |                     |       |       | 0000 uuuu uuuu uuuu |

| ADCBUF3     | 0286  |        |           | —      | —             |        |                                    |       |        |       | ADC Dat  | ta Buffer 3 |                     |       |                     |       |       | 0000 uuuu uuuu uuuu |

| ADCBUF4     | 0288  |        |           | -      | -             |        |                                    |       |        |       | ADC Dat  | ta Buffer 4 |                     |       |                     |       |       | 0000 uuuu uuuu uuuu |

| ADCBUF5     | 028A  |        |           | -      | -             |        |                                    |       |        |       | ADC Dat  | ta Buffer 5 |                     |       |                     |       |       | 0000 uuuu uuuu uuuu |

| ADCBUF6     | 028C  |        |           | -      | -             |        |                                    |       |        |       | ADC Dat  | ta Buffer 6 |                     |       |                     |       |       | 0000 uuuu uuuu uuuu |

| ADCBUF7     | 028E  |        |           | —      | —             |        |                                    |       |        |       | ADC Dat  | ta Buffer 7 |                     |       |                     |       |       | 0000 uuuu uuuu uuuu |

| ADCBUF8     | 0290  |        |           | —      | —             |        |                                    |       |        |       | ADC Dat  | ta Buffer 8 |                     |       |                     |       |       | 0000 uuuu uuuu uuuu |

| ADCBUF9     | 0292  |        |           | —      | —             |        |                                    |       |        |       | ADC Dat  | ta Buffer 9 |                     |       |                     |       |       | 0000 uuuu uuuu uuuu |

| ADCBUFA     | 0294  | -      | -         | _      | _             |        |                                    |       |        |       | ADC Data | a Buffer 10 | )                   |       |                     |       |       | 0000 uuuu uuuu uuuu |

| ADCBUFB     | 0296  | -      | -         | _      | _             |        |                                    |       |        |       | ADC Dat  | a Buffer 1  | I                   |       |                     |       |       | 0000 uuuu uuuu uuuu |

| ADCBUFC     | 0298  |        |           | —      | —             |        |                                    |       |        |       | ADC Data | a Buffer 12 | 2                   |       |                     |       |       | 0000 uuuu uuuu uuuu |

| ADCBUFD     | 029A  |        |           | —      | —             |        |                                    |       |        |       | ADC Data | a Buffer 13 | 3                   |       |                     |       |       | 0000 uuuu uuuu uuuu |

| ADCBUFE     | 029C  |        | -         | —      | —             |        |                                    |       |        |       | ADC Data | a Buffer 14 | 1                   |       |                     |       |       | 0000 uuuu uuuu uuuu |

| ADCBUFF     | 029E  | -      | -         | _      | _             |        |                                    |       |        |       | ADC Data | a Buffer 1  | 5                   |       |                     |       |       | 0000 uuuu uuuu uuuu |

| ADCON1      | 02A0  | ADON   | -         | ADSIDL | _             | -      | _                                  | FORM  | l<1:0> | S     | SRC<2:0  | >           | _                   | —     | ASAM                | SAMP  | DONE  | 0000 0000 0000 0000 |

| ADCON2      | 02A2  | V      | 'CFG<2:0> | >      | _             | -      | - CSCNA BUFS - SMPI<3:0> BUFM ALTS |       |        |       |          |             |                     |       | 0000 0000 0000 0000 |       |       |                     |

| ADCON3      | 02A4  | -      | -         | _      |               | SA     | SAMC<4:0> ADRC — ADCS<5:0>         |       |        |       |          |             | 0000 0000 0000 0000 |       |                     |       |       |                     |

| ADCHS       | 02A6  |        | -         | _      | CH0NB         |        | CH0SB<3:0> — — — CH0NA CH0SA<3:0>  |       |        |       |          |             | 0000 0000 0000 0000 |       |                     |       |       |                     |

| ADPCFG      | 02A8  | PCFG15 | PCFG14    | PCFG13 | PCFG12        | PCFG11 | PCFG10                             | PCFG9 | PCFG8  | PCFG7 | PCFG6    | PCFG5       | PCFG4               | PCFG3 | PCFG2               | PCFG1 | PCFG0 | 0000 0000 0000 0000 |

| ADCSSL      | 02AA  | CSSL15 | CSSL14    | CSSL13 | CSSL12        | CSSL11 | CSSL10                             | CSSL9 | CSSL8  | CSSL7 | CSSL6    | CSSL5       | CSSL4               | CSSL3 | CSSL2               | CSSL1 | CSSL0 | 0000 0000 0000 0000 |

## TABLE 19-2: A/D CONVERTER REGISTER MAP<sup>(1)</sup>

Legend:

u = uninitialized bit; — = unimplemented bit, read as '0'

Note

1:

Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

## REGISTER 20-2: OSCTUN: FRC OSCILLATOR TUNING REGISTER

|               | 20-2. 0001 |                                 |                 |                   |                 |                 |       |

|---------------|------------|---------------------------------|-----------------|-------------------|-----------------|-----------------|-------|

| U-0           | U-0        | U-0                             | U-0             | U-0               | U-0             | U-0             | U-0   |

| —             | —          | —                               | —               | —                 | —               | —               | _     |

| bit 15        |            |                                 |                 |                   |                 |                 | bit   |

|               |            |                                 |                 |                   |                 |                 |       |

| U-0           | U-0        | U-0                             | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| _             | —          |                                 | —               |                   | TUI             | N<3:0>          |       |

| bit 7         |            |                                 |                 |                   |                 |                 | bit ( |

|               |            |                                 |                 |                   |                 |                 |       |

| Legend:       |            |                                 |                 |                   |                 |                 |       |

| R = Readabl   | e bit      | W = Writable I                  | oit             | U = Unimpler      | mented bit, rea | ad as '0'       |       |

| -n = Value at | POR        | '1' = Bit is set                |                 | '0' = Bit is cle  | ared            | x = Bit is unkr | nown  |

|               |            | minal 7.37 MHz<br>mum frequency | •               |                   |                 |                 |       |

|               | 0001 =     | er frequency, os                | cillator is rur | nning at calibrat | ed frequency    |                 |       |

|               |            |                                 |                 |                   |                 |                 |       |

- 1001 =

- 1000 = Minimum frequency

Table 20-5 shows the Reset conditions for the RCON register. Since the control bits within the RCON register are R/W, the information in the table means that all the bits are negated prior to the action specified in the condition column.

| Condition                              | Program<br>Counter    | TRAPR | IOPUWR | EXTR | SWR | WDTO | IDLE | SLEEP | POR | BOR |

|----------------------------------------|-----------------------|-------|--------|------|-----|------|------|-------|-----|-----|

| Power-on Reset                         | 0x000000              | 0     | 0      | 0    | 0   | 0    | 0    | 0     | 1   | 1   |

| Brown-out Reset                        | 0x000000              | 0     | 0      | 0    | 0   | 0    | 0    | 0     | 0   | 1   |

| MCLR Reset during normal operation     | 0x000000              | 0     | 0      | 1    | 0   | 0    | 0    | 0     | 0   | 0   |

| Software Reset during normal operation | 0x000000              | 0     | 0      | 0    | 1   | 0    | 0    | 0     | 0   | 0   |

| MCLR Reset during Sleep                | 0x000000              | 0     | 0      | 1    | 0   | 0    | 0    | 1     | 0   | 0   |

| MCLR Reset during Idle                 | 0x000000              | 0     | 0      | 1    | 0   | 0    | 1    | 0     | 0   | 0   |

| WDT Time-out Reset                     | 0x000000              | 0     | 0      | 0    | 0   | 1    | 0    | 0     | 0   | 0   |

| WDT Wake-up                            | PC + 2                | 0     | 0      | 0    | 0   | 1    | 0    | 1     | 0   | 0   |

| Interrupt Wake-up from Sleep           | PC + 2 <sup>(1)</sup> | 0     | 0      | 0    | 0   | 0    | 0    | 1     | 0   | 0   |

| Clock Failure Trap                     | 0x000004              | 0     | 0      | 0    | 0   | 0    | 0    | 0     | 0   | 0   |

| Trap Reset                             | 0x000000              | 1     | 0      | 0    | 0   | 0    | 0    | 0     | 0   | 0   |

| Illegal Operation Trap                 | 0x000000              | 0     | 1      | 0    | 0   | 0    | 0    | 0     | 0   | 0   |

| TABLE 20-5: | INITIALIZATION CONDITION FOR RCON REGISTER: CASE 1 |

|-------------|----------------------------------------------------|

|-------------|----------------------------------------------------|

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0'

**Note 1:** When the wake-up is due to an enabled interrupt, the PC is loaded with the corresponding interrupt vector.

Table 20-6 shows a second example of the bit conditions for the RCON register. In this case, it is not assumed the user has set/cleared specific bits prior to action specified in the condition column.

| Condition                              | Program<br>Counter    | TRAPR | IOPUWR | EXTR | SWR | WDTO | IDLE | SLEEP | POR | BOR |

|----------------------------------------|-----------------------|-------|--------|------|-----|------|------|-------|-----|-----|

| Power-on Reset                         | 0x000000              | 0     | 0      | 0    | 0   | 0    | 0    | 0     | 1   | 1   |

| Brown-out Reset                        | 0x000000              | u     | u      | u    | u   | u    | u    | u     | 0   | 1   |

| MCLR Reset during normal operation     | 0x000000              | u     | u      | 1    | 0   | 0    | 0    | 0     | u   | u   |

| Software Reset during normal operation | 0x000000              | u     | u      | 0    | 1   | 0    | 0    | 0     | u   | u   |

| MCLR Reset during Sleep                | 0x000000              | u     | u      | 1    | u   | 0    | 0    | 1     | u   | u   |

| MCLR Reset during Idle                 | 0x000000              | u     | u      | 1    | u   | 0    | 1    | 0     | u   | u   |

| WDT Time-out Reset                     | 0x000000              | u     | u      | 0    | 0   | 1    | 0    | 0     | u   | u   |

| WDT Wake-up                            | PC + 2                | u     | u      | u    | u   | 1    | u    | 1     | u   | u   |

| Interrupt Wake-up from Sleep           | PC + 2 <sup>(1)</sup> | u     | u      | u    | u   | u    | u    | 1     | u   | u   |

| Clock Failure Trap                     | 0x000004              | u     | u      | u    | u   | u    | u    | u     | u   | u   |

| Trap Reset                             | 0x000000              | 1     | u      | u    | u   | u    | u    | u     | u   | u   |

| Illegal Operation Reset                | 0x000000              | u     | 1      | u    | u   | u    | u    | u     | u   | u   |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0'

**Note 1:** When the wake-up is due to an enabled interrupt, the PC is loaded with the corresponding interrupt vector.

## 22.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit<sup>™</sup> 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

## 22.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Mouse over variable inspection

- Drag and drop variables from source to watch windows

- Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

| DC CHARACTERISTICS |        |                                          |         | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |         |       |                                                                                                                                |  |  |  |

|--------------------|--------|------------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Param<br>No.       | Symbol | Characteristic                           | Min     | Тур <sup>(1)</sup>                                                                                                                                                                                                                                                                      | Max     | Units | Conditions                                                                                                                     |  |  |  |

|                    | VIL    | Input Low Voltage <sup>(2)</sup>         |         |                                                                                                                                                                                                                                                                                         |         |       |                                                                                                                                |  |  |  |

| DI10               |        | I/O Pins:                                |         |                                                                                                                                                                                                                                                                                         |         |       |                                                                                                                                |  |  |  |

|                    |        | with Schmitt Trigger Buffer              | Vss     | —                                                                                                                                                                                                                                                                                       | 0.2 Vdd | V     |                                                                                                                                |  |  |  |

| DI15               |        | MCLR                                     | Vss     | —                                                                                                                                                                                                                                                                                       | 0.2 Vdd | V     |                                                                                                                                |  |  |  |

| DI16               |        | OSC1 (in XT, HS and LP modes)            | Vss     | —                                                                                                                                                                                                                                                                                       | 0.2 Vdd | V     |                                                                                                                                |  |  |  |

| DI17               |        | OSC1 (in RC mode) <sup>(3)</sup>         | Vss     | _                                                                                                                                                                                                                                                                                       | 0.3 Vdd | V     |                                                                                                                                |  |  |  |

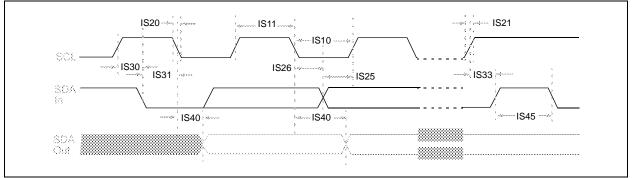

| DI18               |        | SDA, SCL                                 | Vss     | —                                                                                                                                                                                                                                                                                       | 0.3 Vdd | V     | SM bus disabled                                                                                                                |  |  |  |

| DI19               |        | SDA, SCL                                 | Vss     | _                                                                                                                                                                                                                                                                                       | 0.8     | V     | SM bus enabled                                                                                                                 |  |  |  |

|                    | Viн    | Input High Voltage <sup>(2)</sup>        |         |                                                                                                                                                                                                                                                                                         |         |       |                                                                                                                                |  |  |  |

| DI20               |        | I/O Pins:                                |         |                                                                                                                                                                                                                                                                                         |         |       |                                                                                                                                |  |  |  |

|                    |        | with Schmitt Trigger Buffer              | 0.8 Vdd | _                                                                                                                                                                                                                                                                                       | Vdd     | V     |                                                                                                                                |  |  |  |

| DI25               |        | MCLR                                     | 0.8 Vdd |                                                                                                                                                                                                                                                                                         | Vdd     | V     |                                                                                                                                |  |  |  |

| DI26               |        | OSC1 (in XT, HS and LP modes)            | 0.7 Vdd | _                                                                                                                                                                                                                                                                                       | Vdd     | V     |                                                                                                                                |  |  |  |

| DI27               |        | OSC1 (in RC mode) <sup>(3)</sup>         | 0.9 Vdd |                                                                                                                                                                                                                                                                                         | Vdd     | V     |                                                                                                                                |  |  |  |

| DI28               |        | SDA, SCL                                 | 0.7 Vdd | _                                                                                                                                                                                                                                                                                       | Vdd     | V     | SM bus disabled                                                                                                                |  |  |  |

| DI29               |        | SDA, SCL                                 | 2.1     |                                                                                                                                                                                                                                                                                         | Vdd     | V     | SM bus enabled                                                                                                                 |  |  |  |

|                    | ICNPU  | CNxx Pull-up Current <sup>(2)</sup>      |         |                                                                                                                                                                                                                                                                                         |         |       |                                                                                                                                |  |  |  |

| DI30               |        |                                          | 50      | 250                                                                                                                                                                                                                                                                                     | 400     | μΑ    | VDD = 5V, VPIN = VSS                                                                                                           |  |  |  |

|                    | lı∟    | Input Leakage Current <sup>(2,4,5)</sup> |         |                                                                                                                                                                                                                                                                                         |         |       |                                                                                                                                |  |  |  |

| DI50               |        | I/O Ports                                | —       | 0.01                                                                                                                                                                                                                                                                                    | ±1      | μΑ    | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &P{\sf in} \mbox{ at high-impedance } \end{split}$ |  |  |  |

| DI51               |        | Analog Input Pins                        | —       | 0.50                                                                                                                                                                                                                                                                                    | —       | μΑ    | $\label{eq:VSS} \begin{split} \text{VSS} &\leq \text{VPIN} \leq \text{VDD}, \\ \text{Pin at high-impedance} \end{split}$       |  |  |  |

| DI55               |        | MCLR                                     | —       | 0.05                                                                                                                                                                                                                                                                                    | ±5      | μΑ    | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                                       |  |  |  |

| DI56               |        | OSC1                                     | —       | 0.05                                                                                                                                                                                                                                                                                    | ±5      | μΑ    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP Osc mode                                                                             |  |  |  |

#### TABLE 23-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: These parameters are characterized but not tested in manufacturing.

**3:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the dsPIC30F device be driven with an external clock while in RC mode.

4: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

5: Negative current is defined as current sourced by the pin.

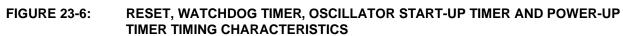

## TABLE 23-20: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER AND BROWN-OUT RESET TIMING REQUIREMENTS

| AC CHARACTERISTICS |                         |                                                             |                                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                   |                |                                                  |  |  |  |

|--------------------|-------------------------|-------------------------------------------------------------|---------------------------------------------|-------------------------------------------------------|-------------------|----------------|--------------------------------------------------|--|--|--|

| Param<br>No.       | Symbol                  | Characteristic <sup>(1)</sup>                               | Min Typ <sup>(2)</sup> Max Units Conditions |                                                       |                   |                |                                                  |  |  |  |

| SY10               | TmcL                    | MCLR Pulse Width (low)                                      | 2                                           | —                                                     | _                 | μS             | -40°C to +85°C                                   |  |  |  |

| SY11               | TPWRT                   | Power-up Timer Period                                       | 2<br>10<br>43                               | 4<br>16<br>64                                         | 8<br>32<br>128    | ms             | -40°C to +85°C,<br>VDD = 5V<br>User programmable |  |  |  |

| SY12               | TPOR                    | Power-on Reset Delay                                        | 3                                           | 10                                                    | 30                | μS             | -40°C to +85°C                                   |  |  |  |

| SY13               | Tioz                    | I/O High-Impedance from MCLR<br>Low or Watchdog Timer Reset |                                             | 0.8                                                   | 1.0               | μS             |                                                  |  |  |  |

| SY20               | Twdt1<br>Twdt2<br>Twdt3 | Watchdog Timer Time-out Period<br>(no prescaler)            | 1.1<br>1.2<br>1.3                           | 2.0<br>2.0<br>2.0                                     | 6.6<br>5.0<br>4.0 | ms<br>ms<br>ms | VDD = 2.5V<br>VDD = 3.3V, ±10%<br>VDD = 5V, ±10% |  |  |  |

| SY25               | TBOR                    | Brown-out Reset Pulse Width <sup>(3)</sup>                  | 100                                         | —                                                     | _                 | μS             | $VDD \leq VBOR (D034)$                           |  |  |  |

| SY30               | Tost                    | Oscillator Start-up Timer Period                            | _                                           | 1024 Tosc                                             | —                 | —              | Tosc = OSC1 period                               |  |  |  |

| SY35               | TFSCM                   | Fail-Safe Clock Monitor Delay                               | —                                           | 500                                                   | 900               | μS             | -40°C to +85°C                                   |  |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated.

3: Refer to Figure 23-2 and Table 23-11 for BOR.

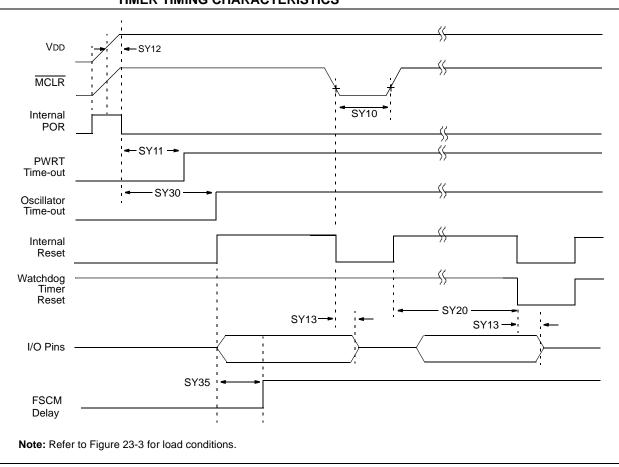

### FIGURE 23-7: BAND GAP START-UP TIME CHARACTERISTICS

#### TABLE 23-21: BAND GAP START-UP TIME REQUIREMENTS

| AC CHARACTERISTICS |        |                               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                    |     |       |                                                                                                                                                                     |

|--------------------|--------|-------------------------------|-------------------------------------------------------|--------------------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup> | Min                                                   | Тур <sup>(2)</sup> | Max | Units | Conditions                                                                                                                                                          |

| SY40               | Tbgap  | Band Gap Start-up Time        |                                                       | 40                 | 65  | μS    | Defined as the time between the<br>instant that the band gap is enabled<br>and the moment that the band gap<br>reference voltage is stable<br>(RCON<13> status bit) |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated.

#### TABLE 23-33: SPI MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                                  | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                    |     |       |                       |  |

|--------------------|-----------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|-----------------------|--|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                    | Min                                                                                                                                                                                                                                                                                 | Тур <sup>(2)</sup> | Max | Units | Conditions            |  |

| SP70               | TscL                  | SCKx Input Low Time                                              | 30                                                                                                                                                                                                                                                                                  |                    | _   | ns    |                       |  |

| SP71               | TscH                  | SCKx Input High Time                                             | 30                                                                                                                                                                                                                                                                                  |                    | _   | ns    |                       |  |

| SP72               | TscF                  | SCKx Input Fall Time <sup>(3)</sup>                              | —                                                                                                                                                                                                                                                                                   |                    | 25  | ns    |                       |  |

| SP73               | TscR                  | SCKx Input Rise Time <sup>(3)</sup>                              | —                                                                                                                                                                                                                                                                                   |                    | 25  | ns    |                       |  |

| SP30               | TdoF                  | SDOx Data Output Fall Time <sup>(3)</sup>                        | _                                                                                                                                                                                                                                                                                   | Ι                  | —   | ns    | See parameter<br>DO32 |  |

| SP31               | TdoR                  | SDOx Data Output Rise Time <sup>(3)</sup>                        | —                                                                                                                                                                                                                                                                                   | _                  | _   | ns    | See parameter<br>DO31 |  |

| SP35               | TscH2do,<br>TscL2doV  | SDOx Data Output Valid after<br>SCKx Edge                        | —                                                                                                                                                                                                                                                                                   | —                  | 30  | ns    |                       |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                       | 20                                                                                                                                                                                                                                                                                  | _                  | _   | ns    |                       |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge                     | 20                                                                                                                                                                                                                                                                                  | -                  | —   | ns    |                       |  |

| SP50               | TssL2scH,<br>TssL2scL | SSx↓ to SCKx↓ or SCKx↑ Input                                     | 120                                                                                                                                                                                                                                                                                 | _                  | _   | ns    |                       |  |

| SP51               | TssH2doZ              | SSx <sup>↑</sup> to SDOx Output<br>High-Impedance <sup>(4)</sup> | 10                                                                                                                                                                                                                                                                                  | —                  | 50  | ns    |                       |  |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx <sup>↑</sup> after SCKx Edge                                 | 1.5 Tcy + 40                                                                                                                                                                                                                                                                        | —                  | _   | ns    |                       |  |

| SP60               | TssL2doV              | SDOx Data Output Valid after<br>SCKx Edge                        | —                                                                                                                                                                                                                                                                                   | —                  | 50  | ns    |                       |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 100 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPI pins.

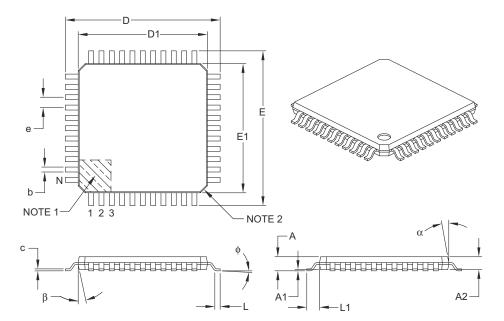

### 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units        | MILLIMETERS |      |      |  |

|--------------------------|--------------|-------------|------|------|--|

| Dimer                    | nsion Limits | MIN         | MAX  |      |  |

| Number of Leads          | Ν            | 44          |      |      |  |

| Lead Pitch               | е            | 0.80 BSC    |      |      |  |

| Overall Height           | А            | - – 1.20    |      |      |  |

| Molded Package Thickness | A2           | 0.95        | 1.00 | 1.05 |  |

| Standoff                 | A1           | 0.05        | -    | 0.15 |  |

| Foot Length              | L            | 0.45        | 0.60 | 0.75 |  |

| Footprint                | L1           | 1.00 REF    |      |      |  |

| Foot Angle               | φ            | 0° 3.5° 7°  |      |      |  |

| Overall Width            | E            | 12.00 BSC   |      |      |  |

| Overall Length           | D            | 12.00 BSC   |      |      |  |

| Molded Package Width     | E1           | 10.00 BSC   |      |      |  |

| Molded Package Length    | D1           | 10.00 BSC   |      |      |  |

| Lead Thickness           | С            | 0.09        | -    | 0.20 |  |

| Lead Width               | b            | 0.30        | 0.37 | 0.45 |  |

| Mold Draft Angle Top     | α            | 11° 12° 13° |      |      |  |

| Mold Draft Angle Bottom  | β            | 11° 12° 13° |      |      |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B

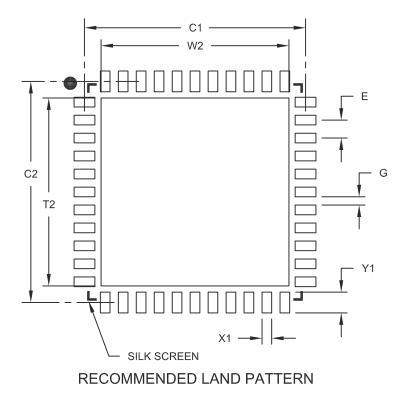

### 44-Lead Plastic Quad Flat, No Lead Package (ML) – 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units |          | MILLIMETERS |      |  |

|----------------------------|-------|----------|-------------|------|--|

| Dimension Limits           |       | MIN      | NOM         | MAX  |  |

| Contact Pitch              | E     | 0.65 BSC |             |      |  |

| Optional Center Pad Width  | W2    |          |             | 6.80 |  |

| Optional Center Pad Length | T2    |          |             | 6.80 |  |

| Contact Pad Spacing        | C1    |          | 8.00        |      |  |

| Contact Pad Spacing        | C2    |          | 8.00        |      |  |

| Contact Pad Width (X44)    | X1    |          |             | 0.35 |  |

| Contact Pad Length (X44)   | Y1    |          |             | 0.80 |  |

| Distance Between Pads      | G     | 0.25     |             |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103A

| Sleep                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power-up Timer                                                                                                                                                                                                             |

| Timing Requirements187                                                                                                                                                                                                     |

| Program Address Space25                                                                                                                                                                                                    |

| Construction26                                                                                                                                                                                                             |

| Data Access from Program Memory                                                                                                                                                                                            |

| Using Program Space Visibility                                                                                                                                                                                             |

| Data Access From Program Memory                                                                                                                                                                                            |

| Using Table Instructions27                                                                                                                                                                                                 |

| Data Access from, Address Generation26                                                                                                                                                                                     |

| Data Space Window into Operation                                                                                                                                                                                           |

| Data Table Access (Isw)27                                                                                                                                                                                                  |

| Data Table Access (MSB)28                                                                                                                                                                                                  |

| dsPIC30F3014 Memory Map25                                                                                                                                                                                                  |

| dsPIC30F4013 Memory Map25                                                                                                                                                                                                  |

| Table Instructions                                                                                                                                                                                                         |

|                                                                                                                                                                                                                            |

| TBLRDH                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                            |

| TBLRDH27                                                                                                                                                                                                                   |

| TBLRDH                                                                                                                                                                                                                     |

| TBLRDH27TBLRDL27TBLWTH27TBLWTL27Program and EEPROM Characteristics180Program Counter16Programmable141Programmer's Model16Diagram17                                                                                         |

| TBLRDH.27TBLRDL27TBLWTH27TBLWTL27Program and EEPROM Characteristics180Program Counter.16Programmable.141Programmer's Model.16Diagram17Programming Operations45                                                             |

| TBLRDH.27TBLRDL27TBLWTH27TBLWTL27Program and EEPROM Characteristics180Program Counter.16Programmable141Programmer's Model16Diagram17Programming Operations45Algorithm for Program Flash45                                  |

| TBLRDH.27TBLRDL27TBLWTH27TBLWTL27Program and EEPROM Characteristics180Program Counter.16Programmable141Programmer's Model16Diagram17Programming Operations45Algorithm for Program Flash45Erasing a Row of Program Memory45 |

## R

| Reader Response                  | 226 |

|----------------------------------|-----|

| Registers                        |     |

| OSCCON (Oscillator Control)      | 147 |

| OSCTUN (Oscillator Tuning)       | 149 |

| Reset                            |     |

| BOR, Programmable                | 153 |

| Brown-out Reset (BOR)            | 141 |

| Oscillator Start-up Timer (OST)  | 141 |

| POR                              |     |

| Operating without FSCM and PWRT  | 153 |

| With Long Crystal Start-up Time  | 153 |

| POR (Power-on Reset)             |     |

| Power-on Reset (POR)             | 141 |

| Power-up Timer (PWRT)            |     |

| Reset Sequence                   | 61  |

| Reset Sources                    | 61  |

| Reset Sources                    |     |

| Brown-out Reset (BOR)            | 61  |

| Illegal Instruction Trap         | 61  |

| Trap Lockout                     | 61  |

| Uninitialized W Register Trap    | 61  |

| Watchdog Time-out                | 61  |

| Reset Timing Requirements        | 187 |

| Revision History                 |     |

| Run-Time Self-Programming (RTSP) |     |

| S                                |     |

| Simple Capture Event Mode                |     |

|------------------------------------------|-----|

| Buffer Operation                         |     |

| Hall Sensor Mode                         |     |

| Prescaler                                | 81  |

| Timer2 and Timer3 Selection Mode         |     |

| Simple OCx/PWM Mode Timing Requirements. | 191 |

| Simple Output Compare Match Mode 86                              |

|------------------------------------------------------------------|

| Simple PWM Mode 86                                               |

| Input Pin Fault Protection 86                                    |

| Period 87                                                        |

| Software Simulator (MPLAB SIM) 169                               |

| Software Stack Pointer, Frame Pointer 16                         |

| CALL Stack Frame 33                                              |

| SPI Module                                                       |

| Framed SPI Support 100                                           |

| Operating Function Description                                   |

| Operation During CPU Idle Mode 101                               |

| Operation During CPU Sleep Mode                                  |

| SDOx Disable 99                                                  |

| Slave Select Synchronization 101                                 |

| SPI1 Register Map 102                                            |

| Timing Requirements                                              |

| Master Mode (CKE = 0) 196                                        |

| Master Mode (CKE = 1) 197                                        |

| Slave Mode (CKE = 0) 198                                         |

| Slave Mode (CKE = 1) 200                                         |

| Word and Byte Communication 99                                   |

| Status Bits, Their Significance and the Initialization Condition |

| for RCON Register, Case 1 154                                    |

| Status Bits, Their Significance and the Initialization Condition |

| for RCON Register, Case 2 154                                    |

| STATUS Register 16                                               |

| Symbols Used in Opcode Descriptions 160                          |

| System Integration 141                                           |

| Register Map 158                                                 |

|                                                                  |

## Т

| Table Instruction Operation Summary    | 43  |

|----------------------------------------|-----|

| Temperature and Voltage Specifications |     |

| AC                                     | 181 |

| DC                                     | 172 |

| Timer1 Module                          | 67  |

| 16-Bit Asynchronous Counter Mode       | 67  |

| 16-Bit Synchronous Counter Mode        | 67  |

| 16-Bit Timer Mode                      | 67  |

| Gate Operation                         | 68  |

| Interrupt                              | 68  |

| Operation During Sleep Mode            | 68  |

| Prescaler                              | 68  |

| Real-Time Clock                        |     |

| Interrupts                             | 68  |

| Oscillator Operation                   | 68  |

| Register Map                           |     |

| Timer2 and Timer3 Selection Mode       | 85  |

| Timer2/3 Module                        | 71  |

| 16-Bit Timer Mode                      |     |

| 32-Bit Synchronous Counter Mode        | 71  |

| 32-Bit Timer Mode                      | 71  |

| ADC Event Trigger                      | 74  |

| Gate Operation                         | 74  |

| Interrupt                              | 74  |

| Operation During Sleep Mode            | 74  |

| Register Map                           |     |

| Timer Prescaler                        |     |

| Timer4/5 Module                        |     |

| Register Map                           |     |

| Timing Diagrams                        |     |

| A/D Conversion                         |     |

| Low-Speed (ASAM = 0, SSRC = 000)       | 208 |

| Band Gap Start-up Time                 |     |

| Brown-out Reset Characteristics        |     |

| CAN Bit                                | -   |