Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 30 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 30                                                                            |

| Program Memory Size        | 24KB (8K x 24)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 1K x 8                                                                        |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 13x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8x8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f3014-30i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **CMOS Technology:**

- Low-Power, High-Speed Flash Technology

- Wide Operating Voltage Range (2.5V to 5.5V)

- Industrial and Extended Temperature Ranges

- Low-Power Consumption

## dsPIC30F3014/4013 Controller Family

|              |       | Program Memory |              | SRAM  | EEPROM | Timer  | Input | Output           | Codec                   | A/D 12-Bit | RТ | Ы  | Ψ   | z  |

|--------------|-------|----------------|--------------|-------|--------|--------|-------|------------------|-------------------------|------------|----|----|-----|----|

| Device       | Pins  | Bytes          | Instructions | Bytes | Bytes  | 16-Bit | Cap   | Comp/<br>Std PWM | Interface               | 200 Ksps   | NA | SF | l²C | CA |

| dsPIC30F3014 | 40/44 | 24K            | 8K           | 2048  | 1024   | 3      | 2     | 2                | _                       | 13 ch      | 2  | 1  | 1   | 0  |

| dsPIC30F4013 | 40/44 | 48K            | 16K          | 2048  | 1024   | 5      | 4     | 4                | AC'97, I <sup>2</sup> S | 13 ch      | 2  | 1  | 1   | 1  |

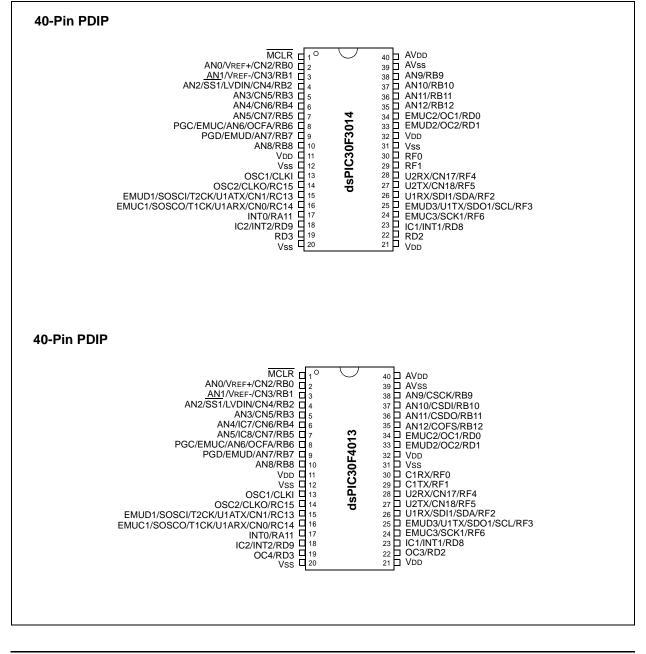

## **Pin Diagrams**

NOTES:

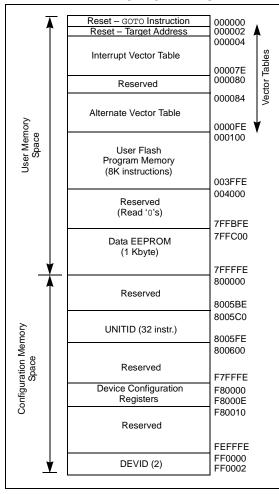

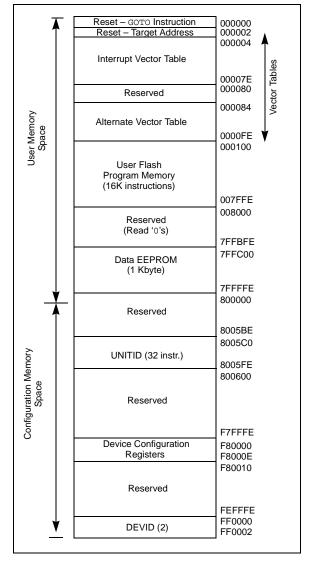

## 3.0 MEMORY ORGANIZATION

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

## 3.1 Program Address Space

The program address space is 4M instruction words. It is addressable by a 24-bit value from either the 23-bit PC, table instruction Effective Address (EA) or data space EA, when program space is mapped into data space as defined by Table 3-1. Note that the program space address is incremented by two between successive program words in order to provide compatibility with data space addressing.

#### FIGURE 3-1: dsPIC30F3014 PROGRAM SPACE MEMORY MAP

User program space access is restricted to the lower 4M instruction word address range (0x000000 to 0x7FFFFE) for all accesses other than TBLRD/TBLWT, which use TBLPAG<7> to determine user or configuration space access. In Table 3-1, bit 23 allows access to the Device ID, the User ID and the Configuration bits; otherwise, bit 23 is always clear.

## FIGURE 3-2:

#### dsPIC30F4013 PROGRAM SPACE MEMORY MAP

#### CORE REGISTER MAP<sup>(1)</sup> (CONTINUED) **TABLE 3-3:**

| IADEL J- | J. U              |        |        |               | (00)     |        | -0,    |        |         |       |       |                     |                     |       | -     | -     |       |                     |

|----------|-------------------|--------|--------|---------------|----------|--------|--------|--------|---------|-------|-------|---------------------|---------------------|-------|-------|-------|-------|---------------------|

| SFR Name | Address<br>(Home) | Bit 15 | Bit 14 | Bit 13        | Bit 12   | Bit 11 | Bit 10 | Bit 9  | Bit 8   | Bit 7 | Bit 6 | Bit 5               | Bit 4               | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset State         |

| CORCON   | 0044              | —      |        | —             | US       | EDT    | DL2    | DL1    | DL0     | SATA  | SATB  | SATDW               | ACCSAT              | IPL3  | PSV   | RND   | IF    | 0000 0000 0010 0000 |

| MODCON   | 0046              | XMODEN | YMODEN | _             | _        |        | BWN    | 1<3:0> |         |       | YWI   | M<3:0>              |                     |       | XWM<  | :3:0> |       | 0000 0000 0000 0000 |

| XMODSRT  | 0048              |        |        |               |          |        |        | X      | 6<15:1> |       |       |                     |                     |       |       |       | 0     | uuuu uuuu uuuu uuu0 |

| XMODEND  | 004A              |        |        |               |          |        |        | XI     | <15:1>  |       |       |                     |                     |       |       |       | 1     | uuuu uuuu uuul      |

| YMODSRT  | 004C              |        |        |               |          |        |        | YS     | S<15:1> |       |       |                     |                     |       |       |       | 0     | uuuu uuuu uuuu uuu0 |

| YMODEND  | 004E              |        |        |               |          |        |        | YE     | <15:1>  |       |       |                     |                     |       |       |       | 1     | uuuu uuuu uuul      |

| XBREV    | 0050              | BREN   |        |               | XB<14:0> |        |        |        |         |       |       |                     | uuuu uuuu uuuu uuuu |       |       |       |       |                     |

| DISICNT  | 0052              | _      | _      | DISICNT<13:0> |          |        |        |        |         |       |       | 0000 0000 0000 0000 |                     |       |       |       |       |                     |

Legend:

u = uninitialized bit; — = unimplemented bit, read as '0'

Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

## 8.1 Interrupt Priority

The user-assignable interrupt priority (IP<2:0>) bits for each individual interrupt source are located in the 3 LSbs of each nibble within the IPCx register(s). Bit 3 of each nibble is not used and is read as a '0'. These bits define the priority level assigned to a particular interrupt by the user.

| Note: | The user-assignable priority levels start at |

|-------|----------------------------------------------|

|       | 0 as the lowest priority and Level 7 as the  |

|       | highest priority.                            |

Since more than one interrupt request source may be assigned to a specific user-assigned priority level, a means is provided to assign priority within a given level. This method is called "Natural Order Priority" and is final.

Natural Order Priority is determined by the position of an interrupt in the vector table, and only affects interrupt operation when multiple interrupts with the same user-assigned priority become pending at the same time.

Table 8-1 and Table 8-2 list the interrupt numbers, corresponding interrupt sources and associated vector numbers for the dsPIC30F3014 and dsPIC30F4013 devices, respectively.

- **Note 1:** The natural order priority scheme has 0 as the highest priority and 53 as the lowest priority.

- **2:** The natural order priority number is the same as the INT number.

The ability for the user to assign every interrupt to one of seven priority levels means that the user can assign a very high overall priority level to an interrupt with a low natural order priority. For example, the PLVD (Programmable Low-Voltage Detect) can be given a priority of 7. The INT0 (External Interrupt 0) may be assigned to priority Level 1, thus giving it a very low effective priority.

#### TABLE 8-1: dsPIC30F3014 INTERRUPT VECTOR TABLE

| INT<br>Number | Vector<br>Number | Interrupt Source                                     |

|---------------|------------------|------------------------------------------------------|

|               | Highest          | Natural Order Priority                               |

| 0             | 8                | INT0 – External Interrupt 0                          |

| 1             | 9                | IC1 – Input Capture 1                                |

| 2             | 10               | OC1 – Output Compare 1                               |

| 3             | 11               | T1 – Timer1                                          |

| 4             | 12               | IC2 – Input Capture 2                                |

| 5             | 13               | OC2 – Output Compare 2                               |

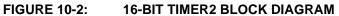

| 6             | 14               | T2 – Timer2                                          |

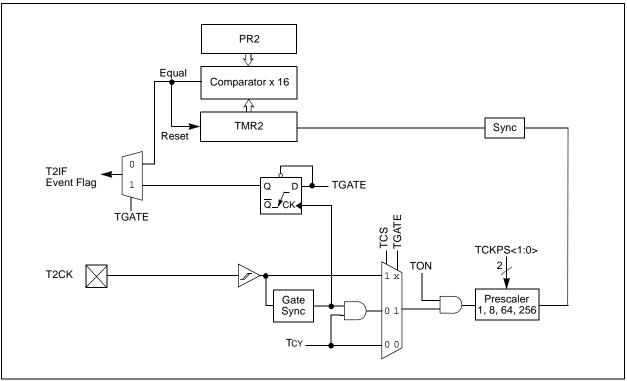

| 7             | 15               | T3 – Timer3                                          |

| 8             | 16               | SPI1                                                 |

| 9             | 17               | U1RX – UART1 Receiver                                |

| 10            | 18               | U1TX – UART1 Transmitter                             |

| 11            | 19               | ADC – ADC Convert Done                               |

| 12            | 20               | NVM – NVM Write Complete                             |

| 13            | 21               | SI2C – I <sup>2</sup> C <sup>™</sup> Slave Interrupt |

| 14            | 22               | MI2C – I <sup>2</sup> C Master Interrupt             |

| 15            | 23               | Input Change Interrupt                               |

| 16            | 24               | INT1 – External Interrupt 1                          |

| 17-22         | 25-30            | Reserved                                             |

| 23            | 31               | INT2 – External Interrupt 2                          |

| 24            | 32               | U2RX – UART2 Receiver                                |

| 25            | 33               | U2TX – UART2 Transmitter                             |

| 26            | 34               | Reserved                                             |

| 27            | 35               | C1 – Combined IRQ for CAN1                           |

| 28-41         | 36-49            | Reserved                                             |

| 42            | 50               | LVD – Low-Voltage Detect                             |

| 43-53         | 51-61            | Reserved                                             |

|               | Lowest           | Natural Order Priority                               |

## 8.5 Alternate Vector Table

In program memory, the Interrupt Vector Table (IVT) is followed by the Alternate Interrupt Vector Table (AIVT), as shown in Figure 8-1. Access to the alternate vector table is provided by the ALTIVT bit in the INTCON2 register. If the ALTIVT bit is set, all interrupt and exception processes use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors. The AIVT supports emulation and debugging efforts by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time.

If the AIVT is not required, the program memory allocated to the AIVT may be used for other purposes. AIVT is not a protected section and may be freely programmed by the user.

## 8.6 Fast Context Saving

A context saving option is available using shadow registers. Shadow registers are provided for the DC, N, OV, Z and C bits in SR, and the registers, W0 through W3. The shadows are only one level deep. The shadow registers are accessible using the PUSH.S and POP.S instructions only.

When the processor vectors to an interrupt, the PUSH.S instruction can be used to store the current value of the aforementioned registers into their respective shadow registers.

If an ISR of a certain priority uses the PUSH.S and POP.S instructions for fast context saving, then a higher priority ISR should not include the same instructions. Users must save the key registers in software during a lower priority interrupt if the higher priority ISR uses fast context saving.

## 8.7 External Interrupt Requests

The interrupt controller supports up to five external interrupt request signals, INTO-INT4. These inputs are edge sensitive; they require a low-to-high or a high-to-low transition to generate an interrupt request. The INTCON2 register has three bits, INTOEP-INT2EP, that select the polarity of the edge detection circuitry.

## 8.8 Wake-up from Sleep and Idle

The interrupt controller may be used to wake-up the processor from either Sleep or Idle mode, if Sleep or Idle mode is active when the interrupt is generated.

If an enabled interrupt request of sufficient priority is received by the interrupt controller, then the standard interrupt request is presented to the processor. At the same time, the processor wakes up from Sleep or Idle and begins execution of the Interrupt Service Routine (ISR) needed to process the interrupt request.

## 14.7 Interrupts

The  $I^2C$  module generates two interrupt flags, MI2CIF ( $I^2C$  Master Interrupt Flag) and SI2CIF ( $I^2C$  Slave Interrupt Flag). The MI2CIF interrupt flag is activated on completion of a master message event. The SI2CIF interrupt flag is activated on detection of a message directed to the slave.

## 14.8 Slope Control

The I<sup>2</sup>C standard requires slope control on the SDA and SCL signals for Fast mode (400 kHz). The control bit, DISSLW, enables the user to disable slew rate control if desired. It is necessary to disable the slew rate control for 1 MHz mode.

## 14.9 IPMI Support

The control bit, IPMIEN, enables the module to support Intelligent Peripheral Management Interface (IPMI). When this bit is set, the module accepts and acts upon all addresses.

## 14.10 General Call Address Support

The general call address can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledgement.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all '0's with R\_W = 0.

The general call address is recognized when the General Call Enable (GCEN) bit is set (I2CCON<7> = 1). Following a Start bit detection, 8 bits are shifted into I2CRSR and the address is compared with I2CADD, and is also compared with the general call address which is fixed in hardware.

If a general call address match occurs, the I2CRSR is transferred to the I2CRCV after the eighth clock, the RBF flag is set and on the falling edge of the ninth bit (ACK bit), the Master Event Interrupt Flag (MI2CIF) is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the I2CRCV to determine if the address was device-specific or a general call address.

## 14.11 I<sup>2</sup>C Master Support

As a master device, six operations are supported:

- Assert a Start condition on SDA and SCL.

- Assert a Restart condition on SDA and SCL.

- Write to the I2CTRN register initiating transmission of data/address.

- Generate a Stop condition on SDA and SCL.

- Configure the I<sup>2</sup>C port to receive data.

- Generate an ACK condition at the end of a received byte of data.

## 14.12 I<sup>2</sup>C Master Operation

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus is not released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the data direction bit. In this case, the data direction bit ( $R_W$ ) is logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an ACK bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the data direction bit. In this case, the data direction bit (R\_W) is logic '1'. Thus, the first byte transmitted is a 7-bit slave address, followed by a '1' to indicate the receive bit. Serial data is received via SDA while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an ACK bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

## 14.12.1 I<sup>2</sup>C MASTER TRANSMISSION

Transmission of a data byte, a 7-bit address or the second half of a 10-bit address, is accomplished by simply writing a value to I2CTRN register. The user should only write to I2CTRN when the module is in a Wait state. This action sets the Buffer Full Flag (TBF) and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/ data is shifted out onto the SDA pin after the falling edge of SCL is asserted. The Transmit Status Flag, TRSTAT (I2CSTAT<14>), indicates that a master transmit is in progress.

## 20.0 SYSTEM INTEGRATION

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

There are several features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving operating modes and offer code protection:

- Oscillator Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Programmable Brown-out Reset (BOR)

- Watchdog Timer (WDT)

- Low-Voltage Detect

- Power-Saving modes (Sleep and Idle)

- Code Protection

- Unit ID Locations

- In-Circuit Serial Programming (ICSP)

dsPIC30F devices have a Watchdog Timer which is permanently enabled via the Configuration bits or can be software controlled. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT) which provides a delay on power-up only, designed to keep the part in Reset while the power supply stabilizes. With these two timers onchip, most applications need no external Reset circuitry.

Sleep mode is designed to offer a very low-current Power-Down mode. The user can wake-up from Sleep through external Reset, Watchdog Timer wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit a wide variety of applications. In the Idle mode, the clock sources are still active but the CPU is shut off. The RC oscillator option saves system cost while the LP crystal option saves power.

### 20.1 Oscillator System Overview

The dsPIC30F oscillator system has the following modules and features:

- Various external and internal oscillator options as clock sources

- An on-chip PLL to boost internal operating frequency

- A clock switching mechanism between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- Clock Control register (OSCCON)

- Configuration bits for main oscillator selection

Configuration bits determine the clock source upon Power-on Reset (POR) and Brown-out Reset (BOR). Thereafter, the clock source can be changed between permissible clock sources. The OSCCON register controls the clock switching and reflects system clock related status bits.

Table 20-1 provides a summary of the dsPIC30F oscillator operating modes. A simplified diagram of the oscillator system is shown in Figure 20-1.

## 20.2 Oscillator Configurations

#### 20.2.1 INITIAL CLOCK SOURCE SELECTION

While coming out of Power-on Reset or Brown-out Reset, the device selects its clock source based on:

- a) FOS<2:0> Configuration bits that select one of four oscillator groups,

- b) and FPR<4:0> Configuration bits that select one of 13 oscillator choices within the primary group.

The selection is as shown in Table 20-2.

#### 20.2.2 OSCILLATOR START-UP TIMER (OST)

In order to ensure that a crystal oscillator (or ceramic resonator) has started and stabilized, an Oscillator Start-up Timer is included. It is a simple 10-bit counter that counts 1024 Tosc cycles before releasing the oscillator clock to the rest of the system. The time-out period is designated as Tost. The Tost time is involved every time the oscillator has to restart (i.e., on POR, BOR and wake-up from Sleep). The Oscillator Start-up Timer is applied to the LP, XT, XTL and HS Oscillator modes (upon wake-up from Sleep, POR and BOR) for the primary oscillator.

| Oscillator Mode | Oscillator<br>Source | F | OS<2:0 | > |   | F | PR<4:( | )> |   | OSC2<br>Function |

|-----------------|----------------------|---|--------|---|---|---|--------|----|---|------------------|

| ECIO w/PLL 4x   | PLL                  | 1 | 1      | 1 | 0 | 1 | 1      | 0  | 1 | I/O              |

| ECIO w/PLL 8x   | PLL                  | 1 | 1      | 1 | 0 | 1 | 1      | 1  | 0 | I/O              |

| ECIO w/PLL 16x  | PLL                  | 1 | 1      | 1 | 0 | 1 | 1      | 1  | 1 | I/O              |

| FRC w/PLL 4x    | PLL                  | 1 | 1      | 1 | 0 | 0 | 0      | 0  | 1 | I/O              |

| FRC w/PLL 8x    | PLL                  | 1 | 1      | 1 | 0 | 1 | 0      | 1  | 0 | I/O              |

| FRC w/PLL 16x   | PLL                  | 1 | 1      | 1 | 0 | 0 | 0      | 1  | 1 | I/O              |

| XT w/PLL 4x     | PLL                  | 1 | 1      | 1 | 0 | 0 | 1      | 0  | 1 | OSC2             |

| XT w/PLL 8x     | PLL                  | 1 | 1      | 1 | 0 | 0 | 1      | 1  | 0 | OSC2             |

| XT w/PLL 16x    | PLL                  | 1 | 1      | 1 | 0 | 0 | 1      | 1  | 1 | OSC2             |

| HS2 w/PLL 4x    | PLL                  | 1 | 1      | 1 | 1 | 0 | 0      | 0  | 1 | OSC2             |

| HS2 w/PLL 8x    | PLL                  | 1 | 1      | 1 | 1 | 0 | 0      | 1  | 0 | OSC2             |

| HS2 w/PLL 16x   | PLL                  | 1 | 1      | 1 | 1 | 0 | 0      | 1  | 1 | OSC2             |

| HS3 w/PLL 4x    | PLL                  | 1 | 1      | 1 | 1 | 0 | 1      | 0  | 1 | OSC2             |

| HS3 w/PLL 8x    | PLL                  | 1 | 1      | 1 | 1 | 0 | 1      | 1  | 0 | OSC2             |

| HS3 w/PLL 16x   | PLL                  | 1 | 1      | 1 | 1 | 0 | 1      | 1  | 1 | OSC2             |

| ECIO            | External             | 0 | 1      | 1 | 0 | 1 | 1      | 0  | 0 | I/O              |

| ХТ              | External             | 0 | 1      | 1 | 0 | 0 | 1      | 0  | 0 | OSC2             |

| HS              | External             | 0 | 1      | 1 | 0 | 0 | 0      | 1  | 0 | OSC2             |

| EXT             | External             | 0 | 1      | 1 | 0 | 1 | 0      | 1  | 1 | CLKO             |

| ERC             | External             | 0 | 1      | 1 | 0 | 1 | 0      | 0  | 1 | CLKO             |

| ERCIO           | External             | 0 | 1      | 1 | 0 | 1 | 0      | 0  | 0 | I/O              |

| XTL             | External             | 0 | 1      | 1 | 0 | 0 | 0      | 0  | 0 | OSC2             |

| LP              | Secondary            | 0 | 0      | 0 | Х | Х | Х      | Х  | Х | (Notes 1, 2)     |

| FRC             | Internal FRC         | 0 | 0      | 1 | Х | Х | Х      | Х  | Х | (Notes 1, 2)     |

| LPRC            | Internal LPRC        | 0 | 1      | 0 | Х | Х | Х      | Х  | Х | (Notes 1, 2)     |

#### TABLE 20-2: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

**Note 1:** The OSC2 pin is either usable as a general purpose I/O pin functionality only depending on the Primary Oscillator mode selection (FPR<4:0>).

2: Note that OSC1 pin cannot be used as an I/O pin even if the secondary oscillator or an internal clock source is selected at all times.

## REGISTER 20-2: OSCTUN: FRC OSCILLATOR TUNING REGISTER

|               | 20-2. 0001 |                                 |                 |                   |                 |                 |       |

|---------------|------------|---------------------------------|-----------------|-------------------|-----------------|-----------------|-------|

| U-0           | U-0        | U-0                             | U-0             | U-0               | U-0             | U-0             | U-0   |

| —             | —          | —                               | —               | —                 | —               | —               | _     |

| bit 15        |            |                                 |                 |                   |                 |                 | bit   |

|               |            |                                 |                 |                   |                 |                 |       |

| U-0           | U-0        | U-0                             | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| _             | —          |                                 | —               |                   | TUI             | N<3:0>          |       |

| bit 7         |            |                                 |                 |                   |                 |                 | bit ( |

|               |            |                                 |                 |                   |                 |                 |       |

| Legend:       |            |                                 |                 |                   |                 |                 |       |

| R = Readabl   | e bit      | W = Writable I                  | oit             | U = Unimpler      | mented bit, rea | ad as '0'       |       |

| -n = Value at | POR        | '1' = Bit is set                |                 | '0' = Bit is cle  | ared            | x = Bit is unkr | nown  |

|               |            | minal 7.37 MHz<br>mum frequency | •               |                   |                 |                 |       |

|               | 0001 =     | er frequency, os                | cillator is rur | nning at calibrat | ed frequency    |                 |       |

|               |            |                                 |                 |                   |                 |                 |       |

- 1001 =

- 1000 = Minimum frequency

Table 20-5 shows the Reset conditions for the RCON register. Since the control bits within the RCON register are R/W, the information in the table means that all the bits are negated prior to the action specified in the condition column.

| Condition                              | Program<br>Counter    | TRAPR | IOPUWR | EXTR | SWR | WDTO | IDLE | SLEEP | POR | BOR |

|----------------------------------------|-----------------------|-------|--------|------|-----|------|------|-------|-----|-----|

| Power-on Reset                         | 0x000000              | 0     | 0      | 0    | 0   | 0    | 0    | 0     | 1   | 1   |

| Brown-out Reset                        | 0x000000              | 0     | 0      | 0    | 0   | 0    | 0    | 0     | 0   | 1   |

| MCLR Reset during normal operation     | 0x000000              | 0     | 0      | 1    | 0   | 0    | 0    | 0     | 0   | 0   |

| Software Reset during normal operation | 0x000000              | 0     | 0      | 0    | 1   | 0    | 0    | 0     | 0   | 0   |

| MCLR Reset during Sleep                | 0x000000              | 0     | 0      | 1    | 0   | 0    | 0    | 1     | 0   | 0   |

| MCLR Reset during Idle                 | 0x000000              | 0     | 0      | 1    | 0   | 0    | 1    | 0     | 0   | 0   |

| WDT Time-out Reset                     | 0x000000              | 0     | 0      | 0    | 0   | 1    | 0    | 0     | 0   | 0   |

| WDT Wake-up                            | PC + 2                | 0     | 0      | 0    | 0   | 1    | 0    | 1     | 0   | 0   |

| Interrupt Wake-up from Sleep           | PC + 2 <sup>(1)</sup> | 0     | 0      | 0    | 0   | 0    | 0    | 1     | 0   | 0   |

| Clock Failure Trap                     | 0x000004              | 0     | 0      | 0    | 0   | 0    | 0    | 0     | 0   | 0   |

| Trap Reset                             | 0x000000              | 1     | 0      | 0    | 0   | 0    | 0    | 0     | 0   | 0   |

| Illegal Operation Trap                 | 0x000000              | 0     | 1      | 0    | 0   | 0    | 0    | 0     | 0   | 0   |

## TABLE 20-5: INITIALIZATION CONDITION FOR RCON REGISTER: CASE 1

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0'

**Note 1:** When the wake-up is due to an enabled interrupt, the PC is loaded with the corresponding interrupt vector.

Table 20-6 shows a second example of the bit conditions for the RCON register. In this case, it is not assumed the user has set/cleared specific bits prior to action specified in the condition column.

## TABLE 20-6: INITIALIZATION CONDITION FOR RCON REGISTER: CASE 2

| Condition                              | Program<br>Counter    | TRAPR | IOPUWR | EXTR | SWR | WDTO | IDLE | SLEEP | POR | BOR |

|----------------------------------------|-----------------------|-------|--------|------|-----|------|------|-------|-----|-----|

| Power-on Reset                         | 0x000000              | 0     | 0      | 0    | 0   | 0    | 0    | 0     | 1   | 1   |

| Brown-out Reset                        | 0x000000              | u     | u      | u    | u   | u    | u    | u     | 0   | 1   |

| MCLR Reset during normal operation     | 0x000000              | u     | u      | 1    | 0   | 0    | 0    | 0     | u   | u   |

| Software Reset during normal operation | 0x000000              | u     | u      | 0    | 1   | 0    | 0    | 0     | u   | u   |

| MCLR Reset during Sleep                | 0x000000              | u     | u      | 1    | u   | 0    | 0    | 1     | u   | u   |

| MCLR Reset during Idle                 | 0x000000              | u     | u      | 1    | u   | 0    | 1    | 0     | u   | u   |

| WDT Time-out Reset                     | 0x000000              | u     | u      | 0    | 0   | 1    | 0    | 0     | u   | u   |

| WDT Wake-up                            | PC + 2                | u     | u      | u    | u   | 1    | u    | 1     | u   | u   |

| Interrupt Wake-up from Sleep           | PC + 2 <sup>(1)</sup> | u     | u      | u    | u   | u    | u    | 1     | u   | u   |

| Clock Failure Trap                     | 0x000004              | u     | u      | u    | u   | u    | u    | u     | u   | u   |

| Trap Reset                             | 0x000000              | 1     | u      | u    | u   | u    | u    | u     | u   | u   |

| Illegal Operation Reset                | 0x000000              | u     | 1      | u    | u   | u    | u    | u     | u   | u   |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0'

**Note 1:** When the wake-up is due to an enabled interrupt, the PC is loaded with the corresponding interrupt vector.

## TABLE 21-2: INSTRUCTION SET OVERVIEW

| Base<br>Instr<br># | Assembly<br>Mnemoni<br>c |       | Assembly Syntax | Description                              | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|--------------------------|-------|-----------------|------------------------------------------|---------------|----------------|--------------------------|

| 1                  | ADD                      | ADD   | Acc             | Add Accumulators                         | 1             | 1              | OA,OB,SA,SB              |

|                    |                          | ADD   | f               | f = f + WREG                             | 1             | 1              | C,DC,N,OV,Z              |

|                    |                          | ADD   | f,WREG          | WREG = f + WREG                          | 1             | 1              | C,DC,N,OV,Z              |

|                    |                          | ADD   | #lit10,Wn       | Wd = lit10 + Wd                          | 1             | 1              | C,DC,N,OV,Z              |

|                    |                          | ADD   | Wb,Ws,Wd        | Wd = Wb + Ws                             | 1             | 1              | C,DC,N,OV,Z              |

|                    |                          | ADD   | Wb,#lit5,Wd     | Wd = Wb + lit5                           | 1             | 1              | C,DC,N,OV,Z              |

|                    |                          | ADD   | Wso,#Slit4,Acc  | 16-bit Signed Add to Accumulator         | 1             | 1              | OA,OB,SA,SB              |

| 2                  | ADDC                     | ADDC  | f               | f = f + WREG + (C)                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                          | ADDC  | f,WREG          | WREG = f + WREG + (C)                    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                          | ADDC  | #lit10,Wn       | Wd = Iit10 + Wd + (C)                    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                          | ADDC  | Wb,Ws,Wd        | Wd = Wb + Ws + (C)                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                          | ADDC  | Wb,#lit5,Wd     | Wd = Wb + lit5 + (C)                     | 1             | 1              | C,DC,N,OV,Z              |

| 3                  | AND                      | AND   | f               | f = f .AND. WREG                         | 1             | 1              | N,Z                      |

|                    |                          | AND   | f,WREG          | WREG = f .AND. WREG                      | 1             | 1              | N,Z                      |

|                    |                          | AND   | #lit10,Wn       | Wd = lit10 .AND. Wd                      | 1             | 1              | N,Z                      |

|                    |                          | AND   | Wb,Ws,Wd        | Wd = Wb .AND. Ws                         | 1             | 1              | N,Z                      |

|                    |                          | AND   | Wb,#lit5,Wd     | Wd = Wb .AND. lit5                       | 1             | 1              | N,Z                      |

| 4                  | ASR                      | ASR   | f               | f = Arithmetic Right Shift f             | 1             | 1              | C,N,OV,Z                 |

|                    |                          | ASR   | f,WREG          | WREG = Arithmetic Right Shift f          | 1             | 1              | C,N,OV,Z                 |

|                    |                          | ASR   | Ws,Wd           | Wd = Arithmetic Right Shift Ws           | 1             | 1              | C,N,OV,Z                 |

|                    |                          | ASR   | Wb,Wns,Wnd      | Wnd = Arithmetic Right Shift Wb by Wns   | 1             | 1              | N,Z                      |

|                    |                          | ASR   | Wb,#lit5,Wnd    | Wnd = Arithmetic Right Shift Wb by lit5  | 1             | 1              | N,Z                      |

| 5                  | BCLR                     | BCLR  | f,#bit4         | Bit Clear f                              | 1             | 1              | None                     |

| •                  | Doni                     | BCLR  | Ws,#bit4        | Bit Clear Ws                             | 1             | 1              | None                     |

| 6                  | BRA                      | BRA   | C,Expr          | Branch if Carry                          | 1             | 1 (2)          | None                     |

| •                  | Ditti                    | BRA   | GE, Expr        | Branch if Greater than or Equal          | 1             | 1 (2)          | None                     |

|                    |                          | BRA   | GEU, Expr       | Branch if Unsigned Greater than or Equal | 1             | 1 (2)          | None                     |

|                    |                          | BRA   | GT, Expr        | Branch if Greater than                   | 1             | 1 (2)          | None                     |

|                    |                          | BRA   | GTU, Expr       | Branch if Unsigned Greater than          | 1             | 1 (2)          | None                     |

|                    |                          | BRA   | LE, Expr        | Branch if Less than or Equal             | 1             | 1 (2)          | None                     |

|                    |                          | BRA   | LEU, Expr       | Branch if Unsigned Less than or Equal    | 1             | 1 (2)          | None                     |

|                    |                          | BRA   | LT, Expr        | Branch if Less than                      | 1             | 1 (2)          | None                     |

|                    |                          | BRA   | LTU, Expr       | Branch if Unsigned Less than             | 1             | 1 (2)          | None                     |

|                    |                          | BRA   | N,Expr          | Branch if Negative                       | 1             | 1 (2)          | None                     |

|                    |                          | BRA   | NC, Expr        | Branch if Not Carry                      | 1             | 1 (2)          | None                     |

|                    |                          | BRA   | NN, Expr        | Branch if Not Negative                   | 1             | 1 (2)          | None                     |

|                    |                          | BRA   |                 | Branch if Not Overflow                   | 1             | 1 (2)          | None                     |

|                    |                          | BRA   | NOV, Expr       | Branch if Not Zero                       | 1             | 1 (2)          | None                     |

|                    |                          |       | NZ, Expr        | Branch if Accumulator A Overflow         | 1             | 1 (2)          | None                     |

|                    |                          | BRA   | OA, Expr        | Branch if Accumulator B Overflow         | 1             | 1 (2)          | None                     |

|                    |                          | BRA   | OB, Expr        | Branch if Overflow                       |               | . ,            |                          |

|                    |                          | BRA   | OV,Expr         |                                          | 1             | 1 (2)          | None                     |

|                    |                          | BRA   | SA, Expr        | Branch if Accumulator A Saturated        | 1             | 1 (2)          | None                     |

|                    |                          | BRA   | SB, Expr        | Branch if Accumulator B Saturated        | 1             | 1 (2)          | None                     |

|                    |                          | BRA   | Expr            | Branch Unconditionally                   | 1             | 2              | None                     |

|                    |                          | BRA   | Z,Expr          | Branch if Zero                           | 1             | 1 (2)          | None                     |

| 7                  |                          | BRA   | Wn              | Computed Branch                          | 1             | 2              | None                     |

| 7                  | BSET                     | BSET  | f,#bit4         | Bit Set f                                | 1             | 1              | None                     |

|                    | 1                        | BSET  | Ws,#bit4        | Bit Set Ws                               | 1             | 1              | None                     |

| 8                  | BSW                      | BSW.C | Ws,Wb           | Write C bit to Ws <wb></wb>              | 1             | 1              | None                     |

## 23.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC30F electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

For detailed information about the dsPIC30F architecture and core, refer to the "dsPIC30F Family Reference Manual" (DS70046).

Absolute maximum ratings for the dsPIC30F family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

## Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 40°C to +125°C |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Storage temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 65°C to +150°C |

| Voltage on any pin with respect to Vss (except VDD and MCLR) (Note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |

| Voltage on VDD with respect to Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0.3V to +5.5V  |

| Voltage on MCLR with respect to Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0V to +13.25V  |

| Maximum current out of Vss pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

| Maximum current into VDD pin (Note 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 250 mA         |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ±20 mA         |

| Output clamp current, IOK (VO < 0 or VO > VDD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ±20 mA         |

| Maximum output current sunk by any I/O pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25 mA          |

| Maximum output current sourced by any I/O pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25 mA          |

| Maximum current sunk by all ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

| Maximum current sourced by all ports (Note 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 200 mA         |

| Note 4. Motors and the balance $M_{\rm eff} = M_{\rm eff}$ | 00             |

**Note 1:** Voltage spikes below Vss at the MCLR/VPP pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100W should be used when applying a "low" level to the MCLR/VPP pin, rather than pulling this pin directly to Vss.