Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20 MIPS                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                     |

| Peripherals                | AC'97, Brown-out Detect/Reset, I <sup>2</sup> S, POR, PWM, WDT                |

| Number of I/O              | 30                                                                            |

| Program Memory Size        | 48KB (16K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 1K x 8                                                                        |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 13x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8x8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f4013-20e-ml |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

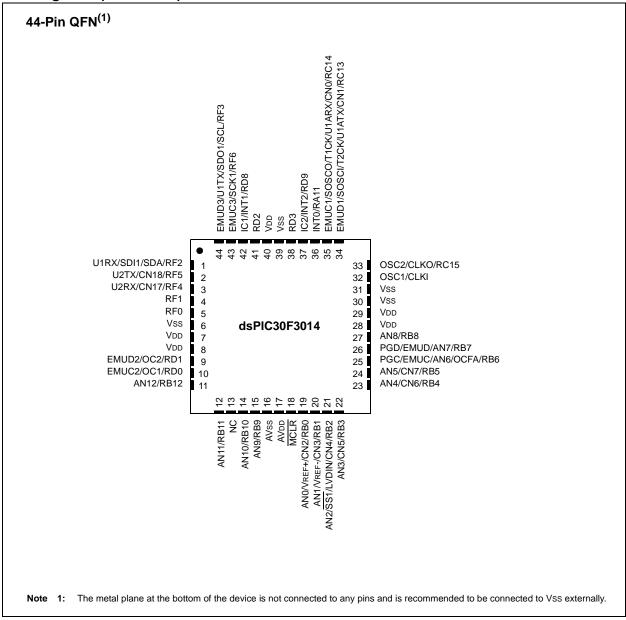

#### Pin Diagrams (Continued)

#### CORE REGISTER MAP<sup>(1)</sup> (CONTINUED) **TABLE 3-3:**

| IADEL J- | J. U              |        |                   |        |                                                                                       |  |  |    |         |  |  |  |  |                     |                     |                     |                     |                     |

|----------|-------------------|--------|-------------------|--------|---------------------------------------------------------------------------------------|--|--|----|---------|--|--|--|--|---------------------|---------------------|---------------------|---------------------|---------------------|

| SFR Name | Address<br>(Home) | Bit 15 | Bit 14            | Bit 13 | t 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |  |  |    |         |  |  |  |  |                     |                     |                     | Reset State         |                     |

| CORCON   | 0044              | —      |                   | —      | US EDT DL2 DL1 DL0 SATA SATB SATDW ACCSAT IPL3 PSV RND IF 00                          |  |  |    |         |  |  |  |  |                     |                     | 0000 0000 0010 0000 |                     |                     |

| MODCON   | 0046              | XMODEN | YMODEN            | _      | BWM<3:0> YWM<3:0> XWM<3:0> 0                                                          |  |  |    |         |  |  |  |  |                     |                     |                     | 0000 0000 0000 0000 |                     |

| XMODSRT  | 0048              |        | XS<15:1> 0        |        |                                                                                       |  |  |    |         |  |  |  |  |                     | uuuu uuuu uuuu uuu0 |                     |                     |                     |

| XMODEND  | 004A              |        | XE<15:1> 1        |        |                                                                                       |  |  |    |         |  |  |  |  | uuuu uuuu uuul      |                     |                     |                     |                     |

| YMODSRT  | 004C              |        |                   |        |                                                                                       |  |  | YS | S<15:1> |  |  |  |  |                     |                     |                     | 0                   | uuuu uuuu uuuu uuu0 |

| YMODEND  | 004E              |        | YE<15:1> 1        |        |                                                                                       |  |  |    |         |  |  |  |  | uuuu uuuu uuul      |                     |                     |                     |                     |

| XBREV    | 0050              | BREN   | BREN XB<14:0>     |        |                                                                                       |  |  |    |         |  |  |  |  | uuuu uuuu uuuu uuuu |                     |                     |                     |                     |

| DISICNT  | 0052              | _      | — — DISICNT<13:0> |        |                                                                                       |  |  |    |         |  |  |  |  | 0000 0000 0000 0000 |                     |                     |                     |                     |

Legend:

u = uninitialized bit; — = unimplemented bit, read as '0'

Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

#### 5.6 **Programming Operations**

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. A programming operation is nominally 2 msec in duration and the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 5.6.1 PROGRAMMING ALGORITHM FOR PROGRAM FLASH

The user can erase or program one row of program Flash memory at a time. The general process is:

- 1. Read one row of program Flash (32 instruction words) and store into data RAM as a data "image".

- 2. Update the data image with the desired new data.

- 3. Erase program Flash row.

- a) Set up NVMCON register for multi-word, program Flash, erase, and set WREN bit.

- b) Write address of row to be erased into NVMADRU/NVMDR.

- c) Write 0x55 to NVMKEY.

- d) Write 0xAA to NVMKEY.

- e) Set the WR bit. This begins erase cycle.

- f) CPU stalls for the duration of the erase cycle.

- g) The WR bit is cleared when erase cycle ends.

#### EXAMPLE 5-1: ERASING A ROW OF PROGRAM MEMORY

|   | -           | ON for erase operation, mult        |       | write                                     |

|---|-------------|-------------------------------------|-------|-------------------------------------------|

| ; | program mer | mory selected, and writes ena       | abled |                                           |

|   | MOV         | #0x4041,W0                          | ;     |                                           |

|   | MOV         | W0,NVMCON                           | ;     | Init NVMCON SFR                           |

| ; | Init pointe | er to row to be ERASED              |       |                                           |

|   | MOV         | <pre>#tblpage(PROG_ADDR),W0</pre>   | ;     |                                           |

|   | MOV         | W0,NVMADRU                          | ;     | Initialize PM Page Boundary SFR           |

|   | MOV         | <pre>#tbloffset(PROG_ADDR),W0</pre> | ;     | Intialize in-page EA[15:0] pointer        |

|   | MOV         | W0, NVMADR                          | ;     | Initialize NVMADR SFR                     |

|   | DISI        | #5                                  | ;     | Block all interrupts with priority <7 for |

|   |             |                                     | ;     | next 5 instructions                       |

|   | MOV         | #0x55,W0                            |       |                                           |

|   | MOV         | W0,NVMKEY                           | ;     | Write the 0x55 key                        |

|   | MOV         | #0xAA,W1                            | ;     |                                           |

|   | MOV         | W1,NVMKEY                           | ;     | Write the OxAA key                        |

|   | BSET        | NVMCON, #WR                         | ;     | Start the erase sequence                  |

|   | NOP         |                                     | ;     | Insert two NOPs after the erase           |

|   | NOP         |                                     | ;     | command is asserted                       |

|   |             |                                     |       |                                           |

- 4. Write 32 instruction words of data from data RAM "image" into the program Flash write latches.

- 5. Program 32 instruction words into program Flash.

- Set up NVMCON register for multi-word, program Flash, program, and set WREN bit.

- b) Write 0x55 to NVMKEY.

- c) Write 0xAA to NVMKEY.

- d) Set the WR bit. This begins program cycle.

- e) CPU stalls for duration of the program cycle.

- f) The WR bit is cleared by the hardware when program cycle ends.

- 6. Repeat steps 1 through 5 as needed to program desired amount of program Flash memory.

### 5.6.2 ERASING A ROW OF PROGRAM MEMORY

Example 5-1 shows a code sequence that can be used to erase a row (32 instructions) of program memory.

NOTES:

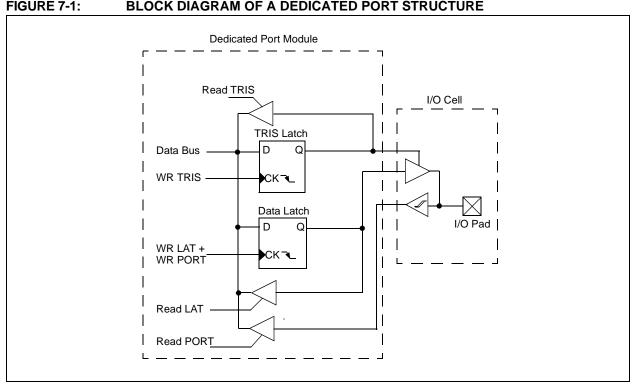

#### 7.0 I/O PORTS

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU. peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

All of the device pins (except VDD, VSS, MCLR and OSC1/CLKI) are shared between the peripherals and the parallel I/O ports.

All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

#### 7.1 Parallel I/O (PIO) Ports

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have three registers directly associated with the operation of the port pin. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset.

Reads from the latch (LATx), read the latch. Writes to the latch, write the latch (LATx). Reads from the port (PORTx), read the port pins and writes to the port pins, write the latch (LATx).

Any bit and its associated data and control registers that are not valid for a particular device are disabled, which means the corresponding LATx and TRISx registers and the port pin read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs. An example is the INT4 pin.

A Parallel I/O (PIO) port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pad cell. Figure 7-2 shows how ports are shared with other peripherals and the associated I/O cell (pad) to which they are connected. Table 7-1 shows the formats of the registers for the shared ports, PORTB through PORTF.

Note: The actual bits in use vary between devices.

FIGURE 7-1: **BLOCK DIAGRAM OF A DEDICATED PORT STRUCTURE**

NOTES:

NOTES:

### TABLE 13-1: dsPIC30F3014 OUTPUT COMPARE REGISTER MAP<sup>(1)</sup>

| SFR Name | Addr.   | Bit 15                          | Bit 14                              | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7     | Bit 6     | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1               | Bit 0               | Reset State         |

|----------|---------|---------------------------------|-------------------------------------|--------|--------|--------|--------|-------|-----------|-----------|-----------|-------|-------|--------|-------|---------------------|---------------------|---------------------|

| OC1RS    | 0180    |                                 | Output Compare 1 Secondary Register |        |        |        |        |       |           |           |           |       |       |        |       |                     | 0000 0000 0000 0000 |                     |

| OC1R     | 0182    |                                 | Output Compare 1 Main Register      |        |        |        |        |       |           |           |           |       |       |        |       | 0000 0000 0000 0000 |                     |                     |

| OC1CON   | 0184    | _                               | _                                   | OCSIDL | _      | _      | —      | _     | _         | _         |           | _     | OCFLT | OCTSEL |       | OCM<2:0>            | >                   | 0000 0000 0000 0000 |

| OC2RS    | 0186    |                                 | Output Compare 2 Secondary Register |        |        |        |        |       |           |           |           |       |       |        |       | 0000 0000 0000 0000 |                     |                     |

| OC2R     | 0188    |                                 |                                     |        |        |        |        | Οι    | utput Com | pare 2 Ma | n Registe | r     |       |        |       |                     |                     | 0000 0000 0000 0000 |

| OC2CON   | 018A    | _                               |                                     | OCSIDL | _      | _      | _      | _     | _         | _         | _         | _     | OCFLT | OCTSE  |       | OCM<2:0>            | >                   | 0000 0000 0000 0000 |

| Legend:  | — – uni | - unimplemented bit read as '0' |                                     |        |        |        |        |       |           |           |           |       |       |        |       |                     |                     |                     |

Legend: = unimplemented bit, read as '0

Note 1: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

#### TABLE 13-2: dsPIC30F4013 OUTPUT COMPARE REGISTER MAP<sup>(1)</sup>

| SFR Name | Addr. | Bit 15                       | Bit 14                              | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7     | Bit 6               | Bit 5 | Bit 4 | Bit 3  | Bit 2               | Bit 1               | Bit 0    | Reset State         |

|----------|-------|------------------------------|-------------------------------------|--------|--------|--------|--------|-------|-----------|-----------|---------------------|-------|-------|--------|---------------------|---------------------|----------|---------------------|

| OC1RS    | 0180  |                              | Output Compare 1 Secondary Register |        |        |        |        |       |           |           |                     |       |       |        |                     | 0000 0000 0000 0000 |          |                     |

| OC1R     | 0182  |                              | Output Compare 1 Main Register      |        |        |        |        |       |           |           |                     |       |       |        |                     | 0000 0000 0000 0000 |          |                     |

| OC1CON   | 0184  | OCSIDL OCFLT OCTSEL OCM<2:0> |                                     |        |        |        |        |       |           |           | 0000 0000 0000 0000 |       |       |        |                     |                     |          |                     |

| OC2RS    | 0186  |                              | Output Compare 2 Secondary Register |        |        |        |        |       |           |           |                     |       |       |        | 0000 0000 0000 0000 |                     |          |                     |

| OC2R     | 0188  |                              | Output Compare 2 Main Register      |        |        |        |        |       |           |           |                     |       |       |        | 0000 0000 0000 0000 |                     |          |                     |

| OC2CON   | 018A  | _                            | _                                   | OCSIDL | _      | _      | _      | _     | _         | _         | _                   | _     | OCFLT | OCTSE  |                     | OCM<2:0>            | •        | 0000 0000 0000 0000 |

| OC3RS    | 018C  |                              |                                     |        |        |        |        | Outpu | ut Compar | e 3 Secon | dary Regi           | ster  |       |        |                     |                     |          | 0000 0000 0000 0000 |

| OC3R     | 018E  |                              |                                     |        |        |        |        | Ou    | utput Com | pare 3 Ma | in Registe          | r     |       |        |                     |                     |          | 0000 0000 0000 0000 |

| OC3CON   | 0190  | _                            | _                                   | OCSIDL | _      | _      | _      | _     | _         | —         | —                   | _     | OCFLT | OCTSEL |                     | OCM<2:0>            | >        | 0000 0000 0000 0000 |

| OC4RS    | 0192  |                              |                                     |        |        |        |        | Outpu | ut Compar | e 4 Secon | dary Regi           | ster  |       | -      | •                   |                     |          | 0000 0000 0000 0000 |

| OC4R     | 0194  |                              |                                     |        |        |        |        | Ou    | utput Com | pare 4 Ma | in Registe          | r     |       |        |                     |                     |          | 0000 0000 0000 0000 |

| OC4CON   | 0196  | —                            |                                     | OCSIDL | _      | _      | _      |       | _         | _         | —                   | _     | OCFLT | OCTSEL |                     | OCM<2:0>            | <b>`</b> | 0000 0000 0000 0000 |

Legend: --- = unimplemented bit, read as '0'

Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields. Note 1:

### 14.2 I<sup>2</sup>C Module Addresses

The I2CADD register contains the Slave mode addresses. The register is a 10-bit register.

If the A10M bit (I2CCON<10>) is '0', the address is interpreted by the module as a 7-bit address. When an address is received, it is compared to the 7 LSbs of the I2CADD register.

If the A10M bit is '1', the address is assumed to be a 10-bit address. When an address is received, it is compared with the binary value, '11110 A9 A8' (where A9 and A8 are two Most Significant bits of I2CADD). If that value matches, the next address is compared with the Least Significant 8 bits of I2CADD, as specified in the 10-bit addressing protocol.

#### TABLE 14-1: 7-BIT I<sup>2</sup>C<sup>™</sup> SLAVE ADDRESSES SUPPORTED BY dsPIC30F

| 0x00      | General Call Address or Start Byte    |

|-----------|---------------------------------------|

| 0x01-0x03 | Reserved                              |

| 0x04-0x07 | HS mode Master Codes                  |

| 0x08-0x77 | Valid 7-Bit Addresses                 |

| 0x78-0x7b | Valid 10-Bit Addresses (lower 7 bits) |

| 0x7c-0x7f | Reserved                              |

### 14.3 I<sup>2</sup>C 7-Bit Slave Mode Operation

Once enabled (I2CEN = 1), the slave module waits for a Start bit to occur (i.e., the I<sup>2</sup>C module is 'Idle'). Following the detection of a Start bit, 8 bits are shifted into I2CRSR, and the address is compared against I2CADD. In 7-bit mode (A10M = 0), bits I2CADD<6:0> are compared against I2CRSR<7:1> and I2CRSR<0> is the R\_W bit. All incoming bits are sampled on the rising edge of SCL.

If an address match occurs, an Acknowledgement is sent and the Slave Event Interrupt Flag (SI2CIF) is set on the falling edge of the ninth (ACK) bit. The address match does not affect the contents of the I2CRCV buffer or the RBF bit.

#### 14.3.1 SLAVE TRANSMISSION

If the R\_W bit received is a '1', the serial port goes into Transmit mode. It sends an ACK on the ninth bit and then holds SCL to '0' until the CPU responds by writing to I2CTRN. SCL is released by setting the SCLREL bit, and 8 bits of data are shifted out. Data bits are shifted out on the falling edge of SCL, such that SDA is valid during SCL high. The interrupt pulse is sent on the falling edge of the ninth clock pulse, regardless of the status of the ACK received from the master.

#### 14.3.2 SLAVE RECEPTION

If the R\_W bit received is a '0' during an address match, then Receive mode is initiated. Incoming bits are sampled on the rising edge of SCL. After 8 bits are received, if I2CRCV is not full or I2COV is not set, I2CRSR is transferred to I2CRCV. ACK is sent on the ninth clock.

If the RBF flag is set, indicating that I2CRCV is still holding data from a previous operation (RBF = 1), then ACK is not sent; however, the interrupt pulse is generated. In the case of an overflow, the contents of the I2CRSR are not loaded into the I2CRCV.

| Note: | The I2CRCV is loaded if the I2COV bit = 1            |

|-------|------------------------------------------------------|

| Note: |                                                      |

|       | and the RBF flag = 0. In this case, a read           |

|       | of the I2CRCV was performed but the                  |

|       | user did not clear the state of the I2COV            |

|       | bit before the next receive occurred. The            |

|       | acknowledgement is not sent ( $\overline{ACK} = 1$ ) |

|       | and the I2CRCV is updated.                           |

### 14.4 I<sup>2</sup>C 10-Bit Slave Mode Operation

In 10-bit mode, the basic receive and transmit operations are the same as in the 7-bit mode. However, the criteria for address match is more complex.

The  $I^2C$  specification dictates that a slave must be addressed for a write operation with two address bytes following a Start bit.

The A10M bit is a control bit that signifies that the address in I2CADD is a 10-bit address rather than a 7-bit address. The address detection protocol for the first byte of a message address is identical for 7-bit and 10-bit messages, but the bits being compared are different.

I2CADD holds the entire 10-bit address. Upon receiving an address following a Start bit, I2CRSR <7:3> is compared against a literal '11110' (the default 10-bit address) and I2CRSR<2:1> are compared against I2CADD<9:8>. If a match occurs and if  $R_W = 0$ , the interrupt pulse is sent. The ADD10 bit is cleared to indicate a partial address match. If a match fails or  $R_W = 1$ , the ADD10 bit is cleared and the module returns to the Idle state.

The low byte of the address is then received and compared with I2CADD<7:0>. If an address match occurs, the interrupt pulse is generated and the ADD10 bit is set, indicating a complete 10-bit address match. If an address match did not occur, the ADD10 bit is cleared and the module returns to the Idle state.

#### 14.4.1 10-BIT MODE SLAVE TRANSMISSION

Once a slave is addressed in this fashion with the full 10-bit address (we refer to this state as "PRIOR\_ADDR\_MATCH"), the master can begin sending data bytes for a slave reception operation.

#### 14.4.2 10-BIT MODE SLAVE RECEPTION

Once addressed, the master can generate a Repeated Start, reset the high byte of the address and set the R\_W bit without generating a Stop bit, thus initiating a slave transmit operation.

#### 14.5 Automatic Clock Stretch

In the Slave modes, the module can synchronize buffer reads and write to the master device by clock stretching.

#### 14.5.1 TRANSMIT CLOCK STRETCHING

Both 10-Bit and 7-Bit Transmit modes implement clock stretching by asserting the SCLREL bit after the falling edge of the ninth clock, if the TBF bit is cleared, indicating the buffer is empty.

In Slave Transmit modes, clock stretching is always performed irrespective of the STREN bit.

Clock synchronization takes place following the ninth clock of the transmit sequence. If the device samples an ACK on the falling edge of the ninth clock and if the TBF bit is still clear, then the SCLREL bit is automatically cleared. The SCLREL being cleared to '0' asserts the SCL line low. The user's ISR must set the SCLREL bit before transmission is allowed to continue. By holding the SCL line low, the user has time to service the ISR and load the contents of the I2CTRN before the master device can initiate another transmit sequence.

- Note 1: If the user loads the contents of I2CTRN, setting the TBF bit before the falling edge of the ninth clock, the SCLREL bit is not be cleared and clock stretching does not occur.

- **2:** The SCLREL bit can be set in software, regardless of the state of the TBF bit.

#### 14.5.2 RECEIVE CLOCK STRETCHING

The STREN bit in the I2CCON register can be used to enable clock stretching in Slave Receive mode. When the STREN bit is set, the SCL pin is held low at the end of each data receive sequence.

#### 14.5.3 CLOCK STRETCHING DURING 7-BIT ADDRESSING (STREN = 1)

When the STREN bit is set in Slave Receive mode, the SCL line is held low when the buffer register is full. The method for stretching the SCL output is the same for both 7 and 10-Bit Addressing modes.

Clock stretching takes place following the ninth clock of the receive sequence. <u>On</u> the falling edge of the ninth clock at the end of the ACK sequence, if the RBF bit is set, the SCLREL bit is automatically cleared, forcing the SCL output to be held low. The user's ISR must set the SCLREL bit before reception is allowed to continue. By holding the SCL line low, the user has time to service the ISR and read the contents of the I2CRCV before the master device can initiate another receive sequence. This prevents buffer overruns from occurring.

- Note 1: If the user reads the contents of the I2CRCV, clearing the RBF bit before the falling edge of the ninth clock, the SCLREL bit is not cleared and clock stretching does not occur.

- 2: The SCLREL bit can be set in software regardless of the state of the RBF bit. The user should be careful to clear the RBF bit in the ISR before the next receive sequence in order to prevent an overflow condition.

#### 14.5.4 CLOCK STRETCHING DURING 10-BIT ADDRESSING (STREN = 1)

Clock stretching takes place automatically during the addressing sequence. Because this module has a register for the entire address, it is not necessary for the protocol to wait for the address to be updated.

After the address phase is complete, clock stretching occurs on each data receive or transmit sequence, as described earlier.

#### 14.6 Software Controlled Clock Stretching (STREN = 1)

When the STREN bit is '1', the SCLREL bit can be cleared by software to allow software to control the clock stretching. Program logic synchronizes writes to the SCLREL bit with the SCL clock. Clearing the SCLREL bit does not assert the SCL output until the module detects a falling edge on the SCL output and SCL is sampled low. If the SCLREL bit is cleared by the user while the SCL line has been sampled low, the SCL output is asserted (held low). The SCL output remains low until the SCLREL bit is set and all other devices on the I<sup>2</sup>C bus have deasserted SCL. This ensures that a write to the SCLREL bit does not violate the minimum high time requirement for SCL.

If the STREN bit is '0', a software write to the SCLREL bit is disregarded and has no effect on the SCLREL bit.

#### Bit 15 Bit 13 Bit 12 Bit 10 Bit 8 SFR Name Addr. Bit 14 Bit 11 Bit 9 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Reset State C1TX1B1 Transmit Buffer 1 Byte 1 Transmit Buffer 1 Byte 0 0356 C1TX1B2 0358 Transmit Buffer 1 Byte 3 Transmit Buffer 1 Byte 2 uuuu uuuu uuuu uuuu C1TX1B3 035A Transmit Buffer 1 Byte 5 Transmit Buffer 1 Byte 4 uuuu uuuu uuuu C1TX1B4 035C Transmit Buffer 1 Byte 7 Transmit Buffer 1 Byte 6 uuuu uuuu uuuu TXABT TXLARB TXERR C1TX1CON 035E \_ \_ TXREQ TXPRI<1:0> 0000 0000 0000 0000 \_ \_ C1TX0SID 0360 Transmit Buffer 0 Standard Identifier<10:6> \_ \_ \_ Transmit Buffer 0 Standard Identifier <5:0> SRR TXIDE uuuu u000 uuuu uuuu C1TX0EID 0362 Transmit Buffer 0 Extended Identifier <17:14> Transmit Buffer 0 Extended Identifier<13:6> \_ \_ \_ uuuu 0000 uuuu uuuu C1TX0DLC 0364 Transmit Buffer 0 Extended Identifier<5:0> TXRTR TXRB1 TXRB0 DLC<3:0> \_ \_ uuuu uuuu uuuu u000 C1TX0B1 0366 Transmit Buffer 0 Byte 0 Transmit Buffer 0 Byte 1 uuuu uuuu uuuu uuuu C1TX0B2 0368 Transmit Buffer 0 Byte 3 Transmit Buffer 0 Byte 2 uuuu uuuu uuuu C1TX0B3 036A Transmit Buffer 0 Byte 5 Transmit Buffer 0 Byte 4 uuuu uuuu uuuu C1TX0B4 036C Transmit Buffer 0 Byte 7 Transmit Buffer 0 Byte 6 uuuu uuuu uuuu uuuu TXABT TXLARB TXERR TXPRI<1:0> C1TX0CON 036E \_ \_\_\_\_ \_\_\_\_ TXREQ \_\_\_\_ 0000 0000 0000 0000 \_ \_ C1RX1SID 0370 Receive Buffer 1 Standard Identifier<10:0> SRR RXIDE 000u uuuu uuuu uuuu \_\_\_\_ C1RX1EID 0372 Receive Buffer 1 Extended Identifier <17:6> \_ \_ \_ \_ 0000 uuuu uuuu uuuu RXRTR RXRB1 RXRB0 DLC<3:0> C1RX1DLC 0374 Receive Buffer 1 Extended Identifier<5:0> uuuu uuuu 000u uuuu C1RX1B1 0376 Receive Buffer 1 Byte 1 Receive Buffer 1 Byte 0 1011011 101010 1010001 101000 C1RX1B2 0378 Receive Buffer 1 Byte 3 Receive Buffer 1 Byte 2 uuuu uuuu uuuu uuuu C1RX1B3 037A Receive Buffer 1 Byte 5 Receive Buffer 1 Byte 4 uuuu uuuu uuuu uuuu C1RX1B4 037C Receive Buffer 1 Byte 7 Receive Buffer 1 Byte 6 uuuu uuuu uuuu uuuu C1RX1CON 037E \_ RXFUL RXRTRRO FIL HIT<2.0> 0000 0000 0000 0000 \_ C1RX0SID 0380 \_ Receive Buffer 0 Standard Identifier<10:0> SRR RXIDE 000u uuuu uuuu uuuu \_ \_ C1RX0EID 0382 Receive Buffer 0 Extended Identifier<17:6> \_ 0000 uuuu uuuu uuuu RXRTR RXRB1 DLC<3:0> C1RX0DLC 0384 Receive Buffer 0 Extended Identifier<5:0> \_ \_ RXRB0 uuuu uuuu 000u uuuu C1RX0B1 0386 Receive Buffer 0 Byte 1 Receive Buffer 0 Byte 0 uuuu uuuu uuuu uuuu C1RX0B2 0388 Receive Buffer 0 Byte 3 Receive Buffer 0 Byte 2 uuuu uuuu uuuu uuuu C1RX0B3 038A Receive Buffer 0 Byte 5 Receive Buffer 0 Byte 4 uuuu uuuu uuuu uuuu C1RX0B4 038C Receive Buffer 0 Byte 7 Receive Buffer 0 Byte 6 uuuu uuuu uuuu RXRTRRO DBEN JTOFF FILHITO C1RX0CON 038F RXFUI \_ 0000 0000 0000 0000 \_ C1CTRL 0390 CANCAP \_ CSIDL ABAT CANCKS REQOP<2:0> OPMODE<2:0> \_ ICODE<2:0> 0000 0100 1000 0000 C1CFG1 0392 \_ \_ \_ \_ \_ \_ \_ SJW<1:0> BRP<5:0> 0000 0000 0000 0000 C1CFG2 SEG2PHTS SEG1PH<2:0> PRSEG<2.0> 0394 \_ WAKFIL \_ \_ \_ SEG2PH<2:0> SAM 0u00 0uuu uuuu uuuu C1INTF 0396 RX00VR RX10VR тхво TXEP RXEP TXWAR RXWAR EWARN IVRIF WAKIF ERRIF TX2IF TX1IF TX0IF RX1IF RX0IF 0000 0000 0000 0000 C1INTE 0398 ERRIE TX2IE TX1IE TX0IE RX1IE RX0IE 0000 0000 0000 0000 IVRIE WAKIE \_ \_ \_ \_\_\_\_ \_ C1EC 039A TERRCNT<7:0> RERRCNT<7:0> 0000 0000 0000 0000

### TABLE 17-1: dsPIC30F4013 CAN1 REGISTER MAP<sup>(1)</sup> (CONTINUED)

Legend: u = uninitialized bit; — = unimplemented bit, read as '0'

**Note** 1: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

### 18.0 DATA CONVERTER INTERFACE (DCI) MODULE

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

#### 18.1 Module Introduction

The dsPIC30F Data Converter Interface (DCI) module allows simple interfacing of devices, such as audio coder/decoders (Codecs), A/D converters and D/A converters. The following interfaces are supported:

- Framed Synchronous Serial Transfer (single or multichannel)

- Inter-IC Sound (I<sup>2</sup>S) Interface

- AC-Link Compliant mode

The DCI module provides the following general features:

- Programmable word size up to 16 bits

- Support for up to 16 time slots, for a maximum frame size of 256 bits

- Data buffering for up to 4 samples without CPU overhead

### 18.2 Module I/O Pins

There are four I/O pins associated with the module. When enabled, the module controls the data direction of each of the four pins.

#### 18.2.1 CSCK PIN

The CSCK pin provides the serial clock for the DCI module. The CSCK pin may be configured as an input or output using the CSCKD control bit in the DCICON1 SFR. When configured as an output, the serial clock is provided by the dsPIC30F. When configured as an input, the serial clock must be provided by an external device.

#### 18.2.2 CSDO PIN

The serial data output (CSDO) pin is configured as an output only pin when the module is enabled. The CSDO pin drives the serial bus whenever data is to be transmitted. The CSDO pin is tri-stated or driven to '0' during CSCK periods when data is not transmitted, depending on the state of the CSDOM control bit. This allows other devices to place data on the serial bus during transmission periods not used by the DCI module.

#### 18.2.3 CSDI PIN

The serial data input (CSDI) pin is configured as an input only pin when the module is enabled.

#### 18.2.3.1 COFS PIN

The Codec Frame Synchronization (COFS) pin is used to synchronize data transfers that occur on the CSDO and CSDI pins. The COFS pin may be configured as an input or an output. The data direction for the COFS pin is determined by the COFSD control bit in the DCICON1 register.

The DCI module accesses the shadow registers while the CPU is in the process of accessing the memory mapped buffer registers.

#### 18.2.4 BUFFER DATA ALIGNMENT

Data values are always stored left justified in the buffers since most Codec data is represented as a signed 2's complement fractional number. If the received word length is less than 16 bits, the unused LSbs in the receive buffer registers are set to '0' by the module. If the transmitted word length is less than 16 bits, the unused LSbs in the transmit buffer register are ignored by the module. The word length setup is described in subsequent sections of this document.

#### 18.2.5 TRANSMIT/RECEIVE SHIFT REGISTER

The DCI module has a 16-bit shift register for shifting serial data in and out of the module. Data is shifted in/ out of the shift register MSb first, since audio PCM data is transmitted in signed 2's complement format.

#### 18.2.6 DCI BUFFER CONTROL

The DCI module contains a buffer control unit for transferring data between the shadow buffer memory and the serial shift register. The buffer control unit is a simple 2-bit address counter that points to word locations in the shadow buffer memory. For the receive memory space (high address portion of DCI buffer memory), the address counter is concatenated with a '0' in the MSb location to form a 3-bit address. For the transmit memory space (high portion of DCI buffer memory), the address counter is concatenated with a '1' in the MSb location.

**Note:** The DCI buffer control unit always accesses the same relative location in the transmit and receive buffers, so only one address counter is provided.

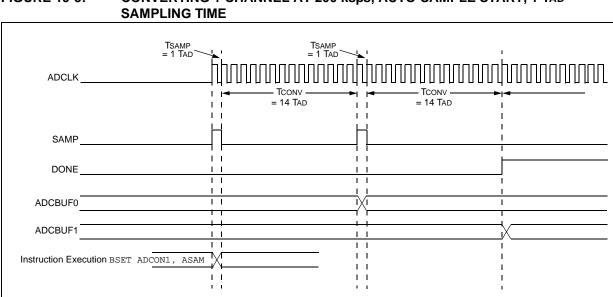

#### CONVERTING 1 CHANNEL AT 200 ksps, AUTO-SAMPLE START, 1 TAD **FIGURE 19-3:**

#### 19.8 **A/D Acquisition Requirements**

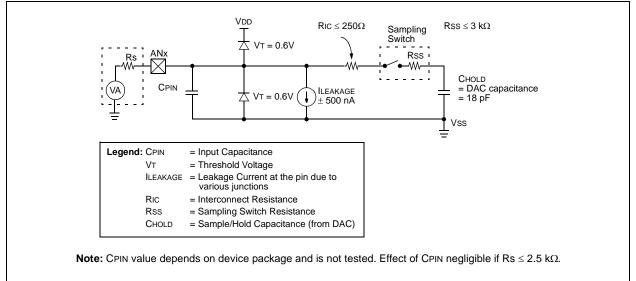

The analog input model of the 12-bit A/D converter is shown in Figure 19-4. The total sampling time for the A/D is a function of the internal amplifier settling time and the holding capacitor charge time.

For the A/D converter to meet its specified accuracy, the Charge Holding Capacitor (CHOLD) must be allowed to fully charge to the voltage level on the analog input pin. The Source Impedance (Rs), the Interconnect Impedance (RIC) and the Internal Sampling Switch (Rss) Impedance combine to directly affect the time required to charge the capacitor, CHOLD. The combined impedance of the analog sources must therefore be small enough to fully charge the holding capacitor within the chosen sample time. To minimize the effects of pin leakage currents on the accuracy of the A/D converter, the maximum recommended source impedance, Rs, is 2.5 kΩ. After the analog input channel is selected (changed), this sampling function must be completed prior to starting the conversion. The internal holding capacitor will be in a discharged state prior to each sample operation.

#### **FIGURE 19-4: 12-BIT A/D CONVERTER ANALOG INPUT MODEL**

#### **19.9 Module Power-Down Modes**

The module has two internal power modes.

When the ADON bit is '1', the module is in Active mode; it is fully powered and functional.

When ADON is '0', the module is in Off mode. The digital and analog portions of the circuit are disabled for maximum current savings.

In order to return to the Active mode from Off mode, the user must wait for the ADC circuitry to stabilize. The time required to stabilize is specified in **Section 23.0** "**Electrical Characteristics**".

#### 19.10 A/D Operation During CPU Sleep and Idle Modes

#### 19.10.1 A/D OPERATION DURING CPU SLEEP MODE

When the device enters Sleep mode, all clock sources to the module are shut down and stay at logic '0'.

If Sleep occurs in the middle of a conversion, the conversion is aborted. The converter does not continue with a partially completed conversion on exit from Sleep mode.

Register contents are not affected by the device entering or leaving Sleep mode.

The A/D module can operate during Sleep mode if the A/D clock source is set to RC (ADRC = 1). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed which eliminates all digital switching noise from the conversion. (When the conversion sequence is complete, the DONE bit is set.)

If the A/D interrupt is enabled, the device wakes up from Sleep. If the A/D interrupt is not enabled, the A/D module is then turned off, although the ADON bit remains set.

#### 19.10.2 A/D OPERATION DURING CPU IDLE MODE

The ADSIDL bit determines if the module stops or continues on Idle. If ADSIDL = 0, the module continues operation on assertion of Idle mode. If ADSIDL = 1, the module stops on Idle.

#### 19.11 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the A/D module to be turned off, and any conversion and sampling sequence is aborted. The values that are in the ADCBUF registers are not modified. The A/D Result register contains unknown data after a Power-on Reset.

#### 19.12 Output Formats

The A/D result is 12 bits wide. The data buffer RAM is also 12 bits wide. The 12-bit data can be read in one of four different formats. The FORM<1:0> bits select the format. Each of the output formats translates to a 16-bit result on the data bus. Write data is always in right-justified (integer) format.

|  | FIGURE 19-5: | A/D OUTPUT DATA FORMATS |

|--|--------------|-------------------------|

|--|--------------|-------------------------|

| RAM Contents:     |     |     |     |     | d11 | d10 | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Read to Bus:      |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Signed Fractional | d11 | d10 | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 | 0   | 0   | 0   | 0   |

|                   |     | 1   |     |     |     | 1   |     |     |     |     |     |     |     |     |     |     |

| Fractional        | d11 | d10 | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 | 0   | 0   | 0   | 0   |

|                   | L   | 1   |     |     |     | I   |     |     |     |     |     |     |     |     |     |     |

| Signed Integer    | d11 | d11 | d11 | d11 | d11 | d10 | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|                   |     | 1   |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Integer           | 0   | 0   | 0   | 0   | d11 | d10 | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|                   | L   | 1   | 1   | 1   | 1   | 1   | 1   |     |     |     | 1   |     |     |     | 1   |     |

### 20.0 SYSTEM INTEGRATION

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

There are several features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving operating modes and offer code protection:

- Oscillator Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Programmable Brown-out Reset (BOR)

- Watchdog Timer (WDT)

- Low-Voltage Detect

- Power-Saving modes (Sleep and Idle)

- Code Protection

- Unit ID Locations

- In-Circuit Serial Programming (ICSP)

dsPIC30F devices have a Watchdog Timer which is permanently enabled via the Configuration bits or can be software controlled. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT) which provides a delay on power-up only, designed to keep the part in Reset while the power supply stabilizes. With these two timers onchip, most applications need no external Reset circuitry.

Sleep mode is designed to offer a very low-current Power-Down mode. The user can wake-up from Sleep through external Reset, Watchdog Timer wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit a wide variety of applications. In the Idle mode, the clock sources are still active but the CPU is shut off. The RC oscillator option saves system cost while the LP crystal option saves power.

#### 20.1 Oscillator System Overview

The dsPIC30F oscillator system has the following modules and features:

- Various external and internal oscillator options as clock sources

- An on-chip PLL to boost internal operating frequency

- A clock switching mechanism between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- Clock Control register (OSCCON)

- Configuration bits for main oscillator selection

Configuration bits determine the clock source upon Power-on Reset (POR) and Brown-out Reset (BOR). Thereafter, the clock source can be changed between permissible clock sources. The OSCCON register controls the clock switching and reflects system clock related status bits.

Table 20-1 provides a summary of the dsPIC30F oscillator operating modes. A simplified diagram of the oscillator system is shown in Figure 20-1.

#### 20.2.3 LP OSCILLATOR CONTROL

Enabling the LP oscillator is controlled with two elements:

- The current oscillator group bits, COSC<2:0>.

- The LPOSCEN bit (OSCCON register).

The LP oscillator is on (even during Sleep mode) if LPOSCEN = 1. The LP oscillator is the device clock if:

- COSC<2:0> = 00 (LP selected as main osc.) and

- LPOSCEN = 1

Keeping the LP oscillator on at all times allows for a fast switch to the 32 kHz system clock for lower power operation. Returning to the faster main oscillator still requires a start-up time

#### 20.2.4 PHASE LOCKED LOOP (PLL)

The PLL multiplies the clock which is generated by the primary oscillator. The PLL is selectable to have either gains of x4, x8 and x16. Input and output frequency ranges are summarized in Table 20-3.

TABLE 20-3: PLL FREQUENCY RANGE

| Fin           | PLL<br>Multiplier | Fout           |

|---------------|-------------------|----------------|

| 4 MHz-10 MHz  | x4                | 16 MHz-40 MHz  |

| 4 MHz-10 MHz  | x8                | 32 MHz-80 MHz  |

| 4 MHz-7.5 MHz | x16               | 64 MHz-120 MHz |

The PLL features a lock output which is asserted when the PLL enters a phase locked state. Should the loop fall out of lock (e.g., due to noise), the lock signal is rescinded. The state of this signal is reflected in the read-only LOCK bit in the OSCCON register.

#### 20.2.5 FAST RC OSCILLATOR (FRC)

The FRC oscillator is a fast (7.37 MHz  $\pm$ 2% nominal) internal RC oscillator. This oscillator is intended to provide reasonable device operating speeds without the use of an external crystal, ceramic resonator, or RC network. The FRC oscillator can be used with the PLL to obtain higher clock frequencies.

The dsPIC30F operates from the FRC oscillator whenever the current oscillator selection control bits in the OSCCON register (OSCCON<14:12>) are set to '001'.

The four-bit field specified by TUN<3:0> (OSCTUN<3:0>) allows the user to tune the internal fast RC oscillator (nominal 7.37 MHz). The user can tune the FRC oscillator within a range of +10.5% (840 kHz) and -12% (960 kHz) in steps of 1.50% around the factory-calibrated setting (see Table 20-4).

| Note: | OSCTUN functionality has been provided      |

|-------|---------------------------------------------|

|       | to help customers compensate for            |

|       | temperature effects on the FRC frequency    |

|       | over a wide range of temperatures. The      |

|       | tuning step size is an approximation and is |

|       | neither characterized nor tested.           |

If OSCCON<14:12> are set to '111' and FPR<4:0> are set to '00101', '00110' or '00111', then a PLL multiplier of 4, 8 or 16 (respectively) is applied.

| Note: | When a                          | a ′ | 16x | PLL   | is | use | эd, | the | FR | RC |  |  |  |

|-------|---------------------------------|-----|-----|-------|----|-----|-----|-----|----|----|--|--|--|

|       | frequen                         | су  | mus | st no | ot | be  | tun | led | to | а  |  |  |  |

|       | frequency greater than 7.5 MHz. |     |     |       |    |     |     |     |    |    |  |  |  |

#### TABLE 20-4: FRC TUNING

| TUN<3:0><br>Bits | FRC Frequency                    |

|------------------|----------------------------------|

| 0111             | +10.5%                           |

| 0110             | +9.0%                            |

| 0101             | +7.5%                            |

| 0100             | +6.0%                            |

| 0011             | +4.5%                            |

| 0010             | +3.0%                            |

| 0001             | +1.5%                            |

| 0000             | Center Frequency (oscillator is  |

|                  | running at calibrated frequency) |

| 1111             | -1.5%                            |

| 1110             | -3.0%                            |

| 1101             | -4.5%                            |

| 1100             | -6.0%                            |

| 1011             | -7.5%                            |

| 1010             | -9.0%                            |

| 1001             | -10.5%                           |

| 1000             | -12.0%                           |

#### 20.2.6 LOW-POWER RC OSCILLATOR (LPRC)

The LPRC oscillator is a component of the Watchdog Timer (WDT) and oscillates at a nominal frequency of 512 kHz. The LPRC oscillator is the clock source for the Power-up Timer (PWRT) circuit, WDT and clock monitor circuits. It may also be used to provide a lowfrequency clock source option for applications where power consumption is critical and timing accuracy is not required.

The LPRC oscillator is always enabled at a Power-on Reset because it is the clock source for the PWRT. After the PWRT expires, the LPRC oscillator remains on if one of the following is TRUE:

- The Fail-Safe Clock Monitor is enabled

- The WDT is enabled

- The LPRC oscillator is selected as the system clock via the COSC<2:0> control bits in the OSCCON register

If one of the above conditions is not true, the LPRC shuts off after the PWRT expires.

| Note 1: | OSC2 pin function is determined by the Primary Oscillator mode selection (FPR<4:0>).                                                  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------|

| 2:      | OSC1 pin cannot be used as an I/O pin<br>even if the secondary oscillator or an<br>internal clock source is selected at all<br>times. |

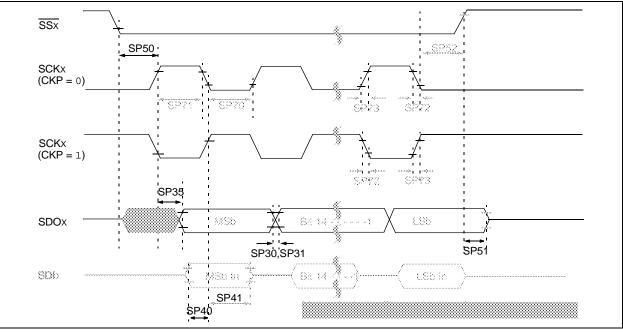

| AC CHARACTERISTICS |                       |                                               | Standard Operating Conditions: 2.5V to 5.5V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                    |     |       |                       |

|--------------------|-----------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|-----------------------|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                 | Min                                                                                                                                                                                                  | Тур <sup>(2)</sup> | Max | Units | Conditions            |

| SP10               | TscL                  | SCKx Output Low Time <sup>(3)</sup>           | Tcy/2                                                                                                                                                                                                | _                  |     | ns    |                       |

| SP11               | TscH                  | SCKx Output High Time <sup>(3)</sup>          | Tcy/2                                                                                                                                                                                                | _                  |     | ns    |                       |

| SP20               | TscF                  | SCKx Output Fall Time <sup>(4)</sup>          | —                                                                                                                                                                                                    | —                  | _   | ns    | See parameter DO32    |

| SP21               | TscR                  | SCKx Output Rise Time <sup>(4)</sup>          | —                                                                                                                                                                                                    | —                  | _   | ns    | See parameter<br>DO31 |

| SP30               | TdoF                  | SDOx Data Output Fall<br>Time <sup>(4)</sup>  | —                                                                                                                                                                                                    | —                  | _   | ns    | See parameter DO32    |

| SP31               | TdoR                  | SDOx Data Output Rise<br>Time <sup>(4)</sup>  | —                                                                                                                                                                                                    | —                  | _   | ns    | See parameter DO31    |

| SP35               | TscH2do,<br>TscL2doV  | SDOx Data Output Valid after<br>SCKx Edge     | —                                                                                                                                                                                                    | —                  | 30  | ns    |                       |

| SP36               | TdoV2sc,<br>TdoV2scL  | SDOx Data Output Setup to<br>First SCKx Edge  | 30                                                                                                                                                                                                   | —                  | _   | ns    |                       |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge | 20                                                                                                                                                                                                   | —                  | _   | ns    |                       |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge     | 20                                                                                                                                                                                                   | —                  | _   | ns    |                       |

#### TABLE 23-31: SPI MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The minimum clock period for SCKx is 100 ns. Therefore, the clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPI pins.

#### FIGURE 23-16: SPI MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

| Transmission93                                         |

|--------------------------------------------------------|

| I <sup>2</sup> C 7-Bit Slave Mode Operation93          |

| Reception                                              |

| Transmission                                           |

| I <sup>2</sup> C Master Mode Operation                 |

|                                                        |

| Baud Rate Generator                                    |

| Clock Arbitration96                                    |

| Multi-Master Communication,                            |

| Bus Collision and Bus Arbitration                      |

| Reception                                              |

| Transmission                                           |

| I <sup>2</sup> C Master Mode Support                   |

| I <sup>2</sup> C Module                                |

|                                                        |

| Addresses                                              |

| Bus Data Timing Requirements                           |

| Master Mode 201                                        |

| Slave Mode204                                          |

| General Call Address Support                           |

| Interrupts                                             |

| IPMI Support                                           |

|                                                        |

| Operating Function Description                         |

| Operation During CPU Sleep and Idle Modes              |

| Pin Configuration91                                    |

| Programmer's Model91                                   |

| Register Map97                                         |

| Registers                                              |

| Slope Control                                          |

| •                                                      |

| Software Controlled Clock Stretching (STREN = 1)94     |

| Various Modes                                          |

| I <sup>2</sup> S Mode Operation129                     |

| Data Justification129                                  |

| Frame and Data Word Length Selection                   |

| Idle Current (IIDLE)                                   |

| In-Circuit Serial Programming (ICSP)                   |

|                                                        |

| Input Capture Module                                   |

| Interrupts82                                           |

| Register Map83                                         |

| Input Capture Operation During Sleep and Idle Modes 82 |

| CPU Idle Mode82                                        |

| CPU Sleep Mode82                                       |

| Input Capture Timing Requirements                      |

| Input Change Notification Module                       |

|                                                        |

| Register Map57                                         |

| Instruction Addressing Modes                           |

| File Register Instructions                             |

| Fundamental Modes Supported                            |

| MAC Instructions                                       |

| MCU Instructions                                       |

| Move and Accumulator Instructions                      |

|                                                        |

| Other Instructions                                     |

| Instruction Set                                        |

| Overview                                               |

| Summary159                                             |

| Internal Clock Timing Examples 183                     |

| Internet Address                                       |

| Interrupt Controller                                   |

|                                                        |

| Register Map                                           |

| Interrupt Priority                                     |

| Traps62                                                |

| Interrupt Sequence63                                   |

| Interrupt Stack Frame63                                |

| Interrupts                                             |

| •                                                      |

| L                                                      |

|                                                        |

| Load Conditions                                        |

| Load Conditions                                        |

| LVDL Characteristics 179 |

|--------------------------|

|--------------------------|

#### М

#### Ν

| NVM        |     |      |

|------------|-----|------|

| Register M | 1ap | . 47 |

#### Ο

| Operating Current (IDD)                       | 4 |

|-----------------------------------------------|---|

| Operating Frequency vs Voltage                | _ |

| dsPIC30FXXXX-20 (Extended) 172                | 2 |

| Oscillator                                    |   |

| Configurations 14                             |   |

| Fail-Safe Clock Monitor 14                    | 6 |

| Fast RC (FRC) 14                              | 5 |

| Initial Clock Source Selection 14             | 4 |

| Low-Power RC (LPRC)14                         | 5 |

| LP Oscillator Control14                       | 5 |

| Phase Locked Loop (PLL)                       |   |

| Start-up Timer (OST) 14                       | 4 |

| Control Registers 14                          |   |

| Operating Modes (Table)142                    | 2 |

| System Overview14                             |   |

| Oscillator Selection 14                       |   |

| Oscillator Start-up Timer                     |   |

| Timing Requirements                           | 7 |

| Output Compare Interrupts                     |   |

| Output Compare Module                         |   |

| Register Map dsPIC30F3014 8                   |   |

| Register Map dsPIC30F4013 8                   |   |

| Timing Requirements                           |   |

| Output Compare Operation During CPU Idle Mode |   |

| Output Compare Sleep Mode Operation           |   |

|                                               | 0 |

| Р                                             |   |

| Packaging Information                     | 211 |

|-------------------------------------------|-----|

| Marking                                   | 211 |

| Peripheral Module Disable (PMD) Registers | 157 |

| Pinout Descriptions                       | 13  |

| POR. See Power-on Reset.                  |     |

| Power Saving Modes                        |     |

| Sleep and Idle                            | 141 |

| Power-Down Current (IPD)                  | 176 |

| Power-Saving Modes                        | 155 |

| Idle                                      | 156 |

|                                           |     |

| CAN Module I/O205<br>CLKOUT and I/O185<br>DCI Module                            |

|---------------------------------------------------------------------------------|

| AC-Link Mode                                                                    |

| External Clock                                                                  |

| Frame Sync, AC-Link Start-Of-Frame                                              |

| Frame Sync, Multichannel Mode124<br>I <sup>2</sup> C Bus Data                   |

| I-C Bus Data<br>Master Mode                                                     |

|                                                                                 |

| Slave Mode203<br>I <sup>2</sup> C Bus Start/Stop Bits                           |

| Master Mode                                                                     |

|                                                                                 |

| Slave Mode                                                                      |

| I <sup>2</sup> S Interface Frame Sync                                           |

| Input Capture (CAPx)                                                            |

| Low-Voltage Detect                                                              |

| OCx/PWM Module                                                                  |

| Oscillator Start-up Timer                                                       |

| Output Compare Module                                                           |

| Power-up Timer                                                                  |

| PWM Output                                                                      |

| Reset                                                                           |

| SPI Module                                                                      |

| Master Mode (CKE = 0)                                                           |

| Master Mode (CKE = 1)                                                           |

| Slave Mode (CKE = 0)                                                            |

| Slave Mode (CKE = 1) 199                                                        |

| Time-out Sequence on Power-up                                                   |

| (MCLR Not Tied to VDD), Case 1                                                  |

| Time-out Sequence on Power-up                                                   |

| (MCLR Not Tied to VDD), Case 2                                                  |

| Time-out Sequence on Power-up                                                   |

| (MCLR Tied to VDD)152                                                           |

| Type A, B and C Timer External Clock                                            |

| Watchdog Timer                                                                  |

| Timing Diagrams and Specifications<br>DC Characteristics - Internal RC Accuracy |

| Timing Diagrams.See Timing Characteristics                                      |

| Timing Requirements                                                             |

| A/D Conversion                                                                  |

| Low-Speed                                                                       |

| Band Gap Start-up Time                                                          |

| Brown-out Reset                                                                 |

| CAN Module I/O                                                                  |

| CLKOUT and I/O                                                                  |

| DCI Module                                                                      |

| AC-Link Mode                                                                    |

| Multichannel, I <sup>2</sup> S Modes                                            |

| External Clock                                                                  |

| l <sup>2</sup> C Bus Data (Master Mode)                                         |

| l <sup>2</sup> C Bus Data (Slave Mode)                                          |

| Input Capture                                                                   |

| Oscillator Start-up Timer                                                       |

| Output Compare Module                                                           |

| Power-up Timer                                                                  |

| Reset                                                                           |

| Simple OCx/PWM Mode                                                             |

| SPI Module                                                                      |

| Master Mode (CKE = 0)                                                           |

| Master Mode (CKE = 1)                                                           |

| Slave Mode (CKE = 0)                                                            |

| Slave Mode (CKE = 1)                                                            |

| Type A Timer External Clock 188                                                 |

| Type B Timer External Clock 189                                                 |

| Type C Timer External Clock | 189 |

|-----------------------------|-----|

| Watchdog Timer              |     |

| Trap Vectors                | 63  |

### U

| UART Module                                 |     |

|---------------------------------------------|-----|

| Address Detect Mode                         | 107 |

| Auto-Baud Support                           | 108 |

| Baud Rate Generator                         | 107 |

| Enabling and Setting Up                     | 105 |

| Framing Error (FERR)                        |     |

| Idle Status                                 |     |

| Loopback Mode                               | 107 |

| Operation During CPU Sleep and Idle Modes   | 108 |

| Overview                                    |     |

| Parity Error (PERR)                         | 107 |

| Receive Break                               |     |

| Receive Buffer (UxRXB)                      | 106 |

| Receive Buffer Overrun Error (OERR Bit)     | 106 |

| Receive Interrupt                           | 106 |

| Receiving Data                              | 106 |

| Receiving in 8-Bit or 9-Bit Data Mode       | 106 |

| Reception Error Handling                    | 106 |

| Transmit Break                              | 106 |

| Transmit Buffer (UxTXB)                     | 105 |

| Transmit Interrupt                          | 106 |

| Transmitting Data                           | 105 |

| Transmitting in 8-Bit Data Mode             | 105 |

| Transmitting in 9-Bit Data Mode             | 105 |

| UART1 Register Map                          | 109 |

| UART2 Register Map                          | 109 |

| UART Operation                              |     |

| Idle Mode                                   | 108 |

| Sleep Mode                                  | 108 |

| Unit ID Locations                           | 141 |

| Universal Asynchronous Receiver Transmitter |     |

| (UART) Module                               | 103 |

| 147                                         |     |

#### W

| Wake-up from Sleep          |          |

|-----------------------------|----------|

| Wake-up from Sleep and Idle |          |

| Watchdog Timer              |          |

| Timing Requirements         | 187      |

| Watchdog Timer (WDT)        | 141, 155 |

| Enabling and Disabling      | 155      |

| Operation                   | 155      |

| WWW Address                 | 225      |

| WWW, On-Line Support        |          |