Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| etails                   |                                                                                |

|--------------------------|--------------------------------------------------------------------------------|

| roduct Status            | Active                                                                         |

| ore Processor            | dsPIC                                                                          |

| ore Size                 | 16-Bit                                                                         |

| peed                     | 30 MIPs                                                                        |

| onnectivity              | CANbus, I <sup>2</sup> C, SPI, UART/USART                                      |

| eripherals               | AC'97, Brown-out Detect/Reset, I <sup>2</sup> S, POR, PWM, WDT                 |

| umber of I/O             | 30                                                                             |

| ogram Memory Size        | 48KB (16K x 24)                                                                |

| ogram Memory Type        | FLASH                                                                          |

| PROM Size                | 1K x 8                                                                         |

| M Size                   | 2K x 8                                                                         |

| ltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                    |

| ta Converters            | A/D 13x12b                                                                     |

| scillator Type           | Internal                                                                       |

| erating Temperature      | -40°C ~ 85°C (TA)                                                              |

| ounting Type             | Surface Mount                                                                  |

| ickage / Case            | 44-VQFN Exposed Pad                                                            |

| ipplier Device Package   | 44-QFN (8x8)                                                                   |

| rchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f4013t-30i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

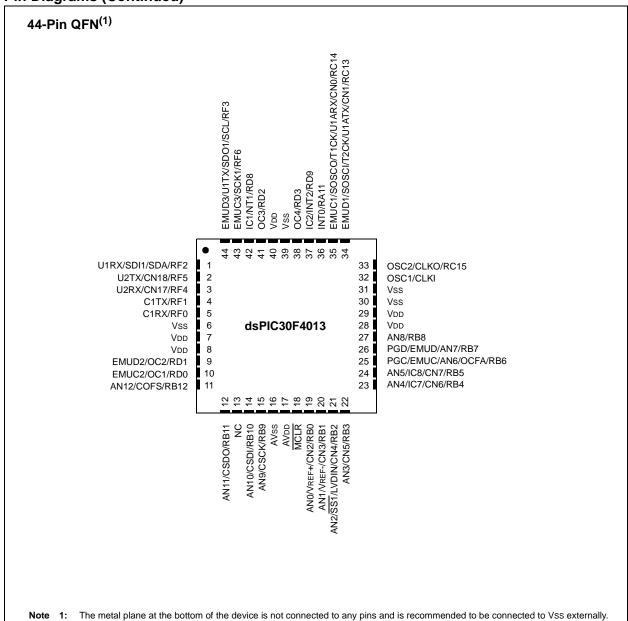

### Pin Diagrams (Continued)

Table 1-1 provides a brief description of device I/O pinouts and the functions that may be multiplexed to a port pin. Multiple functions may exist on one port pin. When multiplexing occurs, the peripheral module's functional requirements may force an override of the data direction of the port pin.

**PINOUT I/O DESCRIPTIONS TABLE 1-1:**

| IADLE I-I.            | FINOU       | I I/O DES      | 3CKIPTIONS                                                                                                                                                                                                       |  |  |  |

|-----------------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name              | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                                      |  |  |  |

| AN0-AN12              | I           | Analog         | Analog input channels. AN6 and AN7 are also used for device programming data and clock inputs, respectively.                                                                                                     |  |  |  |

| AVDD                  | Р           | Р              | Positive supply for analog module. This pin must be connected at all times.                                                                                                                                      |  |  |  |

| AVss                  | Р           | Р              | Ground reference for analog module. This pin must be connected at all times.                                                                                                                                     |  |  |  |

| CLKI                  | ı           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.  Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. |  |  |  |

| CLKO                  | 0           |                | Always associated with OSC2 pin function.                                                                                                                                                                        |  |  |  |

| CN0-CN7,<br>CN17-CN18 | I           | ST             | Input change notification inputs. Can be software programmed for internal weak pull-ups on all inputs.                                                                                                           |  |  |  |

| COFS                  | I/O         | ST             | Data Converter Interface Frame Synchronization pin.                                                                                                                                                              |  |  |  |

| CSCK                  | I/O         | ST             | Data Converter Interface Serial Clock input/output pin.                                                                                                                                                          |  |  |  |

| CSDI                  | I           | ST             | Data Converter Interface Serial data input pin.                                                                                                                                                                  |  |  |  |

| CSDO                  | 0           | _              | Data Converter Interface Serial data output pin.                                                                                                                                                                 |  |  |  |

| C1RX                  | I           | ST             | CAN1 bus receive pin.                                                                                                                                                                                            |  |  |  |

| C1TX                  | 0           | _              | CAN1 bus transmit pin.                                                                                                                                                                                           |  |  |  |

| EMUD                  | I/O         | ST             | ICD Primary Communication Channel data input/output pin.                                                                                                                                                         |  |  |  |

| EMUC                  | I/O         | ST             | ICD Primary Communication Channel clock input/output pin.                                                                                                                                                        |  |  |  |

| EMUD1<br>EMUC1        | I/O<br>I/O  | ST<br>ST       | ICD Secondary Communication Channel data input/output pin. ICD Secondary Communication Channel clock input/output pin.                                                                                           |  |  |  |

| EMUD2                 | 1/0         | ST             | ICD Secondary Communication Channel data input/output pin.                                                                                                                                                       |  |  |  |

| EMUC2                 | 1/0         | ST             | ICD Tertiary Communication Channel clock input/output pin.                                                                                                                                                       |  |  |  |

| EMUD3                 | I/O         | ST             | ICD Quaternary Communication Channel data input/output pin.                                                                                                                                                      |  |  |  |

| EMUC3                 | I/O         | ST             | ICD Quaternary Communication Channel clock input/output pin.                                                                                                                                                     |  |  |  |

| IC1, IC2, IC7,<br>IC8 | I           | ST             | Capture inputs 1,2, 7 and 8.                                                                                                                                                                                     |  |  |  |

| INT0                  | ı           | ST             | External interrupt 0.                                                                                                                                                                                            |  |  |  |

| INT1                  | ı           | ST             | External interrupt 1.                                                                                                                                                                                            |  |  |  |

| INT2                  | - 1         | ST             | External interrupt 2.                                                                                                                                                                                            |  |  |  |

| LVDIN                 | I           | Analog         | Low-Voltage Detect Reference Voltage Input pin.                                                                                                                                                                  |  |  |  |

| MCLR                  | I/P         | ST             | Master Clear (Reset) input or programming voltage input. This pin is an active-low Reset to the device.                                                                                                          |  |  |  |

| OCFA                  | I           | ST             | Compare Fault A input (for Compare channels 1, 2, 3 and 4).                                                                                                                                                      |  |  |  |

| OC1-OC4               | 0           | _              | Compare outputs 1 through 4.                                                                                                                                                                                     |  |  |  |

| OSC1                  | I           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                                                  |  |  |  |

| OSC2                  | I/O         | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                                                         |  |  |  |

| PGD<br>PGC            | I/O<br>I    | ST<br>ST       | In-Circuit Serial Programming data input/output pin. In-Circuit Serial Programming clock input pin.                                                                                                              |  |  |  |

**Legend:** CMOS = CMOS compatible input or output Analog = Analog input

= Schmitt Trigger input with CMOS levels ST 0 = Output

Р = Input = Power

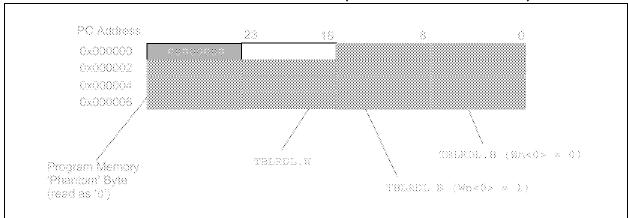

# 3.1.1 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

This architecture fetches 24-bit wide program memory. Consequently, instructions are always aligned. However, as the architecture is modified Harvard, data can also be present in program space.

There are two methods by which program space can be accessed: via special table instructions, or through the remapping of a 16K word program space page into the upper half of data space (see Section 3.1.2 "Data Access from Program Memory Using Program Space Visibility"). The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lsw of any address within program space, without going through data space. The TBLRDH and TBLWTH instructions are the only method whereby the upper 8 bits of a program space word can be accessed as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit word-wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word, and TBLRDH and TBLWTH access the space which contains the MS Data Byte.

Figure 3-3 shows how the EA is created for table operations and data space accesses (PSV = 1). Here, P<23:0> refers to a program space word, whereas D<15:0> refers to a data space word.

A set of table instructions are provided to move byte or word-sized data to and from program space. (See Figure 3-4 and Figure 3-5.)

- TBLRDL: Table Read Low Word: Read the lsw of the program address; P<15:0> maps to D<15:0>.

- Byte: Read one of the LSBs of the program address:

- P<7:0> maps to the destination byte when byte select = 0:

- P<15:8> maps to the destination byte when byte select = 1.

- 2. TBLWTL: Table Write Low (refer to **Section 5.0** "**Flash Program Memory**" for details on Flash programming)

- 3. TBLRDH: Table Read High

- *Word:* Read the most significant word (msw) of the program address; P<23:16> maps to D<7:0>; D<15:8> will always be = 0.

- Byte: Read one of the MSBs of the program address;

- P<23:16> maps to the destination byte when byte select = 0:

- The destination byte will always be = 0 when byte select = 1.

- TBLWTH: Table Write High (refer to Section 5.0

"Flash Program Memory" for details on Flash

Programming)

### 4.1.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note:

For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (register offset) field is shared between both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- · Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- · Register Indirect Pre-Modified

- Register Indirect with Register Offset (Indexed)

- · Register Indirect with Literal Offset

- 8-bit Literal

- 16-bit Literal

Note:

Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.1.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY.N, MOVSAC and MSC), also referred to as MAC instructions, utilize a simplified set of addressing modes to allow the user to effectively manipulate the Data Pointers through register indirect tables.

The two source operand prefetch registers must be a member of the set {W8, W9, W10, W11}. For data reads, W8 and W9 is always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must, therefore, be valid addresses within X data space for W8 and W9 and Y data space for W10 and W11.

Note:

Register Indirect with Register Offset addressing is only available for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the MAC class of instructions:

- · Register Indirect

- · Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- · Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.1.5 OTHER INSTRUCTIONS

Besides the various addressing modes outlined above, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

#### 4.2 Modulo Addressing

Modulo Addressing is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either data or program space (since the data pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into program space) and Y data spaces. Modulo Addressing can operate on any W register pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can only be configured to operate in one direction, as there are certain restrictions on the buffer start address (for incrementing buffers), or end address (for decrementing buffers) based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-2 length. As these buffers satisfy the start and end address criteria, they may operate in a Bidirectional mode (i.e., address boundary checks are performed on both the lower and upper address boundaries).

#### 7.3 Input Change Notification Module

The input change notification module provides the dsPIC30F devices the ability to generate interrupt requests to the processor, in response to a Change-Of-State (COS) on selected input pins. This module is capable of detecting input Change-Of-States, even in Sleep mode, when the clocks are disabled. There are up to 10 external signals (CN0 through CN9, CN17 and CN18) that may be selected (enabled) for generating an interrupt request on a Change-Of-State.

#### 8.1 Interrupt Priority

The user-assignable interrupt priority (IP<2:0>) bits for each individual interrupt source are located in the 3 LSbs of each nibble within the IPCx register(s). Bit 3 of each nibble is not used and is read as a '0'. These bits define the priority level assigned to a particular interrupt by the user.

Note: The user-assignable priority levels start at 0 as the lowest priority and Level 7 as the highest priority.

Since more than one interrupt request source may be assigned to a specific user-assigned priority level, a means is provided to assign priority within a given level. This method is called "Natural Order Priority" and is final.

Natural Order Priority is determined by the position of an interrupt in the vector table, and only affects interrupt operation when multiple interrupts with the same user-assigned priority become pending at the same time.

Table 8-1 and Table 8-2 list the interrupt numbers, corresponding interrupt sources and associated vector numbers for the dsPIC30F3014 and dsPIC30F4013 devices, respectively.

- **Note 1:** The natural order priority scheme has 0 as the highest priority and 53 as the lowest priority.

- **2:** The natural order priority number is the same as the INT number.

The ability for the user to assign every interrupt to one of seven priority levels means that the user can assign a very high overall priority level to an interrupt with a low natural order priority. For example, the PLVD (Programmable Low-Voltage Detect) can be given a priority of 7. The INTO (External Interrupt 0) may be assigned to priority Level 1, thus giving it a very low effective priority.

TABLE 8-1: dsPIC30F3014 INTERRUPT VECTOR TABLE

| INT<br>Number | Vector<br>Number | Interrupt Source                         |

|---------------|------------------|------------------------------------------|

|               | Highest          | Natural Order Priority                   |

| 0             | 8                | INT0 – External Interrupt 0              |

| 1             | 9                | IC1 – Input Capture 1                    |

| 2             | 10               | OC1 – Output Compare 1                   |

| 3             | 11               | T1 – Timer1                              |

| 4             | 12               | IC2 – Input Capture 2                    |

| 5             | 13               | OC2 – Output Compare 2                   |

| 6             | 14               | T2 – Timer2                              |

| 7             | 15               | T3 – Timer3                              |

| 8             | 16               | SPI1                                     |

| 9             | 17               | U1RX – UART1 Receiver                    |

| 10            | 18               | U1TX – UART1 Transmitter                 |

| 11            | 19               | ADC – ADC Convert Done                   |

| 12            | 20               | NVM – NVM Write Complete                 |

| 13            | 21               | SI2C – I <sup>2</sup> C™ Slave Interrupt |

| 14            | 22               | MI2C – I <sup>2</sup> C Master Interrupt |

| 15            | 23               | Input Change Interrupt                   |

| 16            | 24               | INT1 – External Interrupt 1              |

| 17-22         | 25-30            | Reserved                                 |

| 23            | 31               | INT2 – External Interrupt 2              |

| 24            | 32               | U2RX – UART2 Receiver                    |

| 25            | 33               | U2TX – UART2 Transmitter                 |

| 26            | 34               | Reserved                                 |

| 27            | 35               | C1 – Combined IRQ for CAN1               |

| 28-41         | 36-49            | Reserved                                 |

| 42            | 50               | LVD – Low-Voltage Detect                 |

| 43-53         | 51-61            | Reserved                                 |

|               | Lowest           | Natural Order Priority                   |

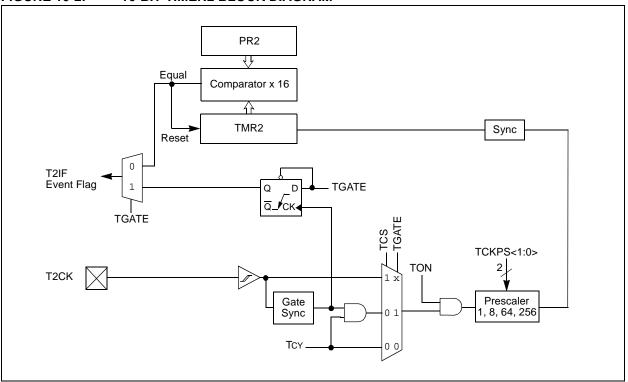

FIGURE 10-2: 16-BIT TIMER2 BLOCK DIAGRAM

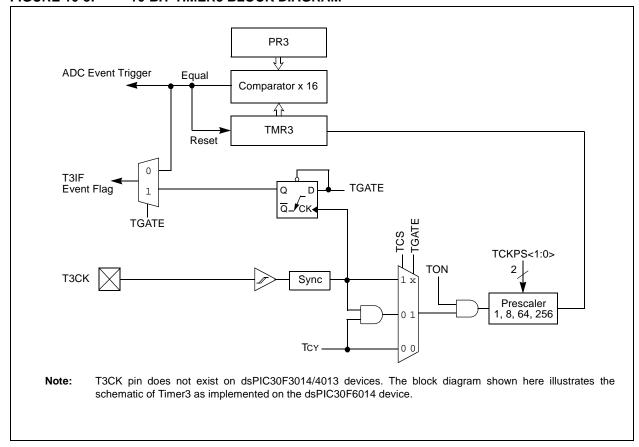

FIGURE 10-3: 16-BIT TIMER3 BLOCK DIAGRAM

#### 16.5.2 FRAMING ERROR (FERR)

The FERR bit (UxSTA<2>) is set if a '0' is detected instead of a Stop bit. If two Stop bits are selected, both Stop bits must be '1'; otherwise, FERR is set. The readonly FERR bit is buffered along with the received data; it is cleared on any Reset.

#### 16.5.3 PARITY ERROR (PERR)

The PERR bit (UxSTA<3>) is set if the parity of the received word is incorrect. This error bit is applicable only if a Parity mode (odd or even) is selected. The read-only PERR bit is buffered along with the received data bytes; it is cleared on any Reset.

#### 16.5.4 IDLE STATUS

When the receiver is active (i.e., between the initial detection of the Start bit and the completion of the Stop bit), the RIDLE bit (UxSTA<4>) is '0'. Between the completion of the Stop bit and detection of the next Start bit, the RIDLE bit is '1', indicating that the UART is Idle.

#### 16.5.5 RECEIVE BREAK

The receiver counts and expects a certain number of bit times based on the values programmed in the PDSEL (UxMODE<2:1>) and STSEL (UxMODE<0>) bits.

If the break is longer than 13 bit times, the reception is considered complete after the number of bit times specified by PDSEL and STSEL. The URXDA bit is set, FERR is set, zeros are loaded into the receive FIFO, interrupts are generated if appropriate, and the RIDLE bit is set.

When the module receives a long Break signal and the receiver has detected the Start bit, the data bits and the invalid Stop bit (which sets the FERR), the receiver must wait for a valid Stop bit before looking for the next Start bit. It cannot assume that the Break condition on the line is the next Start bit.

Break is regarded as a character containing all '0's with the FERR bit set. The Break character is loaded into the buffer. No further reception can occur until a Stop bit is received. Note that RIDLE goes high when the Stop bit has not yet been received.

#### 16.6 Address Detect Mode

Setting the ADDEN bit (UxSTA<5>) enables this special mode in which a 9th bit (URX8) value of '1' identifies the received word as an address, rather than data. This mode is only applicable for 9-bit data communication. The URXISEL control bit does not have any impact on interrupt generation in this mode since an interrupt (if enabled) is generated every time the received word has the 9th bit set.

#### 16.7 Loopback Mode

Setting the LPBACK bit enables this special mode in which the UxTX pin is internally connected to the UxRX pin. When configured for the Loopback mode, the UxRX pin is disconnected from the internal UART receive logic. However, the UxTX pin still functions as in a normal operation.

To select this mode:

- a) Configure UART for desired mode of operation.

- b) Set LPBACK = 1 to enable Loopback mode.

- c) Enable transmission as defined in Section 16.3 "Transmitting Data".

#### 16.8 Baud Rate Generator

The UART has a 16-bit Baud Rate Generator to allow maximum flexibility in baud rate generation. The Baud Rate Generator register (UxBRG) is readable and writable. The baud rate is computed as follows:

BRG = 16-bit value held in UxBRG register (0 through 65535)

FCY = Instruction Clock Rate (1/Tcy)

The Baud Rate is given by Equation 16-1.

#### **EQUATION 16-1: BAUD RATE**

Baud Rate = FCY/(16\*(BRG+1))

Therefore, the maximum baud rate possible is:

FCY/16 (if BRG = 0),

and the minimum baud rate possible is:

Fcy/(16 \* 65536).

With a full 16-bit Baud Rate Generator at 30 MIPS operation, the minimum baud rate achievable is 28.5 bps.

#### 20.3 Oscillator Control Registers

The oscillators are controlled with two SFRs, OSCCON and OSCTUN and one Configuration register, FOSC.

Note: The description of the OSCCON and OSCTUN SFRs, as well as the FOSC Configuration register provided in this section are applicable only to the dsPIC30F3014 and dsPIC30F4013 devices in the dsPIC30F product family.

#### REGISTER 20-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0    | R-y | R-y       | R-y | U-0 | R/W-y | R/W-y     | R/W-y |

|--------|-----|-----------|-----|-----|-------|-----------|-------|

| _      |     | COSC<2:0> |     |     |       | NOSC<2:0> |       |

| bit 15 |     |           |     |     |       |           | bit 8 |

| R/W-0 | R/W-0 | R-0  | U-0 | R/W-0 | U-0 | R/W-0   | R/W-0 |

|-------|-------|------|-----|-------|-----|---------|-------|

| POST  | <1:0> | LOCK | _   | CF    | _   | LPOSCEN | OSWEN |

| bit 7 |       |      |     |       |     |         | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 **Unimplemented:** Read as '0'

bit 14-12 COSC<2:0>: Current Oscillator Group Selection bits (read-only)

111 = PLL oscillator; PLL source selected by FPR<4:0> bits

011 = External oscillator; OSC1/OSC2 pins; external oscillator configuration selected by FPR<4:0> bits

010 = LPRC internal low-power RC

001 = FRC internal fast RC

000 = LP crystal oscillator; SOSCI/SOSCO pins

Set to FOS<2:0> values on POR or BOR. Loaded with NOSC<2:0> at the completion of a successful clock switch. Set to FRC value when FSCM detects a failure and switches clock to FRC.

bit 11 Unimplemented: Read as '0'

bit 10-8 NOSC<2:0>: New Oscillator Group Selection bits

111 = PLL Oscillator; PLL source selected by FPR<4:0> bits

011 = External oscillator; OSC1/OSC2 pins; external oscillator configuration selected by FPR<4:0> bits

010 = LPRC internal low-power RC

001 = FRC internal fast RC

000 = LP crystal oscillator; SOSCI/SOSCO pins

Set to FOS<2:0> values on POR or BOR.

bit 7-6 **POST<1:0>:** Oscillator Postscaler Selection bits

11 = Oscillator postscaler divides clock by 64

10 = Oscillator postscaler divides clock by 16

01 = Oscillator postscaler divides clock by 4

00 = Oscillator postscaler does not alter clock

TABLE 23-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

| DC CHARACTERISTICS |        |                                          | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                    |         |       |                                            |

|--------------------|--------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------|-------|--------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                           | Min                                                                                                                                                                                                                                              | Typ <sup>(1)</sup> | Max     | Units | Conditions                                 |

|                    | VIL    | Input Low Voltage <sup>(2)</sup>         |                                                                                                                                                                                                                                                  |                    |         |       |                                            |

| DI10               |        | I/O Pins:                                | .,                                                                                                                                                                                                                                               |                    |         |       |                                            |

|                    |        | with Schmitt Trigger Buffer              | Vss                                                                                                                                                                                                                                              | _                  | 0.2 VDD | V     |                                            |

| DI15               |        | MCLR                                     | Vss                                                                                                                                                                                                                                              |                    | 0.2 VDD | V     |                                            |

| DI16               |        | OSC1 (in XT, HS and LP modes)            | Vss                                                                                                                                                                                                                                              | _                  | 0.2 VDD | V     |                                            |

| DI17               |        | OSC1 (in RC mode) <sup>(3)</sup>         | Vss                                                                                                                                                                                                                                              | _                  | 0.3 VDD | V     |                                            |

| DI18               |        | SDA, SCL                                 | Vss                                                                                                                                                                                                                                              | _                  | 0.3 VDD | V     | SM bus disabled                            |

| DI19               |        | SDA, SCL                                 | Vss                                                                                                                                                                                                                                              | _                  | 8.0     | V     | SM bus enabled                             |

|                    | VIH    | Input High Voltage <sup>(2)</sup>        |                                                                                                                                                                                                                                                  |                    |         |       |                                            |

| DI20               |        | I/O Pins:                                |                                                                                                                                                                                                                                                  |                    |         |       |                                            |

|                    |        | with Schmitt Trigger Buffer              | 0.8 VDD                                                                                                                                                                                                                                          | _                  | Vdd     | V     |                                            |

| DI25               |        | MCLR                                     | 0.8 VDD                                                                                                                                                                                                                                          | _                  | Vdd     | V     |                                            |

| DI26               |        | OSC1 (in XT, HS and LP modes)            | 0.7 VDD                                                                                                                                                                                                                                          | _                  | Vdd     | V     |                                            |

| DI27               |        | OSC1 (in RC mode) <sup>(3)</sup>         | 0.9 Vdd                                                                                                                                                                                                                                          | _                  | Vdd     | V     |                                            |

| DI28               |        | SDA, SCL                                 | 0.7 Vdd                                                                                                                                                                                                                                          | _                  | Vdd     | V     | SM bus disabled                            |

| DI29               |        | SDA, SCL                                 | 2.1                                                                                                                                                                                                                                              | _                  | Vdd     | ٧     | SM bus enabled                             |

|                    | ICNPU  | CNxx Pull-up Current <sup>(2)</sup>      |                                                                                                                                                                                                                                                  |                    |         |       |                                            |

| DI30               |        |                                          | 50                                                                                                                                                                                                                                               | 250                | 400     | μΑ    | VDD = 5V, VPIN = VSS                       |

|                    | lı∟    | Input Leakage Current <sup>(2,4,5)</sup> |                                                                                                                                                                                                                                                  |                    |         |       |                                            |

| DI50               |        | I/O Ports                                | _                                                                                                                                                                                                                                                | 0.01               | ±1      | μΑ    | Vss ≤ Vpin ≤ Vdd,<br>Pin at high-impedance |

| DI51               |        | Analog Input Pins                        | _                                                                                                                                                                                                                                                | 0.50               | _       | μΑ    | Vss ≤ Vpin ≤ Vdd,<br>Pin at high-impedance |

| DI55               |        | MCLR                                     | _                                                                                                                                                                                                                                                | 0.05               | ±5      | μΑ    | $Vss \leq Vpin \leq Vdd$                   |

| DI56               |        | OSC1                                     | _                                                                                                                                                                                                                                                | 0.05               | ±5      | μΑ    | VSS ≤ VPIN ≤ VDD, XT, HS and LP Osc mode   |

Note 1: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **2:** These parameters are characterized but not tested in manufacturing.

- **3:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the dsPIC30F device be driven with an external clock while in RC mode.

- **4:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 5: Negative current is defined as current sourced by the pin.

TABLE 23-9: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

| DC CHARACTERISTICS |        |                                                        | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                    |      |       |                                                                        |

|--------------------|--------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|-------|------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                         | Min                                                                                                                                                                                                                                              | Typ <sup>(1)</sup> | Max  | Units | Conditions                                                             |

|                    | VOL    | Output Low Voltage <sup>(2)</sup>                      |                                                                                                                                                                                                                                                  |                    |      |       |                                                                        |

| DO10               |        | I/O Ports                                              | _                                                                                                                                                                                                                                                | _                  | 0.6  | V     | IOL = 8.5  mA, VDD = 5V                                                |

|                    |        |                                                        | _                                                                                                                                                                                                                                                | _                  | 0.15 | V     | IOL = 2.0  mA, VDD = 3V                                                |

| DO16               |        | OSC2/CLKO                                              | _                                                                                                                                                                                                                                                | _                  | 0.6  | V     | IOL = 1.6 mA, VDD = 5V                                                 |

|                    |        | (RC or EC Oscillator mode)                             | _                                                                                                                                                                                                                                                | _                  | 0.72 | V     | IOL = 2.0  mA, VDD = 3V                                                |

|                    | Voн    | Output High Voltage <sup>(2)</sup>                     |                                                                                                                                                                                                                                                  |                    |      |       |                                                                        |

| DO20               |        | I/O Ports                                              | VDD - 0.7                                                                                                                                                                                                                                        | _                  | _    | V     | IOH = -3.0 mA, VDD = 5V                                                |

|                    |        |                                                        | VDD - 0.2                                                                                                                                                                                                                                        | _                  | _    | V     | IOH = -2.0 mA, VDD = 3V                                                |

| DO26               |        | OSC2/CLKO                                              | VDD - 0.7                                                                                                                                                                                                                                        | _                  | _    | V     | IOH = -1.3 mA, VDD = 5V                                                |

|                    |        | (RC or EC Oscillator mode)                             | VDD - 0.1                                                                                                                                                                                                                                        | _                  |      | V     | IOH = -2.0 mA, VDD = 3V                                                |

|                    |        | Capacitive Loading Specs on Output Pins <sup>(2)</sup> |                                                                                                                                                                                                                                                  |                    |      |       |                                                                        |

| DO50               | Cosc2  | OSC2/SOSC2 Pin                                         | _                                                                                                                                                                                                                                                | _                  | 15   | pF    | In XTL, XT, HS and LP modes when external clock is used to drive OSC1. |

| DO56               | Cio    | All I/O Pins and OSC2                                  | _                                                                                                                                                                                                                                                | _                  | 50   | pF    | RC or EC Oscillator mode                                               |

| DO58               | Св     | SCL, SDA                                               | _                                                                                                                                                                                                                                                | —                  | 400  | pF    | In I <sup>2</sup> C mode                                               |

**Note 1:** Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: These parameters are characterized but not tested in manufacturing.

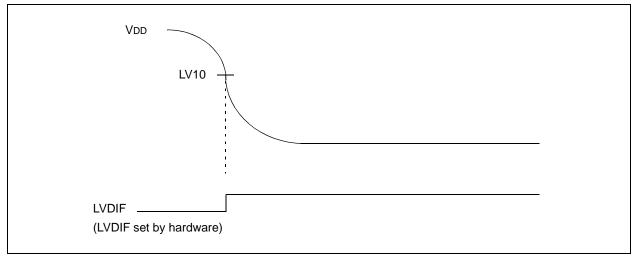

FIGURE 23-1: LOW-VOLTAGE DETECT CHARACTERISTICS

TABLE 23-10: ELECTRICAL CHARACTERISTICS: LVDL

|         |                    | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated) |                 |        |                                  |                 |          |             |

|---------|--------------------|-----------------------------------------------------------------------|-----------------|--------|----------------------------------|-----------------|----------|-------------|

| DC CHAI | DC CHARACTERISTICS |                                                                       | Operating tempe | rature | -40°C ≤ TA ≤ +85°C for Industria |                 |          | Industrial  |

|         |                    |                                                                       |                 |        | -40°C ≤                          | TA ≤ <b>+</b> 1 | 125°C fo | or Extended |

|         |                    |                                                                       |                 |        |                                  |                 |          |             |

| Param<br>No. | Symbol | Characteristic <sup>(1)</sup>                 |                            | Min  | Тур | Max  | Units | Conditions |

|--------------|--------|-----------------------------------------------|----------------------------|------|-----|------|-------|------------|

| LV10         | VPLVD  | LVDL Voltage on VDD<br>Transition High-to-Low | LVDL = 0000 <sup>(2)</sup> |      |     | _    | V     |            |

|              |        |                                               | LVDL = 0001 <sup>(2)</sup> | _    | _   | _    | V     |            |

|              |        |                                               | LVDL = 0010 <sup>(2)</sup> |      |     | _    | V     |            |

|              |        |                                               | LVDL = 0011 <sup>(2)</sup> |      |     | _    | V     |            |

|              |        |                                               | LVDL = 0100                | 2.50 | _   | 2.65 | V     |            |

|              |        |                                               | LVDL = 0101                | 2.70 | _   | 2.86 | V     |            |

|              |        |                                               | LVDL = 0110                | 2.80 | _   | 2.97 | V     |            |

|              |        |                                               | LVDL = 0111                | 3.00 | _   | 3.18 | V     |            |

|              |        |                                               | LVDL = 1000                | 3.30 | _   | 3.50 | V     |            |

|              |        |                                               | LVDL = 1001                | 3.50 | _   | 3.71 | V     |            |

|              |        |                                               | LVDL = 1010                | 3.60 | _   | 3.82 | ٧     |            |

|              |        |                                               | LVDL = 1011                | 3.80 | _   | 4.03 | ٧     |            |

|              |        |                                               | LVDL = 1100                | 4.00 | _   | 4.24 | V     |            |

|              |        |                                               | LVDL = 1101                | 4.20 | _   | 4.45 | V     |            |

|              |        |                                               | LVDL = 1110                | 4.50 | _   | 4.77 | V     |            |

| LV15         | VLVDIN | External LVD Input Pin                        | LVDL = 1111                | _    | _   | _    | V     |            |

|              |        | Threshold Voltage                             |                            |      |     |      |       |            |

Note 1: These parameters are characterized but not tested in manufacturing.

2: These values not in usable operating range.

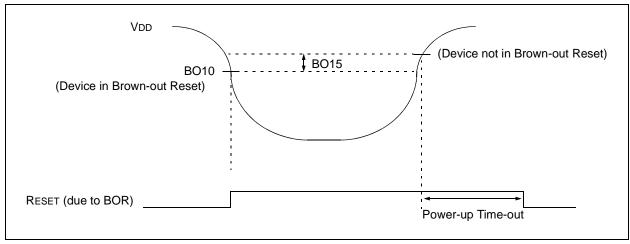

FIGURE 23-2: BROWN-OUT RESET CHARACTERISTICS

#### TABLE 23-13: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated) |

|--------------------|-----------------------------------------------------------------------|

| AC CHARACTERISTICS | Operating temperature -40°C ≤ TA ≤ +85°C for Industrial               |

|                    | -40°C ≤ TA ≤ +125°C for Extended                                      |

|                    | Operating voltage VDD range as described in Table 23-1.               |

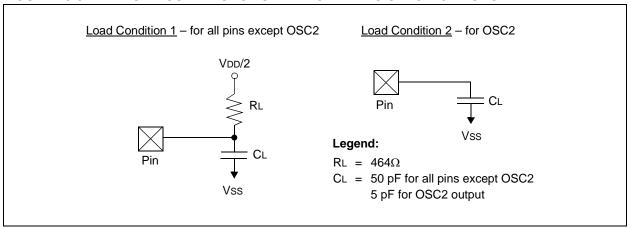

#### FIGURE 23-3: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

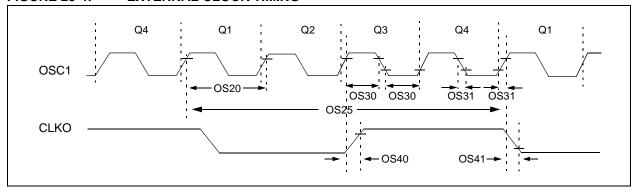

#### FIGURE 23-4: EXTERNAL CLOCK TIMING

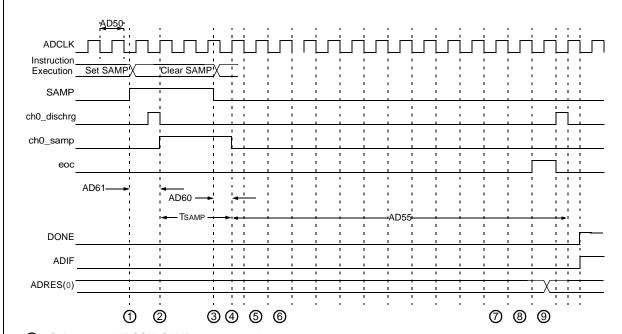

FIGURE 23-23: 12-BIT A/D CONVERSION TIMING CHARACTERISTICS (ASAM = 0, SSRC = 000)

- 1 Software sets ADCON. SAMP to start sampling.

- ② Sampling starts after discharge period.

TSAMP is described in **Section 18. "12-bit A/D Converter"** of the *dsPIC30F Family Reference Manual* (DS70046).

- 3 Software clears ADCON. SAMP to start conversion.

- (4) Sampling ends, conversion sequence starts.

- (5) Convert bit 11.

- 6 Convert bit 10.

- 7 Convert bit 1.

- (8) Convert bit 0.

- (9) One TAD for end of conversion.

### **Revision G (November 2010)**

This revision includes minor typographical and formatting changes throughout the data sheet text.

The major changes are referenced by their respective section in Table A-1.

TABLE A-1: MAJOR SECTION UPDATES

| Section Name                                          | Update Description                                                                                                                                                        |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-Bit Digital Signal Controllers" | Added Note 1 to all QFN pin diagrams (see "Pin Diagrams").                                                                                                                |

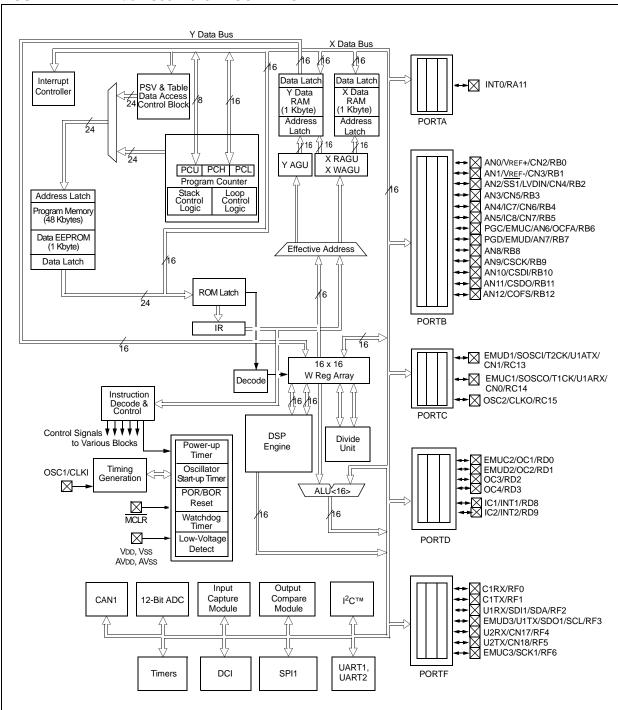

| Section 1.0 "Device Overview"                         | Removed the "DCI" peripheral block from the dsPIC30F3014 Block Diagram (see Figure 1-1).                                                                                  |

|                                                       | Updated the Pinout I/O Descriptions for AVDD and AVSS (see Table 1-1).                                                                                                    |

| Section 20.0 "System Integration"                     | Added a note on OSCTUN functionality in Section 20.2.5 "Fast RC Oscillator (FRC)".                                                                                        |

|                                                       | Updated the operating frequencies for the following Oscillator Operating Modes (see Table 20-1):                                                                          |

|                                                       | <ul> <li>XTL</li> <li>XT w/PLL 16x</li> <li>HS/2 w/PLL 4x, 8x, and 16x</li> <li>HS/3 w/PLL 4x, 8x, and 16x</li> <li>EC w/PLL 4x, 8x, and 16x</li> </ul>                   |

| Section 23.0 "Electrical Characteristics"             | Updated the maximum value for parameter DI19 and the minimum value for parameter DI29 in the I/O Pin Input Specifications (see Table 23-8).                               |

|                                                       | Removed parameter D136 and updated the minimum, typical, maximum, and conditions for parameters D122 and D134 in the Program and EEPROM specifications (see Table 23-12). |

| Transmission                                           | 93  | LVDL Characteristics                               | . 179 |

|--------------------------------------------------------|-----|----------------------------------------------------|-------|

| I <sup>2</sup> C 7-Bit Slave Mode Operation            | 93  | 1.4                                                |       |

| Reception                                              | 93  | M                                                  |       |

| Transmission                                           |     | Memory Organization                                |       |

| I <sup>2</sup> C Master Mode Operation                 | 95  | Core Register Map                                  |       |

| Baud Rate Generator                                    | 96  | Microchip Internet Web Site                        | . 225 |

| Clock Arbitration                                      | 96  | Modes of Operation                                 |       |

| Multi-Master Communication,                            |     | Disable                                            |       |

| Bus Collision and Bus Arbitration                      |     | Initialization                                     |       |

| Reception                                              |     | Listen All Messages                                |       |

| Transmission                                           |     | Listen Only                                        |       |

| I <sup>2</sup> C Master Mode Support                   |     | Loopback                                           |       |

| I <sup>2</sup> C Module                                |     | Normal Operation                                   |       |

| Addresses                                              | 93  | Modulo Addressing                                  |       |

| Bus Data Timing Requirements                           |     | Applicability                                      |       |

| Master Mode                                            |     | Incrementing Buffer Operation Example              |       |

| Slave Mode                                             |     | Start and End Address                              |       |

| General Call Address Support                           |     | W Address Register Selection                       |       |

| Interrupts                                             |     | MPLAB ASM30 Assembler, Linker, Librarian           |       |

| IPMI Support                                           |     | MPLAB Integrated Development Environment Software. |       |

| Operating Function Description                         |     | MPLAB PM3 Device Programmer                        |       |

| Operation During CPU Sleep and Idle Mode               |     | MPLAB REAL ICE In-Circuit Emulator System          |       |

| Pin Configuration                                      |     | MPLINK Object Linker/MPLIB Object Librarian        | . 168 |

| Programmer's Model                                     |     | N                                                  |       |

| Register Map                                           |     | NVM                                                |       |

| Registers                                              |     | Register Map                                       | 47    |

| Slope Control                                          |     | Register Map                                       | 41    |

| Software Controlled Clock Stretching (STR              | ,   | 0                                                  |       |

| Various Modes                                          |     | Operating Current (IDD)                            | 17/   |

| I <sup>2</sup> S Mode Operation                        |     | Operating Frequency vs Voltage                     | . 177 |

| Data Justification                                     |     | dsPIC30FXXXX-20 (Extended)                         | 172   |

| Frame and Data Word Length Selection                   |     | Oscillator                                         | . 112 |

| Idle Current (IDLE)                                    |     | Configurations                                     | 144   |

| In-Circuit Serial Programming (ICSP)                   |     | Fail-Safe Clock Monitor                            |       |

| Input Capture Module                                   |     | Fast RC (FRC)                                      |       |

| Interrupts                                             |     | Initial Clock Source Selection                     |       |

| Register Map                                           |     | Low-Power RC (LPRC)                                |       |

| Input Capture Operation During Sleep and Idle N        |     | LP Oscillator Control                              |       |

| CPU Idle Mode                                          |     | Phase Locked Loop (PLL)                            |       |

| CPU Sleep Mode                                         |     | Start-up Timer (OST)                               |       |

| Input Capture Timing Requirements                      |     | Control Registers                                  |       |

| Input Change Notification Module                       |     | Operating Modes (Table)                            |       |

| Register Map                                           |     | System Overview                                    |       |

| Instruction Addressing Modes                           |     | Oscillator Selection                               |       |

| File Register Instructions Fundamental Modes Supported |     | Oscillator Start-up Timer                          |       |

| • •                                                    |     | Timing Requirements                                | . 187 |

| MAC Instructions                                       |     | Output Compare Interrupts                          |       |

| MCU Instructions  Move and Accumulator Instructions    |     | Output Compare Module                              |       |

|                                                        |     | Register Map dsPIC30F3014                          |       |

| Other InstructionsInstruction Set                      |     | Register Map dsPIC30F4013                          |       |

| Overview                                               | 162 | Timing Requirements                                |       |

| Summary                                                |     | Output Compare Operation During CPU Idle Mode      |       |

| Internal Clock Timing Examples                         |     | Output Compare Sleep Mode Operation                |       |

| Internal Clock Hilling Examples                        |     |                                                    |       |

| Interrupt Controller                                   | 223 | Р                                                  |       |

| Register Map                                           | 66  | Packaging Information                              | . 211 |

| Interrupt Priority                                     |     | Marking                                            | . 211 |

| Traps                                                  |     | Peripheral Module Disable (PMD) Registers          |       |

| Interrupt Sequence                                     |     | Pinout Descriptions                                |       |

| Interrupt Stack Frame                                  |     | POR. See Power-on Reset.                           |       |

| Interrupt Stack Frame                                  |     | Power Saving Modes                                 |       |

|                                                        |     | Sleep and Idle                                     |       |

| L                                                      |     | Power-Down Current (IPD)                           | . 176 |

| Load Conditions                                        | 181 | Power-Saving Modes                                 |       |

| Low-Voltage Detect (LVD)                               |     | Idle                                               | . 156 |

| CLKOUT and I/O185 DCI Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| AC-Link Mode194                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4                                                                                                                                        |

| Multichannel, I <sup>2</sup> S Modes192                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                          |

| External Clock181                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                          |

| Frame Sync, AC-Link Start-Of-Frame124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                          |

| Frame Sync, Multichannel Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                          |

| I <sup>2</sup> C Bus Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •                                                                                                                                        |

| Master Mode201                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                                        |

| Slave Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                          |

| I <sup>2</sup> C Bus Start/Stop Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ,                                                                                                                                        |