#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | H8S/2600                                                                         |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 20MHz                                                                            |

| Connectivity               | FIFO, I <sup>2</sup> C, LPC, SCI, SmartCard                                      |

| Peripherals                | POR, PWM, WDT                                                                    |

| Number of I/O              | 128                                                                              |

| Program Memory Size        | 160KB (160K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | External                                                                         |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

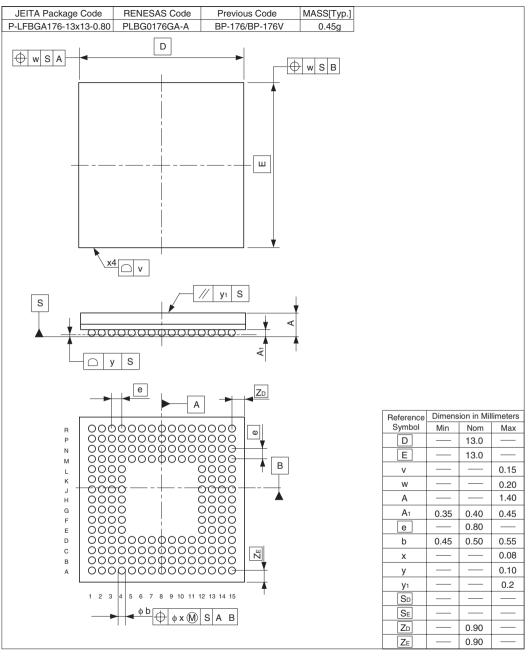

| Package / Case             | 176-LFBGA                                                                        |

| Supplier Device Package    | 176-LFBGA (13x13)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2117rvpbg20hv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2. Description of Numbers and Symbols

Aspects of the notations for register names, bit names, numbers, and symbolic names in this manual are explained below.

| (1)    | Dverall notation<br>n descriptions involving the names of bits and bit fields within this manual, the modules and<br>egisters to which the bits belong may be clarified by giving the names in the forms<br>module name"."register name"."bit name" or "register name"."bit name".                                                                                                                     |  |  |  |  |  |  |  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| (2)    | Register notation<br>The style "register name"_"instance number" is used in cases where there is more than one<br>instance of the same function or similar functions.<br>[Example] CMCSR_0: Indicates the CMCSR register for the compare-match timer of channel 0.                                                                                                                                     |  |  |  |  |  |  |  |

| (3)    | Number notation<br>Binary numbers are given as B'nnnn (B' may be omitted if the number is obviously binary),<br>hexadecimal numbers are given as H'nnnn or 0xnnnn, and decimal numbers are given as nnnn.<br>[Examples] Binary: B'11 or 11<br>Hexadecimal: H'EFA0 or 0xEFA0<br>Decimal: 1234                                                                                                           |  |  |  |  |  |  |  |

| (4)    | Notation for active-low<br>An overbar on the name indicates that a signal or pin is active-low.<br>[Example] WDTOVF                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|        | (4) (2)                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| _      |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

|        |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

|        | 14.2.2 Compare Match Control/Status Register_0, _1 (CMCSR_0, CMCSR_1)                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| L<br>T | CMCSR indicates compare match generation, enables or disables interrupts, and selects the counter<br>ut clock. Generation of a WDTOVF signal or interrupt initializes the TCNT value to 0.                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|        | 14.3 Opt-                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

|        | 14.3.1 Interval Count Operation                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

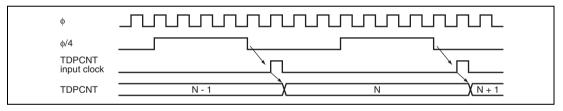

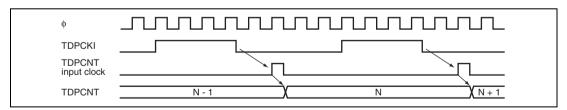

|        | When an internal clock is selected with the CKS1 and CKS0 bits in CMCSR and the STR bit in CMSTR is set to 1, CMCNT starts incrementing using the selected clock. When the values in CMCNT and the compare match constant register (CMCOR) match, CMCNT is cleared to H'0000 and the CMF flag in CMCSR is set to 1. When the CKS1 and CKS0 bits are set to B'01 at this time, a f/4 clock is selected. |  |  |  |  |  |  |  |

|        | Rev. 0.50, 10/04, page 416 of 914                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| L      | (3)                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|        | Note: The bit names and sentences in the above figure are examples and have nothing to do with the contents of this manual.                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

# Contents

| Secti | on 1 O   | verview                                           | 1    |

|-------|----------|---------------------------------------------------|------|

| 1.1   | Feature  | s                                                 | 1    |

|       | 1.1.1    | Applications                                      | 1    |

|       | 1.1.2    | Overview of Functions                             | 2    |

| 1.2   | List of  | Products                                          | 7    |

| 1.3   | Block I  | Diagram                                           | 8    |

| 1.4   | Pin Des  | scriptions                                        | 9    |

|       | 1.4.1    | Pin Assignments                                   | 9    |

|       | 1.4.2    | Pin Assignment in Each Operating Mode             | . 12 |

|       | 1.4.3    | Pin Functions                                     | . 19 |

| Secti | on 2 C   | PU                                                | 29   |

| 2.1   |          | S                                                 |      |

| 2.1   | 2.1.1    | Differences between H8S/2600 CPU and H8S/2000 CPU |      |

|       | 2.1.2    | Differences from H8/300 CPU                       |      |

|       | 2.1.3    | Differences from H8/300H CPU                      |      |

| 2.2   | CPU O    | perating Modes                                    |      |

|       | 2.2.1    | Normal Mode                                       |      |

|       | 2.2.2    | Advanced Mode                                     |      |

| 2.3   | Addres   | s Space                                           | . 36 |

| 2.4   | Registe  | rs                                                | . 37 |

|       | 2.4.1    | General Registers                                 | . 38 |

|       | 2.4.2    | Program Counter (PC)                              | . 39 |

|       | 2.4.3    | Extended Control Register (EXR)                   | . 39 |

|       | 2.4.4    | Condition-Code Register (CCR)                     |      |

|       | 2.4.5    | Multiply-Accumulate Register (MAC)                | .41  |

|       | 2.4.6    | Initial Values of CPU Registers                   | .41  |

| 2.5   | Data Fo  | ormats                                            | . 42 |

|       | 2.5.1    | General Register Data Formats                     | . 42 |

|       | 2.5.2    | Memory Data Formats                               | . 44 |

| 2.6   | Instruct | ion Set                                           | . 45 |

|       | 2.6.1    | Table of Instructions Classified by Function      | . 46 |

|       | 2.6.2    | Basic Instruction Formats                         | . 56 |

| 2.7   | Addres   | sing Modes and Effective Address Calculation      | . 57 |

|       | 2.7.1    | Register Direct—Rn                                | . 57 |

|       | 2.7.2    | Register Indirect—@ERn                            | . 57 |

|       | 15.9.8   | Note on Writing to Registers in Transmission, Reception, and   |     |

|-------|----------|----------------------------------------------------------------|-----|

|       |          | Simultaneous Transmission and Reception                        | 467 |

|       |          |                                                                |     |

| Secti | on 16 (  | CIR Interface                                                  | 469 |

| 16.1  | Feature  | <sup>2</sup> S                                                 | 469 |

| 16.2  | Input P  | 'ins                                                           | 471 |

| 16.3  | Registe  | er Description                                                 | 471 |

|       | 16.3.1   | Receive Control Register 1 (CCR1)                              | 472 |

|       | 16.3.2   | Receive Control Register 2 (CCR2)                              | 473 |

|       | 16.3.3   | Receive Status Register (CSTR)                                 | 474 |

|       | 16.3.4   | Interrupt Enable Register (CEIR)                               | 476 |

|       | 16.3.5   | Bit Rate Register (BRR)                                        | 477 |

|       | 16.3.6   | Receive Data Register 0 to 17 (CIRRDR0 to CIRRDR17)            | 478 |

|       | 16.3.7   | Header Minimum/Maximum High-Level Period Register              |     |

|       |          | (HHMIN and HHMAX)                                              | 478 |

|       | 16.3.8   | Header Minimum/Maximum Low-Level Period Register (HLMIN/HLMAX) | 480 |

|       | 16.3.9   | Data Level 1 Minimum/Maximum Period Register (DT1MIN/DT1MAX)   | 480 |

|       | 16.3.10  | ) Data Level 0 Minimum/Maximum Period Register (DT0MIN/DT0MAX) | 481 |

|       | 16.3.11  | Repeat Header Minimum/Maximum Low-Level Period Register        |     |

|       |          | (RMIN/RMAX)                                                    | 481 |

| 16.4  | Operati  | ion                                                            | 482 |

|       | 16.4.1   | Determination of Signal Type by Low/High-Level Period          | 484 |

|       | 16.4.2   | Operation of FIFO Register                                     | 486 |

|       | 16.4.3   | Operation in Watch Mode                                        | 487 |

|       | 16.4.4   | Switching between System Clock and Sub Clock                   | 487 |

| 16.5  | Noise (  | Canceler Circuit                                               | 488 |

| 16.6  | Reset C  | Conditions                                                     | 490 |

| 16.7  | Interrup | pt Sources                                                     | 490 |

| 16.8  | Usage I  | Note                                                           | 491 |

|       |          |                                                                |     |

| Secti | on 17 S  | Serial Communication Interface with FIFO (SCIF)                | 493 |

| 17.1  | Feature  | 28                                                             | 493 |

| 17.2  | Input/C  | Dutput Pins                                                    | 495 |

| 17.3  | Registe  | er Descriptions                                                | 496 |

|       | 17.3.1   | Receive Shift Register (FRSR)                                  | 497 |

|       |          | Receive Buffer Register (FRBR)                                 |     |

|       | 17.3.3   | Transmitter Shift Register (FTSR)                              | 498 |

|       |          | Transmitter Holding Register (FTHR)                            |     |

|       |          | Divisor Latch H, L (FDLH, FDLL)                                |     |

|       | 17.3.6   | Interrupt Enable Register (FIER)                               | 499 |

| TFP-<br>144V         BP.<br>176V         TLP-<br>145V         Single-Chip Mode           45         R5         N4         PF5/PWMU3A           46         M6         M5         PF4/PWMU2A           47         N6         L5         PF3/IRQ11/TMOX/TDPCKI0/TDPMCI0           48         R6         M6         PF2/IRQ3/IRQ1/TMOY/TDPCYI0           49         P6         N5         PF1/IRQ9/PWMU1A           50         M7         K5         PF0/IRQ8/PWMU0A           -         N7 (N)         -         PI1           51 (N)         R7 (N)         L6 (N)         PG7/EXIRQ15/ExSCLB           52 (N)         P7 (N)         M7 (N)         PG6/EXIRQ14/ExSDAB           53 (N)         M8 (N)         N6 (N)         PG5/EXIRQ13/ExSCLA           -         N8 (N)         N6 (N)         PG3/EXIRQ13/ExSCLA           -         N8 (N)         N6 (N)         PG3/EXIRQ13/ExSCLA           -         M9 (N)         -         NC           56 (N)         P8 (N)         K7 (N)         PG3/EXIRQ17/SD2L           -         M9 (N)         N7 (N)         PG1/EXIRQ17/SD2L           -         M9 (N)         N7 (N)         PG1/EXIRQ17/SD2L           57 (N) </th <th></th> <th>Pin No</th> <th></th> <th>Pin Name</th> |        | Pin No      |        | Pin Name                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------|--------|---------------------------------|

| 144V         176V         145V         Mode 2 (EXPE = 0)           45         R5         N4         PF5/PWMU3A           46         M6         M5         PF4/PWMU2A           47         N6         L5         PF3/IRQ11/TMOX/TDPCKI0/TDPMCI0           48         R6         M6         PF2/IRQ10/TMOY/TDPCYI0           49         P6         N5         PF1/IRQ9/PWMU1A           50         M7         K5         PF0/IRQ8/PVMU0A           -         N7 (N)         -         PI1           51 (N)         R7 (N)         L6 (N)         PG7/EXIRQ15/EXSCLB           52 (N)         P7 (N)         M7 (N)         PG6/EXIRQ13/EXSCLA           -         N8 (N)         M6 (N)         PG5/EXIRQ13/EXSCLA           -         N8 (N)         -         PI0           54 (N)         R6 (N)         PG4/EXIRQ12/EXSDAA           55 (N)         P8 (N)         K7 (N)         PG3/EXIRQ11/SCL2           -         M8 (N)         MG2/EXIRQ17/SDA2         57 (N)           57 (N)         PG1/EXIRQ8/TMIX/TDPCK11/TDPMC11         58 (N)           58 (N)         PG0/EXIRQ8/TMIX/TDPCK11/TDPMC11         58 (N)           59         M10         L7         <                                                               | TFP-   | P- BP- TLP- |        | Single-Chip Mode                |

| 46         M6         M5         PF4/PWMU2A           47         N6         L5         PF3/IRQ11/TMOX/TDPCKI0/TDPMCI0           48         R6         M6         PF2/IRQ10/TMOY/TDPCYI0           49         P6         N5         PF1/IRQ9/PWMU1A           50         M7         K5         PF0/IRQ8/PWMU0A           -         N7 (N)         -         PI1           51 (N)         R7 (N)         L6 (N)         PG7/EXIRQ15/ExSCLB           52 (N)         P7 (N)         M7 (N)         PG6/EXIRQ13/ExSCLA           -         N8 (N)         N6 (N)         PG5/EXIRQ12/ExSDAA           53 (N)         M8 (N)         N6 (N)         PG4/EXIRQ12/ExSDAA           54 (N)         R8 (N)         K6 (N)         PG4/EXIRQ17/SCL2           -         M9 (N)         -         NC           56 (N)         N9 (N)         K8 (N)         PG2/EXIRQ9/TMIY/TDPCKI1/TDPMCI1           58 (N)         P9 (N)         M8 (N)         PG0/EXIRQ8/TMIX/TDPCYI1           59         M10         L7         PD7/AN15           60         N10         K9         PD6/AN14           61         R10         N8         PD5/AN13           62         P10 </th <th></th> <th></th> <th></th> <th>Mode 2 (EXPE = 0)</th>               |        |             |        | Mode 2 (EXPE = 0)               |

| 47         N6         L5         PF3/IRQ11/TMOX/TDPCKI0/TDPMCI0           48         R6         M6         PF2/IRQ10/TMOY/TDPCYI0           49         P6         N5         PF1/IRQ9/PWMU1A           50         M7         K5         PF0/IRQ6/PWMU0A           -         N7 (N)         -         PI1           51 (N)         R7 (N)         L6 (N)         PG7/EXIRQ15/ExSCLB           52 (N)         P7 (N)         M7 (N)         PG6/EXIRQ14/ExSDAB           53 (N)         M8 (N)         N6 (N)         PG5/EXIRQ13/ExSCLA           -         N8 (N)         -         PI0           54 (N)         R6 (N)         PG4/EXIRQ12/ExSDAA           55 (N)         P8 (N)         K7 (N)         PG3/EXIRQ11/SCL2           -         M9 (N)         -         NC           56 (N)         N9 (N)         K8 (N)         PG2/EXIRQ10/SDA2           57 (N)         R9 (N)         N7 (N)         PG1/EXIRQ8/TMIX/TDPCKI1/TDPMCI1           58 (N)         P9 (N)         M8 (N)         PG0/EXIRQ8/TMIX/TDPCYI1           59         M10         L7         PD7/AN15           60         N10         K9         PD6/AN14           61         R10                                                                         | 45     | R5          | N4     | PF5/PWMU3A                      |

| 48         R6         M6         PF2/IRQ10/TMOY/TDPCY10           49         P6         N5         PF1/IRQ9/PWMU1A           50         M7         K5         PF0/IRQ6/PWMU0A            N7 (N)          PI1           51 (N)         R7 (N)         L6 (N)         PG7/ExIRQ15/ExSCLB           52 (N)         P7 (N)         M7 (N)         PG6/ExIRQ14/ExSDAB           53 (N)         M8 (N)         N6 (N)         PG5/ExIRQ13/ExSCLA           -         N8 (N)         -         PI0           54 (N)         R8 (N)         M6 (N)         PG3/ExIRQ11/ExSDAA           55 (N)         P8 (N)         K7 (N)         PG3/ExIRQ11/SCL2           -         M9 (N)         -         NC           56 (N)         N9 (N)         K8 (N)         PG2/ExIRQ10/SDA2           57 (N)         R9 (N)         N7 (N)         PG1/ExIRQ8/TMIX/TDPCKI1/TDPMCI1           58 (N)         P9 (N)         M8 (N)         PG0/ExIRQ8/TMIX/TDPCYI1           59         M10         L7         PD7/AN15           60         N10         K9         PD6/AN14           61         R10         N8         PD5/AN13           62         P10 </td <td>46</td> <td>M6</td> <td>M5</td> <td>PF4/PWMU2A</td>                                    | 46     | M6          | M5     | PF4/PWMU2A                      |

| 49         P6         N5         PF1/IRQ9/PWMU1A           50         M7         K5         PF0/IRQ8/PWMU0A           -         N7 (N)         -         PI1           51 (N)         R7 (N)         L6 (N)         PG7/ExIRQ15/ExSCLB           52 (N)         P7 (N)         M7 (N)         PG6/ExIRQ14/ExSDAB           53 (N)         M8 (N)         N6 (N)         PG5/ExIRQ12/ExSCLA           -         N8 (N)         -         PI0           54 (N)         R8 (N)         K6 (N)         PG4/ExIRQ12/ExSDAA           55 (N)         P8 (N)         K7 (N)         PG3/ExIRQ10/SDA2           -         M9 (N)         -         NC           56 (N)         N9 (N)         K8 (N)         PG2/ExIRQ9/TMIY/TDPCKI1/TDPMCI1           58 (N)         P9 (N)         M8 (N)         PG0/ExIRQ9/TMIY/TDPCKI1/TDPMCI1           59         M10         L7         PD7/AN15           60         N10         K9         PD6/AN14           61         R10         N8         PD5/AN13           62         P10         M9         PD4/AN12           63         N11         L8         PD3/AN11           64         R11         N10                                                                                           | 47     | N6          | L5     | PF3/IRQ11/TMOX/TDPCKI0/TDPMCI0  |

| 50         M7         K5         PF0/IRQ8/PWMU0A            N7 (N)          PI1           51 (N)         R7 (N)         L6 (N)         PG7/ExIRQ15/ExSCL8           52 (N)         P7 (N)         M7 (N)         PG6/ExIRQ14/ExSDAB           53 (N)         M8 (N)         N6 (N)         PG5/ExIRQ13/ExSCLA           -         N8 (N)         -         PI0           54 (N)         R8 (N)         FG (N)         PG4/ExIRQ12/ExSDAA           55 (N)         P8 (N)         K7 (N)         PG3/ExIRQ10/SDA2           -         M9 (N)         -         NC           56 (N)         N9 (N)         K8 (N)         PG2/ExIRQ10/SDA2           57 (N)         R9 (N)         N7 (N)         PG1/ExIRQ9/TMIY/TDPCKI1/TDPMCI1           58 (N)         P9 (N)         M8 (N)         PG0/ExIRQ8/TMIX/TDPCYI1           59         M10         L7         PD7/AN15           60         N10         K9         PD6/AN14           61         R10         N8         PD5/AN13           62         P10         M9         PD4/AN12           63         N11         L8         PD3/AN11           64         R11         M1                                                                                                         | 48     | R6          | M6     | PF2/IRQ10/TMOY/TDPCYI0          |

| N7 (N)         PI1           51 (N)         R7 (N)         L6 (N)         PG7/ExIRQ15/ExSCLB           52 (N)         P7 (N)         M7 (N)         PG6/ExIRQ14/ExSDAB           53 (N)         M8 (N)         N6 (N)         PG5/ExIRQ13/ExSCLA           -         N8 (N)         -         PI0           54 (N)         R8 (N)         K6 (N)         PG4/ExIRQ12/ExSDAA           55 (N)         P8 (N)         K7 (N)         PG3/ExIRQ11/SCL2           -         M9 (N)         -         NC           56 (N)         N9 (N)         K8 (N)         PG2/ExIRQ9/TMIY/TDPCKI1/TDPMCI1           58 (N)         P9 (N)         N7 (N)         PG1/ExIRQ9/TMIY/TDPCKI1/TDPMCI1           59 M10         L7         PD7/AN15           60 N10         K9         PD6/AN14           61 R10         N8         PD5/AN13           62 P10         M9         PD4/AN12           63 N11         L8         PD3/AN11           64         R11         K10         PD2/AN10           65         P11         N9         PD1/AN9           66         M11         M10         PD0/AN8           67         R12         L9         AVSS                                                                                                  | 49     | P6          | N5     | PF1/IRQ9/PWMU1A                 |

| 51 (N)       R7 (N)       L6 (N)       PG7/ExIRQ15/ExSCLB         52 (N)       P7 (N)       M7 (N)       PG6/ExIRQ14/ExSDAB         53 (N)       M8 (N)       N6 (N)       PG5/ExIRQ13/ExSCLA         -       N8 (N)       -       PI0         54 (N)       R8 (N)       K6 (N)       PG4/ExIRQ12/ExSDAA         55 (N)       P8 (N)       K7 (N)       PG3/ExIRQ10/ExSDAA         55 (N)       P8 (N)       K7 (N)       PG3/ExIRQ10/SDA2         -       M9 (N)       -       NC         56 (N)       N9 (N)       K8 (N)       PG2/ExIRQ10/SDA2         57 (N)       R9 (N)       N7 (N)       PG1/ExIRQ9/TMIY/TDPCKI1/TDPMCI1         58 (N)       P9 (N)       M8 (N)       PG0/ExIRQ8/TMIX/TDPCYI1         59       M10       L7       PD7/AN15         60       N10       K9       PD6/AN14         61       R10       N8       PD5/AN13         62       P10       M9       PD4/AN12         63       N11       L8       PD3/AN11         64       R11       K10       PD2/AN10         65       P11       N9       PD1/AN8         66       M11       M10       P                                                                                                                                                          | 50     | M7          | K5     | PF0/IRQ8/PWMU0A                 |

| 52 (N)       P7 (N)       M7 (N)       PG6/ExIRQ14/ExSDAB         53 (N)       M8 (N)       N6 (N)       PG5/ExIRQ13/ExSCLA         -       N8 (N)       -       PI0         54 (N)       R8 (N)       K6 (N)       PG4/ExIRQ12/ExSDAA         55 (N)       P8 (N)       K7 (N)       PG3/ExIRQ11/SCL2         -       M9 (N)       -       NC         56 (N)       N9 (N)       K8 (N)       PG2/ExIRQ9/TMIY/TDPCKI1/TDPMCI1         58 (N)       P9 (N)       N7 (N)       PG1/ExIRQ9/TMIY/TDPCKI1/TDPMCI1         58 (N)       P9 (N)       M8 (N)       PG0/ExIRQ9/TMIX/TDPCYI1         59       M10       L7       PD7/AN15         60       N10       K9       PD6/AN14         61       R10       N8       PD5/AN13         62       P10       M9       PD4/AN12         63       N11       L8       PD3/AN11         64       R11       K10       PD2/AN10         65       P11       N9       PD1/AN9         66       M11       M10       PD0/AN8         67       R12       L9       AVSS         -       P12       AVSS         68                                                                                                                                                                                      | _      | N7 (N)      |        | PI1                             |

| 53 (N)         M8 (N)         N6 (N)         PG5/ExIRQ13/ExSCLA           -         N8 (N)         -         PI0           54 (N)         R8 (N)         K6 (N)         PG4/ExIRQ12/ExSDAA           55 (N)         P8 (N)         K7 (N)         PG3/ExIRQ11/SCL2           -         M9 (N)         -         NC           56 (N)         N9 (N)         K8 (N)         PG2/ExIRQ10/SDA2           57 (N)         R9 (N)         N7 (N)         PG1/ExIRQ9/TMIY/TDPCKI1/TDPMCI1           58 (N)         P9 (N)         M8 (N)         PG0/ExIRQ8/TMIX/TDPCYI1           59         M10         L7         PD7/AN15           60         N10         K9         PD6/AN14           61         R10         N8         PD5/AN13           62         P10         M9         PD4/AN12           63         N11         L8         PD3/AN11           64         R11         K10         PD2/AN10           65         P11         N9         PD1/AN9           66         M11         M10         PD0/AN8           67         R12         L9         AVSS           -         P12         -         AVSS                                                                                                                            | 51 (N) | R7 (N)      | L6 (N) | PG7/ExIRQ15/ExSCLB              |

| N8 (N)         PI0           54 (N)         R8 (N)         K6 (N)         PG4/ExIRQ12/ExSDAA           55 (N)         P8 (N)         K7 (N)         PG3/ExIRQ11/SCL2           -         M9 (N)         -         NC           56 (N)         N9 (N)         K8 (N)         PG2/ExIRQ10/SDA2           57 (N)         R9 (N)         N7 (N)         PG1/ExIRQ9/TMIY/TDPCKI1/TDPMCI1           58 (N)         P9 (N)         M8 (N)         PG0/ExIRQ8/TMIX/TDPCY11           59         M10         L7         PD7/AN15           60         N10         K9         PD6/AN14           61         R10         N8         PD5/AN13           62         P10         M9         PD4/AN12           63         N11         L8         PD3/AN11           64         R11         K10         PD2/AN10           65         P11         N9         PD1/AN9           66         M11         M10         PD0/AN8           67         R12         L9         AVSS            P12         -         AVSS           68         N12         N10         P70/AN0                                                                                                                                                                              | 52 (N) | P7 (N)      | M7 (N) | PG6/ExIRQ14/ExSDAB              |

| 54 (N)         R8 (N)         K6 (N)         PG4/ExIRQ12/ExSDAA           55 (N)         P8 (N)         K7 (N)         PG3/ExIRQ11/SCL2           -         M9 (N)         -         NC           56 (N)         N9 (N)         K8 (N)         PG2/ExIRQ10/SDA2           57 (N)         R9 (N)         N7 (N)         PG1/ExIRQ9/TMIY/TDPCKI1/TDPMCI1           58 (N)         P9 (N)         M8 (N)         PG0/ExIRQ8/TMIX/TDPCYI1           59         M10         L7         PD7/AN15           60         N10         K9         PD6/AN14           61         R10         N8         PD5/AN13           62         P10         M9         PD4/AN12           63         N11         L8         PD3/AN11           64         R11         K10         PD2/AN10           65         P11         N9         PD1/AN9           66         M11         M10         PD0/AN8           67         R12         L9         AVSS            P12         -         AVSS           68         N12         N10         P70/AN0                                                                                                                                                                                                           | 53 (N) | M8 (N)      | N6 (N) | PG5/ExIRQ13/ExSCLA              |

| 55 (N)         P8 (N)         K7 (N)         PG3/ExIRQ11/SCL2           -         M9 (N)         -         NC           56 (N)         N9 (N)         K8 (N)         PG2/ExIRQ10/SDA2           57 (N)         R9 (N)         N7 (N)         PG1/ExIRQ9/TMIY/TDPCKI1/TDPMCI1           58 (N)         P9 (N)         M8 (N)         PG0/ExIRQ8/TMIX/TDPCYI1           59         M10         L7         PD7/AN15           60         N10         K9         PD6/AN14           61         R10         N8         PD5/AN13           62         P10         M9         PD4/AN12           63         N11         L8         PD3/AN11           64         R11         K10         PD2/AN10           65         P11         N9         PD1/AN9           66         M11         M10         PD0/AN8           67         R12         L9         AVSS            P12         -         AVSS           68         N12         N10         P70/AN0                                                                                                                                                                                                                                                                                     | _      | N8 (N)      |        | PIO                             |

| M9 (N)         NC           56 (N)         N9 (N)         K8 (N)         PG2/ExIRQ10/SDA2           57 (N)         R9 (N)         N7 (N)         PG1/ExIRQ9/TMIY/TDPCKI1/TDPMCI1           58 (N)         P9 (N)         M8 (N)         PG0/ExIRQ8/TMIX/TDPCYI1           59         M10         L7         PD7/AN15           60         N10         K9         PD6/AN14           61         R10         N8         PD5/AN13           62         P10         M9         PD4/AN12           63         N11         L8         PD3/AN11           64         R11         K10         PD2/AN10           65         P11         N9         PD1/AN9           66         M11         M10         PD0/AN8           67         R12         L9         AVSS           -         P12         AVSS           68         N12         N10         P70/AN0                                                                                                                                                                                                                                                                                                                                                                                  | 54 (N) | R8 (N)      | K6 (N) | PG4/ExIRQ12/ExSDAA              |

| 56 (N)         N9 (N)         K8 (N)         PG2/ExIRQ10/SDA2           57 (N)         R9 (N)         N7 (N)         PG1/ExIRQ9/TMIY/TDPCKI1/TDPMCI1           58 (N)         P9 (N)         M8 (N)         PG0/ExIRQ8/TMIX/TDPCYI1           59         M10         L7         PD7/AN15           60         N10         K9         PD6/AN14           61         R10         N8         PD5/AN13           62         P10         M9         PD4/AN12           63         N11         L8         PD3/AN11           64         R11         K10         PD2/AN10           65         P11         N9         PD1/AN9           66         M11         M10         PD0/AN8           67         R12         L9         AVSS           -         P12         -         AVSS           68         N12         N10         P70/AN0                                                                                                                                                                                                                                                                                                                                                                                                    | 55 (N) | P8 (N)      | K7 (N) | PG3/ExIRQ11/SCL2                |

| 57 (N)         R9 (N)         N7 (N)         PG1/ExIRQ9/TMIY/TDPCKI1/TDPMCI1           58 (N)         P9 (N)         M8 (N)         PG0/ExIRQ8/TMIX/TDPCYI1           59         M10         L7         PD7/AN15           60         N10         K9         PD6/AN14           61         R10         N8         PD5/AN13           62         P10         M9         PD4/AN12           63         N11         L8         PD3/AN11           64         R11         K10         PD2/AN10           65         P11         N9         PD1/AN8           66         M11         M10         PD0/AN8           67         R12         L9         AVSS            P12         -         AVSS           68         N12         N10         P70/AN0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _      | M9 (N)      |        | NC                              |

| 58 (N)       P9 (N)       M8 (N)       PG0/ExIRQ8/TMIX/TDPCYI1         59       M10       L7       PD7/AN15         60       N10       K9       PD6/AN14         61       R10       N8       PD5/AN13         62       P10       M9       PD4/AN12         63       N11       L8       PD3/AN11         64       R11       K10       PD2/AN10         65       P11       N9       PD1/AN9         66       M11       M10       PD0/AN8         67       R12       L9       AVSS         -       P12       -       AVSS         68       N12       N10       P70/AN0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 56 (N) | N9 (N)      | K8 (N) | PG2/ExIRQ10/SDA2                |

| 59         M10         L7         PD7/AN15           60         N10         K9         PD6/AN14           61         R10         N8         PD5/AN13           62         P10         M9         PD4/AN12           63         N11         L8         PD3/AN11           64         R11         K10         PD2/AN10           65         P11         N9         PD1/AN9           66         M11         M10         PD0/AN8           67         R12         L9         AVSS            P12          AVSS           68         N12         N10         P70/AN0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 57 (N) | R9 (N)      | N7 (N) | PG1/ExIRQ9/TMIY/TDPCKI1/TDPMCI1 |

| 60         N10         K9         PD6/AN14           61         R10         N8         PD5/AN13           62         P10         M9         PD4/AN12           63         N11         L8         PD3/AN11           64         R11         K10         PD2/AN10           65         P11         N9         PD1/AN9           66         M11         M10         PD0/AN8           67         R12         L9         AVSS            P12          AVSS           68         N12         N10         P70/AN0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 58 (N) | P9 (N)      | M8 (N) | PG0/ExIRQ8/TMIX/TDPCYI1         |

| 61       R10       N8       PD5/AN13         62       P10       M9       PD4/AN12         63       N11       L8       PD3/AN11         64       R11       K10       PD2/AN10         65       P11       N9       PD1/AN9         66       M11       M10       PD0/AN8         67       R12       L9       AVSS          P12        AVSS         68       N12       N10       P70/AN0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 59     | M10         | L7     | PD7/AN15                        |

| 62       P10       M9       PD4/AN12         63       N11       L8       PD3/AN11         64       R11       K10       PD2/AN10         65       P11       N9       PD1/AN9         66       M11       M10       PD0/AN8         67       R12       L9       AVSS          P12        AVSS         68       N12       N10       P70/AN0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 60     | N10         | K9     | PD6/AN14                        |

| 63         N11         L8         PD3/AN11           64         R11         K10         PD2/AN10           65         P11         N9         PD1/AN9           66         M11         M10         PD0/AN8           67         R12         L9         AVSS            P12          AVSS           68         N12         N10         P70/AN0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 61     | R10         | N8     | PD5/AN13                        |

| 64         R11         K10         PD2/AN10           65         P11         N9         PD1/AN9           66         M11         M10         PD0/AN8           67         R12         L9         AVSS            P12          AVSS           68         N12         N10         P70/AN0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 62     | P10         | M9     | PD4/AN12                        |

| 65         P11         N9         PD1/AN9           66         M11         M10         PD0/AN8           67         R12         L9         AVSS            P12          AVSS           68         N12         N10         P70/AN0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 63     | N11         | L8     | PD3/AN11                        |

| 66         M11         M10         PD0/AN8           67         R12         L9         AVSS            P12          AVSS           68         N12         N10         P70/AN0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 64     | R11         | K10    | PD2/AN10                        |

| 67         R12         L9         AVSS            P12          AVSS           68         N12         N10         P70/AN0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 65     | P11         | N9     | PD1/AN9                         |

| P12         AVSS           68         N12         N10         P70/AN0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 66     | M11         | M10    | PD0/AN8                         |

| 68 N12 N10 P70/AN0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 67     | R12         | L9     | AVSS                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _      | P12         |        | AVSS                            |

| 69 R13 M11 P71/AN1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 68     | N12         | N10    | P70/AN0                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 69     | R13         | M11    | P71/AN1                         |

### 1.4.3 Pin Functions

### Table 1.4Pin Functions

| Pin No.                      |            |                        |                                                           |                            |        |                                                                                                                                                                                                    |

|------------------------------|------------|------------------------|-----------------------------------------------------------|----------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Туре                         | Symbol     | TFP-144V               | BP-176V                                                   | TLP-145V                   | I/O    | Name and Function                                                                                                                                                                                  |

| Power<br>supply              | VCC        | 1, 36, 86              | A1, J15,<br>P1, P2                                        | B1, M1,<br>H10             | Input  | Power supply pins. Connect all<br>these pins to the system power<br>supply. Connect the bypass<br>capacitor between VCC and VSS<br>(that is located near these pins).                              |

|                              | VCL        | 13                     | F1                                                        | E1                         | Input  | External capacitance pin for<br>internal step-down power. Connect<br>this pin to VSS through an external<br>capacitor (that is located near this<br>pin) to stabilize internal step-down<br>power. |

|                              | VSS        | 7, 42, 95,<br>111, 139 | D1, D2,<br>P4, R4,<br>F12, F13,<br>B13,<br>A13, A4,<br>B4 | D2, L3,<br>F10, B11,<br>C5 | Input  | Ground pins. Connect all these<br>pins to the system power supply<br>(0 V).                                                                                                                        |

| Clock                        | XTAL       | 143                    | A2                                                        | A3                         | Input  | For connection to a crystal                                                                                                                                                                        |

|                              | EXTAL      | 144                    | B2                                                        | A2                         | Input  | resonator. An external clock can be<br>supplied from the EXTAL pin. For<br>an example of crystal resonator<br>connection, see section 25, Clock<br>Pulse Generator.                                |

|                              | φ          | 18                     | H1                                                        | F4                         | Output | Supplies the system clock to external devices.                                                                                                                                                     |

|                              | EXCL       | 18                     | H1                                                        | F4                         | Input  | 32.768 kHz external sub clock                                                                                                                                                                      |

|                              | ExEXCL     | 32                     | M3                                                        | K1                         | Input  | should be supplied. To which pin<br>the external clock is input can be<br>selected from the EXCL or<br>ExEXCL pin.                                                                                 |

| Operating<br>mode<br>control | MD2<br>MD1 | 25<br>9                | K1<br>E2                                                  | H1<br>D1                   | Input  | These pins set the operating mode.<br>Inputs at these pins should not be<br>changed during operation.                                                                                              |

| System control               | RES        | 8                      | E3                                                        | D3                         | Input  | Reset pin. When this pin is low, the chip is reset.                                                                                                                                                |

RENESAS

- -

Rev. 2.00 Sep. 28, 2009 Page 19 of 994 REJ09B0452-0200

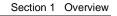

### 2.4.1 General Registers

The H8S/2600 CPU has eight 32-bit general registers. These general registers are all functionally identical and can be used as both address registers and data registers. When a general register is used as a data register, it can be accessed as a 32-bit, 16-bit, or 8-bit register. Figure 2.7 illustrates the usage of the general registers. When the general registers are used as 32-bit registers or address registers, they are designated by the letters ER (ER0 to ER7).

The ER registers divide into 16-bit general registers designated by the letters E (E0 to E7) and R (R0 to R7). These registers are functionally equivalent, providing a maximum of sixteen 16-bit registers. The E registers (E0 to E7) are also referred to as extended registers.

The R registers divide into 8-bit general registers designated by the letters RH (R0H to R7H) and RL (R0L to R7L). These registers are functionally equivalent, providing a maximum of sixteen 8-bit registers.

The usage of each register can be selected independently.

General register ER7 has the function of stack pointer (SP) in addition to its general-register function, and is used implicitly in exception handling and subroutine calls. Figure 2.8 shows the stack.

Figure 2.7 Usage of General Registers

| Instructio   | on S  | Size*        | Function                                                                                                                                                                                                                                                                                                        |

|--------------|-------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADD<br>SUB   | E     | 3/W/L        | $Rd \pm Rs \rightarrow Rd$ , $Rd \pm \#IMM \rightarrow Rd$<br>Performs addition or subtraction on data in two general registers, or on<br>immediate data and data in a general register (immediate byte data<br>cannot be subtracted from byte data in a general register. Use the SUBX<br>or ADD instruction.) |

| ADDX<br>SUBX | E     | 3            | $Rd \pm Rs \pm C \rightarrow Rd$ , $Rd \pm \#IMM \pm C \rightarrow Rd$<br>Performs addition or subtraction with carry on byte data in two general<br>registers, or on immediate data and data in a general register.                                                                                            |

| INC<br>DEC   | E     | 3/W/L        | $Rd \pm 1 \rightarrow Rd$ , $Rd \pm 2 \rightarrow Rd$<br>Increments or decrements a general register by 1 or 2. (Byte operands<br>can be incremented or decremented by 1 only.)                                                                                                                                 |

| ADDS<br>SUBS | L     | _            | $Rd \pm 1 \rightarrow Rd$ , $Rd \pm 2 \rightarrow Rd$ , $Rd \pm 4 \rightarrow Rd$<br>Adds or subtracts the value 1, 2, or 4 to or from data in a 32-bit register.                                                                                                                                               |

| DAA<br>DAS   | E     | 3            | Rd decimal adjust $\rightarrow$ Rd<br>Decimal-adjusts an addition or subtraction result in a general register by<br>referring to the CCR to produce 4-bit BCD data.                                                                                                                                             |

| MULXU        | E     | 3/W          | $Rd \times Rs \rightarrow Rd$<br>Performs unsigned multiplication on data in two general registers: either<br>8 bits × 8 bits $\rightarrow$ 16 bits or 16 bits × 16 bits $\rightarrow$ 32 bits.                                                                                                                 |

| MULXS        | E     | 3/W          | $Rd \times Rs \rightarrow Rd$<br>Performs signed multiplication on data in two general registers: either 8<br>bits $\times$ 8 bits $\rightarrow$ 16 bits or 16 bits $\times$ 16 bits $\rightarrow$ 32 bits.                                                                                                     |

| DIVXU        | E     | 3/W          | Rd ÷ Rs → Rd<br>Performs unsigned division on data in two general registers: either 16<br>bits ÷ 8 bits → 8-bit quotient and 8-bit remainder or 32 bits ÷ 16 bits →<br>16-bit quotient and 16-bit remainder.                                                                                                    |

| Note: *      | Refer | s to the     | operand size.                                                                                                                                                                                                                                                                                                   |

|              |       | Byte<br>Vord |                                                                                                                                                                                                                                                                                                                 |

#### **Arithmetic Operations Instructions (1)** Table 2.4

L: Longword

| Origin of           |                                                                                                                          | <b>N</b> (       | Vector Address |       |          |

|---------------------|--------------------------------------------------------------------------------------------------------------------------|------------------|----------------|-------|----------|

| Interrupt<br>Source | Name                                                                                                                     | Vector<br>Number | Advanced Mode  | ICR   | Priority |

| _                   | Reserved for system use                                                                                                  | 24               | H'000060       | _     | High     |

| WDT_0               | WOVI0 (Interval timer)                                                                                                   | 25               | H'000064       | ICRA1 | _ ↑      |

| WDT_1               | WOVI1 (Interval timer)                                                                                                   | 26               | H'000068       | ICRA0 | -        |

| _                   | Address break                                                                                                            | 27               | H'00006C       | _     | -        |

| A/D converter       | ADI (A/D conversion end)                                                                                                 | 28               | H'000070       | ICRB7 | -        |

| _                   | Reserved for system use                                                                                                  | 29               | H'000074       | _     | -        |

|                     |                                                                                                                          |                  |                |       |          |

|                     |                                                                                                                          | 32               | H'000080       |       |          |

| External pin        | WUE15 to WUE8                                                                                                            | 33               | H'000084       | ICRD4 | -        |

| TPU_0               | TGI0A (TGR0A input                                                                                                       | 34               | H'000088       | ICRD3 | -        |

|                     | capture/compare match)<br>TGI0B (TGR0B input<br>capture/compare match)                                                   | 35               | H'00008C       |       |          |

|                     | TGI0C (TGR0C input                                                                                                       | 36               | H'000090       |       |          |

|                     | capture/compare match)<br>TGI0D (TGR0D input<br>capture/compare match)                                                   | 37               | H'000094       |       |          |

|                     | TGI0V (Overflow 0)                                                                                                       | 38               | H'000098       |       |          |

| TPU_1               | TGI1A (TGR1A input                                                                                                       | 39               | H'00009C       | ICRD2 | _        |

|                     | capture/compare match)<br>TGI1B (TGR1B input<br>capture/compare match)                                                   | 40               | H'0000A0       |       |          |

|                     | TGI1V (Overflow 1)                                                                                                       | 41               | H'0000A4       |       |          |

|                     | TGI1U (Underflow 1)                                                                                                      | 42               | H'0000A8       |       |          |

| TPU_2               | TGI2A (TGR2A input<br>capture/compare match)                                                                             | 43               | H'0000AC       | ICRD1 | _        |

|                     | TGI2B (TGR2B input<br>capture/compare match)                                                                             | 44               | H'0000B0       |       |          |

|                     | TGI2V (Overflow 2)                                                                                                       | 45               | H'0000B4       |       |          |

|                     | TGI2U (Underflow 2)                                                                                                      | 46               | H'0000B8       |       |          |

| _                   | Reserved for system use                                                                                                  | 47               | H'0000BC       | _     |          |

| TCM_0               | TICI0 (Input capture)<br>TCMI0 (Compare match)<br>TOVMI0 (Cycle overflow)<br>TUDI0 (Cycle underflow)<br>TOVI0 (Overflow) | 48               | H'0000C0       | ICRB6 | _        |

| TCM_1               | TICI1 (Input capture)<br>TCMI1 (Compare match)<br>TOVMI1 (Cycle overflow)<br>TUDI1 (Cycle underflow)<br>TOVI1 (Overflow) | 49               | H'0000C4       | _     | Low      |

| Origin of<br>Interrupt |                                                                                                                                              | Vector   | Vector Address       |       |          |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------|-------|----------|

| Source                 | Name                                                                                                                                         | Number   | Advanced Mode        | ICR   | Priority |

| SCI_2                  | ERI2 (Reception error)                                                                                                                       | 88       | H'000160             | ICRC5 | High     |

|                        | RXI2 (Reception completion)<br>TXI2 (Transmission data empty 2)                                                                              | 89<br>90 | H'000164<br>H'000168 |       | <b></b>  |

|                        | TEI2 (Transmission end 2)                                                                                                                    | 90<br>91 | H'00016C             |       |          |

| IIC_0                  | IICI0 (1-byte transmission/reception completion)                                                                                             | 92       | H'000170             | ICRC4 | -        |

| CIR                    | RENDI (Reception end)<br>OVEI (Overrun error)<br>REPI (Repeat detection)<br>FREI (Framing error)<br>ABI (Abort)<br>HEADFI (Header detection) | 93       | H'000174             | ICRB4 | -        |

| IIC_1                  | IICI1 (1-byte transmission/reception completion)                                                                                             | 94       | H'000178             | ICRC3 | -        |

| IIC_2                  | IICl2 (1-byte transmission/reception completion)                                                                                             | 95       | H'00017C             |       |          |

| PS2                    | KBIA (Reception completion A)                                                                                                                | 96       | H'000180             | ICRB0 | -        |

|                        | KBIB (Reception completion B)                                                                                                                | 97       | H'000184             |       |          |

|                        | KBIC (Reception completion C)                                                                                                                | 98       | H'000188             |       |          |

|                        | KBTIA (Transmission completion A)/<br>KBCA (1st KCLKA)                                                                                       | 99       | H'00018C             |       |          |

|                        | KBTIB (Transmission completion B)/<br>KBCB (1st KCLKB)                                                                                       | 100      | H'000190             |       |          |

|                        | KBTIC (Transmission completion C)/<br>KBCC (1st KCLKC)                                                                                       | 101      | H'000194             |       |          |

|                        | KBID (Reception completion D)                                                                                                                | 102      | H'000198             |       |          |

|                        | KBTID (Transmission completion<br>D)/KBCD (1st KCLKD)                                                                                        | 103      | H'00019C             |       |          |

| FSI                    | LFSII (Command reception)/(Write reception)                                                                                                  | 104      | H'0001A0             | ICRC1 | -        |