Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                                  |

|---------------------------------|----------------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                                         |

| Core Processor                  | MIPS-I                                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                                   |

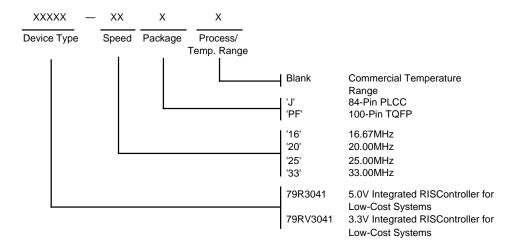

| Speed                           | 25MHz                                                                            |

| Co-Processors/DSP               | System Control; CP0                                                              |

| RAM Controllers                 | DRAM                                                                             |

| Graphics Acceleration           | No                                                                               |

| Display & Interface Controllers | -                                                                                |

| Ethernet                        | -                                                                                |

| SATA                            | -                                                                                |

| JSB                             | -                                                                                |

| /oltage - I/O                   | 5.0V                                                                             |

| Operating Temperature           | 0°C ~ 85°C (TC)                                                                  |

| Security Features               | -                                                                                |

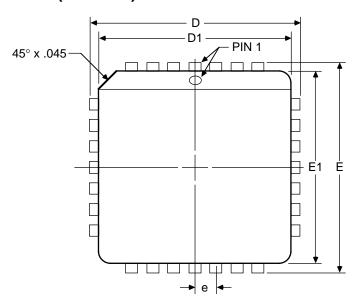

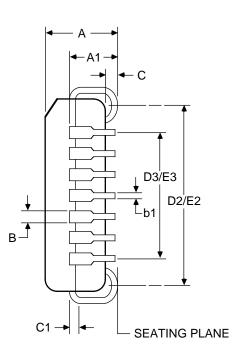

| Package / Case                  | 84-LCC (J-Lead)                                                                  |

| Supplier Device Package         | 84-PLCC (29.31x29.31)                                                            |

| Purchase URL                    | https://www.e-xfl.com/product-detail/renesas-electronics-america/idt79r3041-25j8 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **System Control Co-Processor**

The R3041 also integrates on-chip a System Control Coprocessor, CP0. CP0 manages the exception handling capability of the R3041, the virtual to physical address mapping of the R3041, and the programmable bus interface capabilities of the R3041. These topics are discussed in subsequent sections.

The R3041 does not include the optional TLB found in other members of the RISController family, but instead performs the same virtual to physical address mapping of the base version of the RISController family. These devices still support distinct kernel and user mode operation, but do not require page management software or an on-chip TLB, leading to a simpler software model and a lower-cost processor.

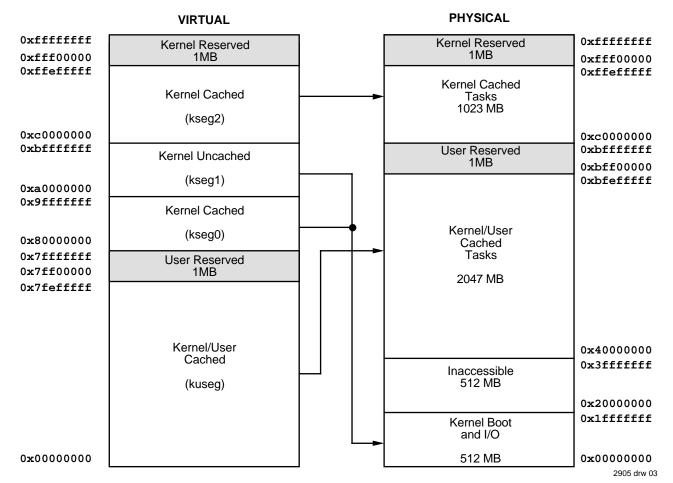

The memory mapping used by these devices is illustrated in Figure 3. Note that the reserved address spaces shown are for compatibility with future family members; in the current family members, references to these addresses are translated in the same fashion as their respective segments, with no traps or exceptions taken.

When using the base versions of the architecture, the system designer can implement a distinction between the user tasks and the kernel tasks, without having to execute page management software. This distinction can take the form of physical memory protection, accomplished by ad-

dress decoding, or in other system specific forms. In systems which do not wish to implement memory protection, and wish to have the kernel and user tasks operate out of a single unified memory space, upper address lines can be ignored by the address decoder, and thus all references will be seen in the lower gigabyte of the physical address space.

The R3041 adds additional resources into the on-chip CP0. These resources are detailed in the R3041 User's Manual. They allow kernel software to directly control activity of the processor internal resources and bus interface, and include:

- Cache Configuration Register: This register controls the data cache block size and miss refill algorithm.

- Bus Control Register: This register controls the behavior of the various bus interface signals.

- Count and Compare Registers: Together, these two registers implement a programmable 24-bit timer, which can be used for DRAM refresh or as a general purpose timer.

- Port Size Control Register: This register allows the kernel to indicate the port width of reads and writes to various sub-regions of the physical address space. Thus, the R3041 can interface directly with 8-, 16-, and 32-bit memory ports, including a mix of sizes, for both instruction and data references, without requiring additional external logic.

Figure 3. Virtual to Physical Mapping of Base Architecture Versions

R3041.

### **SYSTEM USAGE**

The IDT RISController family is specifically designed to easily connect to low-cost memory systems. Typical low-cost memory systems use inexpensive EPROMs, DRAMs, and application specific peripherals.

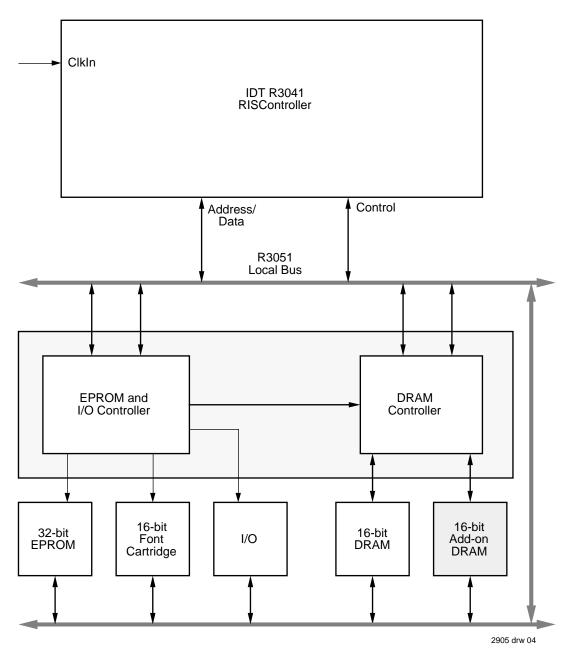

Figure 4 shows some of the flexibility inherent in the R3041. In this example system, which is typical of a laser printer, a 32-bit PROM interface is used due to the size of the PDL interpreter. An embedded system can optionally use an 8-bit

boot PROM instead. A 16-bit font/program cartridge interface is provided for add-in cards. A 16-bit DRAM interface is used for a low-cost page frame buffer. In this system example, a field or manufacturing upgrade to a 32-bit page frame buffer is supported by the boot software and DRAM controller. Embedded systems may optionally substitute SRAMs for the DRAMs. Finally various 8/16/32-bit I/O ports such as RS-232/422, SCSI, and LAN as well as the laser printer engine interface are supported. Such a system features a very low entry price, with a range of field upgrade options including the ability to upgrade to a more powerful member of the RISController family.

Figure 4. Typical R3041-Based Application

#### **DEVELOPMENT SUPPORT**

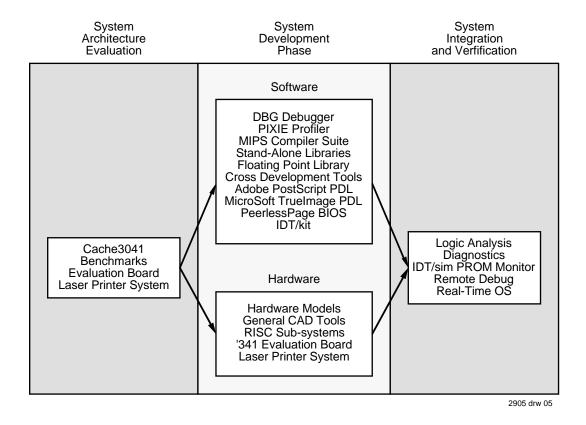

The IDT RISController family is supported by a rich set of development tools, ranging from system simulation tools through PROM monitor and debug support, applications software and utility libraries, logic analysis tools, and sub-system modules.

Figure 5 is an overview of the system development process typically used when developing R3041 applications. The RISController family is supported in all phases of project development. These tools allow timely, parallel development of hardware and software for RISController family based applications, and include tools such as:

Optimizing compilers from MIPS Technology, the acknowl-

- edged leader in optimizing compiler technology.

- Cross development tools, available in a variety of development environments.

- The high-performance IDT floating point emulation library software.

- The IDT Evaluation Board, which includes RAM, EPROM, I/O, and the IDT PROM Monitor.

- IDT Laser Printer System boards, which directly drive a lowcost print engine, and runs Adobe PostScript<sup>™</sup> Page Description Language

- Adobe PostScript Page Description Language running on the IDT RISController family.

- The IDT/sim<sup>™</sup> PROM Monitor, which implements a full PROM monitor (diagnostics, remote debug support, peek/

Figure 5. R3041 Development Environment

Programmable memory Port Widths: The R3041 allows

the kernel to partition the physical memory space into

various sub-regions, and to individually indicate the port

width of these sub-regions. Thus, the bus interface unit can

perform data packing and unpacking when communicating

with narrow memory sub-regions. For example, these features, can be used to allow the R3041 to interface with

narrow 8-bit boot PROMs, or to implement 16-bit only

memory systems.

#### THERMAL CONSIDERATIONS

The RISController family utilizes special packaging techniques to improve the thermal properties of high-speed processors. Thus, all versions of the RISController family are packaged in cavity down packaging.

The lowest cost members of the family use a standard cavity down, injection molded PLCC package (the "J" package). This package is used for all speeds of the R3041 family.

Higher speed and higher performance members of the RISController family utilize more advanced packaging techniques to dissipate power while remaining both low-cost and pin- and socket- compatible with the PLCC package. Thus, these members of the RISController family are available in the MQUAD package (the "MJ" package), which is an all aluminum package with the die attached to a normal copper lead-frame mounted to the aluminum casing. The MQUAD package is pin and form compatible with the PLCC package. Thus, designers can choose to utilize this package without changing their PCB.

|             | Airflow (ft/min) |     |     |     |     |      |  |  |  |  |

|-------------|------------------|-----|-----|-----|-----|------|--|--|--|--|

| ØCA         | 0                | 200 | 400 | 600 | 800 | 1000 |  |  |  |  |

| "J" Package | 29               | 26  | 21  | 18  | 16  | 15   |  |  |  |  |

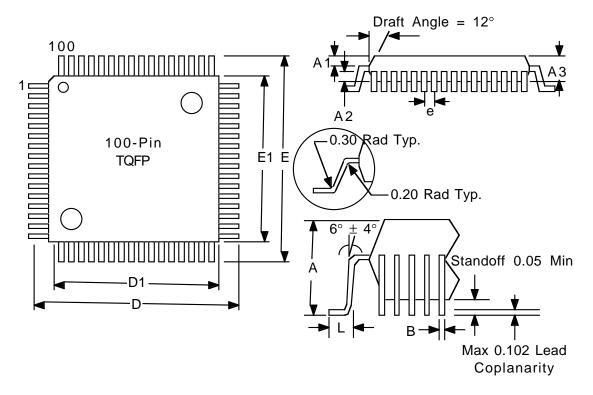

| TQFP        | 55               | 40  | 35  | 33  | 31  | 30   |  |  |  |  |

2905 tbl 02

Table 2. Thermal Resistance (ØcA) at Various Airflows

The members of the RISController family are guaranteed in a case temperature range of 0°C to +85°C. The type of package, speed (power) of the device, and airflow conditions, affect the equivalent ambient conditions which meet this specification.

The equivalent allowable ambient temperature, TA, can be calculated using the thermal resistance from case to ambient (ØCA) of the given package. The following equation relates ambient and case temperature:

$$TA = TC - P * ØCA$$

where P is the maximum power consumption at hot temperature, calculated by using the maximum Icc specification for the device.

Typical values for ØCA at various airflows are shown in Table 2 for the PLCC package.

#### NOTES ON SYSTEM DESIGN

The R3041 has been designed to simplify the task of highspeed system design. Thus, set-up and hold-time requirements have been kept to a minimum, allowing a wide variety of system interface strategies.

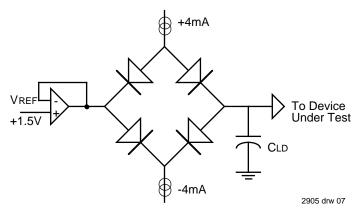

To minimize these AC parameters, the R3041 employs feedback from its SysClk output to the internal bus interface unit. This allows the R3041 to reference input signals to the reference clock seen by the external system. The SysClk output is designed to provide relatively large AC drive to minimize skew due to slow rise or fall times. A typical part will have less than 2ns rise or fall (10% to 90% signal times) when driving the test load.

Therefore, the system designer should use care when designing for direct SysClk use. Total loading (due to devices connected on the signal net and the routing of the net itself) should be minimized to ensure the SysClk output has a smooth and rapid transition. Long rise and/or fall times may cause a degradation in the speed capability of an individual device.

Similarly, the R3041 employs feedback on its ALE output to ensure adequate address hold time to ALE. The system designer should be careful when designing the ALE net to minimize total loading and to minimize skew between ALE and the A/D bus, which will ensure adequate address access latch time.

IDT's field and factory applications groups can provide the system designer with assistance for these and other design issues.

## **PIN DESCRIPTION**

| about the transfer is presented to the memory system to be captured using the ALE output. This information consists of:  Address(31:4):  The high-order address for the transfer is presented on A/D(31:4).  BE(3:0):  These strobes indicate which bytes of the 32-bit bus will be involved the transfer, and are presented on A/D(3:0). Bindicates that A/D(31:24) will be used, and BE(0) corresponds to A/D(7:0). These strobes are only valid for accesses to 32-bit whemenory ports. No that BE(3:0) can be held in-active during reads by setting the appropria bit of CP0; thus when latched, these signals can be directly used as Writer (3:0):  During the second phase, these signals are the data bus for the transaction.  Data(31:0):  During write cycles, the bus receives the data from the external resource, either a single data transaction or in a burst of four words, and places into the on-chip read buffer.  The byte lanes used during the transfer are a function of the datum siz the memory port width, and the system byte-ordering.  Addr(3:0)  O Low Address (3:0) A 4-bit bus which indicates which word/haltword/byte is currently expected by the memory port. Processor. For 32-bit port widths, only Addr(3:2) is valid during the transfer for 16-bit port widths, all of Addr(3:0) are valid. These address for 16-bit port widths, all of Addr(3:0) are valid. These address since shays contain the address of the current datum to be transferred. In writes and single datum reads, the addresses of the addresses of the addresses of the current datum to be transferred. In writes and single datum reads, the addresses of the addresses in the transfer are a function of the transfer are a function of the datum is wider than the target memory port. For quad word reads, these outputs function as a counter starting at '0000', and incrementing according to the width of the memory port.  During Reser, the Addr(3:0) pins act as Reset Configuration Mode bit inputs for the BootProm16, BootProm6, Reserveditigh, and ExtAddrificial options.  The R3041 Addr(1: | PIN NAME       | 1/0          |                                                                                                                                                                | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| about the transfer is presented to the memory system to be captured using the ALE output. This information consists of:  Address(31:4):  The high-order address for the transfer is presented on A/D(31:4).  BE(3:0):  These strobes indicate which bytes of the 32-bit bus will be involved the transfer, and are presented on A/D(31). Bit of decay that A/D(31:24) will be used, and BE(0) corresponds to A/D(7:0). These strobes are only valid for accesses to 32-bit will memory ports. No that BE(3:0) can be held in-active during reads by setting the appropria bit of CPC; thus when latched, these signals can be directly used as Writer (A) and be appropriate to the data to be stored and is drive from the internal write buffer.  Data(31:0):  During the second phase, those signals are the data bus for the transaction.  Data(31:0):  During write cycles, the bus receives the data from the external resource, either a single data transaction or in a burst of four words, and places into the on-chip read buffer.  The byte lanse used during the transfer are a function of the datum size the memory port width, and the system byte-ordering.  Addr(3:0)  O Low Address (3:0) A 4-bit bus which indicates which word/haltword/byte is currently expected by the processor. For 32-bit port widths, only Addr(3:2) is valid during the transfer for 16-bit port widths, only Addr(3:2) is valid during the transfer for 16-bit port widths, only Addr(3:2) is valid during the transfer for 16-bit port widths, only Addr(3:2) is valid during the transfer for 16-bit port widths, only Addr(3:2) is valid during the transfer of 16-bit port widths, only Addr(3:2) is valid during the transfer of 16-bit port widths, only Addr(3:2) is valid during the transfer of 16-bit port widths, only Addr(3:2) is valid during the transfer of 16-bit port widths, only Addr(3:2) is valid during the transfer of 16-bit port widths, only Addr(3:2) is valid during the transfer of 16-bit port widths, and 16-bit port widths, and 16-bit port widths, and 16-bit port widths, and 16-bit port wi | A/D(31:0)      | I/O          | in one phase, and which is us                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| BE(3:0): These strobes indicate which bytes of the 32-bit bus will be involved the transfer, and are presented on AD(3:0). BE(3) indicates that AD(3:1-2) will be used, and BE(0) corresponds to AD(7:0). These strobes are only valid for accesses to 32-bit wide memory ports. Not that BE(3:0) can be held in-active during reads by setting the appropria bit of CP0; thus when latched, these signals can be directly used as Writerable strobes.    During the second phase, these signals are the data bus for the transaction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |              | about the transfer is present                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| the transfer, and are presented on Ar(D(3:0), BE(3) indicates that AD(3:124) will be used, and BE(0) corresponds to AV(D(7:0). These strobes are only valid for accesses to 32-bit wide memory ports. No hat BE(3:0) can be held in-active during reads by setting the appropria bit of CP0; thus when latched, these signals can be directly used as Wife Enable strobes.  During the second phase, these signals are the data bus for the transaction.  Data(31:0):  During write cycles, the bus contains the data to be stored and is drive from the internal write buffer.  On read cycles, the bus receives the data from the external resource, either a single data transaction or in a burst of four words, and places into the on-chip read buffer.  The byte lanes used during the transfer are a function of the datum size the memory port width, and the system byte-ordering.  Addr(3:0)  O Low Address (3:0) A 4-bit bus which indicates which word/halfword/byte is currently expected by the processor. For 32-bit port widths, only Addr(3:2) is valid during the transfer; for 16-bit port widths, only Addr(3:1) are valid; for 8-bit port widths, all of Addr(3:0) are valid. These address lines always contain the address of the current datum to be transferred. In writes and single dature dash, the address of the current datum to be transferred. In writes and single dature reads, the addresses initial output the specific target address, and will increment if the size of the datum is wider than the target memory port. For quad word reads, these outputs function as a counter starting at '10000', and incrementing according to the width of the memory port.  During Reset, the Addr(3:0) pins act as Reset Configuration Mode bit inputs for the BootProm16, BootProm8, Reservedfield, and ExtAddrHold options.  The R3041 Addr(1:0) output pins are designated as the unconnected Rsvd(1:0) pins in the R3051 and R3081.  Diag Diagnostic Pin. This output indicates whether the current bus read transaction is due to an on-chip cache miss and whether the read is an instru |                |              | Address(31:4):                                                                                                                                                 | The high-order address for the transfer is presented on A/D(31:4).                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Data(31:0):  During write cycles, the bus contains the data to be stored and is drive from the internal write buffer.  On read cycles, the bus receives the data from the external resource, either a single data transaction or in a burst of four words, and places into the on-chip read buffer.  The byte lanes used during the transfer are a function of the datum siz the memory port width, and the system byte-ordering.  Addr(3:0)  O Low Address (3:0) A 4-bit bus which indicates which word/halfword/byte is currently expected by the processor. For 32-bit port widths, only Addr(3:2) is valid during the transfer; for 16-bit port widths, only Addr(3:0) are valid; for 8-bit port widths, all of Addr(3:0) are valid; for 8-bit port widths, all of Addr(3:0) are valid; for the specific target address, and will increment if the size of the datum is wider than the target memory port. For quad word reads, these outputs function as a counter starting at '0000', and incrementing according to the width of the memory port.  During Reset, the Addr(3:0) pins act as Reset Configuration Mode bit inputs for the BootProm16, BootProm8, ReservedHigh, and ExtRddrHold options.  The R3041 Addr(1:0) output pins are designated as the unconnected Rsvd(1:0) pins in the R3051 an R3081.  Diag  O Diagnostic Pin. This output indicates whether the current bus read transaction is due to an on-chip cache miss and whether the read is an instruction or data. It is time multiplexed as described below Cached/Uncached:  During the phase in which the A/D bus presents address information, the pin is an active high output which indicates whether or not the currer read is a result of a cache miss. The value of this pin at this time other than in read cycles is undefined.  A high at this time indicates an instruction reference, and a low indicate a data reference. The value of this pin at this time other than in read cycles is undefined.  The R3041 Diag output pin is designated as the Diag(1) output pin in the R3051 and R3081.  ALE  O Address Latch Enable: Used to  |                |              | BE(3:0):                                                                                                                                                       | A/D(31:24) will be used, and $\overline{BE(0)}$ corresponds to A/D(7:0). These strobes are only valid for accesses to 32-bit wide memory ports. Note that $\overline{BE(3:0)}$ can be held in-active during reads by setting the appropriate bit of CP0; thus when latched, these signals can be directly used as Write                                                                         |  |  |  |  |  |  |  |

| from the internal write buffer. On read cycles, the bus receives the data from the external resource, either a single data transaction or in a burst of four words, and places into the on-chip read buffer.  The byte lanes used during the transfer are a function of the datum siz the memory port width, and the system byte-ordering.  Addr(3:0)  O Low Address (3:0) A 4-bit bus which indicates which word/halfword/byte is currently expected by the processor. For 32-bit port widths, only Addr(3:2) is valid during the transfer; for 16-bit port widths, on Addr(3:1) are valid. These address sines always contain the address of the current datum to be transferred. In writes and single datum reads, the addresses initial output the specific target address, and will increment if the size of the datum is wider than the target memory port. For quad word reads, these outputs function as a counter starting at '0000', and incrementing according to the width of the memory port.  During Reset, the Addr(3:0) pins act as Reset Configuration Mode bit inputs for the BootProm16, BootProm8, ReservedHigh, and ExtAddrHold options.  The R3041 Addr(1:0) output pins are designated as the unconnected Rsvd(1:0) pins in the R3051 ar R3081.  Diag  O Diagnostic Pin. This output indicates whether the current bus read transaction is due to an on-chip cache miss and whether the read is an instruction or data. It is time multiplexed as described belowed the start of the bust reads and the start of a cache miss. The value of this pin at this time oth than in read cycles is undefined.  I/D:  A high at this time indicates an instruction reference, and a low indicate a data reference. The value of this pin at this time oth than in read cycles is undefined.  The R3041 Diag output pin is designated as the Diag(1) output pin in the R3051 and R3081.  ALE  O Address Latch Enable: Used to indicate that the A/D bus contains valid address information for the bus transaction. This signal is used by external logic to capture the address for the transfer, typica by us |                |              | During the second phase, th                                                                                                                                    | nese signals are the data bus for the transaction.                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Addr(3:0)  O Low Address (3:0) A 4-bit bus which indicates which word/halfword/byte is currently expected by the processor. For 32-bit port widths, only Addr(3:2) is valid during the transfer; for 16-bit port widths, only Addr(3:2) is valid during the transfer; for 16-bit port widths, only Addr(3:0) are valid. These address lines always contathe address of the current datum to be transferred. In writes and single datum reads, the addresses initia output the specific target address, and will increment if the size of the datum is wider than the target memory port. For quad word reads, these outputs function as a counter starting at '0000', and incrementing according to the width of the memory port.  During Reset, the Addr(3:0) pins act as Reset Configuration Mode bit inputs for the BootProm16, BootProm8, ReservedHigh, and ExtAddrHold options.  The R3041 Addr(1:0) output pins are designated as the unconnected Rsvd(1:0) pins in the R3051 are R3081.  Diag  O Diagnostic Pin. This output indicates whether the current bus read transaction is due to an on-chip cache miss and whether the read is an instruction or data. It is time multiplexed as described below Cached/Uncached:  During the phase in which the A/D bus presents address information, the pin is an active high output which indicates whether or not the current read is a result of a cache miss. The value of this pin at this time oth than in read cycles is undefined.  I/D:  A high at this time indicates an instruction reference, and a low indicate a data reference. The value of this pin at this time other than in read cycles is undefined.  The R3041 Diag output pin is designated as the Diag(1) output pin in the R3051 and R3081.  ALE  O Address Latch Enable: Used to indicate that the A/D bus contains valid address information for the bus transaction. This signal is used by external logic to capture the address for the transfer, typica by using transparent latches.  DataEnable: This signal indicates that the A/D bus is no longer being driven by the processor during  |                |              | Data(31:0):                                                                                                                                                    | On read cycles, the bus receives the data from the external resource, in either a single data transaction or in a burst of four words, and places it                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| processor. For 32-bit port widths, only Addr(3:2) is valid during the transfer; for 16-bit port widths, or Addr(3:1) are valid; for 8-bit port widths, all of Addr(3:0) are valid. These address intense always contains the address of the current dutum to be transferred. In writes and single datum reads, the addresses initial output the specific target address, and will increment if the size of the datum is wider than the target memory port. For quad word reads, these outputs function as a counter starting at '0000', and incrementing according to the width of the memory port.    I(1)   During Reset, the Addr(3:0) pins act as Reset Configuration Mode bit inputs for the BootProm16, BootProm8, ReservedHigh, and ExtAddrHold options.    The R3041 Addr(1:0) output pins are designated as the unconnected Rsvd(1:0) pins in the R3051 at R3081.    Diag   O   Diagnostic Pin. This output indicates whether the current bus read transaction is due to an onchip cache miss and whether the read is an instruction or data. It is time multiplexed as described below the pins are active high output which indicates whether or not the current ead is a result of a cache miss. The value of this pin at this time oth than in read cycles is undefined.    I/D:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |              |                                                                                                                                                                | The byte lanes used during the transfer are a function of the datum size, the memory port width, and the system byte-ordering.                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| BootProm8, ReservedHigh, and ExtAddrHold options.  The R3041 Addr(1:0) output pins are designated as the unconnected Rsvd(1:0) pins in the R3051 ar R3081.  Diag  O Diagnostic Pin. This output indicates whether the current bus read transaction is due to an onchip cache miss and whether the read is an instruction or data. It is time multiplexed as described below Cached/Uncached:  During the phase in which the A/D bus presents address information, the pin is an active high output which indicates whether or not the current read is a result of a cache miss. The value of this pin at this time oth than in read cycles is undefined.  I/D:  A high at this time indicates an instruction reference, and a low indicate a data reference. The value of this pin at this time other than in read cycles is undefined.  The R3041 Diag output pin is designated as the Diag(1) output pin in the R3051 and R3081.  ALE  O Address Latch Enable: Used to indicate that the A/D bus contains valid address information for the bus transaction. This signal is used by external logic to capture the address for the transfer, typica by using transparent latches.  DataEn  O Data Enable: This signal indicates that the A/D bus is no longer being driven by the processor during read cycles, and thus the external memory system may enable the drivers of the memory system onto this bus without having a bus conflict occur. During write cycles, or when no bus  tran                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Addr(3:0)      | 0            | processor. For 32-bit port w<br>Addr(3:1) are valid; for 8-bit<br>the address of the current dat<br>output the specific target ad<br>memory port. For quad wor | widths, only Addr(3:2) is valid during the transfer; for 16-bit port widths, only port widths, all of Addr(3:0) are valid. These address lines always contain turn to be transferred. In writes and single datum reads, the addresses initially dress, and will increment if the size of the datum is wider than the target dreads, these outputs function as a counter starting at '0000', and |  |  |  |  |  |  |  |

| Diag O Diagnostic Pin. This output indicates whether the current bus read transaction is due to an onchip cache miss and whether the read is an instruction or data. It is time multiplexed as described below Cached/Uncached:  During the phase in which the A/D bus presents address information, the pin is an active high output which indicates whether or not the current read is a result of a cache miss. The value of this pin at this time oth than in read cycles is undefined.  I/D:  A high at this time indicates an instruction reference, and a low indicate a data reference. The value of this pin at this time other than in read cycles is undefined.  The R3041 Diag output pin is designated as the Diag(1) output pin in the R3051 and R3081.  ALE  O Address Latch Enable: Used to indicate that the A/D bus contains valid address information for the bus transaction. This signal is used by external logic to capture the address for the transfer, typical by using transparent latches.  DataEn  O Data Enable: This signal indicates that the A/D bus is no longer being driven by the processor during read cycles, and thus the external memory system may enable the drivers of the memory system onto this bus without having a bus conflict occur. During write cycles, or when no bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                | <b>I</b> (1) |                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Cached/Uncached:  During the phase in which the A/D bus presents address information, the pin is an active high output which indicates whether or not the currer read is a result of a cache miss. The value of this pin at this time oth than in read cycles is undefined.  I/D:  A high at this time indicates an instruction reference, and a low indicate a data reference. The value of this pin at this time other than in read cycles is undefined.  The R3041 Diag output pin is designated as the Diag(1) output pin in the R3051 and R3081.  ALE  O  Address Latch Enable: Used to indicate that the A/D bus contains valid address information for the bus transaction. This signal is used by external logic to capture the address for the transfer, typica by using transparent latches.  DataEn  O  Data Enable: This signal indicates that the A/D bus is no longer being driven by the processor read cycles, and thus the external memory system may enable the drivers of the memory system onto this bus without having a bus conflict occur. During write cycles, or when no bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |              |                                                                                                                                                                | dr(1:0) output pins are designated as the unconnected Rsvd(1:0) pins in the R3051 and                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| pin is an active high output which indicates whether or not the currer read is a result of a cache miss. The value of this pin at this time oth than in read cycles is undefined.  I/D:  A high at this time indicates an instruction reference, and a low indicate a data reference. The value of this pin at this time other than in read cycles is undefined.  The R3041 Diag output pin is designated as the Diag(1) output pin in the R3051 and R3081.  ALE  O  Address Latch Enable: Used to indicate that the A/D bus contains valid address information for the bus transaction. This signal is used by external logic to capture the address for the transfer, typica by using transparent latches.  DataEn  O  Data Enable: This signal indicates that the A/D bus is no longer being driven by the processor during read cycles, and thus the external memory system may enable the drivers of the memory system onto this bus without having a bus conflict occur. During write cycles, or when no bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Diag           | 0            | •                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| a data reference. The value of this pin at this time other than in read cycles is undefined.  The R3041 Diag output pin is designated as the Diag(1) output pin in the R3051 and R3081.  ALE  O  Address Latch Enable: Used to indicate that the A/D bus contains valid address information for the bus transaction. This signal is used by external logic to capture the address for the transfer, typica by using transparent latches.  DataEn  O  Data Enable: This signal indicates that the A/D bus is no longer being driven by the processor during read cycles, and thus the external memory system may enable the drivers of the memory system onto this bus without having a bus conflict occur. During write cycles, or when no bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |              | Cached/Uncached:                                                                                                                                               | During the phase in which the A/D bus presents address information, this pin is an active high output which indicates whether or not the current read is a result of a cache miss. The value of this pin at this time other than in read cycles is undefined.                                                                                                                                   |  |  |  |  |  |  |  |

| ALE O Address Latch Enable: Used to indicate that the A/D bus contains valid address information for the bus transaction. This signal is used by external logic to capture the address for the transfer, typica by using transparent latches.  DataEn O Data Enable: This signal indicates that the A/D bus is no longer being driven by the processor during read cycles, and thus the external memory system may enable the drivers of the memory system onto this bus without having a bus conflict occur. During write cycles, or when no bus  tran                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |              | I∕Ō:                                                                                                                                                           | A high at this time indicates an instruction reference, and a low indicates a data reference. The value of this pin at this time other than in read cycles is undefined.                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| the bus transaction. This signal is used by external logic to capture the address for the transfer, typica by using transparent latches.  DataEn  O Data Enable: This signal indicates that the A/D bus is no longer being driven by the processor during read cycles, and thus the external memory system may enable the drivers of the memory system onto this bus without having a bus conflict occur. During write cycles, or when no bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |              | The R3041 Diag output pin                                                                                                                                      | is designated as the Diag(1) output pin in the R3051 and R3081.                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| during read cycles, and thus the external memory system may enable the drivers of the memory system onto this bus without having a bus conflict occur. During write cycles, or when no bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ALE            | 0            | the bus transaction. This sig                                                                                                                                  | nal is used by external logic to capture the address for the transfer, typically                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| action is occurring, this signal is negated, thus disabling the external memory drivers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | system onto th | during in    | read cycles, and thus the external out having a bus conflict occur. Do                                                                                         | memory system may enable the drivers of the memory uring write cycles, or when no bus trans-                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

#### NOTE:

Reset Configuration Mode bit input when Reset is asserted, normal signal function when Reset is de-asserted.

## **PIN DESCRIPTION (Continued):**

|                          |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

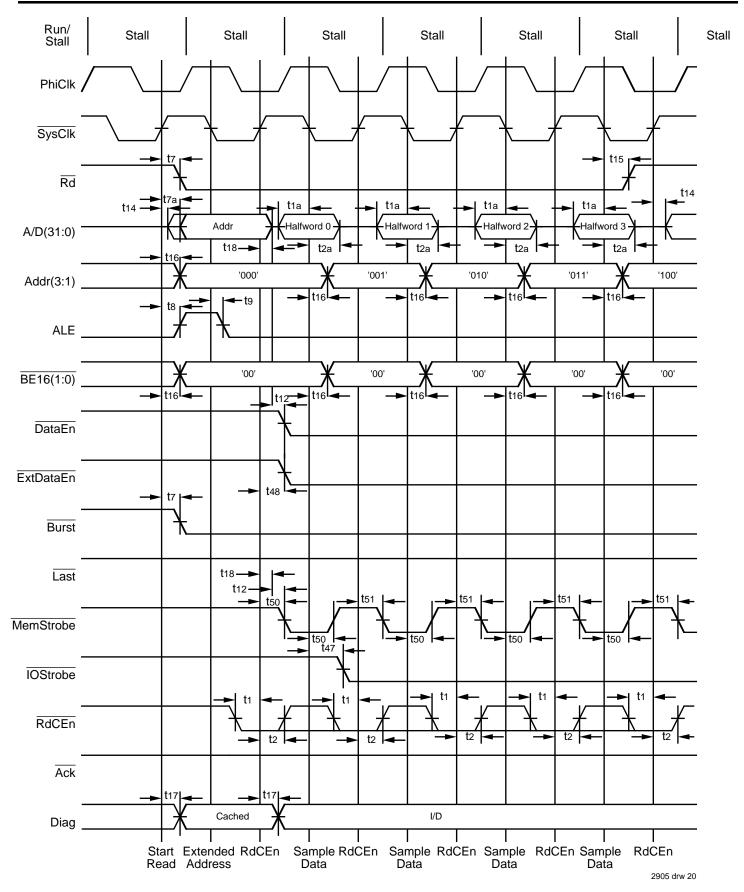

| Burst/<br>WrNear         | 0   | <b>Burst Transfer/Write Near:</b> On read transactions, the Burst signal indicates that the current bus read is requesting a block of four contiguous words from memory. This signal is asserted only in read cycles due to cache misses; it is asserted for all I-Cache miss read cycles, and for D-Cache miss read cycles if the 4-word data block refill option is selected in the CP0 Cache Config Register.                                                                                                          |

|                          |     | On write transactions, the WrNear output tells the external memory system that the bus interface unit is performing back-to-back write transactions to an address within the same 256 byte page as the prior write transaction. This signal is useful in memory systems which employ page mode or static column DRAMs, and allows nearby writes to be retired quickly.                                                                                                                                                    |

| Rd                       | 0   | Read: An output which indicates that the current bus transaction is a read.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Wr                       | 0   | Write: An output which indicates that the current bus transaction is a write.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Ack                      | I   | <b>Acknowledge:</b> An input which indicates to the device that the memory system has sufficiently processed the bus transaction. On write transactions, this signal indicates that the CPU may either progress to the next data item (for mini-burst writes of wide datums to narrow memories), or terminate the write cycle. On read transactions, this signal indicates that the memory system has sufficiently processed the read, and that the processor core may begin processing the data from this read transfer. |

| RdCEn                    | I   | <b>Read Buffer Clock Enable:</b> An input which indicates to the device that the memory system has placed valid data on the A/D bus, and that the processor may move the data into the on-chip Read Buffer.                                                                                                                                                                                                                                                                                                               |

| SysClk                   | 0   | <b>System Reference Clock:</b> An output from the CPU which reflects the timing of the internal processor "System" clock. This clock is used to control state transitions in the read buffer, write buffer, memory controller, and bus interface unit.                                                                                                                                                                                                                                                                    |

| BusReq                   | -   | <b>DMA Arbiter Bus Request:</b> An input to the device which requests that the CPU tri-state its bus interface signals so that they may be driven by an external master. The negation of this input relinquishes mastership back to the CPU.                                                                                                                                                                                                                                                                              |

| BusGnt                   | 0   | <b>DMA Arbiter Bus Grant.</b> An output from the CPU used to acknowledge that a BusReq has been detected, and that the bus is relinquished to the external master.                                                                                                                                                                                                                                                                                                                                                        |

|                          |     | The R3041 adds an additional DMA protocol, under the control of CP0. If the DMA Protocol is enabled, the R3041 can request that the external master relinquish bus mastership back to the processor by negating the BusGnt output early, and waiting for the BusReq input to be negated.                                                                                                                                                                                                                                  |

| SBrCond(3)/<br>IOStrobe  | I/O | <b>Branch Condition Port/IO Strobe:</b> The use of this signal depends on the setting of various bits of the CP0 Bus Control register. If BrCond mode is selected, this input is logically connected to CpCond(3), and can be used by the branch on co-processor condition instructions as an input port. The SBrCond(3) input has special internal logic to synchronize the input, and thus may be driven by asynchronous agents.                                                                                        |

|                          |     | If this pin is selected to function as $\overline{\text{IOStrobe}}$ , it may be asserted as an output on reads, writes, or both, as programmed into CP0. This strobe asserts in the second clock cycle of a transfer, and thus can be used to strobe various control signals on the bus interface.                                                                                                                                                                                                                        |

| SBrCond(2)/<br>ExtDataEn | I/O | <b>Branch Condition Port/Extended Data Enable:</b> The use of this signal depends on the settings in the CP0 Bus Control register. If BrCond mode is selected, this input is logically connected to CpCond(2), and can be used by the branch on co-processor condition instructions as an input port. The SBrCond(2) input has special internal logic to synchronize the input, and thus may be driven by asynchronous agents.                                                                                            |

|                          |     | If this pin is selected to function as Extended Data Enable, it may be asserted as an output on reads, writes, or both, as programmed into CP0. This strobe can be used as an extended data enable strobe, in that it is held asserted for one-half clock cycle after the negation of $\overline{Rd}$ or $\overline{Wr}$ . This signal may typically be used as a write enable control line for transceivers, as a write line for I/O, or as an address mux select for DRAMs.                                             |

| MemStrobe                | 0   | <b>Memory Strobe:</b> This active low output pulses low for each data read or written, as configured in the CP0 Bus Control register. Thus, it can be used as a read strobe, write strobe, or both, for SRAM type memories or for I/O devices.                                                                                                                                                                                                                                                                            |

|                          |     | The R3041 MemStrobe output pin is designated as the BrCond(0) input pin in the R3051 and R3081.                                                                                                                                                                                                                                                                                                                                                                                                                           |

## **PIN DESCRIPTION (Continued):**

| PIN NAME              | 1/0                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BE16(1:0)             | 0                       | Byte Enable Strobes for 16-bit Memory Port: These active low outputs are the byte lane strobes for accesses to 16-bit wide memory ports; they are not necessarily valid for 8- or 32-bit wide ports. If BE16(1) is asserted, then the most significant byte (either D(31:24) or D(15:8), depending on system endianness) is going to be used in this transfer. If BE16(0) is asserted, the least significant byte (D(23:16) or D(7:0)) will be used.                                           |

|                       |                         | $\overline{\text{BE16}(1:0)}$ can be held inactive (masked) during read transfers, according to the programming of the CP0 Bus Control register.                                                                                                                                                                                                                                                                                                                                               |

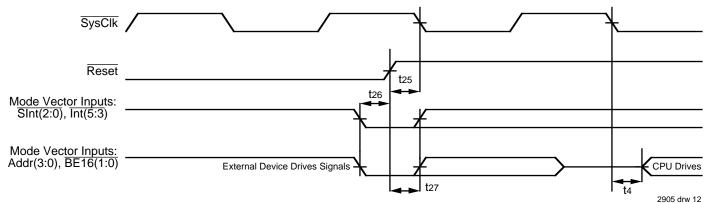

|                       | <b>[</b> (1)            | During $\overline{\text{Reset}}$ , the $\overline{\text{BE16}(1:0)}$ act as Reset Configuration Mode bit inputs for two ReservedHigh options.                                                                                                                                                                                                                                                                                                                                                  |

|                       |                         | The $\overline{\text{BE16}(1:0)}$ output pins are designated as the unconnected Rsvd(3:2) pins in the R3051 and R3081.                                                                                                                                                                                                                                                                                                                                                                         |

| Last                  | 0                       | <b>Last Datum in Mini-Burst:</b> This active low output indicates that this is the last datum transfer in a given transaction. It is asserted after the next to last $\overline{RdCEn}$ (reads) or $\overline{Ack}$ (writes), and is negated when $\overline{Rd}$ or $\overline{Wr}$ is negated.                                                                                                                                                                                               |

|                       |                         | The $\overline{Last}$ output pin is designated in the R3051 and R3081 as the Diag(0) output pin.                                                                                                                                                                                                                                                                                                                                                                                               |

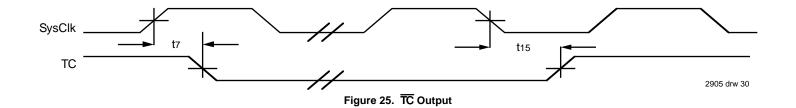

| TC                    | 0                       | <b>Terminal Count:</b> This is an active low output from the processor which indicates that the on-chip timer has reached its terminal count. It will remain low for either 1.5 clock cycles, or until software resets the timer, depending on the mode selected in the CP0 Bus Control register. Thus, the on-chip timer can function either as a free running timer for system functions such as DRAM refresh, or can operate as a software controlled time-slice timer, or real-time clock. |

|                       |                         | The $\overline{\text{TC}}$ output pin is designated in the R3051 as the BrCond(1) input pin, and in the R3081 as the Run pin output.                                                                                                                                                                                                                                                                                                                                                           |

| BusError              | -                       | <b>Bus Error:</b> Input to the bus interface unit to terminate a bus transaction due to an external bus error. This signal is only sampled during read and write operations. If the bus transaction is a read operation, then the CPU will take a bus error exception.                                                                                                                                                                                                                         |

| Int(5:3)<br>SInt(2:0) | 1                       | <b>Processor Interrupt:</b> During normal operation, these signals are logically the same as the Int(5:0) signals of the R3000A. During processor reset, these signals perform mode initialization of the CPU, but in a different (simpler) fashion than the interrupt signals on the original R3000A.                                                                                                                                                                                         |

|                       | <b>I</b> <sup>(1)</sup> | During Reset, Int(3) and SInt(0) act as Reset Configuration Mode bit inputs for the AddrDisplayAndForceCacheMiss and BigEndian options.                                                                                                                                                                                                                                                                                                                                                        |

|                       |                         | There are two types of interrupt inputs: the SInt inputs are internally synchronized by the processor, and may be driven by an asynchronous external agent. The direct interrupt inputs are not internally synchronized, and thus must be externally synchronized to the CPU. The direct interrupt inputs have one cycle lower latency than the synchronized interrupts.                                                                                                                       |

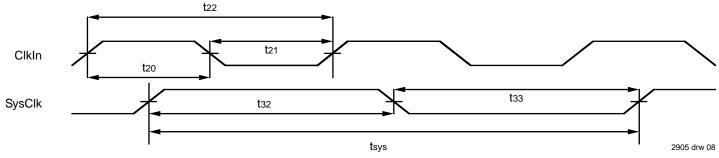

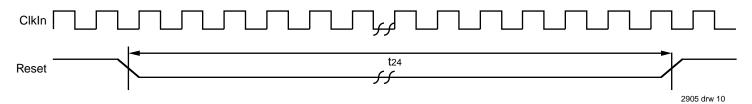

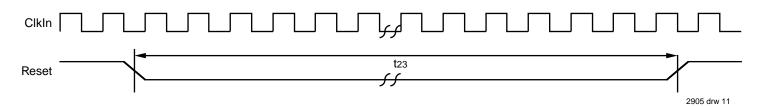

| ClkIn                 | 1                       | Master Clock Input: This is a double frequency input used to control the timing of the CPU.                                                                                                                                                                                                                                                                                                                                                                                                    |

| Reset                 | I                       | <b>Master Processor Reset:</b> This signal initializes the CPU. Reset initialization mode selection is performed during the last cycle of Reset.                                                                                                                                                                                                                                                                                                                                               |

| TriState              |                         | <b>Tri-State:</b> This input to the R3041 requests that the R3041 tri-state all of its outputs. In addition to those outputs tri-stated during DMA, tri-state will cause SysClk, TC, and BusGnt to tri-state. This signal is intended for use during board testing and emulation during debug and board manufacture.                                                                                                                                                                           |