#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XE

| Product Status                  | Obsolete                                                                         |

|---------------------------------|----------------------------------------------------------------------------------|

| Core Processor                  | MIPS-I                                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                                   |

| Speed                           | 33MHz                                                                            |

| Co-Processors/DSP               | System Control; CP0                                                              |

| RAM Controllers                 | DRAM                                                                             |

| Graphics Acceleration           | No                                                                               |

| Display & Interface Controllers | _                                                                                |

| Ethernet                        | -                                                                                |

| SATA                            | -                                                                                |

| USB                             | _                                                                                |

| Voltage - I/O                   | 5.0V                                                                             |

| Operating Temperature           | 0°C ~ 85°C (TC)                                                                  |

| Security Features               | -                                                                                |

| Package / Case                  | 100-LQFP                                                                         |

| Supplier Device Package         | 100-TQFP (14x14)                                                                 |

| Purchase URL                    | https://www.e-xfl.com/product-detail/renesas-electronics-america/idt79r3041-33pf |

|                                 |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### INTRODUCTION

The IDT RISController family is a series of high-performance 32-bit microprocessors featuring a high-level of integration, and targeted to high-performance but cost sensitive embedded processing applications. The RISController family is designed to bring the high-performance inherent in the MIPS RISC architecture into low-cost, simplified, power sensitive applications.

Thus, functional units have been integrated onto the CPU core in order to reduce the total system cost, rather than to increase the inherent performance of the integer engine. Nevertheless, the RISController family is able to offer 35MIPS of integer performance at 40MHz without requiring external SRAM or caches.

Further, the RISController family brings dramatic power reduction to these embedded applications, allowing the use of low-cost packaging. Thus, the RISController family allows customer applications to bring maximum performance at minimum cost.

The R3041 extends the range of price/performance achiev-

able with the RISController family, by dramatically lowering the cost of using the MIPS architecture. The R3041 is designed to achieve minimal system and components cost, yet maintain the high-performance inherent in the MIPS architecture. The R3041 also maintains pin and software compatibility with the RISController and R3081.

The RISController family offers a variety of price/performance features in a pin-compatible, software compatible family. Table 1 provides an overview of the current members of the RISController family. Note that the R3051, R3052, and R3081 are also available in pin-compatible versions that include a full-function memory management unit, including 64-entry TLB. The R3051/2 and R3081 are described in separate manuals and data sheets.

Figure 1 shows a block level representation of the functional units within the R3041. The R3041 can be viewed as the embodiment of a discrete solution built around the R3000A. By integrating this functionality on a single chip, dramatic cost and power reductions are achieved.

An overview of these blocks is presented here, followed with detailed information on each block.

| Device<br>Name | Instruction<br>Cache | Data<br>Cache | Floating<br>Point                                 | Bus<br>Options                         |

|----------------|----------------------|---------------|---------------------------------------------------|----------------------------------------|

| R3051          | 4kB                  | 2kB           | Software Emulation                                | Mux'ed A/D                             |

| R3052          | 8kB                  | 2kB           | Software Emulation                                | Mux'ed A/D                             |

| R3071<br>R3081 | 16kB<br>or 8kB       | 4kB<br>or 8kB | On-chip Hardware                                  | 1/2 frequency bus option               |

| R3041          | 2kB                  | 512B          | Software Emulation<br>Programmable timing support | 8-, 16-, and 32-bit port width support |

|                |                      |               |                                                   | 2905 tbl 01                            |

Table 1. Pin-Compatible RISController Family

#### **CPU Core**

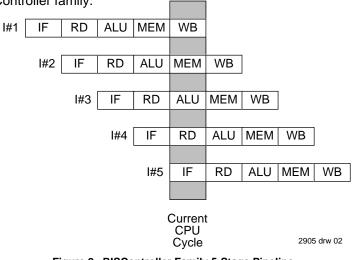

The CPU core is a full 32-bit RISC integer execution engine, capable of sustaining close to a single cycle execution rate. The CPU core contains a five stage pipeline, and 32 orthogonal 32-bit registers. The RISController family implements the MIPS-I Instruction Set Architecture (ISA). In fact, the execution engine of the R3041 is the same as the execution engine of the R3000A. Thus, the R3041 is binary compatible with those CPU engines, as well as compatible with other members of the RISController family. The execution engine of the RISController family uses a five-stage pipeline to achieve close to single cycle execution. A new instruction can be started in every clock cycle; the execution engine actually processes five instructions concurrently (in various pipeline stages). The five parts of the pipeline are the Instruction Fetch, Read register, ALU execution, Memory, and Write Back stages. Figure 2 shows the concurrency achieved by the RISController family pipeline.

R3041.

#### SYSTEM USAGE

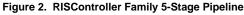

The IDT RISController family is specifically designed to easily connect to low-cost memory systems. Typical low-cost memory systems use inexpensive EPROMs, DRAMs, and application specific peripherals.

Figure 4 shows some of the flexibility inherent in the R3041. In this example system, which is typical of a laser printer, a 32bit PROM interface is used due to the size of the PDL interpreter. An embedded system can optionally use an 8-bit boot PROM instead. A 16-bit font/program cartridge interface is provided for add-in cards. A 16-bit DRAM interface is used for a low-cost page frame buffer. In this system example, a field or manufacturing upgrade to a 32-bit page frame buffer is supported by the boot software and DRAM controller. Embedded systems may optionally substitute SRAMs for the DRAMs. Finally various 8/16/32-bit I/O ports such as RS-232/ 422, SCSI, and LAN as well as the laser printer engine interface are supported. Such a system features a very low entry price, with a range of field upgrade options including the ability to upgrade to a more powerful member of the RISController family.

Figure 4. Typical R3041-Based Application

#### **DEVELOPMENT SUPPORT**

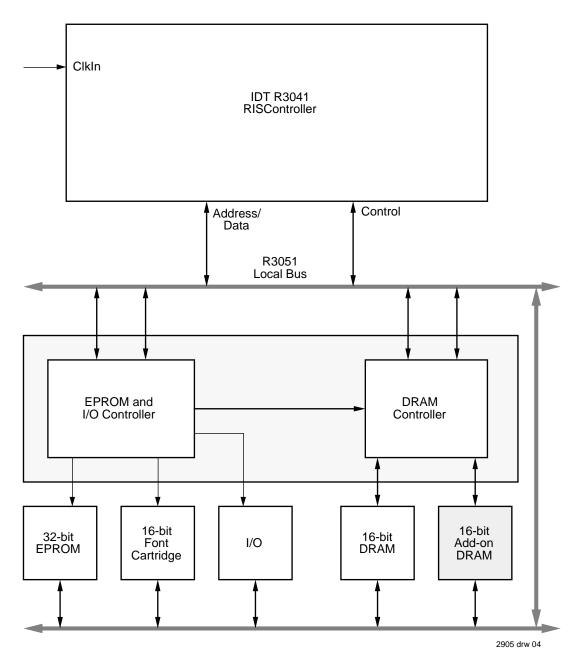

The IDT RISController family is supported by a rich set of development tools, ranging from system simulation tools through PROM monitor and debug support, applications software and utility libraries, logic analysis tools, and sub-system modules.

Figure 5 is an overview of the system development process typically used when developing R3041 applications. The RISController family is supported in all phases of project development. These tools allow timely, parallel development of hardware and software for RISController family based applications, and include tools such as:

· Optimizing compilers from MIPS Technology, the acknowl-

edged leader in optimizing compiler technology.

- Cross development tools, available in a variety of development environments.

- The high-performance IDT floating point emulation library software.

- The IDT Evaluation Board, which includes RAM, EPROM, I/O, and the IDT PROM Monitor.

- IDT Laser Printer System boards, which directly drive a lowcost print engine, and runs Adobe PostScript<sup>™</sup> Page Description Language

- Adobe PostScript Page Description Language running on the IDT RISController family.

- The IDT/sim<sup>™</sup> PROM Monitor, which implements a full PROM monitor (diagnostics, remote debug support, peek/

2905 drw 05

Figure 5. R3041 Development Environment

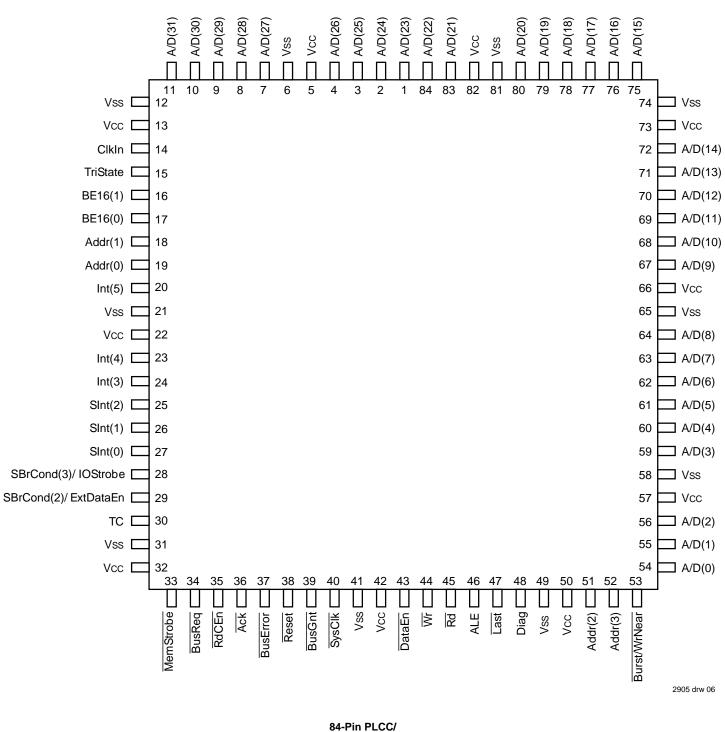

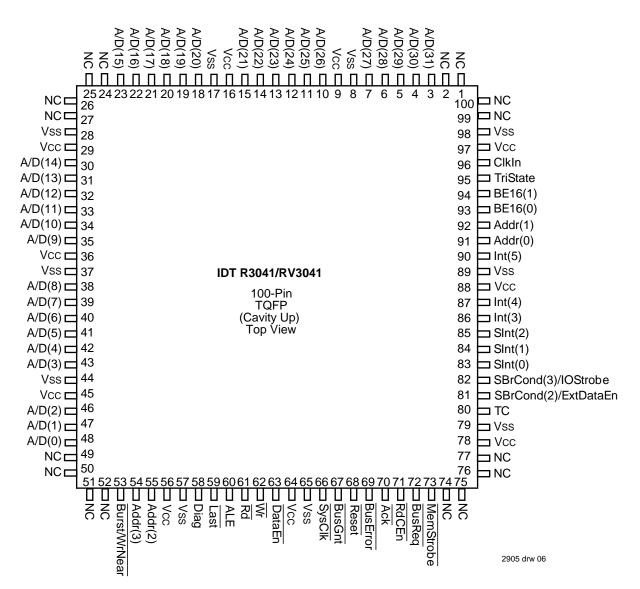

#### **PIN CONFIGURATIONS**

Top View (Cavity Down)

### **PIN CONFIGURATIONS**

### **PIN DESCRIPTION**

| PIN NAME  | I/O          |                                                                                                                                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------|--------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A/D(31:0) | I/O          |                                                                                                                                  | e multiplexed bus which indicates the desired address for a bus transaction<br>and to transmit data between the CPU and external memory resources during                                                                                                                                                                                                                                                                                                                                                                 |

|           |              |                                                                                                                                  | are logically separated into two phases: during the first phase, information ted to the memory system to be captured using the ALE output. This                                                                                                                                                                                                                                                                                                                                                                          |

|           |              | Address(31:4):                                                                                                                   | The high-order address for the transfer is presented on A/D(31:4).                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           |              | BE(3:0):                                                                                                                         | These strobes indicate which bytes of the 32-bit bus will be involved in the transfer, and are presented on A/D(3:0). $\overline{BE(3)}$ indicates that A/D(31:24) will be used, and $\overline{BE(0)}$ corresponds to A/D(7:0). These strobes are only valid for accesses to 32-bit wide memory ports. Note that $\overline{BE(3:0)}$ can be held in-active during reads by setting the appropriate bit of CP0; thus when latched, these signals can be directly used as Write Enable strobes.                          |

|           |              | During the second phase, the                                                                                                     | nese signals are the data bus for the transaction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           |              | Data(31:0):                                                                                                                      | During write cycles, the bus contains the data to be stored and is driver<br>from the internal write buffer.<br>On read cycles, the bus receives the data from the external resource, in<br>either a single data transaction or in a burst of four words, and places is<br>into the on-chip read buffer.                                                                                                                                                                                                                 |

|           |              |                                                                                                                                  | The byte lanes used during the transfer are a function of the datum size the memory port width, and the system byte-ordering.                                                                                                                                                                                                                                                                                                                                                                                            |

| Addr(3:0) | 0            | processor. For 32-bit port w<br>Addr(3:1) are valid; for 8-bit<br>the address of the current da<br>output the specific target ad | bus which indicates which word/halfword/byte is currently expected by the<br>vidths, only Addr(3:2) is valid during the transfer; for 16-bit port widths, only<br>port widths, all of Addr(3:0) are valid. These address lines always contain<br>rum to be transferred. In writes and single datum reads, the addresses initially<br>dress, and will increment if the size of the datum is wider than the target<br>d reads, these outputs function as a counter starting at '0000', and<br>he width of the memory port. |

|           | <b>I</b> (1) | During Reset, the Addr(3:0)<br>BootProm8, ReservedHigh,                                                                          | pins act as Reset Configuration Mode bit inputs for the $\overline{\text{BootProm16}}$ , and $\overline{\text{ExtAddrHold}}$ options.                                                                                                                                                                                                                                                                                                                                                                                    |

|           |              | The R3041 Addr(1:0) outpu<br>R3081.                                                                                              | pins are designated as the unconnected Rsvd(1:0) pins in the R3051 and                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Diag      | 0            | •                                                                                                                                | It indicates whether the current bus read transaction is due to an on-<br>the read is an instruction or data. It is time multiplexed as described below                                                                                                                                                                                                                                                                                                                                                                  |

|           |              | Cached/Uncached:                                                                                                                 | During the phase in which the A/D bus presents address information, this pin is an active high output which indicates whether or not the current read is a result of a cache miss. The value of this pin at this time othe than in read cycles is undefined.                                                                                                                                                                                                                                                             |

|           |              | ₩ <u>D</u> :                                                                                                                     | A high at this time indicates an instruction reference, and a low indicates<br>a data reference. The value of this pin at this time other than in read<br>cycles is undefined.                                                                                                                                                                                                                                                                                                                                           |

|           |              | The R3041 Diag output pin                                                                                                        | is designated as the Diag(1) output pin in the R3051 and R3081.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ALE       | 0            |                                                                                                                                  | sed to indicate that the A/D bus contains valid address information for<br>nal is used by external logic to capture the address for the transfer, typically<br>s.                                                                                                                                                                                                                                                                                                                                                        |

| DataEn    | O            |                                                                                                                                  | dicates that the A/D bus is no longer being driven by the processor memory system may enable the drivers of the memory                                                                                                                                                                                                                                                                                                                                                                                                   |

|           |              | hout having a bus conflict occur. D                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

1. Reset Configuration Mode bit input when Reset is asserted, normal signal function when Reset is de-asserted.

## ABSOLUTE MAXIMUM RATINGS<sup>(1, 3)</sup> R3041

| Symbol | Rating                                  | Commercial   | Unit |

|--------|-----------------------------------------|--------------|------|

| Vterm  | Terminal Voltage with<br>Respect to GND | -0.5 to +7.0 | V    |

| Тс     | Operating Case Temperature              | 0 to +85     | °C   |

| TBIAS  | Temperature Under Bias                  | –55 to +125  | °C   |

| Тѕтс   | Storage Temperature                     | -55 to +125  | °C   |

| Vin    | Input Voltage                           | -0.5 to +7.0 | V    |

#### NOTES:

2905 tbl 06 1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS

may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. VIN minimum = -3.0V for pulse width less than 15ns. VIN should not exceed Vcc +0.5 Volts.

3. Not more than one output should be shorted at a time. Duration of the short should not exceed 30 seconds.

### **AC TEST CONDITIONS R3041**

| Symbol | Parameter          | Min. | Max. | Unit        |

|--------|--------------------|------|------|-------------|

| Viн    | Input HIGH Voltage | 3.0  |      | V           |

| VIL    | Input LOW Voltage  | —    | 0    | V           |

| Vihs   | Input HIGH Voltage | 3.5  | —    | V           |

| VILS   | Input LOW Voltage  | —    | 0    | V           |

|        |                    |      |      | 2905 tbl 08 |

### **RECOMMENDED OPERATING TEMPERATURE AND SUPPLY VOLTAGE**

| Grade      | Temperature  | GND | Vcc     |

|------------|--------------|-----|---------|

| Commercial | 0°C to +85°C | 0V  | 5.0 ±5% |

|            | (Case)       |     |         |

2905 tbl 07

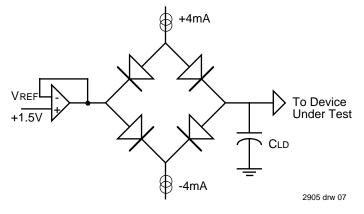

# **OUTPUT LOADING FOR AC TESTING**

| Signal      | Cld         |

|-------------|-------------|

| All Signals | 25 pF       |

|             | 2905 tbl 09 |

## DC ELECTRICAL CHARACTERISTICS R3041 — (Tc = 0°C to +85°C, Vcc = +5.0V ±5%)

|        |                                     |                        | 16.67MHz |      | 16.67MHz 20MHz |      | 25MHz |      | 33MHz |      |      |

|--------|-------------------------------------|------------------------|----------|------|----------------|------|-------|------|-------|------|------|

| Symbol | Parameter                           | Test Conditions        | Min.     | Max. | Min.           | Max. | Min.  | Max. | Min.  | Max. | Unit |

| Vон    | Output HIGH Voltage                 | Vcc = Min., Iон = -4mA | 3.5      | —    | 3.5            | —    | 3.5   | —    | 3.5   |      | V    |

| Vol    | Output LOW Voltage                  | Vcc = Min., IoL = 4mA  | —        | 0.4  | _              | 0.4  |       | 0.4  |       | 0.4  | V    |

| Vih    | Input HIGH Voltage <sup>(3)</sup>   | _                      | 2.0      | —    | 2.0            | —    | 2.0   | _    | 2.0   | ų    | V    |

| VIL    | Input LOW Voltage <sup>(1)</sup>    | _                      | —        | 0.8  |                | 0.8  |       | 0.8  | —     | 0.8  | V    |

| Vihs   | Input HIGH Voltage <sup>(2,3)</sup> | _                      | 3.0      |      | 3.0            | _    | 3.0   | _    | 3.0   |      | V    |

| VILS   | Input LOW Voltage <sup>(1,2)</sup>  | _                      | —        | 0.4  |                | 0.4  | _     | 0.4  |       | 0.4  | V    |

| CIN    | Input Capacitance <sup>(4)</sup>    | _                      | —        | 10   | _              | 10   |       | 10   |       | 10   | pF   |

| Соит   | Output Capacitance <sup>(4)</sup>   | _                      | —        | 10   | _              | 10   |       | 10   | +     | 10   | pF   |

| lcc    | Operating Current                   | Vcc = 5V, Tc = 25°C    | _        | 225  | _              | 250  | _     | 300  | T     | 370  | mA   |

| Ін     | Input HIGH Leakage                  | VIH = VCC              | _        | 100  | —              | 100  | _     | 100  |       | 100  | μΑ   |

| lı∟    | Input LOW Leakage                   | VIL = GND              | -100     | _    | -100           | _    | -100  | _    | -100  |      | μΑ   |

| loz    | Output Tri-state Leakage            | VOH = 2.4V, VOL = 0.5V | -100     | 100  | -100           | 100  | -100  | 100  | -100  | 100  | μΑ   |

#### NOTES:

1. VIL Min. = -3.0V for pulse width less than 15ns. VIL should not fall below -0.5 volts for larger periods.

2. VIHS and VILS apply to ClkIn and Reset.

3. VIH should not be held above Vcc + 0.5 volts.

4. Guaranteed by design.

2905 tbl 10

# AC ELECTRICAL CHARACTERISTICS R3041 <sup>(1, 2, 3)</sup> (Tc = 0°C to +85°C, Vcc = +5.0V ±5%)

|        |                                                      |                                                          | 16.6    | 67MHz   | 20      | MHz     | 25N     | //Hz  | 33M      | IHz     |      |

|--------|------------------------------------------------------|----------------------------------------------------------|---------|---------|---------|---------|---------|-------|----------|---------|------|

| Symbol | Signals                                              | Description                                              | Min.    | Max.    | Min.    | Max.    | Min.    | Max.  | Min.     | Max.    | Unit |

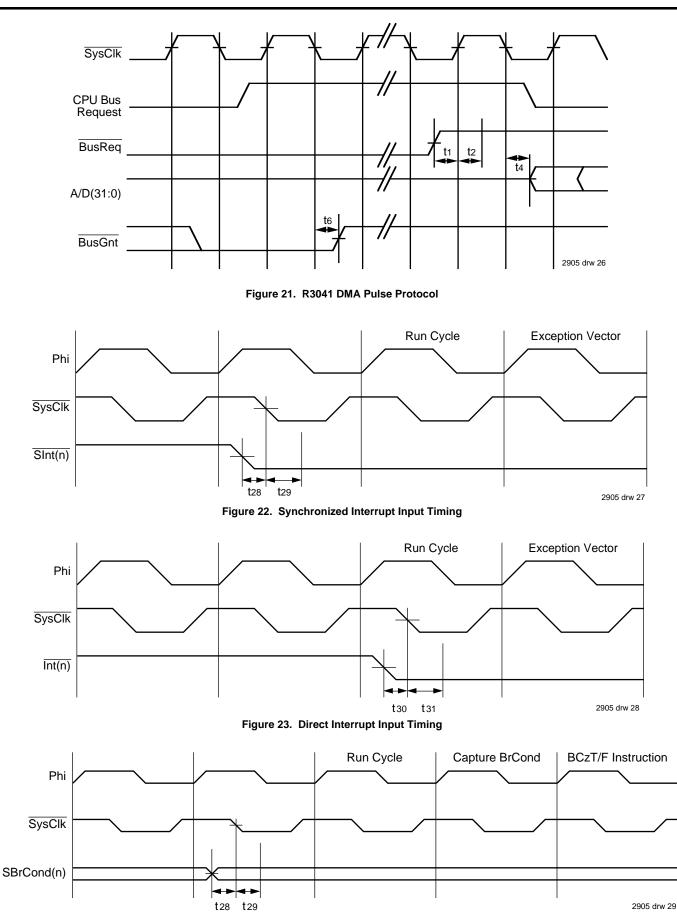

| t1     | BusReq, Ack, BusError, RdCEn                         | Set-up to SysClk rising                                  | 11      | _       | 8       | _       | 5.5     | _     | 5.5      | +       | ns   |

| t1a    | A/D                                                  | Set-up to SysClk falling                                 | 12      | _       | 9       | _       | 7       | _     | 7        | +       | ns   |

| t2     | BusReq, Ack, BusError, RdCEn                         | Hold from SysClk rising                                  | 4       | _       | 3       | _       | 2.5     | _     | 2.5      |         | ns   |

| t2a    | A/D                                                  | Hold from SysClk falling                                 | 2       | _       | 2       | _       | 1       | _     | 1        | +       | ns   |

| t3     | A/D, Addr, Diag, ALE, Wr<br>Burst/WrNear, Rd, DataEn | Tri-state from SysClk rising<br>(after driven condition) |         | 13      | _       | 10      | —       | 10    |          | 10      | ns   |

| t4     | A/D, Addr, Diag, ALE, Wr<br>Burst/WrNear, Rd, DataEn | Driven from SysClk falling (after tri-state condition)   | _       | 13      | —       | 10      | —       | 10    | -        | 10      | ns   |

| t5     | BusGnt                                               | Asserted from SysClk rising                              | _       | 10      | _       | 8       | _       | 7     | _        | 7       | ns   |

| t6     | BusGnt                                               | Negated from SysClk falling                              | _       | 10      | _       | 8       | _       | 7     | _        | 7       | ns   |

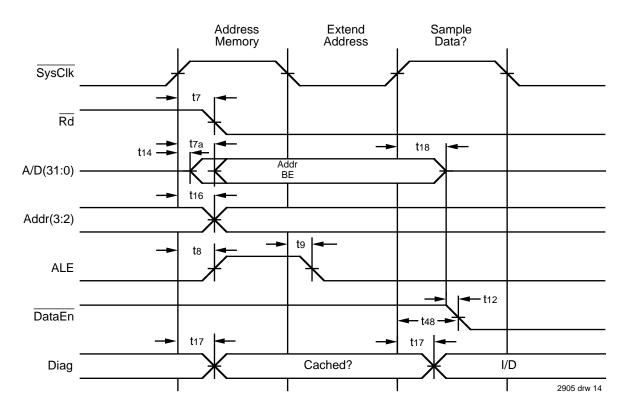

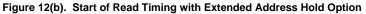

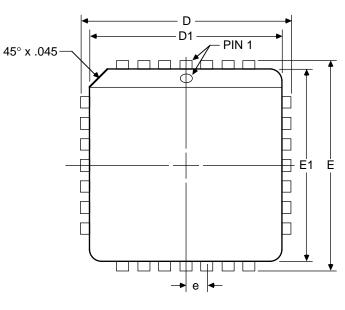

| t7     | Wr, Rd, Burst/WrNear, TC                             | Valid from SysClk rising                                 | _       | 8       | _       | 6       | _       | 5     |          | 5       | ns   |

| t7a    | A/D                                                  | Valid from SysClk rising                                 | _       | 12      | _       | 9       | _       | 8     | -        | 8       | ns   |

| t7b    | Last                                                 | Valid from SysClk rising                                 | _       | 12      | _       | 9       | _       | 8     | 1        | 8       | ns   |

| t8     | ALE                                                  | Asserted from SysClk rising                              | _       | 5       | —       | 4       | _       | 4     |          | 4       | ns   |

| t9     | ALE                                                  | Negated from SysClk falling                              | _       | 5       | —       | 4       | _       | 4     | +        | 4       | ns   |

| t10    | A/D                                                  | Hold from ALE negated                                    | 2       |         | 2       | _       | 2       | _     | 1.5      | 7       | ns   |

| t11    | DataEn                                               | Asserted from SysClk                                     | _       | 19      | _       | 15      | _       | 15    |          | 15      | ns   |

| t12    | DataEn                                               | Asserted from A/D tri-state <sup>(4)</sup>               | 0       |         | 0       | _       | 0       | _     | 0        | _       | ns   |

| t14    | A/D                                                  | Driven from SysClk rising <sup>(4)</sup>                 | 0       |         | 0       | _       | 0       | _     | 0        |         | ns   |

| t15    | Wr, Rd, DataEn, Burst/WrNear,<br>Last, TC            | Negated from SysClk falling                              | _       | 9       | _       | 7       | _       | 6     | <u> </u> | 6       | ns   |

| t16    | Addr(3:0), BE 16(1:0)                                | Valid from SysClk                                        | _       | 11      | _       | 8       | _       | 7     | —        | 7       | ns   |

| t17    | Diag                                                 | Valid from SysClk                                        | _       | 15      | _       | 12      | _       | 11    | _        | 11      | ns   |

| t18    | A/D                                                  | Tri-state from SysClk                                    | _       | 13      | _       | 10      | _       | 10    | _        | 10      | ns   |

| t19    | A/D                                                  | SysClk to data out                                       | _       | 16      | _       | 13      | _       | 12    | +        | 12      | ns   |

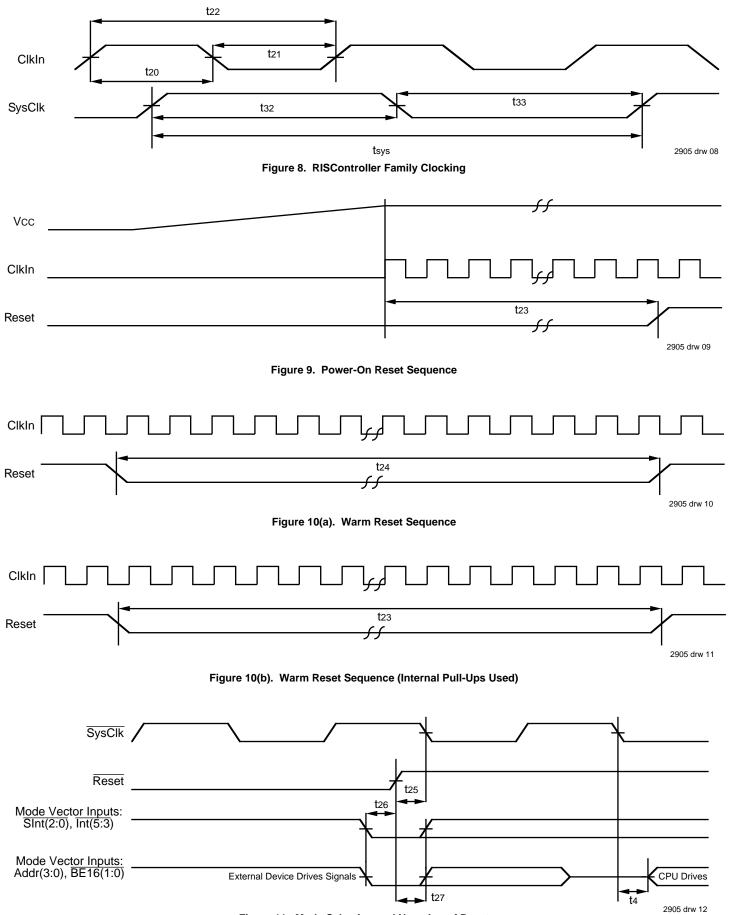

| t20    | ClkIn                                                | Pulse Width High                                         | 12      |         | 10      | _       | 8       | _     | 6.5      | _       | ns   |

| t21    | ClkIn                                                | Pulse Width Low                                          | 12      |         | 10      |         | 8       | _     | 6.5      |         | ns   |

| t22    | ClkIn                                                | Clock Period                                             | 30      | 250     | 25      | 250     | 20      | 250   | 15       | 250     | ns   |

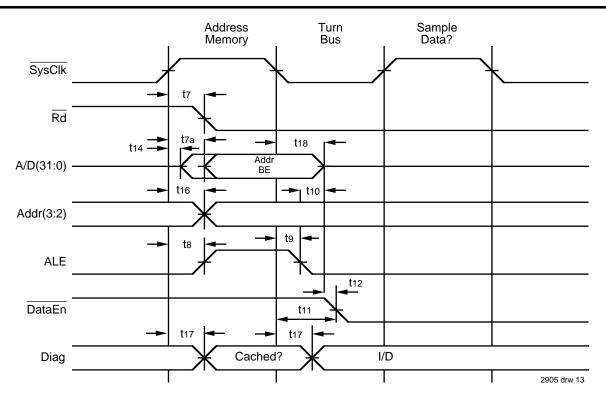

| t23    | Reset                                                | Pulse Width from Vcc valid                               | 200     |         | 200     | _       | 200     | _     | 200      | _       | μs   |

| t24    | Reset                                                | Minimum Pulse Width                                      | 32      |         | 32      | _       | 32      | _     | 32       | _       | sys  |

| t25    | Reset                                                | Set-up to SysClk falling                                 | 8       |         | 6       | _       | 5       | _     | 5        |         | ns   |

| t26    | Int                                                  | Mode set-up to Reset rising                              | 8       |         | 6       | _       | 5       | _     | 5        | +       | ns   |

| t27    | Int                                                  | Mode hold from Reset rising                              | 2.5     |         | 2.5     | _       | 2.5     | _     | 2.5      | +       | ns   |

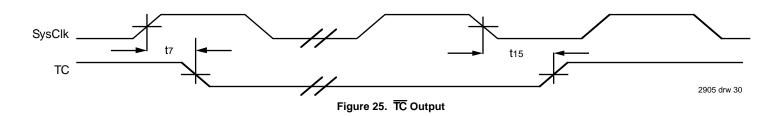

| t28    | SInt, SBrCond                                        | Set-up to SysClk falling                                 | 8       | _       | 6       | _       | 5       | _     | 5        | _       | ns   |

| t29    | SInt, SBrCond                                        | Hold from SysClk falling                                 | 4       |         | 3       | _       | 3       | _     | 3        | 1       | ns   |

| t30    | Int, BrCond                                          | Set-up to SysClk falling                                 | 8       | _       | 6       | _       | 5       | _     | 5        |         | ns   |

| t31    | Int, BrCond                                          | Hold from SysClk falling                                 | 4       | _       | 3       | _       | 3       | _     | 3        | 4       | ns   |

| tsys   | SysClk                                               | Pulse Width                                              | 2*t22   | 2*t22   | 2*t22   | 2*t22   | 2*t22   | 2*t22 | 2*t22    | 2*t22   | ns   |

| t32    | SysClk                                               | Clock High Time                                          | t22 - 2 | t22 + 2 | t22 - 2 | t22 + 2 | t22 - 2 |       |          | t22 + 2 | ns   |

| t33    | SysClk                                               | Clock Low Time                                           |         |         |         | t22 + 2 |         |       |          |         |      |

2905 tbl 11

## AC ELECTRICAL CHARACTERISTICS R3041 (CONT.)

|         |                   |                                                          | 16.6 | 16.67MHz 20MH |      | 20MHz |      | MHz  | 33MHz     |             |

|---------|-------------------|----------------------------------------------------------|------|---------------|------|-------|------|------|-----------|-------------|

| Symbol  | Signals           | Description                                              | Min. | Max.          | Min. | Max.  | Min. | Max. | Min. Max. | Unit        |

| t45     | ExtDataEn         | Tri-state from SysClk rising<br>(after driven condition) | -    | 13            | -    | 10    | -    | 10   |           | ns          |

| t46     | ExtDataEn         | Driven from SysClk falling<br>(after driven condition)   | -    | 13            | -    | 10    | -    | 10   |           | ns          |

| t47     | IOStrobe          | Valid from SysClk falling                                | _    | 10            | —    | 8     | _    | 7    | + 7       | ns          |

| t48     | ExtDataEn, DataEn | Asserted from SysClk rising                              | _    | 15            | —    | 12    | _    | 9    | - 9       | ns          |

| t49     | ExtDataEn         | Negated from SysClk rising                               | _    | 9             | —    | 7     | -    | 6    | 6         | ns          |

| t50     | MemStrobe         | Asserted from SysClk rising                              | _    | 19            | —    | 15    | _    | 15   | 15        | ns          |

| t51     | MemStrobe         | Negated from SysClk falling                              | _    | 19            | —    | 15    | -    | 15   | - 15      | ns          |

| t52     | MemStrobe         | Asserted from Addr(3:0) valid <sup>(4)</sup>             | 0    | _             | 0    | _     | 0    | _    | 0 -       | ns          |

| tderate | All outputs       | Timing deration for loading over 25pF <sup>(4, 5)</sup>  | -    | 0.5           | -    | 0.5   | -    | 0.5  | - 0.5     | ns/<br>25pF |

| NOTES:  | I                 | · · ·                                                    | 1    |               | 1    |       | 1    |      | 2         | 2905 tb     |

1. All timings referenced to 1.5 Volts, with a rise and fall time of less than 2.5ns.

2. All outputs tested with 25pF loading.

3. The AC values listed here reference timing diagrams contained in the R3041 Hardware User's Manual.

4. Guaranteed by design.

5. This parameter is used to derate the AC timings according to the loading of the system. This parameter provides a deration for loads over the specified test condition; that is, the deration factor is applied for each 25pF over the specified test load condition.

6. Timings t34 - t44 are reserved for other RISController family members.

# ABSOLUTE MAXIMUM RATINGS<sup>(1, 3)</sup> RV3041

| Symbol | Rating                                  | Commercial   | Unit        |

|--------|-----------------------------------------|--------------|-------------|

| Vterm  | Terminal Voltage with<br>Respect to GND | -0.5 to +7.0 | V           |

| Тс     | Operating Case Temperature              | 0 to +85     | °C          |

| TBIAS  | Temperature Under Bias                  | -55 to +125  | °C          |

| Tstg   | Storage Temperature                     | -55 to +125  | °C          |

| Vin    | Input Voltage                           | -0.5 to +7.0 | V           |

| NOTES: |                                         |              | 2905 tbl 06 |

- 1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. VIN minimum = -3.0V for pulse width less than 15ns. VIN should not exceed Vcc +0.5 Volts.

- 3. Not more than one output should be shorted at a time. Duration of the short should not exceed 30 seconds.

# **AC TEST CONDITIONS RV3041**

| Symbol | Parameter          | Min. | Max. | Unit |

|--------|--------------------|------|------|------|

| Vih    | Input HIGH Voltage | 3.0  |      | V    |

| VIL    | Input LOW Voltage  |      | 0    | V    |

| VIHS   | Input HIGH Voltage | 3.0  | _    | V    |

| VILS   | Input LOW Voltage  | _    | 0    | V    |

2905 tbl 08

### **RECOMMENDED OPERATING TEMPERATURE AND SUPPLY VOLTAGE**

| Grade      | Temperature  | GND | Vcc         |

|------------|--------------|-----|-------------|

| Commercial | 0°C to +85°C | 0V  | 3.3 ±5%     |

| RV3041     | (Case)       |     |             |

|            |              |     | 2905 tbl 07 |

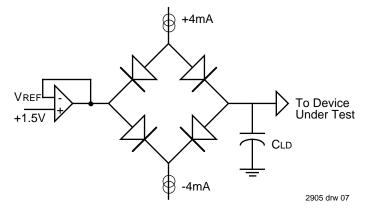

# OUTPUT LOADING FOR AC TESTING

| Signal      | Cld         |

|-------------|-------------|

| All Signals | 25 pF       |

|             | 2905 tbl 09 |

|         |                     |                                                          | 16.67 MHz |         | 20 MHz  |         | 25MHz   |         | 33MHz    |         |             |

|---------|---------------------|----------------------------------------------------------|-----------|---------|---------|---------|---------|---------|----------|---------|-------------|

| Symbol  | Signals             | Description                                              | Min.      | Max.    | Min.    | Max.    | Min.    | Max.    | Min.     | Max.    | Uni         |

| t18     | A/D                 | Tri-state from SysClk                                    | _         | 13      |         | 10      | _       | 10      | —        | 10      | ns          |

| t19     | A/D                 | SysClk to data out                                       | _         | 16      | _       | 13      | _       | 12      | _        | 12      | ns          |

| t20     | ClkIn               | Pulse Width High                                         | 12        |         | 10      |         | 8       |         | 6.5      | -       | ns          |

| t21     | ClkIn               | Pulse Width Low                                          | 12        | _       | 10      | _       | 8       |         | 6.5      |         | ns          |

| t22     | ClkIn               | Clock Period                                             | 30        | 250     | 25      | 250     | 20      | 250     | 15       | 250     | ns          |

| t23     | Reset               | Pulse Width from Vcc valid                               | 200       |         | 200     |         | 200     |         | 200      |         | μs          |

| t24     | Reset               | Minimum Pulse Width                                      | 32        |         | 32      | _       | 32      |         | 32       |         | sys         |

| t25     | Reset               | Set-up to SysClk falling                                 | 8         |         | 6       |         | 5       |         | 5        | 1       | ns          |

| t26     | Int                 | Mode set-up to Reset rising                              | 8         | —       | 6       | _       | 5       |         | 5        | +       | ns          |

| t27     | Int                 | Mode hold from Reset rising                              | 2.5       |         | 2.5     |         | 2.5     |         | 2.5      | -       | ns          |

| t28     | SInt, SBrCond       | Set-up to SysClk falling                                 | 8         | _       | 6       | _       | 5       |         | 5        |         | ns          |

| t29     | SInt, SBrCond       | Hold from SysClk falling                                 | 4         | _       | 3       | _       | 3       |         | 3        |         | ns          |

| t30     | Int, BrCond         | Set-up to SysClk falling                                 | 8         | _       | 6       | _       | 5       |         | 5        | -       | ns          |

| t31     | Int, BrCond         | Hold from SysClk falling                                 | 4         |         | 3       |         | 3       |         | 3        |         | ns          |

| tsys    | SysClk              | Pulse Width                                              | 2*t22     | 2*t22   | 2*t22   | 2*t22   | 2*t22   | 2*t22   | 2*t22    | 2*t22   | ns          |

| t32     | SysClk              | Clock High Time                                          | t22 - 2   | t22 + 2 | t22 - 2 | t22 + 2 | t22 - 2 | t22 + 2 | t22 - 2  | t22 + 2 | ns          |

| t33     | SysClk              | Clock Low Time                                           | t22 - 2   | t22 + 2 | t22 - 2 | t22 + 2 | t22 - 2 | t22 + 2 | t22 - 2  | t22 + 2 | ns          |

| t45     | ExtDataEn           | Tri-state from SysClk rising<br>(after driven condition) | _         | 13      | —       | 10      | —       | 10      |          | 10      | ns          |

| t46     | ExtDataEn           | Driven from SysClk falling<br>(after driven condition)   | _         | 13      | —       | 10      | —       | 10      |          | 10      | ns          |

| t47     | IOStrobe            | Valid from SysClk falling                                |           | 10      | —       | 8       | —       | 7       |          | 7       | ns          |

| t48     | ExtDataEn,          | Asserted from SysClk rising                              |           | 15      | —       | 12      | —       | 9       | _        | 9       | ns          |

| t49     | ExtDataEn<br>DataEn | Negated from SysClk rising                               | _         | 9       | _       | 7       | —       | 6       | _        | 6       | ns          |

| t50     | MemStrobe           | Asserted from SysClk rising                              | _         | 19      | _       | 15      | _       | 15      | <u> </u> | 15      | ns          |

| t51     | MemStrobe           | Negated from SysClk falling                              | —         | 19      | —       | 15      |         | 15      | —        | 15      | ns          |

| t52     | MemStrobe           | Asserted from Addr(3:0) valid <sup>(4)</sup>             | 0         | _       | 0       |         | 0       |         | 0        | -       | ns          |

| tderate | All outputs         | Timing deration for loading over $25pF^{(4, 5)}$         |           | 0.5     | -       | 0.5     | -       | 0.5     | -        | 0.5     | ns/<br>25pl |

### AC ELECTRICAL CHARACTERISTICS RV3041 (CONT.)

1. All timings referenced to 1.5 Volts, with a rise and fall time of less than 2.5ns.

2. All outputs tested with 25pF loading.

3. The AC values listed here reference timing diagrams contained in the R3041 Hardware User's Manual.

4. Guaranteed by design.

5. This parameter is used to derate the AC timings according to the loading of the system. This parameter provides a deration for loads over the specified test condition; that is, the deration factor is applied for each 25pF over the specified test load condition.

6. Timings t34 - t44 are reserved for other RISController family members.

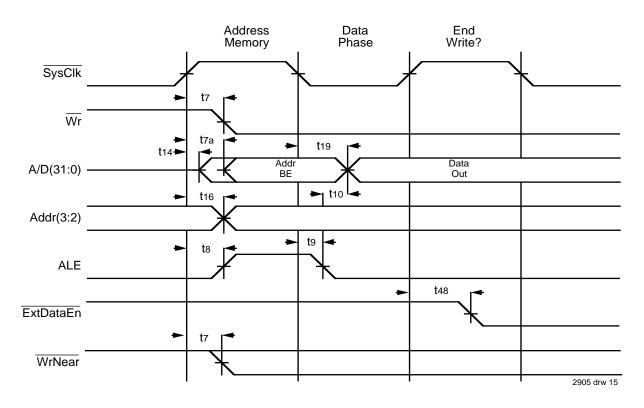

Figure 12(a). Start of Read Timing with Non-Extended Address Hold Option

Figure 12(c). Start of Write Timing with Non-Extended Address Hold Option

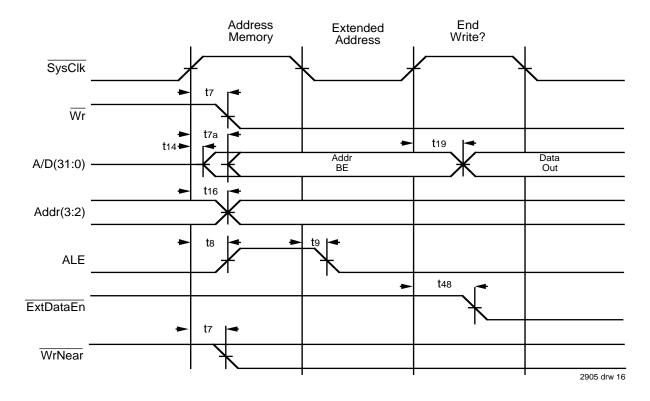

Figure 12(d). Start of Write Timing with Extended Address Hold Option

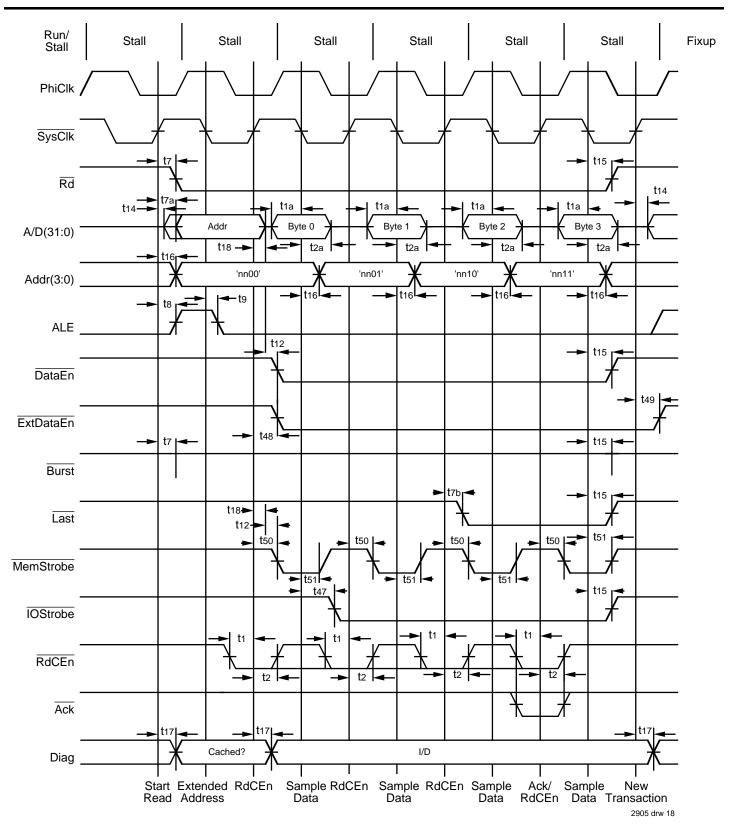

Figure 14. Mini-burst read of 32-bit datum from 8-bit wide memory port

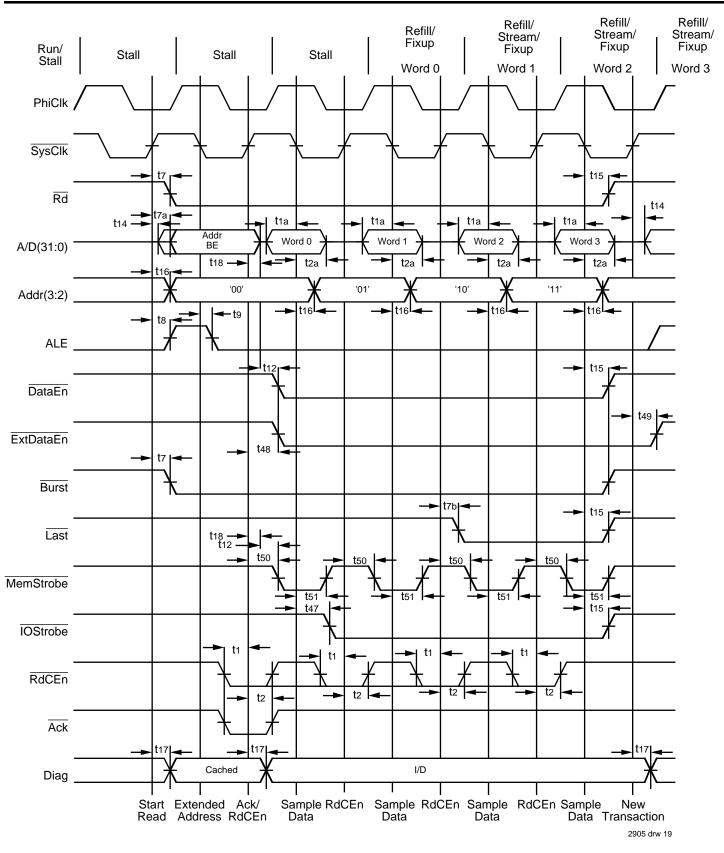

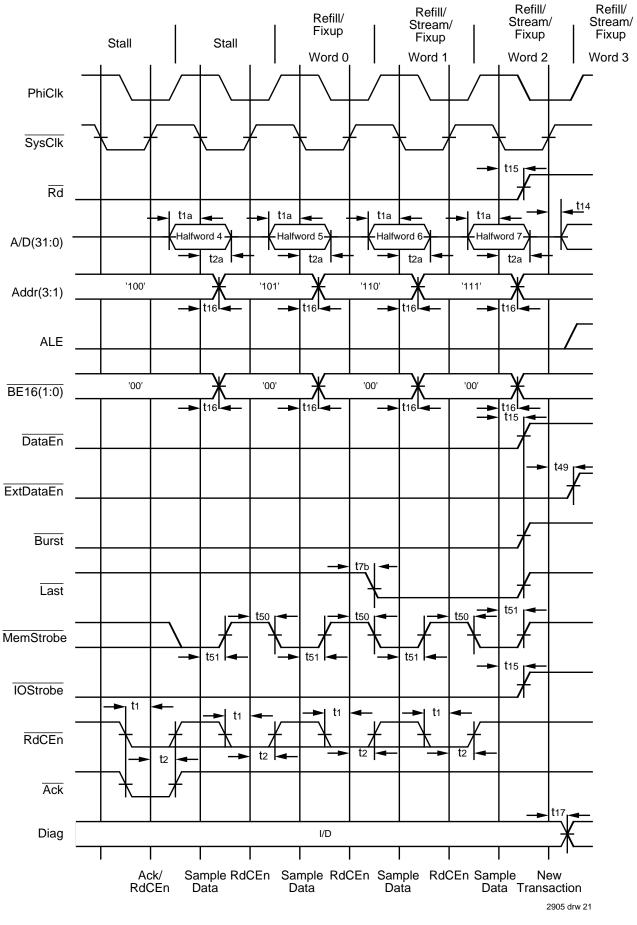

Figure 15. R3041 Quad Word Read

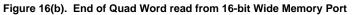

Figure 18. Tri-Byte Mini-burst Write to 8-bit Port

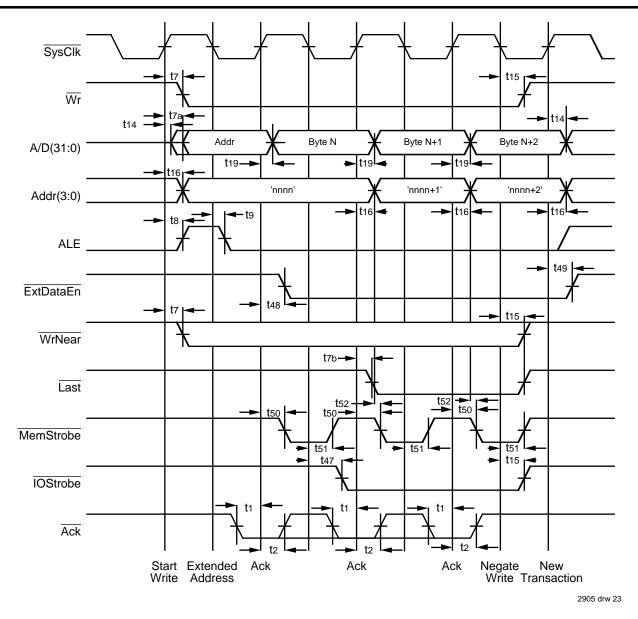

Figure 20. R3041 Regaining Bus Mastership

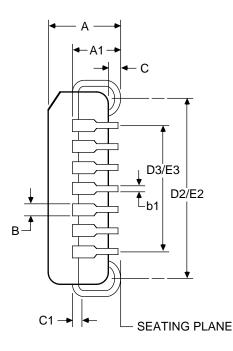

### 84 LEAD PLCC (SQUARE)

2905 drw 31

| DWG #      | J84-1<br>84 |       |  |  |

|------------|-------------|-------|--|--|

| # of Leads |             |       |  |  |

| Symbol     | Min.        | Max.  |  |  |

| А          | 165         | .180  |  |  |

| A1         | .095        | .115  |  |  |

| В          | .026        | .032  |  |  |

| b1         | .013        | .021  |  |  |

| С          | .020        | .040  |  |  |

| C1         | .008        | .012  |  |  |

| D          | 1.185       | 1.195 |  |  |

| D1         | 1.150       | 1.156 |  |  |

| D2/E2      | 1.090       | 1.130 |  |  |

| D3/E3      | 1.000 REF   |       |  |  |

| E          | 1.185       | 1.195 |  |  |

| E1         | 1.150       | 1.156 |  |  |

| е          | .050 BSC    |       |  |  |

| ND/NE      | 21          |       |  |  |

#### NOTES:

- 1. All dimensions are in inches, unless otherwise noted.

- 2. BSC—Basic lead Spacing between Centers.

3. D & E do not include mold flash or protutions.

- 4. Formed leads shall be planar with respect to one another and within .004" at the seating plane.

- 5. ND & NE represent the number of leads in the D & E directions respectively.

- 6. D1 & E1 should be measured from the bottom of the package.7. PLCC is pin & form compatible with MQUAD; the MQUAD package is used in other RISController family members.