#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | C500                                                                        |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 10MHz                                                                       |

| Connectivity               | CANbus, EBI/EMI, SPI, UART/USART                                            |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 49                                                                          |

| Program Memory Size        | 64KB (64K x 8)                                                              |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 2.5K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.25V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 80-QFP                                                                      |

| Supplier Device Package    | P-MQFP-80-1                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/c515c8emcafxqma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2003-02 Published by Infineon Technologies AG, St.-Martin-Strasse 53, 81669 München, Germany © Infineon Technologies AG 2003.

All Rights Reserved.

### Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (www.infineon.com).

### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

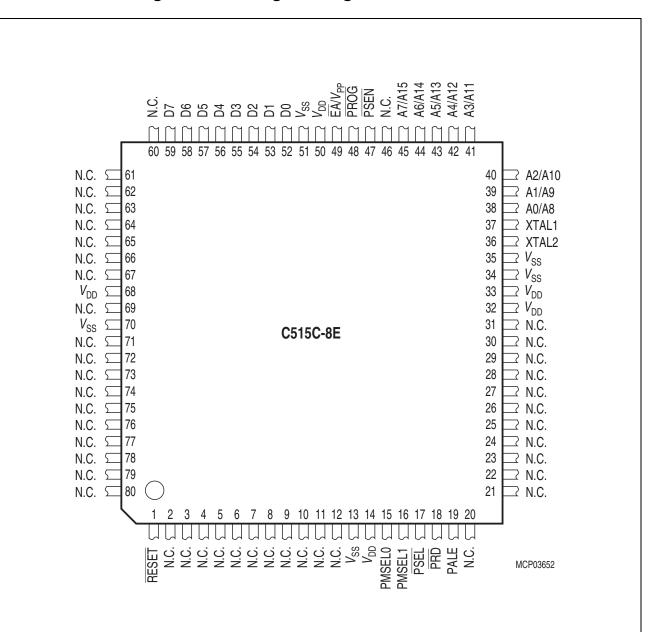

# Table 2Pin Definitions and Functions (cont'd)

| Symbol                                 | Pin Number  | I/O <sup>1)</sup> | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|----------------------------------------|-------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                        | P-MQFP-80-1 |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| PE/SWD                                 | 75          | 1                 | Power saving mode enable / Start watchdog<br>timer<br>A low level on this pin allows the software to ente<br>the power down, idle and slow down mode. In cas<br>the low level is also seen during reset, the watchdo<br>timer function is off on default.<br>Use of the software controlled power saving mode<br>is blocked, when this pin is held on high level. A hig<br>level during reset performs an automatic start of th<br>watchdog timer immediately after reset. When lef<br>unconnected this pin is pulled high by a weak<br>internal pull-up resistor. |  |  |  |  |

| V <sub>SSCLK</sub>                     | 13          | _                 | <b>Ground (0 V) for on-chip oscillator</b><br>This pin is used for ground connection of the on-chip<br>oscillator circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| V <sub>DDCLK</sub>                     | 14          | _                 | <b>Supply voltage for on-chip oscillator</b><br>This pin is used for power supply of the on-chip<br>oscillator circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| $V_{\text{DDE1}}$<br>$V_{\text{DDE2}}$ | 32<br>68    | -                 | <b>Supply voltage for I/O ports</b><br>These pins are used for power supply of the I/O<br>ports during normal, idle, and power down mode.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| $V_{\rm SSE1}$<br>$V_{\rm SSE2}$       | 35<br>70    | _                 | <b>Ground (0 V) for I/O ports</b><br>These pins are used for ground connections of the<br>I/O ports during normal, idle, and power down<br>mode.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| V <sub>DD1</sub>                       | 33          | _                 | <b>Supply voltage for internal logic</b><br>This pins is used for the power supply of the internal<br>logic circuits during normal, idle, and power down<br>mode.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| V <sub>SS1</sub>                       | 34          | _                 | <b>Ground (0 V) for internal logic</b><br>This pin is used for the ground connection of the<br>internal logic circuits during normal, idle, and power<br>down mode.                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

C515C

The XRAM/CAN controller can be accessed by read/write instructions (MOVX A,DPTR, MOVX @DPTR,A), which use the 16-bit DPTR for indirect addressing. For accessing the XRAM or CAN controller, the effective address stored in DPTR must be in the range of F700<sub>H</sub> to FFFF<sub>H</sub>.

The XRAM can be also accessed by read/write instructions (MOVX A,@Ri, MOVX @Ri,A), which use only an 8-bit address (indirect addressing with registers R0 or R1). Therefore, a special page register XPAGE which provides the upper address information (A8-A15) during 8-bit XRAM accesses. The behaviour of Port 0 and P2 during a MOVX access depends on the control bits XMAP0 and XMAP1 in register SYSCON and on the state of pin EA. Table 3 lists the various operating conditions.

# Table 3Behaviour of P0/P2 and RD/WR During MOVX Accesses

|               |               |                                              |                                                                             | XMAP1, XMAP0                                                                                                                |                                                                                                                                      |

|---------------|---------------|----------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

|               |               |                                              | 00                                                                          | 10                                                                                                                          | X1                                                                                                                                   |

| <b>EA</b> = 0 | MOVX<br>@DPTR | DPTR<br><<br>XRAM/CAN<br>address range       | a) P0/P2→Bus<br>b) RD/WR active<br>c) ext.memory<br>is used                 | a) P0/P2→Bus<br>b) RD/WR active<br>c) ext.memory<br>is used                                                                 | a) P0/P2→Bus<br>b) RD/WR active<br>c) ext.memory<br>is used                                                                          |

|               |               | DPTR<br>≥<br>XRAMCAN<br>address range        | a) P0/P2→Bus<br>(RD/WR-Data)<br>b) RD/WR inactive<br>c) XRAM is used        | a) P0/P2→Bus<br>(RD/WR-Data)<br>b) RD/WR active<br>c) XRAM is used                                                          | a) P0/P2→Bus<br>b) RD/WR active<br>c) ext.memory<br>is used                                                                          |

|               | MOVX<br>@ Ri  | XPAGE<br><<br>XRAMCAN<br>addr. page<br>range | a) P0→Bus<br>P2→I/O<br>b) RD/WR active<br>c) ext.memory<br>is used          | a) P0→Bus<br>P2→I/O<br>b) RD/WR active<br>c) ext.memory<br>is used                                                          | a) P0→Bus<br>P2→I/O<br>b) RD/WR active<br>c) ext.memory<br>is used                                                                   |

|               |               | XPAGE<br>≥<br>XRAMCAN<br>addr. page<br>range | a) P0→Bus<br>(RD/WR-Data)<br>P2→I/O<br>b) RD/WR inactive<br>c) XRAM is used | a) P0 $\rightarrow$ Bus<br>(RD/WR-Data only)<br>P2 $\rightarrow$ I/O<br>b) RD/WR active<br>c) XRAM is used                  | a) P0 $\rightarrow$ Bus<br>P2 $\rightarrow$ I/O<br>b) $\overline{\text{RD}}/\overline{\text{WR}}$ active<br>c) ext.memory<br>is used |

| <b>EA</b> = 1 | MOVX<br>@DPTR | DPTR<br><<br>XRAM/CAN<br>address range       | a) P0/P2→Bus<br>b) RD/WR active<br>c) ext.memory<br>is used                 | a) P0/P2→Bus<br>b) RD/WR active<br>c) ext.memory<br>is used                                                                 | a) P0/P2→Bus<br>b) RD/WR active<br>c) ext.memory<br>is used                                                                          |

|               |               | DPTR<br>≥<br>XRAMCAN<br>address range        | a) P0/P2→I/0<br>b) RD/WR inactive<br>c) XRAM is used                        | a) P0/P2→Bus<br>(RD/WR-Data)<br>b) RD/WR active<br>c) XRAM is used                                                          | <ul> <li>a) P0/P2→Bus</li> <li>b) RD/WR active</li> <li>c) ext.memory</li> <li>is used</li> </ul>                                    |

|               | MOVX<br>@ Ri  | XPAGE<br><<br>XRAMCAN<br>addr. page<br>range | a) P0→Bus<br>P2→I/O<br>b) RD/WR active<br>c) ext.memory<br>is used          | a) P0→Bus<br>P2→I/O<br>b) RD/WR active<br>c) ext.memory is<br>used                                                          | a) P0→Bus<br>P2→I/O<br>b) RD/WR active<br>c) ext.memory<br>is used                                                                   |

|               |               | XPAGE<br>≥<br>XRAMCAN<br>addr. page<br>range | a) P2→I/O<br>P0/P2→I/O<br>b) RD/WR inactive<br>c) XRAM is used              | a) P0→Bus<br>( $\overline{RD}/\overline{WR}$ -Data)<br>P2→I/O<br>b) $\overline{RD}/\overline{WR}$ active<br>c) XRAM is used | <ul> <li>a) P0→Bus</li> <li>P2→I/O</li> <li>b) RD/WR active</li> <li>c) ext.memory</li> <li>is used</li> </ul>                       |

modes compatible to 8051/C501 family

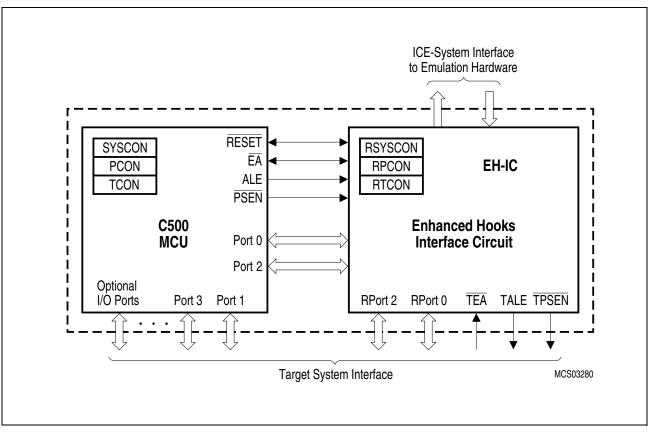

## **Enhanced Hooks Emulation Concept**

The Enhanced Hooks Emulation Concept of the C500 microcontroller family is a new, innovative way to control the execution of C500 MCUs and to gain extensive information on the internal operation of the controllers. Emulation of on-chip ROM based programs is possible, too.

Each production chip has built-in logic for the support of the Enhanced Hooks Emulation Concept. Therefore, no costly bond-out chips are necessary for emulation. This also ensure that emulation and production chips are identical.

The Enhanced Hooks Technology, which requires embedded logic in the C500 allows the C500 together with an EH-IC to function similar to a bond-out chip. This simplifies the design and reduces costs of an ICE-system. ICE-systems using an EH-IC and a compatible C500 are able to emulate all operating modes of the different versions of the C500 microcontrollers. This includes emulation of ROM, ROM with code rollover and ROMless modes of operation. It is also able to operate in single step mode and to read the SFRs after a break.

## Figure 9 Basic C500 MCU Enhanced Hooks Concept Configuration

Port 0, port 2 and some of the control lines of the C500 based MCU are used by Enhanced Hooks Emulation Concept to control the operation of the device during emulation and to transfer informations about the program execution and data transfer between the external emulation hardware (ICE-system) and the C500 MCU.

| Table 4             | Special                                                                      | Function Registers - Functional Blo                                                                                                                                                                                                                                                        | DCK                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Block               | Symbol                                                                       | Name                                                                                                                                                                                                                                                                                       | Addr                                                                                                                                                                                                                                                                                                  | Contents after<br>Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CPU                 | ACC<br>B<br>DPH<br>DPL<br>DPSEL<br>PSW<br>SP<br>SYSCON <sup>1)</sup>         | Accumulator<br>B-Register<br>Data Pointer, High Byte<br>Data Pointer, Low Byte<br>Data Pointer Select Register<br>Program Status Word Register<br>Stack Pointer<br>System Control Register C515C-8R<br>C515C-8E                                                                            | E0 <sub>H</sub> <sup>2)</sup><br>F0 <sub>H</sub> <sup>2)</sup><br>83 <sub>H</sub><br>82 <sub>H</sub><br>92 <sub>H</sub><br>D0 <sub>H</sub> <sup>2)</sup><br>81 <sub>H</sub><br>B1 <sub>H</sub><br>B1 <sub>H</sub>                                                                                     | $\begin{array}{c} 00_{\rm H} \\ 00_{\rm H} \\ 00_{\rm H} \\ 00_{\rm H} \\ XXXXX000_{\rm B}^{3)} \\ 00_{\rm H} \\ 07_{\rm H} \\ X010XX01_{\rm B}^{3)} \\ X010X001_{\rm B}^{3)} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A/D-<br>Converter   | ADCON0 <sup>1)</sup><br>ADCON1<br>ADDATH<br>ADDATL                           | A/D Converter Control Register 0<br>A/D Converter Control Register 1<br>A/D Converter Data Register High Byte<br>A/D Converter Data Register Low Byte                                                                                                                                      | D8 <sub>H</sub> <sup>2)</sup><br>DC <sub>H</sub><br>D9 <sub>H</sub><br>DA <sub>H</sub>                                                                                                                                                                                                                | $\begin{array}{c} 00_{H} \\ 0XXXX000_{B}{}^{3)} \\ 00_{H} \\ 00XXXXX_{B}{}^{3)} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Interrupt<br>System |                                                                              | Interrupt Enable Register 0<br>Interrupt Enable Register 1<br>Interrupt Enable Register 2<br>Interrupt Priority Register 0<br>Interrupt Priority Register 1<br>Timer Control Register<br>Timer 2 Control Register<br>Serial Channel Control Register<br>Interrupt Request Control Register | <b>A8</b> <sub>H</sub> <sup>2)</sup><br><b>B8</b> <sub>H</sub> <sup>2)</sup><br>9A <sub>H</sub><br>A9 <sub>H</sub><br>B9 <sub>H</sub><br><b>88</b> <sub>H</sub> <sup>2)</sup><br><b>C8</b> <sub>H</sub> <sup>2)</sup><br><b>98</b> <sub>H</sub> <sup>2)</sup><br><b>C0</b> <sub>H</sub> <sup>2)</sup> | $\begin{array}{c} 00_{\rm H} \\ 00_{\rm H} \\ XX00X00X_{\rm B}{}^{3)} \\ 00_{\rm H} \\ 0X0000000_{\rm B}{}^{3)} \\ 00_{\rm H} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| XRAM                | XPAGE<br>SYSCON <sup>1)</sup>                                                | Page Address Register for Extended<br>on-chip XRAM and CAN Controller<br>System Control Register C515C-8R<br>C515C-8E                                                                                                                                                                      | 91 <sub>H</sub><br>B1 <sub>H</sub><br>B1 <sub>H</sub>                                                                                                                                                                                                                                                 | 00 <sub>H</sub><br>X010XX01 <sub>B</sub> <sup>3)</sup><br>X010X001 <sub>B</sub> <sup>3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Ports               | P0<br>P1<br>P2<br>P3<br>P4<br>P5<br>DIR5<br>P6<br>P7<br>SYSCON <sup>1)</sup> | Port 0<br>Port 1<br>Port 2<br>Port 3<br>Port 4<br>Port 5<br>Port 5 Direction Register<br>Port 6, Analog/Digital Input<br>Port 7<br>System Control Register C515C-8R<br>C515C-8E                                                                                                            | 80 <sub>H</sub> <sup>2)</sup><br>90 <sub>H</sub> <sup>2)</sup><br>A0 <sub>H</sub> <sup>2)</sup><br>B0 <sub>H</sub> <sup>2)</sup><br>E8 <sub>H</sub> <sup>2)</sup><br>F8 <sub>H</sub> <sup>2)</sup><br>F8 <sub>H</sub><br>DB <sub>H</sub><br>FA <sub>H</sub><br>B1 <sub>H</sub>                        | $\begin{array}{c} FF_{H} \\ A_{V_{V}} \\ V_{V_{V}} \\ V_{V} \\ V_{V} \\ V_{V}} \\ V_{V} \\ V_{V} \\ V_{V} \\ V_{V} \\ V_{V} \\ V_{V}} \\ V_{V} \\ V $ |

| Watchdog            | WDTREL<br>IEN0 <sup>1)</sup><br>IEN1 <sup>1)</sup><br>IP0 <sup>1)</sup>      | Watchdog Timer Reload Register<br>Interrupt Enable Register 0<br>Interrupt Enable Register 1<br>Interrupt Priority Register 0                                                                                                                                                              | 86 <sub>H</sub><br><b>A8<sub>H</sub></b> <sup>2)</sup><br><b>B8<sub>H</sub></b> <sup>2)</sup><br>A9 <sub>H</sub>                                                                                                                                                                                      | 00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## Table 4 Special Function Registers - Functional Block

# Table 5Contents of the SFRs, SFRs in Numeric Order<br/>of their Addresses

| Addr.                         | Register            | Content<br>after<br>Reset <sup>1)</sup> | Bit 7       | Bit 6       | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------------------------|---------------------|-----------------------------------------|-------------|-------------|-------|-------|-------|-------|-------|-------|

| 80 <sub>H</sub> <sup>2)</sup> | P0                  | FF <sub>H</sub>                         | .7          | .6          | .5    | .4    | .3    | .2    | .1    | .0    |

| 81 <sub>H</sub>               | SP                  | 07 <sub>H</sub>                         | .7          | .6          | .5    | .4    | .3    | .2    | .1    | .0    |

| 82 <sub>H</sub>               | DPL                 | 00 <sub>H</sub>                         | .7          | .6          | .5    | .4    | .3    | .2    | .1    | .0    |

| 83 <sub>H</sub>               | DPH                 | 00 <sub>H</sub>                         | .7          | .6          | .5    | .4    | .3    | .2    | .1    | .0    |

| 86 <sub>H</sub>               | WDTREL              | 00 <sub>H</sub>                         | WDT<br>PSEL | .6          | .5    | .4    | .3    | .2    | .1    | .0    |

| 87 <sub>H</sub>               | PCON                | 00 <sub>H</sub>                         | SMOD        | PDS         | IDLS  | SD    | GF1   | GF0   | PDE   | IDLE  |

| 88 <sub>H</sub> <sup>2)</sup> | TCON                | 00 <sub>H</sub>                         | TF1         | TR1         | TF0   | TR0   | IE1   | IT1   | IE0   | IT0   |

| 88 <sub>H</sub> <sup>3)</sup> | PCON1 <sup>4)</sup> | 0XXX-<br>XXXX <sub>B</sub>              | EWPD        | -           | -     | -     | -     | _     | -     | -     |

| 88 <sub>H</sub> <sup>3)</sup> | PCON1 <sup>5)</sup> | 0XX0-<br>XXXX <sub>B</sub>              | EWPD        | -           | -     | WS    | -     | _     | -     | -     |

| 89 <sub>H</sub>               | TMOD                | 00 <sub>H</sub>                         | GATE        | C/T         | M1    | M0    | GATE  | C/T   | M1    | MO    |

| 8A <sub>H</sub>               | TL0                 | 00 <sub>H</sub>                         | .7          | .6          | .5    | .4    | .3    | .2    | .1    | .0    |

| 8B <sub>H</sub>               | TL1                 | 00 <sub>H</sub>                         | .7          | .6          | .5    | .4    | .3    | .2    | .1    | .0    |

| 8C <sub>H</sub>               | TH0                 | 00 <sub>H</sub>                         | .7          | .6          | .5    | .4    | .3    | .2    | .1    | .0    |

| 8D <sub>H</sub>               | TH1                 | 00 <sub>H</sub>                         | .7          | .6          | .5    | .4    | .3    | .2    | .1    | .0    |

| 90 <sub>H</sub> <sup>2)</sup> | P1                  | FF <sub>H</sub>                         | T2          | CLK-<br>OUT | T2EX  | INT2  | INT6  | INT5  | INT4  | INT3  |

| 91 <sub>H</sub>               | XPAGE               | 00 <sub>H</sub>                         | .7          | .6          | .5    | .4    | .3    | .2    | .1    | .0    |

| 92 <sub>H</sub>               | DPSEL               | XXXX-<br>X000 <sub>B</sub>              | -           | -           | -     | -     | -     | .2    | .1    | .0    |

| 93 <sub>H</sub>               | SSCCON              | 07 <sub>H</sub>                         | SCEN        | TEN         | MSTR  | CPOL  | CPHA  | BRS2  | BRS1  | BRS0  |

| 94 <sub>H</sub>               | STB                 | XX <sub>H</sub>                         | .7          | .6          | .5    | .4    | .3    | .2    | .1    | .0    |

| 95 <sub>H</sub>               | SRB                 | XX <sub>H</sub>                         | .7          | .6          | .5    | .4    | .3    | .2    | .1    | .0    |

| 96 <sub>H</sub>               | SSCMOD              | 00 <sub>H</sub>                         | LOOPB       | TRIO        | 0     | 0     | 0     | 0     | 0     | LSBSM |

| 98 <sub>H</sub> <sup>2)</sup> | SCON                | 00 <sub>H</sub>                         | SM0         | SM1         | SM2   | REN   | TB8   | RB8   | ТІ    | RI    |

| 99 <sub>H</sub>               | SBUF                | XX <sub>H</sub>                         | .7          | .6          | .5    | .4    | .3    | .2    | .1    | .0    |

| 9A <sub>H</sub>               | IEN2                | X00X-<br>X00X <sub>B</sub>              | _           | _           | EX8   | EX7   | _     | ESSC  | ECAN  | -     |

| A0 <sub>H</sub> <sup>2)</sup> | P2                  | FF <sub>H</sub>                         | .7          | .6          | .5    | .4    | .3    | .2    | .1    | .0    |

| A8 <sub>H</sub> <sup>2)</sup> | IEN0                | 00 <sub>H</sub>                         | EAL         | WDT         | ET2   | ES    | ET1   | EX1   | ET0   | EX0   |

| A9 <sub>H</sub>               | IP0                 | 00 <sub>H</sub>                         | OWDS        | WDTS        | .5    | .4    | .3    | .2    | .1    | .0    |

# Table 5Contents of the SFRs, SFRs in Numeric Order<br/>of their Addresses (cont'd)

| Addr.                         | Register             | Content<br>after<br>Reset <sup>1)</sup> | Bit 7      | Bit 6      | Bit 5      | Bit 4      | Bit 3      | Bit 2      | Bit 1      | Bit 0      |

|-------------------------------|----------------------|-----------------------------------------|------------|------------|------------|------------|------------|------------|------------|------------|

| AA <sub>H</sub>               | SRELL                | D9 <sub>H</sub>                         | .7         | .6         | .5         | .4         | .3         | .2         | .1         | .0         |

| AB <sub>H</sub>               | SCF                  | XXXX-<br>XX00 <sub>B</sub>              | -          | -          | -          | -          | -          | -          | WCOL       | тс         |

| AC <sub>H</sub>               | SCIEN                | XXXX-<br>XX00 <sub>B</sub>              | -          | -          | -          | -          | -          | -          | WCEN       | TCEN       |

| 80 <sub>H</sub> <sup>2)</sup> | P3                   | FF <sub>H</sub>                         | RD         | WR         | T1         | то         | INT1       | INT0       | TxD        | RxD        |

| B1 <sub>H</sub>               | SYSCON <sup>4)</sup> | X010-<br>XX01 <sub>B</sub>              | -          | PMOD       | EALE       | RMAP       | -          | -          | XMAP1      | XMAP0      |

| B1 <sub>H</sub>               | SYSCON <sup>5)</sup> | X010-<br>X001 <sub>B</sub>              | -          | PMOD       | EALE       | RMAP       | -          | CSWO       | XMAP1      | XMAP0      |

| 88 <sub>H</sub> <sup>2)</sup> | IEN1                 | 00 <sub>H</sub>                         | EXEN2      | SWDT       | EX6        | EX5        | EX4        | EX3        | EX2        | EADC       |

| B9 <sub>H</sub>               | IP1                  | 0X00-<br>0000 <sub>B</sub>              | PDIR       | -          | .5         | .4         | .3         | .2         | .1         | .0         |

| BA <sub>H</sub>               | SRELH                | XXXX-<br>XX11 <sub>B</sub>              | -          | -          | -          | -          | -          | -          | .1         | .0         |

| C0 <sub>H</sub> <sup>2)</sup> | IRCON                | 00 <sub>H</sub>                         | EXF2       | TF2        | IEX6       | IEX5       | IEX4       | IEX3       | IEX2       | IADC       |

| C1 <sub>H</sub>               | CCEN                 | 00 <sub>H</sub>                         | COCA<br>H3 | COCA<br>L3 | COCA<br>H2 | COCA<br>L2 | COCA<br>H1 | COCA<br>L1 | COCA<br>H0 | COCA<br>L0 |

| C2 <sub>H</sub>               | CCL1                 | 00 <sub>H</sub>                         | .7         | .6         | .5         | .4         | .3         | .2         | .1         | .0         |

| C3 <sub>H</sub>               | CCH1                 | 00 <sub>H</sub>                         | .7         | .6         | .5         | .4         | .3         | .2         | .1         | .0         |

| C4 <sub>H</sub>               | CCL2                 | 00 <sub>H</sub>                         | .7         | .6         | .5         | .4         | .3         | .2         | .1         | .0         |

| C5 <sub>H</sub>               | CCH2                 | 00 <sub>H</sub>                         | .7         | .6         | .5         | .4         | .3         | .2         | .1         | .0         |

| C6 <sub>H</sub>               | CCL3                 | 00 <sub>H</sub>                         | .7         | .6         | .5         | .4         | .3         | .2         | .1         | .0         |

| C7 <sub>H</sub>               | ССНЗ                 | 00 <sub>H</sub>                         | .7         | .6         | .5         | .4         | .3         | .2         | .1         | .0         |

| C8 <sub>H</sub> <sup>2)</sup> | T2CON                | 00 <sub>H</sub>                         | T2PS       | I3FR       | I2FR       | T2R1       | T2R0       | T2CM       | T2I1       | T2I0       |

| CA <sub>H</sub>               | CRCL                 | 00 <sub>H</sub>                         | .7         | .6         | .5         | .4         | .3         | .2         | .1         | .0         |

| CB <sub>H</sub>               | CRCH                 | 00 <sub>H</sub>                         | .7         | .6         | .5         | .4         | .3         | .2         | .1         | .0         |

| CC <sub>H</sub>               | TL2                  | 00 <sub>H</sub>                         | .7         | .6         | .5         | .4         | .3         | .2         | .1         | .0         |

| CD <sub>H</sub>               | TH2                  | 00 <sub>H</sub>                         | .7         | .6         | .5         | .4         | .3         | .2         | .1         | .0         |

# Table 5Contents of the SFRs, SFRs in Numeric Order<br/>of their Addresses (cont'd)

| Addr.                         | Register            | Content<br>after<br>Reset <sup>1)</sup> | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------------------------|---------------------|-----------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| D0 <sub>H</sub> <sup>2)</sup> | PSW                 | 00 <sub>H</sub>                         | CY    | AC    | F0    | RS1   | RS0   | OV    | F1    | Р     |

| D8 <sub>H</sub> <sup>2)</sup> | ADCON0              | 00 <sub>H</sub>                         | BD    | CLK   | ADEX  | BSY   | ADM   | MX2   | MX1   | MX0   |

| D9 <sub>H</sub>               | ADDATH              | 00 <sub>H</sub>                         | .9    | .8    | .7    | .6    | .5    | .4    | .3    | .2    |

| DA <sub>H</sub>               | ADDATL              | 00XX-<br>XXXX <sub>B</sub>              | .1    | .0    | -     | -     | -     | -     | _     | -     |

| DB <sub>H</sub>               | P6                  | -                                       | .7    | .6    | .5    | .4    | .3    | .2    | .1    | .0    |

| DC <sub>H</sub>               | ADCON1              | 0XXX-<br>X000 <sub>B</sub>              | ADCL  | -     | -     | -     | 0     | MX2   | MX1   | MX0   |

| E0 <sub>H</sub> <sup>2)</sup> | ACC                 | 00 <sub>H</sub>                         | .7    | .6    | .5    | .4    | .3    | .2    | .1    | .0    |

| E8 <sub>H</sub> <sup>2)</sup> | P4                  | FF <sub>H</sub>                         | RXDC  | TXDC  | INT8  | SLS   | STO   | SRI   | SCLK  | ADST  |

| F0 <sub>H</sub> <sup>2)</sup> | В                   | 00 <sub>H</sub>                         | .7    | .6    | .5    | .4    | .3    | .2    | .1    | .0    |

| F8 <sub>H</sub> <sup>2)</sup> | P5                  | FF <sub>H</sub>                         | .7    | .6    | .5    | .4    | .3    | .2    | .1    | .0    |

| F8 <sub>H</sub> <sup>2)</sup> | DIR5 <sup>6)</sup>  | FF <sub>H</sub>                         | .7    | .6    | .5    | .4    | .3    | .2    | .1    | .0    |

| FA <sub>H</sub>               | P7                  | XXXX-<br>XXX1 <sub>B</sub>              | _     | -     | -     | -     | -     | -     | _     | INT7  |

| FC <sub>H</sub>               | VR0 <sup>7)8)</sup> | C5 <sub>H</sub>                         | 1     | 1     | 0     | 0     | 0     | 1     | 0     | 1     |

| FD <sub>H</sub>               | VR1 <sup>7)8)</sup> | 95 <sub>H</sub>                         | 1     | 0     | 0     | 1     | 0     | 1     | 0     | 1     |

| FE <sub>H</sub>               | VR2 <sup>7)8)</sup> | 02 <sub>H</sub> 9)                      | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     |

<sup>1)</sup> "X" means that the value is undefined and the location is reserved.

<sup>2)</sup> Bit-addressable special function registers

<sup>3)</sup> SFR is located in the mapped SFR area. For accessing this SFR, bit RMAP in SFR SYSCON must be set.

<sup>4)</sup> This SFR is available in the C515C-8R and C515C-L.

<sup>5)</sup> This SFR is available in the C515C-8E.

- <sup>6)</sup> This SFR is a mapped SFR. For accessing this SFR, bit PDIR in SFR IP1 must be set.

- <sup>7)</sup> This SFR is a mapped SFR. For accessing this SFR, bit RMAP in SFR SYSCON must be set.

- <sup>8)</sup> These SFRs are read-only registers (C515C-8E only).

- <sup>9)</sup> The content of this SFR varies with the actual step of the C515C-8E (e.g.  $01_{H}$  for the first step).

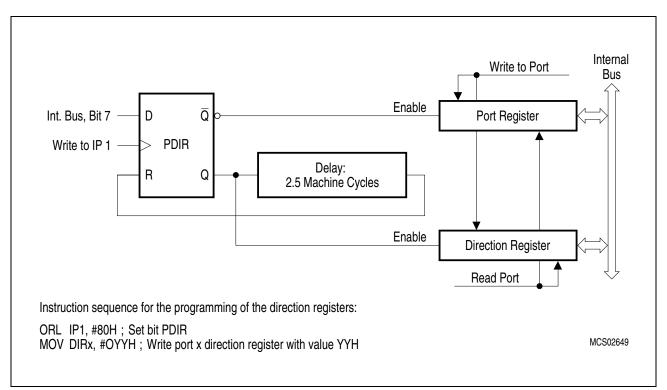

### Port Structure Selection of Port 5

After a reset operation of the C515C, the quasi-bidirectional 8051-compatible port structure is selected. For selection of the bidirectional (CMOS) port 5 structure the bit PMOD of SFR SYSCON must be set. Because each port 5 pin can be programmed as an input or an output, additionally, after the selection of the bidirectional mode the direction register DIR5 of port 5 must be written. This direction register is mapped to the port 5 register. This means, the port register address is equal to its direction register address. **Figure 10** illustrates the port and direction register configuration.

Figure 10 Port Register, Direction Register

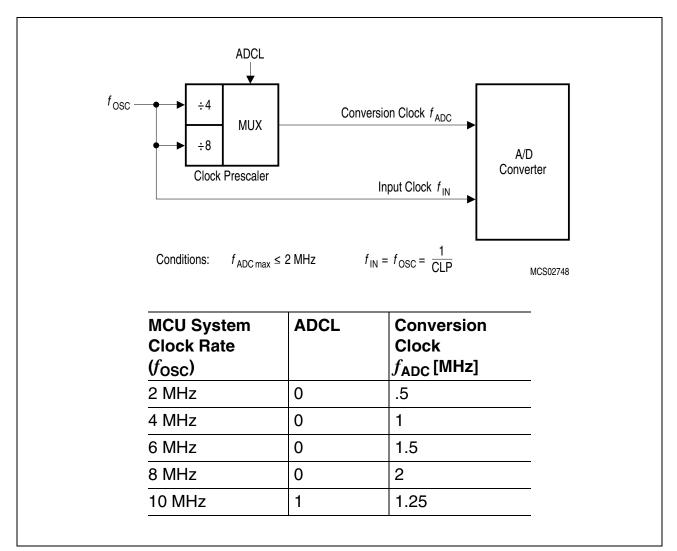

Figure 18 A/D Converter Clock Selection

### Interrupt System

The C515C provides 17 interrupt sources with four priority levels. Seven interrupts can be generated by the on-chip peripherals (timer 0, timer 1, timer 2, serial interface, A/D converter, SSC interface, CAN controller), and ten interrupts may be triggered externally (P1.5/T2EX, P3.2/INT0, P3.3/INT1, P1.4/INT2, P1.0/INT3, P1.1/INT4, P1.2/INT5, P1.3/INT6, P7.0/INT7, P4.5/INT8). The wake-up from power-down mode interrupt has a special functionality which allows to exit from the software power-down mode by a short low pulse at pin P3.2/INT0.

In the C515C the 17 interrupt sources are combined to six groups of two or three interrupt sources. Each interrupt group can be programmed to one of the four interrupt priority levels. **Figure 20** to **Figure 22** give a general overview of the interrupt sources and illustrate the interrupt request and control flags.

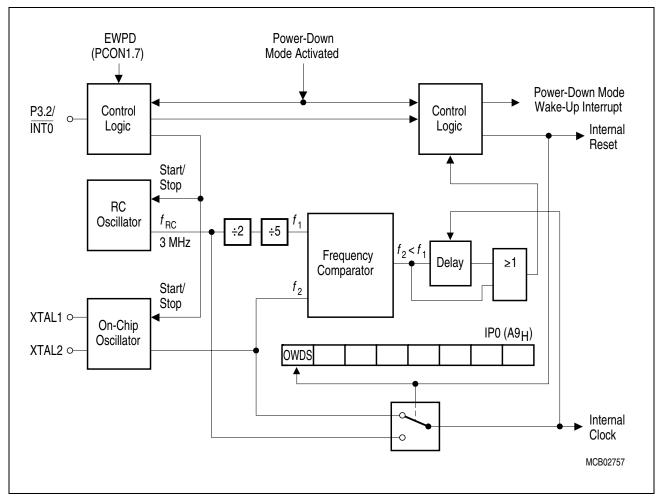

Figure 24 Block Diagram of the Oscillator Watchdog

## **Power Saving Modes**

The C515C provides two basic power saving modes, the idle mode and the power down mode. Additionally, a slow down mode is available. This power saving mode reduces the internal clock rate in normal operating mode and it can be also used for further power reduction in idle mode.

## Idle mode

The CPU is gated off from the oscillator. All peripherals are still provided with the clock and are able to work. Idle mode is entered by software and can be left by an interrupt or reset.

## Power down mode

The operation of the C515C is completely stopped and the oscillator is turned off. This mode is used to save the contents of the internal RAM with a very low standby current. **Software power down mode:** Software power down mode is entered by software and can be left by reset or by a short low pulse at pin P3.2/INT0 (or P4.7/RXDC, C515C-8E only).

Hardware power down mode: Hardware power down mode is entered when the pin HWPD is put to low level.

## • Slow-down mode

The controller keeps up the full operating functionality, but its normal clock frequency is internally divided by 32. This slows down all parts of the controller, the CPU and all peripherals, to 1/32<sup>th</sup> of their normal operating frequency. Slowing down the frequency significantly reduces power consumption. The slow down mode can be combined with the idle mode.

Table 11 gives a general overview of the entry and exit conditions of the power saving modes.

In the power down mode of operation,  $V_{\rm DD}$  can be reduced to minimize power consumption. It must be ensured, however, that  $V_{\rm DD}$  is not reduced before the power down mode is invoked, and that  $V_{\rm DD}$  is restored to its normal operating level, before the power down mode is terminated.

If e.g. the idle mode is left through an interrupt, the microcontroller state (CPU, ports, peripherals) remains preserved. If a power saving mode is left by a hardware reset, the microcontroller state is disturbed and replaced by the reset state of the C515C.

If WS (bit 4) is SFR PCON1 is set (C515C-8E only), pin P4.7/RXDC is alternatively selected as wake-up pin for the software power down mode. If WS (bit 4) is SFR PCON1 is cleared (C515C-8E only), pin P3.2/INTO is selected as wake-up pin for the software power down mode.

For the C515C-8R, P3.2/INTO is always selected as wake-up pin.

### C515C-8E Pin Configuration in Programming Mode

Figure 26 P-MQFP-80-1 Pin Configuration of the C515C-8E in Programming Mode (top view)

# Absolute Maximum Ratings

| Parameter                                                                  | Symbol            | Limit | Unit                  | Notes |   |

|----------------------------------------------------------------------------|-------------------|-------|-----------------------|-------|---|

|                                                                            |                   | min.  | max.                  |       |   |

| Storage temperature                                                        | T <sub>ST</sub>   | -65   | 150                   | °C    | - |

| Voltage on $V_{\text{DD}}$ pins with respect to ground ( $V_{\text{SS}}$ ) | V <sub>DD</sub>   | -0.5  | 6.5                   | V     | - |

| Voltage on any pin with respect to ground $(V_{SS})$                       | V <sub>IN</sub>   | -0.5  | V <sub>DD</sub> + 0.5 | V     | - |

| Input current on any pin during overload condition                         | -                 | -10   | 10                    | mA    | - |

| Absolute sum of all input<br>currents during overload<br>condition         | -                 | -     | 1100 mAl              | mA    | - |

| Power dissipation                                                          | P <sub>DISS</sub> | _     | 1                     | W     | _ |

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage of the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for longer periods may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DD}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DD}$  pins with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

## **Power Supply Current Calculation Formulas**

| Parameter                          |                       | Symbol                                     | Formula                                                                                                    |

|------------------------------------|-----------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Active mode                        | C515C-8R/<br>C515C-LM | I <sub>DD typ</sub><br>I <sub>DD max</sub> | $1.71 \times f_{OSC} + 1.71$<br>$1.84 \times f_{OSC} + 2.7$                                                |

|                                    | C515C-8E              | I <sub>DD typ</sub><br>I <sub>DD max</sub> | $\begin{array}{c} {\rm 1.59} \times f_{\rm OSC} + 1.76 \\ {\rm 1.79} \times f_{\rm OSC} + 2.2 \end{array}$ |

| Idle mode                          | C515C-8R/<br>C515C-LM | I <sub>DD typ</sub><br>I <sub>DD max</sub> | $0.89 \times f_{OSC}$ + 1.56<br>1.00 × $f_{OSC}$ + 1.87                                                    |

|                                    | C515C-8E              | I <sub>DD typ</sub><br>I <sub>DD max</sub> | $0.19 \times f_{OSC}$ + 2.81<br>$0.20 \times f_{OSC}$ + 3.5                                                |

| Active mode with slow-down enabled | C515C-8R/<br>C515C-LM | I <sub>DD typ</sub><br>I <sub>DD max</sub> | $0.14 \times f_{OSC} + 3.22$<br>$0.18 \times f_{OSC} + 3.95$                                               |

|                                    | C515C-8E              | I <sub>DD typ</sub><br>I <sub>DD max</sub> | $0.16 \times f_{OSC} + 3.05$<br>$0.19 \times f_{OSC} + 3.63$                                               |

| Idle mode with slow-down enabled   | C515C-8R/<br>C515C-LM | I <sub>DD typ</sub><br>I <sub>DD max</sub> | $0.08 \times f_{OSC}$ + 3.06<br>$0.11 \times f_{OSC}$ + 3.8                                                |

|                                    | C515C-8E              | $I_{ m DD \ typ}$<br>$I_{ m DD \ max}$     | $0.13 \times f_{OSC}$ + 2.84<br>$0.14 \times f_{OSC}$ + 3.37                                               |

Note:  $f_{OSC}$  is the oscillator frequency in MHz.  $I_{DD}$  values are given in mA.

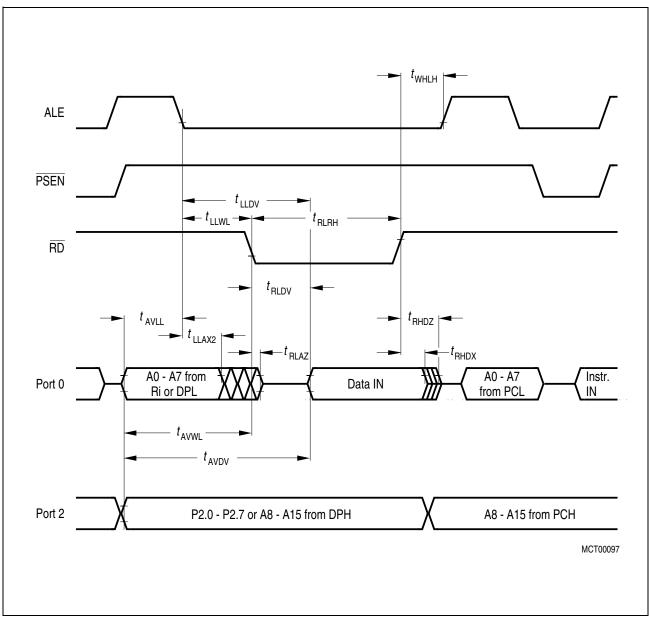

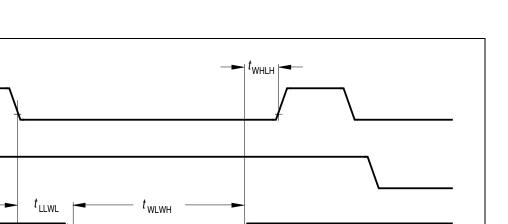

Figure 31 Data Memory Read Cycle

ALE

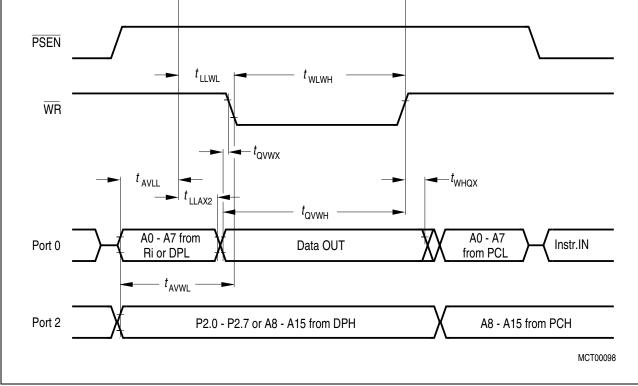

Figure 32 Data Memory Write Cycle

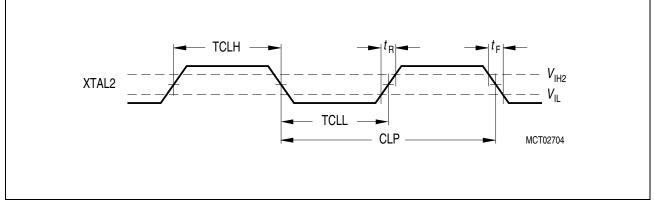

Figure 33 External Clock Drive at XTAL2

C515C

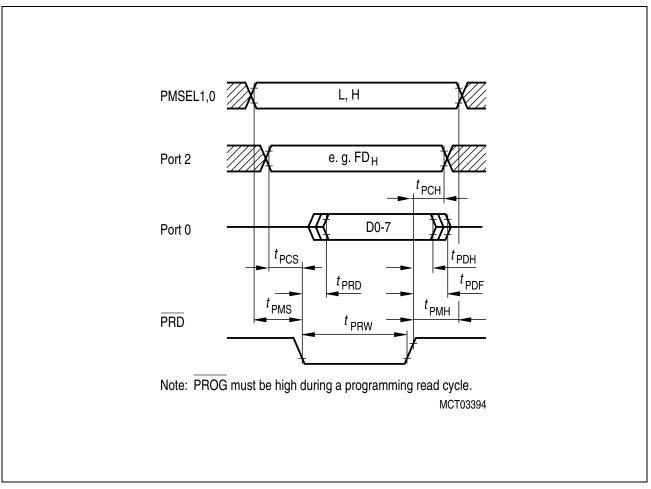

Figure 38 Version Byte - Read Timing