Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20 MIPS                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                     |

| Peripherals                | Brown-out Detect/Reset, LVD, Motor Control PWM, QEI, POR, PWM, WDT            |

| Number of I/O              | 68                                                                            |

| Program Memory Size        | 144KB (48K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 4K x 8                                                                        |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 16x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 80-TQFP                                                                       |

| Supplier Device Package    | 80-TQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f6010-20i-pf |

## dsPIC30F6010 Enhanced Flash 16-Bit Digital Signal Controller

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "dsPIC30F/33F Programmer's Reference Manual" (DS70157).

## **High-Performance Modified RISC CPU:**

- · Modified Harvard architecture

- C compiler optimized instruction set architecture with flexible addressing modes

- 83 base instructions

- 24-bit wide instructions, 16-bit wide data path

- 144 Kbytes on-chip Flash program space (Instruction words)

- · 8 Kbytes of on-chip data RAM

- 4 Kbytes of nonvolatile data EEPROM

- Up to 30 MIPS operation:

- DC to 40 MHz external clock input

- 4 MHz-10 MHz oscillator input with PLL active (4x, 8x, 16x)

- 44 interrupt sources:

- 5 external interrupt sources

- 8 user-selectable priority levels for each interrupt source

- 4 processor trap sources

- 16 x 16-bit working register array

### **DSP Engine Features:**

- Dual data fetch

- · Accumulator write-back for DSP operations

- · Modulo and Bit-Reversed Addressing modes

- Two, 40-bit wide accumulators with optional saturation logic

- 17-bit x 17-bit single-cycle hardware fractional/ integer multiplier

- · All DSP instructions single cycle

- ± 16-bit single-cycle shift

### **Peripheral Features:**

- High current sink/source I/O pins: 25 mA/25 mA

- Timer module with programmable prescaler:

- Five 16-bit timers/counters; optionally pair 16-bit timers into 32-bit timer modules

- 16-bit Capture input functions

- 16-bit Compare/PWM output functions

- 3-wire SPI modules (supports 4 Frame modes)

- I<sup>2</sup>C<sup>TM</sup> module supports Multi-Master/Slave mode and 7-bit/10-bit addressing

- · 2 UART modules with FIFO Buffers

- · 2 CAN modules, 2.0B compliant

### **Motor Control PWM Module Features:**

- 8 PWM output channels

- Complementary or Independent Output modes

- Edge and Center-Aligned modes

- 4 duty cycle generators

- · Dedicated time base

- · Programmable output polarity

- · Dead-time control for Complementary mode

- · Manual output control

- Trigger for A/D conversions

## **Quadrature Encoder Interface Module Features:**

- · Phase A, Phase B and Index Pulse input

- 16-bit up/down position counter

- · Count direction status

- Position Measurement (x2 and x4) mode

- · Programmable digital noise filters on inputs

- Alternate 16-bit Timer/Counter mode

- · Interrupt on position counter rollover/underflow

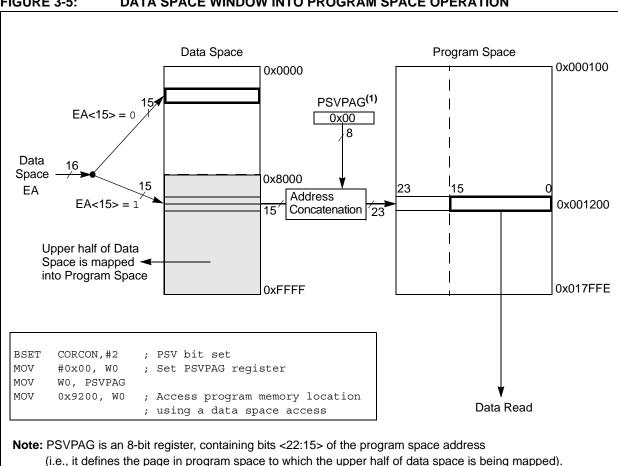

#### FIGURE 3-5: DATA SPACE WINDOW INTO PROGRAM SPACE OPERATION

**Data Address Space**

3.2

The core has two data spaces. The data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths.

#### 3.2.1 DATA SPACE MEMORY MAP

The data space memory is split into two blocks, X and Y data space. A key element of this architecture is that Y space is a subset of X space, and is fully contained within X space. In order to provide an apparent linear addressing space, X and Y spaces have contiguous addresses.

When executing any instruction other than one of the MAC class of instructions, the X block consists of the 64 Kbyte data address space (including all Y addresses). When executing one of the MAC class of instructions, the X block consists of the 64 Kbyte data address space excluding the Y address block (for data reads only). In other words, all other instructions regard the entire data memory as one composite address space. The MAC class instructions extract the Y address space from data space and address it using EAs sourced from W10 and W11. The remaining X data space is addressed using W8 and W9. Both address spaces are concurrently accessed only with the MAC class instructions.

A data space memory map is shown in Figure 3-6.

Figure 3-7 shows a graphical summary of how X and Y data spaces are accessed for MCU and DSP instructions.

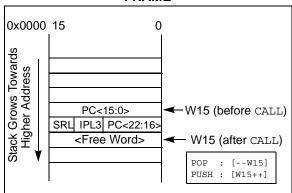

## 5.4 Interrupt Sequence

All interrupt event flags are sampled in the beginning of each instruction cycle by the IFSx registers. A pending interrupt request (IRQ) is indicated by the flag bit being equal to a '1' in an IFSx register. The IRQ will cause an interrupt to occur if the corresponding bit in the interrupt enable (IECx) register is set. For the remainder of the instruction cycle, the priorities of all pending interrupt requests are evaluated.

If there is a pending IRQ with a priority level greater than the current processor priority level in the IPL bits, the processor will be interrupted.

The processor then stacks the current program counter and the low byte of the processor status register (SRL), as shown in Figure 5-2. The low byte of the status register contains the processor priority level at the time, prior to the beginning of the interrupt cycle. The processor then loads the priority level for this interrupt into the status register. This action will disable all lower priority interrupts until the completion of the Interrupt Service Routine.

FIGURE 5-2: INTERRUPT STACK FRAME

- Note 1: The user can always lower the priority level by writing a new value into SR. The Interrupt Service Routine must clear the interrupt flag bits in the IFSx register before lowering the processor interrupt priority, in order to avoid recursive interrupts.

- 2: The IPL3 bit (CORCON<3>) is always clear when interrupts are being processed. It is set only during execution of traps.

The RETFIE (Return from Interrupt) instruction will unstack the program counter and status registers to return the processor to its state prior to the interrupt sequence.

#### 5.5 Alternate Vector Table

In Program Memory, the Interrupt Vector Table (IVT) is followed by the Alternate Interrupt Vector Table (AIVT), as shown in Figure 5-1. Access to the Alternate Vector Table is provided by the ALTIVT bit in the INTCON2 register. If the ALTIVT bit is set, all interrupt and exception processes will use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors. The AIVT supports emulation and debugging efforts by providing a means to switch between an application and a support environment, without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time.

If the AIVT is not required, the program memory allocated to the AIVT may be used for other purposes. AIVT is not a protected section and may be freely programmed by the user.

### 5.6 Fast Context Saving

A context saving option is available using shadow registers. Shadow registers are provided for the DC, N, OV, Z and C bits in SR, and the registers W0 through W3. The shadows are only one level deep. The shadow registers are accessible using the  ${\tt PUSH.S}$  and  ${\tt POP.S}$  instructions only.

When the processor vectors to an interrupt, the PUSH.S instruction can be used to store the current value of the aforementioned registers into their respective shadow registers.

If an ISR of a certain priority uses the PUSH.S and POP.S instructions for fast context saving, then a higher priority ISR should not include the same instructions. Users must save the key registers in software during a lower priority interrupt, if the higher priority ISR uses fast context saving.

## 5.7 External Interrupt Requests

The interrupt controller supports five external interrupt request signals, INT0-INT4. These inputs are edge sensitive; they require a low-to-high or a high-to-low transition to generate an interrupt request. The INTCON2 register has five bits, INT0EP-INT4EP, that select the polarity of the edge detection circuitry.

### 5.8 Wake-up from Sleep and Idle

The interrupt controller may be used to wake up the processor from either Sleep or Idle modes, if Sleep or Idle mode is active when the interrupt is generated.

If an enabled interrupt request of sufficient priority is received by the interrupt controller, then the standard interrupt request is presented to the processor. At the same time, the processor will wake-up from Sleep or Idle and begin execution of the Interrupt Service Routine (ISR) needed to process the interrupt request.

TABLE 5-2: INTERRUPT CONTROLLER REGISTER MAP

| SFR<br>Name | ADR  | Bit 15 | Bit 14 | Bit 13    | Bit 12   | Bit 11 | Bit 10 | Bit 9      | Bit 8        | Bit 7  | Bit 6 | Bit 5      | Bit 4   | Bit 3   | Bit 2       | Bit 1       | Bit 0               | Reset State         |

|-------------|------|--------|--------|-----------|----------|--------|--------|------------|--------------|--------|-------|------------|---------|---------|-------------|-------------|---------------------|---------------------|

| INTCON1     | 0080 | NSTDIS |        | _         |          | _      | OVATE  | OVBTE      | COVTE        | _      | _     | _          | MATHERR | ADDRERR | STKERR      | OSCFAIL     | _                   | 0000 0000 0000 0000 |

| INTCON2     | 0082 | ALTIVT | _      | _         | _        | _      |        | _          | _            | _      | _     | _          | INT4EP  | INT3EP  | INT2EP      | INT1EP      | INT0EP              | 0000 0000 0000 0000 |

| IFS0        | 0084 | CNIF   | MI2CIF | SI2CIF    | NVMIF    | ADIF   | U1TXIF | U1RXIF     | SPI1IF       | T3IF   | T2IF  | OC2IF      | IC2IF   | T1IF    | OC1IF       | IC1IF       | INT0IF              | 0000 0000 0000 0000 |

| IFS1        | 0086 | IC6IF  | IC5IF  | IC4IF     | IC3IF    | C1IF   | SPI2IF | U2TXIF     | U2RXIF       | INT2IF | T5IF  | T4IF       | OC4IF   | OC3IF   | IC8IF       | IC7IF       | INT1IF              | 0000 0000 0000 0000 |

| IFS2        | 0088 |        | 1      | 1         | FLTBIF   | FLTAIF | LVDIF  | 1          | QEIIF        | PWMIF  | C2IF  | INT4IF     | INT3IF  | OC8IF   | OC7IF       | OC6IF       | OC5IF               | 0000 0000 0000 0000 |

| IEC0        | 008C | CNIE   | MI2CIE | SI2CIE    | NVMIE    | ADIE   | U1TXIE | U1RXIE     | SPI1IE       | T3IE   | T2IE  | OC2IE      | IC2IE   | T1IE    | OC1IE       | IC1IE       | INT0IE              | 0000 0000 0000 0000 |

| IEC1        | 008E | IC6IE  | IC5IE  | IC4IE     | IC3IE    | C1IE   | SPI2IE | U2TXIE     | U2RXIE       | INT2IE | T5IE  | T4IE       | OC4IE   | OC3IE   | IC8IE       | IC7IE       | INT1IE              | 0000 0000 0000 0000 |

| IEC2        | 0090 | _      | 1      | 1         | FLTBIE   | FLTAIE | LVDIE  | 1          | QEIIE        | PWMIE  | C2IE  | INT4IE     | INT3IE  | OC8IE   | OC7IE       | OC6IE       | OC5IE               | 0000 0000 0000 0000 |

| IPC0        | 0094 |        |        | T1IP<2:0> | •        | _      |        | C1IP<2:0   | >            | _      |       | IC1IP<2    | 2:0>    | 1       | INT0IP<2:0> |             | 0100 0100 0100 0100 |                     |

| IPC1        | 0096 |        | ٦      | Γ31P<2:0  | >        | _      |        | T2IP<2:0>  |              | _      |       | OC2IP<2:0> |         | 1       | IC2IP<2:0>  |             | 0100 0100 0100 0100 |                     |

| IPC2        | 0098 |        | A      | ADIP<2:0: | >        | _      | U      | 1TXIP<2:0  | )>           | _      |       | U1RXIP     | <2:0>   | 1       | 5           | SPI1IP<2:0> | >                   | 0100 0100 0100 0100 |

| IPC3        | 009A |        | C      | ONIP<2:0: | >        | _      | N      | 112CIP<2:0 | <b> &gt;</b> | _      |       | SI2CIP<    | :2:0>   | 1       | N           | NVMIP<2:0   | >                   | 0100 0100 0100 0100 |

| IPC4        | 009C | _      | 0      | C3IP<2:0  | >        | _      | -      | C8IP<2:0   | >            | _      |       | IC7IP<2    | 2:0>    | 1       | I           | NT1IP<2:0>  | >                   | 0100 0100 0100 0100 |

| IPC5        | 009E | _      | IN     | NT2IP<2:0 | )>       | _      |        | T5IP<2:0>  |              | _      |       | T4IP<2     | 2:0>    | ı       | (           | OC4IP<2:0>  | •                   | 0100 0100 0100 0100 |

| IPC6        | 00A0 | _      | (      | C1IP<2:0> | >        | _      | S      | PI2IP<2:0  | >            | _      |       | U2TXIP     | <2:0>   | ı       | U           | 2RXIP<2:0   | >                   | 0100 0100 0100 0100 |

| IPC7        | 00A2 |        | Ė      | C6IP<2:0: | >        | _      |        | C5IP<2:0   | >            | _      |       | IC4IP<2    | 2:0>    | I       |             | IC3IP<2:0>  |                     | 0100 0100 0100 0100 |

| IPC8        | 00A4 |        | 0      | C8IP<2:0  | <u> </u> | _      | O      | C7IP<2:0   | >            | _      |       | OC6IP<     | 2:0>    | I       | (           | DC5IP<2:0>  | •                   | 0100 0100 0100 0100 |

| IPC9        | 00A6 | _      | P\     | WMIP<2:0  | )>       | _      |        | C2IP<2:0>  |              | _      |       | INT41IP    | <2:0>   | -       | ı           | NT3IP<2:0>  | >                   | 0100 0100 0100 0100 |

| IPC10       | 00A8 | _      | FI     | LTAIP<2:0 | )>       | _      | L      | VDIP<2:0   | >            | _      | _     | _          | -       | -       |             | QEIIP<2:0>  |                     | 0100 0100 0000 0100 |

| IPC11       | 00AA | _      | _      | _         |          | _      | _      |            |              | _      | _     | _          | -       | -       | F           | LTBIP<2:0:  | >                   | 0000 0000 0000 0100 |

**Legend:** u = uninitialized bit

**Note:** Refer to "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

### 9.4 Timer Interrupt

The 16-bit timer has the ability to generate an interrupt on period match. When the timer count matches the period register, the T1IF bit is asserted and an interrupt will be generated, if enabled. The T1IF bit must be cleared in software. The timer interrupt flag T1IF is located in the IFS0 control register in the Interrupt Controller.

When the Gated Time Accumulation mode is enabled, an interrupt will also be generated on the falling edge of the gate signal (at the end of the accumulation cycle).

Enabling an interrupt is accomplished via the respective Timer Interrupt Enable bit, T1IE. The Timer Interrupt Enable bit is located in the IEC0 control register in the Interrupt Controller.

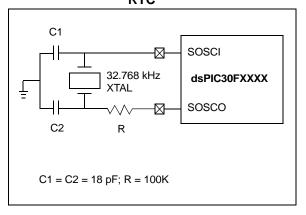

### 9.5 Real-Time Clock

Timer1, when operating in Real-Time Clock (RTC) mode, provides time-of-day and event time stamping capabilities. Key operational features of the RTC are:

- Operation from 32 kHz LP oscillator

- · 8-bit prescaler

- Low power

- Real-Time Clock Interrupts

These operating modes are determined by setting the appropriate bit(s) in the T1CON Control register

FIGURE 9-2: RECOMMENDED

COMPONENTS FOR

TIMER1 LP OSCILLATOR

RTC

#### 9.5.1 RTC OSCILLATOR OPERATION

When the TON = 1, TCS = 1 and TGATE = 0, the timer increments on the rising edge of the 32 kHz LP oscillator output signal, up to the value specified in the period register, and is then reset to '0'.

The TSYNC bit must be asserted to a logic '0' (Asynchronous mode) for correct operation.

Enabling LPOSCEN (OSCCON<1>) will disable the normal Timer and Counter modes and enable a timer carry-out wake-up event.

When the CPU enters Sleep mode, the RTC will continue to operate, provided the 32 kHz external crystal oscillator is active and the control bits have not been changed. The TSIDL bit should be cleared to '0' in order for RTC to continue operation in Idle mode.

#### 9.5.2 RTC INTERRUPTS

When an interrupt event occurs, the respective interrupt flag, T1IF, is asserted and an interrupt will be generated, if enabled. The T1IF bit must be cleared in software. The respective Timer interrupt flag, T1IF, is located in the IFS0 status register in the Interrupt Controller.

Enabling an interrupt is accomplished via the respective Timer Interrupt Enable bit, T1IE. The Timer Interrupt Enable bit is located in the IEC0 control register in the Interrupt Controller.

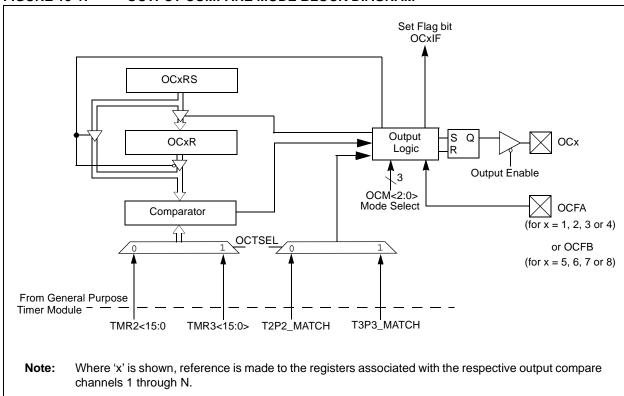

### 13.0 OUTPUT COMPARE MODULE

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

This section describes the Output Compare module and associated operational modes. The features provided by this module are useful in applications requiring operational modes such as:

- · Generation of Variable Width Output Pulses

- Power Factor Correction

Figure 13-1 depicts a block diagram of the Output Compare module.

The key operational features of the Output Compare module include:

- Timer2 and Timer3 Selection mode

- Simple Output Compare Match mode

- Dual Output Compare Match mode

- · Simple PWM mode

- · Output Compare during Sleep and Idle modes

- Interrupt on Output Compare/PWM Event

These operating modes are determined by setting the appropriate bits in the 16-bit OCxCON SFR (where x = 1,2,3,...,N). The dsPIC30F6010 device has 8 compare channels.

OCxRS and OCxR in the figure represent the Dual Compare registers. In the Dual Compare mode, the OCxR register is used for the first compare and OCxRS is used for the second compare.

FIGURE 13-1: OUTPUT COMPARE MODE BLOCK DIAGRAM

## TABLE 16-1: SPI1 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15                      | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6  | Bit 5 | Bit 4               | Bit 3 | Bit 2 | Bit 1  | Bit 0  | Reset State         |

|-------------|-------|-----------------------------|--------|---------|--------|--------|--------|-------|-------|-------|--------|-------|---------------------|-------|-------|--------|--------|---------------------|

| SPI1STAT    | 0220  | SPIEN                       | _      | SPISIDL | _      | _      | _      | _     |       | _     | SPIROV | _     | _                   | _     | _     | SPITBF | SPIRBF | 0000 0000 0000 0000 |

| SPI1CON     | 0222  | _                           | FRMEN  | SPIFSD  | _      | DISSDO | MODE16 | SMP   | CKE   | SSEN  | CKP    | MSTEN | SPRE2               | SPRE1 | SPRE0 | PPRE1  | PPRE0  | 0000 0000 0000 0000 |

| SPI1BUF     | 0224  | Transmit and Receive Buffer |        |         |        |        |        |       |       |       |        |       | 0000 0000 0000 0000 |       |       |        |        |                     |

**Legend:** u = uninitialized bit

**Note:** Refer to "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

## TABLE 16-2: SPI2 REGISTER MAP

| SFR Name | Addr. | Bit 15                      | Bit 14                                                                                | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6  | Bit 5               | Bit 4 | Bit 3               | Bit 2 | Bit 1  | Bit 0  | Reset State         |

|----------|-------|-----------------------------|---------------------------------------------------------------------------------------|---------|--------|--------|--------|-------|-------|-------|--------|---------------------|-------|---------------------|-------|--------|--------|---------------------|

| SPI2STAT | 0226  | SPIEN                       | _                                                                                     | SPISIDL | _      | _      | _      | _     | _     | _     | SPIROV | _                   | _     | _                   | _     | SPITBF | SPIRBF | 0000 0000 0000 0000 |

| SPI2CON  | 0228  | _                           | - FRMEN SPIFSD - DISSDO MODE16 SMP CKE SSEN CKP MSTEN SPRE2 SPRE1 SPRE0 PPRE1 PPRE0 0 |         |        |        |        |       |       |       |        | 0000 0000 0000 0000 |       |                     |       |        |        |                     |

| SPI2BUF  | 022A  | Transmit and Receive Buffer |                                                                                       |         |        |        |        |       |       |       |        |                     |       | 0000 0000 0000 0000 |       |        |        |                     |

**Legend:** u = uninitialized bit

**Note:** Refer to "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

## 18.10 UART Operation During CPU Sleep and Idle Modes

## 18.10.1 UART OPERATION DURING CPU SLEEP MODE

When the device enters Sleep mode, all clock sources to the module are shutdown and stay at logic '0'. If entry into Sleep mode occurs while a transmission is in progress, then the transmission is aborted. The UxTX pin is driven to logic '1'. Similarly, if entry into Sleep mode occurs while a reception is in progress, then the reception is aborted. The UxSTA, UxMODE, transmit and receive registers and buffers, and the UxBRG register are not affected by Sleep mode.

If the WAKE bit (UxMODE<7>) is set before the device enters Sleep mode, then a falling edge on the UxRX pin will generate a receive interrupt. The Receive Interrupt Select Mode bit (URXISEL) has no effect for this function. If the receive interrupt is enabled, then this will wake-up the device from Sleep. The UARTEN bit must be set in order to generate a wake-up interrupt.

## 18.10.2 UART OPERATION DURING CPU IDLE MODE

For the UART, the USIDL bit selects if the module will stop operation when the device enters Idle mode, or whether the module will continue on Idle. If USIDL = 0, the module will continue operation during Idle mode. If USIDL = 1, the module will stop on Idle.

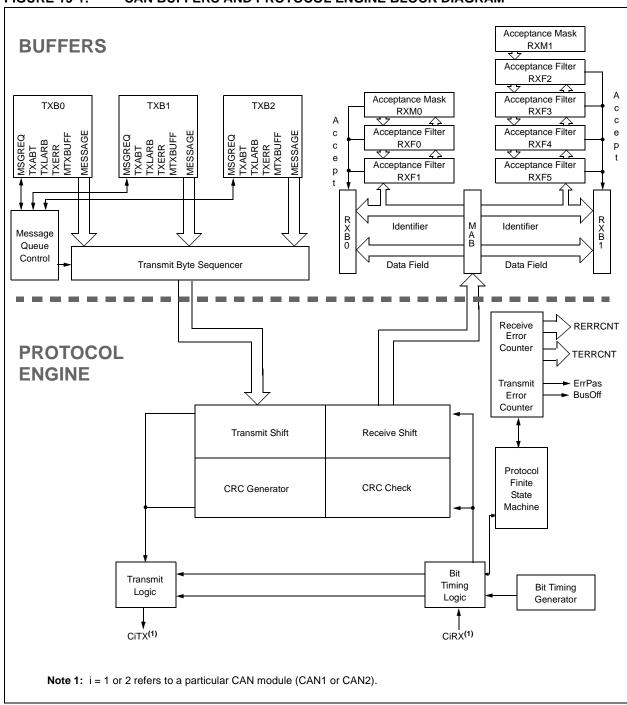

FIGURE 19-1: CAN BUFFERS AND PROTOCOL ENGINE BLOCK DIAGRAM

#### 19.6.2 PRESCALER SETTING

There is a programmable prescaler, with integral values ranging from 1 to 64, in addition to a fixed divide-by-2 for clock generation. The Time Quantum (TQ) is a fixed unit of time derived from the oscillator period, and is given by Equation 19-1, where FCAN is FCY (if the CANCKS bit is set or 4 FCY (if CANCKS is cleared).

**Note:** FCAN must not exceed 30 MHz. If CANCKS = 0, then FCY must not exceed 7.5 MHz.

## EQUATION 19-1: TIME QUANTUM FOR CLOCK GENERATION

TQ = 2 (BRP < 5:0 > + 1)/FCAN

#### 19.6.3 PROPAGATION SEGMENT

This part of the bit time is used to compensate physical delay times within the network. These delay times consist of the signal propagation time on the bus line and the internal delay time of the nodes. The Propagation Segment can be programmed from 1 TQ to 8 TQ by setting the PRSEG<2:0> bits (CiCFG2<2:0>).

#### 19.6.4 PHASE SEGMENTS

The phase segments are used to optimally locate the sampling of the received bit within the transmitted bit time. The sampling point is between Phase1 Seg and Phase2 Seg. These segments are lengthened or shortened by re-synchronization. The end of the Phase1 Seg determines the sampling point within a bit period. The segment is programmable from 1 TQ to 8 TQ. Phase2 Seg provides delay to the next transmitted data transition. The segment is programmable from 1 TQ to 8 TQ, or it may be defined to be equal to the greater of Phase1 Seg or the Information Processing Time (2 TQ). The Phase1 Seg is initialized by setting bits SEG1PH<2:0> (CiCFG2<5:3>), and Phase2 Seg is initialized by setting SEG2PH<2:0> (CiCFG2<10:8>).

The following requirement must be fulfilled while setting the lengths of the Phase Segments:

Propagation Segment + Phase1 Seg > = Phase2 Seg

#### 19.6.5 SAMPLE POINT

The Sample Point is the point of time at which the bus level is read and interpreted as the value of that respective bit. The location is at the end of Phase1 Seg. If the bit timing is slow and contains many TQ, it is possible to specify multiple sampling of the bus line at the sample point. The level determined by the CAN bus then corresponds to the result from the majority decision of three values. The majority samples are taken at the sample point and twice before with a distance of TQ/2. The CAN module allows the user to chose between sampling three times at the same point or once at the same point, by setting or clearing the SAM bit (CiCFG2<6>).

Typically, the sampling of the bit should take place at about 60-70% through the bit time, depending on the system parameters.

#### 19.6.6 SYNCHRONIZATION

To compensate for phase shifts between the oscillator frequencies of the different bus stations, each CAN controller must be able to synchronize to the relevant signal edge of the incoming signal. When an edge in the transmitted data is detected, the logic will compare the location of the edge to the expected time (Synchronous Segment). The circuit will then adjust the values of Phase1 Seg and Phase2 Seg. There are 2 mechanisms used to synchronize.

#### 19.6.6.1 Hard Synchronization

Hard Synchronization is only done whenever there is a 'recessive' to 'dominant' edge during Bus Idle, indicating the start of a message. After hard synchronization, the bit time counters are restarted with the Synchronous Segment. Hard synchronization forces the edge which has caused the hard synchronization to lie within the synchronization segment of the restarted bit time. If a hard synchronization is done, there will not be a re-synchronization within that bit time.

#### 19.6.6.2 Resynchronization

As a result of resynchronization, Phase1 Seg may be lengthened or Phase2 Seg may be shortened. The amount of lengthening or shortening of the phase buffer segment has an upper bound known as the Synchronization Jump Width, and is specified by the SJW<1:0> bits (CiCFG1<7:6>). The value of the synchronization jump width will be added to Phase1 Seg or subtracted from Phase2 Seg. The re-synchronization jump width is programmable between 1 TQ and 4 TQ.

The following requirement must be fulfilled while setting the SJW<1:0> bits:

Phase2 Seg > Synchronization Jump Width

#### 20.1 ADC Result Buffer

The module contains a 16-word dual port read-only buffer, called ADCBUFO...ADCBUFF, to buffer the A/D results. The RAM is 10 bits wide, but is read into different format 16-bit words. The contents of the sixteen ADC conversion result buffer registers, ADCBUF0 through ADCBUFF, cannot be written by user software.

### 20.2 Conversion Operation

After the ADC module has been configured, the sample acquisition is started by setting the SAMP bit. Various sources, such as a programmable bit, timer time-outs and external events, will terminate acquisition and start a conversion. When the A/D conversion is complete, the result is loaded into ADCBUF0...ADCBUFF, and the ADC interrupt flag ADIF and the DONE bit are set after the number of samples specified by the SMPI bit.

The following steps should be followed for doing an ADC conversion:

- 1. Configure the ADC module:

- Configure analog pins, voltage reference and digital I/O

- Select ADC input channels

- Select ADC conversion clock

- Select ADC conversion trigger

- Turn on ADC module

- 2. Configure ADC interrupt (if required):

- Clear ADIF bit

- Select A/D interrupt priority

- 3. Start sampling.

- 4. Wait the required acquisition time.

- 5. Trigger acquisition end, start conversion

- 6. Wait for ADC conversion to complete, by either:

- Waiting for the ADC interrupt

- Waiting for the DONE bit to get set

- 7. Read A/D result buffer, clear ADIF if required.

## 20.3 Selecting the Conversion Sequence

Several groups of control bits select the sequence in which the ADC connects inputs to the sample/hold channels, converts channels, writes the buffer memory, and generates interrupts. The sequence is controlled by the sampling clocks.

The SIMSAM bit controls the acquire/convert sequence for multiple channels. If the SIMSAM bit is '0', the two or four selected channels are acquired and converted sequentially, with two or four sample clocks. If the SIMSAM bit is '1', two or four selected channels are acquired simultaneously, with one sample clock. The channels are then converted sequentially. Obviously, if there is only 1 channel selected, the SIMSAM bit is not applicable.

The CHPS bits selects how many channels are sampled. This can vary from 1, 2 or 4 channels. If CHPS selects 1 channel, the CH0 channel will be sampled at the sample clock and converted. The result is stored in the buffer. If CHPS selects 2 channels, the CH0 and CH1 channels will be sampled and converted. If CHPS selects 4 channels, the CH0, CH1, CH2 and CH3 channels will be sampled and converted.

The SMPI bits select the number of acquisition/conversion sequences that would be performed before an interrupt occurs. This can vary from 1 sample per interrupt to 16 samples per interrupt.

The user cannot program a combination of CHPS and SMPI bits that specifies more than 16 conversions per interrupt, or 8 conversions per interrupt, depending on the BUFM bit. The BUFM bit, when set, will split the 16-word results buffer (ADCBUF0...ADCBUFF) into two 8-word groups. Writing to the 8-word buffers will be alternated on each interrupt event. Use of the BUFM bit will depend on how much time is available for moving data out of the buffers after the interrupt, as determined by the application.

If the processor can quickly unload a full buffer within the time it takes to acquire and convert one channel, the BUFM bit can be '0' and up to 16 conversions may be done per interrupt. The processor will have one sample and conversion time to move the sixteen conversions.

If the processor cannot unload the buffer within the acquisition and conversion time, the BUFM bit should be '1'. For example, if SMPI<3:0> (ADCON2<5:2>) = 0111, then eight conversions will be loaded into 1/2 of the buffer, following which an interrupt occurs. The next eight conversions will be loaded into the other 1/2 of the buffer. The processor will have the entire time between interrupts to move the eight conversions.

The ALTS bit can be used to alternate the inputs selected during the sampling sequence. The input multiplexer has two sets of sample inputs: MUX A and MUX B. If the ALTS bit is '0', only the MUX A inputs are selected for sampling. If the ALTS bit is '1' and SMPI<3:0> = 0000, on the first sample/convert sequence, the MUX A inputs are selected, and on the next acquire/convert sequence, the MUX B inputs are selected.

The CSCNA bit (ADCON2<10>) will allow the CH0 channel inputs to be alternately scanned across a selected number of analog inputs for the MUX A group. The inputs are selected by the ADCSSL register. If a particular bit in the ADCSSL register is '1', the corresponding input is selected. The inputs are always scanned from lower to higher numbered inputs, starting after each interrupt. If the number of inputs selected is greater than the number of samples taken per interrupt, the higher numbered inputs are unused.

### 20.13 Configuring Analog Port Pins

The use of the ADPCFG and TRIS registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CH0SA<3:0>/CH0SB<3:0> bits and the TRIS bits.

When reading the PORT register, all pins configured as analog input channels will read as cleared.

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin that is defined as a digital input (including the ANx pins), may cause the input buffer to consume current that exceeds the device specifications.

#### 20.14 Connection Considerations

The analog inputs have diodes to VDD and Vss as ESD protection. This requires that the analog input be between VDD and Vss. If the input voltage exceeds this range by greater than 0.3V (either direction), one of the diodes becomes forward biased and it may damage the device if the input current specification is exceeded.

An external RC filter is sometimes added for antialiasing of the input signal. The R component should be selected to ensure that the sampling time requirements are satisfied. Any external components connected (via high impedance) to an analog input pin (capacitor, zener diode, etc.) should have very little leakage current at the pin.

NOTES:

If the oscillator has a very slow start-up time coming out of POR, BOR or Sleep, it is possible that the PWRT timer will expire before the oscillator has started. In such cases, the FSCM will be activated and the FSCM will initiate a clock failure trap, and the COSC<1:0> bits are loaded with FRC oscillator selection. This will effectively shut-off the original oscillator that was trying to start.

The user may detect this situation and restart the oscillator in the clock fail trap ISR.

Upon a clock failure detection, the FSCM module will initiate a clock switch to the FRC Oscillator as follows:

- 1. The COSC bits (OSCCON<13:12>) are loaded with the FRC Oscillator selection value.

- 2. CF bit is set (OSCCON<3>).

- 3. OSWEN control bit (OSCCON<0>) is cleared.

For the purpose of clock switching, the clock sources are sectioned into four groups:

- 1. Primary

- 2. Secondary

- 3. Internal FRC

- 4. Internal LPRC

The user can switch between these functional groups, but cannot switch between options within a group. If the primary group is selected, then the choice within the group is always determined by the FPR<3:0> Configuration bits.

The OSCCON register holds the Control and Status bits related to clock switching.

- COSC<1:0>: Read only status bits always reflect the current oscillator group in effect.

- NOSC<1:0>: Control bits which are written to indicate the new oscillator group of choice.

- On POR and BOR, COSC<1:0> and NOSC<1:0> are both loaded with the Configuration bit values FOS<1:0>.

- LOCK: The LOCK status bit indicates a PLL lock.

- CF: Read only status bit indicating if a clock fail detect has occurred.

- OSWEN: Control bit changes from a '0' to a '1'

when a clock transition sequence is initiated.

Clearing the OSWEN control bit will abort a clock

transition in progress (used for hang-up

situations).

If Configuration bits FCKSM<1:0> = 1x, then the clock switching and fail-safe clock monitor functions are disabled. This is the default Configuration bit setting.

If clock switching is disabled, then the FOS<1:0> and FPR<3:0> bits directly control the oscillator selection and the COSC<1:0> bits do not control the clock selection. However, these bits will reflect the clock source selection.

Note: The application should not attempt to switch to a clock of frequency lower than 100 KHz when the fail-safe clock monitor is enabled. If such clock switching is performed, the device may generate an oscillator fail trap and switch to the Fast RC oscillator.

## 21.2.8 PROTECTION AGAINST ACCIDENTAL WRITES TO OSCCON

A write to the OSCCON register is intentionally made difficult because it controls clock switching and clock scaling.

To write to the OSCCON low byte, the following code sequence must be executed without any other instructions in between:

- Byte Write "0x46" to OSCCON low

- Byte Write "0x57" to OSCCON low

Byte Write is allowed for one instruction cycle. Write the desired value or use bit manipulation instruction.

To write to the OSCCON high byte, the following instructions must be executed without any other instructions in between:

- Byte Write "0x78" to OSCCON high

- Byte Write "0x9A" to OSCCON high

Byte Write is allowed for one instruction cycle. Write the desired value or use bit manipulation instruction.

Most single word instructions are executed in a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all Table Reads and Writes and RETURN/RETFIE instructions, which are single-word instructions, but take two or three cycles. Certain instructions that involve skipping over the subsequent instruction, require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word

or two-word instruction. Moreover, double-word moves require two cycles. The double-word instructions execute in two instruction cycles.

**Note:** For more details on the instruction set, refer to the "dsPIC30F/33F Programmer's Reference Manual" (DS70157).

TABLE 23-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

| Field           | Description                                                                 |

|-----------------|-----------------------------------------------------------------------------|

| #text           | Means literal defined by "text"                                             |

| (text)          | Means "content of text"                                                     |

| [text]          | Means "the location addressed by text"                                      |

| { }             | Optional field or operation                                                 |

| <n:m></n:m>     | Register bit field                                                          |

| .b              | Byte mode selection                                                         |

| .d              | Double-word mode selection                                                  |

| .S              | Shadow register select                                                      |

| . W             | Word mode selection (default)                                               |

| Acc             | One of two accumulators {A, B}                                              |

| AWB             | Accumulator write-back destination address register ∈ {W13, [W13]+=2}       |

| bit4            | 4-bit bit selection field (used in word addressed instructions) ∈ {015}     |

| C, DC, N, OV, Z | MCU status bits: Carry, Digit Carry, Negative, Overflow, Zero               |

| Expr            | Absolute address, label or expression (resolved by the linker)              |

| f               | File register address ∈ {0x00000x1FFF}                                      |

| lit1            | 1-bit unsigned literal ∈ {0,1}                                              |

| lit4            | 4-bit unsigned literal ∈ {015}                                              |

| lit5            | 5-bit unsigned literal ∈ {031}                                              |

| lit8            | 8-bit unsigned literal ∈ {0255}                                             |

| lit10           | 10-bit unsigned literal ∈ {0255} for Byte mode, {0:1023} for Word mode      |

| lit14           | 14-bit unsigned literal ∈ {016384}                                          |

| lit16           | 16-bit unsigned literal ∈ {065535}                                          |

| lit23           | 23-bit unsigned literal ∈ {08388608}; LSB must be 0                         |

| None            | Field does not require an entry, may be blank                               |

| OA, OB, SA, SB  | DSP status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate |

| PC              | Program Counter                                                             |

| Slit10          | 10-bit signed literal ∈ {-512511}                                           |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                       |

| Slit6           | 6-bit signed literal ∈ {-1616}                                              |

TABLE 23-2: INSTRUCTION SET OVERVIEW

| Base<br>Instr<br># | Assembly<br>Mnemonic |         | Assembly Syntax            | Description                                                               | # of<br>words | # of<br>cycle<br>s | Status Flags<br>Affected |

|--------------------|----------------------|---------|----------------------------|---------------------------------------------------------------------------|---------------|--------------------|--------------------------|

| 9                  | BTG                  | BTG     | f,#bit4                    | Bit Toggle f                                                              | 1             | 1                  | None                     |

|                    |                      | BTG     | Ws,#bit4                   | Bit Toggle Ws                                                             | 1             | 1                  | None                     |

| 10                 | BTSC                 | BTSC    | f,#bit4                    | Bit Test f, Skip if Clear                                                 | 1             | 1<br>(2 or<br>3)   | None                     |

|                    |                      | BTSC    | Ws,#bit4                   | Bit Test Ws, Skip if Clear                                                | 1             | 1<br>(2 or<br>3)   | None                     |

| 11                 | BTSS                 | BTSS    | f,#bit4                    | Bit Test f, Skip if Set                                                   | 1             | 1<br>(2 or<br>3)   | None                     |

|                    |                      | BTSS    | Ws,#bit4                   | Bit Test Ws, Skip if Set                                                  | 1             | 1<br>(2 or<br>3)   | None                     |

| 12                 | BTST                 | BTST    | f,#bit4                    | Bit Test f                                                                | 1             | 1                  | Z                        |

|                    |                      | BTST.C  | Ws,#bit4                   | Bit Test Ws to C                                                          | 1             | 1                  | С                        |

|                    |                      | BTST.Z  | Ws,#bit4                   | Bit Test Ws to Z                                                          | 1             | 1                  | Z                        |

|                    |                      | BTST.C  | Ws,Wb                      | Bit Test Ws <wb> to C</wb>                                                | 1             | 1                  | С                        |

|                    |                      | BTST.Z  | Ws,Wb                      | Bit Test Ws <wb> to Z</wb>                                                | 1             | 1                  | Z                        |

| 13                 | BTSTS                | BTSTS   | f,#bit4                    | Bit Test then Set f                                                       | 1             | 1                  | Z                        |

|                    |                      | BTSTS.C | Ws,#bit4                   | Bit Test Ws to C, then Set                                                | 1             | 1                  | С                        |

|                    |                      | BTSTS.Z | Ws,#bit4                   | Bit Test Ws to Z, then Set                                                | 1             | 1                  | Z                        |

| 14                 | CALL                 | CALL    | lit23                      | Call subroutine                                                           | 2             | 2                  | None                     |

|                    |                      | CALL    | Wn                         | Call indirect subroutine                                                  | 1             | 2                  | None                     |

| 15                 | CLR                  | CLR     | f                          | f = 0x0000                                                                | 1             | 1                  | None                     |

|                    |                      | CLR     | WREG                       | WREG = 0x0000                                                             | 1             | 1                  | None                     |

|                    |                      | CLR     | Ws                         | Ws = 0x0000                                                               | 1             | 1                  | None                     |

|                    |                      | CLR     | Acc, Wx, Wxd, Wy, Wyd, AWB | Clear Accumulator                                                         | 1             | 1                  | OA,OB,SA,SB              |

| 16                 | CLRWDT               | CLRWDT  |                            | Clear Watchdog Timer                                                      | 1             | 1                  | WDTO,Sleep               |

| 17                 | COM                  | COM     | f                          | $f = \overline{f}$                                                        | 1             | 1                  | N,Z                      |

|                    |                      | COM     | f,WREG                     | WREG = $\overline{f}$                                                     | 1             | 1                  | N,Z                      |

|                    |                      | COM     | Ws,Wd                      | $Wd = \overline{Ws}$                                                      | 1             | 1                  | N,Z                      |

| 18                 | CP                   | CP      | f                          | Compare f with WREG                                                       | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | CP      | Wb,#lit5                   | Compare Wb with lit5                                                      | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | CP      | Wb,Ws                      | Compare Wb with Ws (Wb - Ws)                                              | 1             | 1                  | C,DC,N,OV,Z              |

| 19                 | CP0                  | CP0     | f                          | Compare f with 0x0000                                                     | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | CP0     | Ws                         | Compare Ws with 0x0000                                                    | 1             | 1                  | C,DC,N,OV,Z              |

| 20                 | CPB                  | CPB     | f                          | Compare f with WREG, with Borrow                                          | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | CPB     | Wb,#lit5                   | Compare Wb with lit5, with Borrow                                         | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | CPB     | Wb,Ws                      | Compare $W\underline{b}$ with Ws, with Borrow (Wb - Ws - $\overline{C}$ ) | 1             | 1                  | C,DC,N,OV,Z              |

| 21                 | CPSEQ                | CPSEQ   | Wb, Wn                     | Compare Wb with Wn, skip if =                                             | 1             | 1<br>(2 or<br>3)   | None                     |

| 22                 | CPSGT                | CPSGT   | Wb, Wn                     | Compare Wb with Wn, skip if >                                             | 1             | 1<br>(2 or<br>3)   | None                     |

| 23                 | CPSLT                | CPSLT   | Wb, Wn                     | Compare Wb with Wn, skip if <                                             | 1             | 1<br>(2 or<br>3)   | None                     |

| 24                 | CPSNE                | CPSNE   | Wb, Wn                     | Compare Wb with Wn, skip if ≠                                             | 1             | 1<br>(2 or<br>3)   | None                     |

| 25                 | DAW                  | DAW     | Wn                         | Wn = decimal adjust Wn                                                    | 1             | 1                  | С                        |

| 26                 | DEC                  | DEC     | f                          | f = f -1                                                                  | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | DEC     | f,WREG                     | WREG = f -1                                                               | 1             | 1                  | C,DC,N,OV,Z              |

|                    | 1                    | DEC     | Ws, Wd                     | Wd = Ws - 1                                                               | 1             | 1                  | C,DC,N,OV,Z              |

TABLE 24-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

| DC CHARACT       | ERISTICS                 |     | (unless other | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |       |                |  |  |  |  |  |

|------------------|--------------------------|-----|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------|--|--|--|--|--|

| Parameter<br>No. | Typical <sup>(1,2)</sup> | Max | Units         | Units Conditions                                                                                                                                                                                                                                 |       |                |  |  |  |  |  |

| Operating Cur    | rent (IDD)               |     |               |                                                                                                                                                                                                                                                  |       |                |  |  |  |  |  |

| DC51a            | 6.7                      | 10  | mA            | 25°C                                                                                                                                                                                                                                             |       |                |  |  |  |  |  |

| DC51b            | 6.3                      | 10  | mA            | 85°C                                                                                                                                                                                                                                             | 3.3V  |                |  |  |  |  |  |

| DC51c            | 6.1                      | 10  | mA            | 125°C                                                                                                                                                                                                                                            | ]     | 0.128 MIPS     |  |  |  |  |  |

| DC51e            | 13                       | 18  | mA            | 25°C                                                                                                                                                                                                                                             |       | LPRC (512 kHz) |  |  |  |  |  |

| DC51f            | 13                       | 18  | mA            | 85°C                                                                                                                                                                                                                                             | 5V    |                |  |  |  |  |  |

| DC51g            | 13                       | 18  | mA            | 125°C                                                                                                                                                                                                                                            | 1     |                |  |  |  |  |  |

| DC50a            | 11                       | 15  | mA            | 25°C                                                                                                                                                                                                                                             |       |                |  |  |  |  |  |

| DC50b            | 10                       | 15  | mA            | 85°C                                                                                                                                                                                                                                             | 3.3V  |                |  |  |  |  |  |

| DC50c            | 10                       | 15  | mA            | 125°C                                                                                                                                                                                                                                            | 1     | (1.8 MIPS)     |  |  |  |  |  |

| DC50e            | 23                       | 35  | mA            | 25°C                                                                                                                                                                                                                                             |       | FRC (7.37 MHz) |  |  |  |  |  |

| DC50f            | 21                       | 35  | mA            | 85°C                                                                                                                                                                                                                                             | 5V    |                |  |  |  |  |  |

| DC50g            | 21                       | 35  | mA            | 125°C                                                                                                                                                                                                                                            | 1     |                |  |  |  |  |  |

| DC43a            | 17                       | 26  | mA            | 25°C                                                                                                                                                                                                                                             |       |                |  |  |  |  |  |

| DC43b            | 16                       | 26  | mA            | 85°C                                                                                                                                                                                                                                             | 3.3V  |                |  |  |  |  |  |

| DC43c            | 16                       | 26  | mA            | 125°C                                                                                                                                                                                                                                            | 1     | 4 MIDC         |  |  |  |  |  |

| DC43e            | 31                       | 44  | mA            | 25°C                                                                                                                                                                                                                                             |       | 4 MIPS         |  |  |  |  |  |

| DC43f            | 28                       | 44  | mA            | 85°C                                                                                                                                                                                                                                             | 5V    |                |  |  |  |  |  |

| DC43g            | 28                       | 44  | mA            | 125°C                                                                                                                                                                                                                                            | 1     |                |  |  |  |  |  |

| DC44a            | 31                       | 45  | mA            | 25°C                                                                                                                                                                                                                                             |       |                |  |  |  |  |  |

| DC44b            | 31                       | 45  | mA            | 85°C                                                                                                                                                                                                                                             | 3.3V  |                |  |  |  |  |  |

| DC44c            | 31                       | 45  | mA            | 125°C                                                                                                                                                                                                                                            | 1     | 40 MIDC        |  |  |  |  |  |

| DC44e            | 53                       | 69  | mA            | 25°C                                                                                                                                                                                                                                             |       | 10 MIPS        |  |  |  |  |  |

| DC44f            | 52                       | 69  | mA            | 85°C                                                                                                                                                                                                                                             | 5V    |                |  |  |  |  |  |

| DC44g            | 52                       | 69  | mA            | 125°C                                                                                                                                                                                                                                            | 1     |                |  |  |  |  |  |

| DC47a            | 54                       | 70  | mA            | 25°C                                                                                                                                                                                                                                             | 2 2)/ |                |  |  |  |  |  |

| DC47b            | 54                       | 70  | mA            | 85°C                                                                                                                                                                                                                                             | 3.3V  |                |  |  |  |  |  |

| DC47d            | 89                       | 110 | mA            | 25°C                                                                                                                                                                                                                                             |       | 20 MIPS        |  |  |  |  |  |

| DC47e            | 94                       | 110 | mA            | 85°C                                                                                                                                                                                                                                             | 5V    |                |  |  |  |  |  |

| DC47f            | 89                       | 110 | mA            | 125°C                                                                                                                                                                                                                                            | 1     |                |  |  |  |  |  |

| DC49a            | 125                      | 145 | mA            | 25°C                                                                                                                                                                                                                                             | E\/   | 30 MIPS        |  |  |  |  |  |

| DC49b            | 124                      | 145 | mA            | 85°C                                                                                                                                                                                                                                             | - 5V  | SU IVIIPS      |  |  |  |  |  |

**Note 1:** Data in "Typical" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

<sup>2:</sup> Base IIDLE current is measured with Core off, Clock on and all modules turned off.

## TABLE 24-24: TIMER2 AND TIMER4 EXTERNAL CLOCK TIMING REQUIREMENTS

AC CHARACTERISTICS Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated) Operating temperature  $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$  for Industrial  $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$  for Extended

| Param<br>No. | Symbol               | Characte                                  | Min                         | Тур                                     | Max     | Units | Conditions |                               |

|--------------|----------------------|-------------------------------------------|-----------------------------|-----------------------------------------|---------|-------|------------|-------------------------------|

| TB10         | TtxH                 | TxCK High Time                            | Synchronous, no prescaler   | 0.5 Tcy + 20                            | l       | _     | ns         | Must also meet parameter TB15 |

|              |                      |                                           | Synchronous, with prescaler | 10                                      | 1       |       | ns         |                               |

| TB11         | 1 TtxL TxCK Low Time |                                           | Synchronous, no prescaler   | 0.5 Tcy + 20                            |         | _     | ns         | Must also meet parameter TB15 |

|              |                      |                                           | Synchronous, with prescaler | 10                                      | _       | _     | ns         |                               |

| TB15         | TtxP                 | TxCK Input Period                         | Synchronous, no prescaler   | Tcy + 10                                | _       | _     | ns         | N = prescale value            |

|              |                      |                                           | Synchronous, with prescaler | Greater of:<br>20 ns or<br>(Tcy + 40)/N |         |       |            | (1, 8, 64, 256)               |

| TB20         | TCKEXT-<br>MRL       | Delay from Externa<br>Edge to Timer Incre | 0.5 Tcy                     | _                                       | 1.5 Tcy |       |            |                               |

### TABLE 24-25: TIMER3 AND TIMER5 EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHA       | RACTERIS | rics              | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |          |              |     |     |              |                               |  |

|--------------|----------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------|-----|-----|--------------|-------------------------------|--|

| Param<br>No. | Symbol   | Characte          | eristic                                                                                                                                                                                                                                           |          | Min          | Тур | Max | Units        | Conditions                    |  |

| TC10         | TtxH     | TxCK High Time    | Synchror                                                                                                                                                                                                                                          | nous     | 0.5 Tcy + 20 |     | _   | ns           | Must also meet parameter TC15 |  |

| TC11         | TtxL     | TxCK Low Time     | Synchror                                                                                                                                                                                                                                          | nous     | 0.5 Tcy + 20 |     |     | ns           | Must also meet parameter TC15 |  |

| TC15         | TtxP     | TxCK Input Period | nous,                                                                                                                                                                                                                                             | Tcy + 10 | _            | _   | ns  | N = prescale |                               |  |

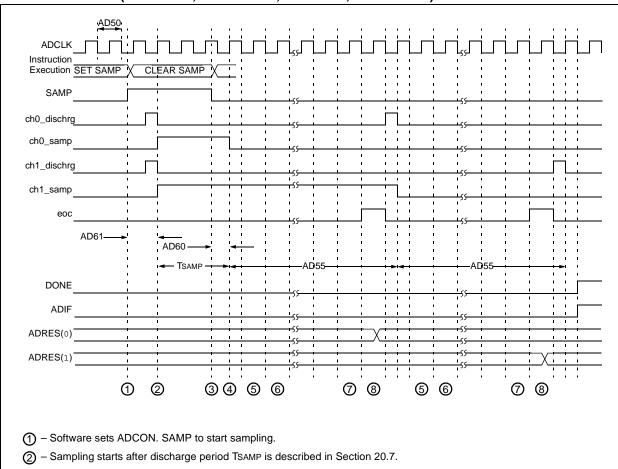

FIGURE 24-26: 10-BIT HIGH-SPEED A/D CONVERSION TIMING CHARACTERISTICS (CHPS = 01, SIMSAM = 0, ASAM = 0, SSRC = 000)

- 3 Software clears ADCON. SAMP to start conversion.

- (4) Sampling ends, conversion sequence starts.

- (5) Convert bit 9.

- 6 Convert bit 8.

- 7 Convert bit 0.

- (8) One TAD for end of conversion.

### APPENDIX A: REVISION HISTORY

#### Revision E (November 2006)

Previous versions of this data sheet contained Advance or Preliminary Information. They were distributed with incomplete characterization data.

Revision E of this document reflects the following updates:

- Supported I<sup>2</sup>C Slave Addresses (see Table 17-1)

- ADC Conversion Clock selection to allow 1 Msps operation (see Section 20.0 "10-bit High-Speed Analog-to-Digital Converter (ADC) Module")

- Base Instruction CP1 removed from instruction set (see Table 23-2)

- · Revised electrical characteristics:

- Operating Current (IDD) (see Table 24-5)

- Idle Current (IIDLE) (see Table 24-6)

- Power-down Current (IPD) (see Table 24-7)

- I/O Pin Input specifications (see Table 24-8)

- Brown-out Reset (BOR) (see Table 24-11)

- Watchdog Timer (see Table 24-21)