#### WIZnet - W7500P Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                             |

|----------------------------|----------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                    |

| Core Size                  | 32-Bit Single-Core                                 |

| Speed                      | 48MHz                                              |

| Connectivity               | Ethernet/TCP/IP, I <sup>2</sup> C, SSP, UART/USART |

| Peripherals                | DMA, POR, PWM, WDT                                 |

| Number of I/O              | 34                                                 |

| Program Memory Size        | 128KB (32K x 32)                                   |

| Program Memory Type        | FLASH                                              |

| EEPROM Size                | -                                                  |

| RAM Size                   | 16K x 8                                            |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                        |

| Data Converters            | A/D 9x12b                                          |

| Oscillator Type            | External, Internal                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                    |

| Mounting Type              | Surface Mount                                      |

| Package / Case             | 64-LQFP                                            |

| Supplier Device Package    | 64-TQFP (7x7)                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/wiznet/w7500p |

|                            |                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 23.3.         | 11 Programming the SSPCR1 Control Register           |  |  |  |

|---------------|------------------------------------------------------|--|--|--|

| 23.3.         | 12 Frame format                                      |  |  |  |

| 23.3.         | 13 Texas Instruments synchronous serial frame format |  |  |  |

| 23.3.         | 14 Motorola SPI frame format100                      |  |  |  |

| 23.3.         | 15 National Semiconductor Microwire frame format     |  |  |  |

| 23.3.         | 16 Master and Slave configurations108                |  |  |  |

| 23.3.         | 17 SSP Flow chart                                    |  |  |  |

| 24Pin Assign  | ment                                                 |  |  |  |

| 24.1 I        | Pin Descriptions                                     |  |  |  |

| 25 Electrical | Characteristics                                      |  |  |  |

| 25.1          | Absolute maximum ratings114                          |  |  |  |

| 25.1.         | 1 Voltage Characteristics                            |  |  |  |

| 25.1.         | 2 Current Characteristics114                         |  |  |  |

| 25.1.         | 3 Thermal Characteristics                            |  |  |  |

| 25.2 (        | Dperating conditions                                 |  |  |  |

| 25.2.         | 1 General Operating Conditions115                    |  |  |  |

| 25.2.         | 2 Supply Current Characteristics115                  |  |  |  |

| 25.3 I        | /O PAD Characteristics116                            |  |  |  |

| 25.3.         | 1 DC Specification                                   |  |  |  |

| 25.4 I        | Flash memory                                         |  |  |  |

| 25.5 I        | Electrical Sensitivity Characteristics116            |  |  |  |

| 25.5.         | 1 Electostatic discharge (ESD)116                    |  |  |  |

| 25.5.         | 2 Static latch-up117                                 |  |  |  |

| 25.6          | ADC Characteristics                                  |  |  |  |

| 25.6.         | 1 ADC Electrical characteristics117                  |  |  |  |

| 25.6.         | 2 ADC Transform function description118              |  |  |  |

| 25.7 I        | 2C interface Characteristics118                      |  |  |  |

| 25.8          | SP Interface Characteristics119                      |  |  |  |

| 26 Package C  | haracteristics                                       |  |  |  |

| 26.1 I        | Package dimension information120                     |  |  |  |

| 26.2 I        | 26.2 Package footprint information121                |  |  |  |

| Document Hi   | story Information                                    |  |  |  |

# List of table

| Table 1 W7500P interrupt assignments    18                                         |

|------------------------------------------------------------------------------------|

| Table 2 W7500P sleep mode summary    21                                            |

| Table 3. Offset Address for Common Register    26                                  |

| Table 4. Offset Address in Socket n Register Block (n = $0,,7$ , where n is Socket |

| number)                                                                            |

| Table 5 operation of mode selection                                                |

| Table 6 description of Flash memory    30                                          |

| Table 7 External oscillator clock sources    38                                    |

| Table 8 functional description table                                               |

| Table 9 Summary of the DMA requests for each channel         51                    |

| Table 10 DMA trigger points for the transmit and receive FIFOs                     |

| Table 11. Pin Type Notation    111                                                 |

| Table 12. W7500P Pin Description    112                                            |

| Table 13 Voltage characteristics    114                                            |

| Table 14 Current characteristics    114                                            |

| Table 15 Thermal Charateristics    114                                             |

| Table 16 General operating conditions    115                                       |

| Table 17 Normal operation supply current115                                        |

| Table 18 Sleep mode supply current                                                 |

| Table 19 Deep sleep mode supply current    115                                     |

| Table 20 DC specification of PAD    116                                            |

| Table 21 Flash memory Reliability Characteristics    116                           |

| Table 22 Electrostatic discharge (ESD)    116                                      |

| Table 23 Static latch-up    117                                                    |

| Table 24 ADC electrical characteristics    117                                     |

| Table 25 I2C characteristics    118                                                |

| Table 26 SSP characteristics    119                                                |

| Table 27 Package mechanical data120                                                |

| IRQ[13] | Dualtimer1 | Dualtimer1 global interrupt   | 0x0000_0074 |

|---------|------------|-------------------------------|-------------|

| IRQ[14] | PWM0       | PWM0 global interrupt         | 0x0000_0078 |

| IRQ[15] | PWM1       | PWM1 global interrupt         | 0x0000_007C |

| IRQ[16] | PWM2       | PWM2 global interrupt         | 0x0000_0080 |

| IRQ[17] | PWM3       | PWM3 global interrupt         | 0x0000_0084 |

| IRQ[18] | PWM4       | PWM4 global interrupt         | 0x0000_0088 |

| IRQ[19] | PWM5       | PWM5 global interrupt         | 0x0000_008C |

| IRQ[20] | PWM6       | PWM6 global interrupt         | 0x0000_0090 |

| IRQ[21] | PWM7       | PWM7 global interrupt         | 0x0000_0094 |

| IRQ[22] | reserved   |                               | 0x0000_0098 |

| IRQ[23] | ADC        | ADC acquisition end interrupt | 0x0000_009C |

| IRQ[24] | TCPIP      | TCPIP global interrupt        | 0x000_00A0  |

| IRQ[25] | EXT_INT    | External pin interrupt        | 0x0000_00A4 |

| IRQ[26] | reserved   |                               | 0x0000_00A8 |

| IRQ[27] | reserved   |                               | 0x000_00AC  |

| IRQ[28] | reserved   |                               | 0x0000_00B0 |

| IRQ[29] | reserved   |                               | 0x0000_00B4 |

| IRQ[30] | reserved   |                               | 0x0000_00B8 |

| IRQ[31] | reserved   |                               | 0x0000_00BC |

## 4.3 Event

W7500P is able to handle internal events in order to wake up the core(WFE). The wakeup event can be generated by

• When after DMA process finished

# 5 Power supply

## 5.1 Introduction

W7500P embeds a voltage regulator in order to supply the internal 1.5V digital power domain.

- Require a 2.7V ~ 5.5V operating supply voltage (VDD)

- ADC ref voltage is same as VDD

# 5.2 Voltage regulator

The voltage regulator is always enabled after Reset and works in only one mode.

- In Run mode, the regulator supplies full power to the 1.5V domain.

- There is no power down or sleep mode

Two of them are almost the same except the clock gated peripherals kinds. Table 2 shows the Sleep mode summary.

| Mode            | Entry         | Wakeup          | Effect on clocks  |

|-----------------|---------------|-----------------|-------------------|

|                 | DEEPSLEEP = 0 | Apvintorrupt    | CPU clock OFF     |

| Clean made      | Enable WFI    | Any interrupt   | APB Bus Clock ON  |

| Sleep mode      | DEEPSLEEP = 0 |                 | AHB Bus clock ON  |

|                 | Enable WFE    | Wakeup event    | Memory clocks ON  |

|                 | DEEPSLEEP = 1 | Anne interreset | CPU clock OFF     |

| Deep Sleep mode | Enable WFI    | Any interrupt   | APB Bus Clock OFF |

|                 | DEEPSLEEP = 1 | Wakeup event    | AHB Bus clock OFF |

|                 | Enable WFE    | Wakeup event    | Memory clocks OFF |

Table 2 W7500P sleep mode summary

# 5.4.2 Peripheral clock gating

In Run mode, individual clocks can be stopped at any time to reduce power.

Peripheral clock gating is controlled by the CRG block.

Below is the list of clocks which can be gating in CRG block.

- ADC clock (ADCCLK)

- SSP0, SSP1 clock (SSPCLK)

- UARTO, UART1 clock (UARTCLK)

- Two Timer clocks (TIMCLK0, TIMCLK1)

- 8ea PWM clocks (PWMCLK0 ~ PWMCLK7)

- WDOG clock (WDOGCLK)

- Random number generator clock (RNGCLK)

# 6 System tick timer

#### 6.1 Introduction

System tick timer(SysTick) is part of the ARM Cortex-M0 core

#### 6.2 Features

Simple 24bit timer.

Clocked internally by the system clock or the system clock/2.

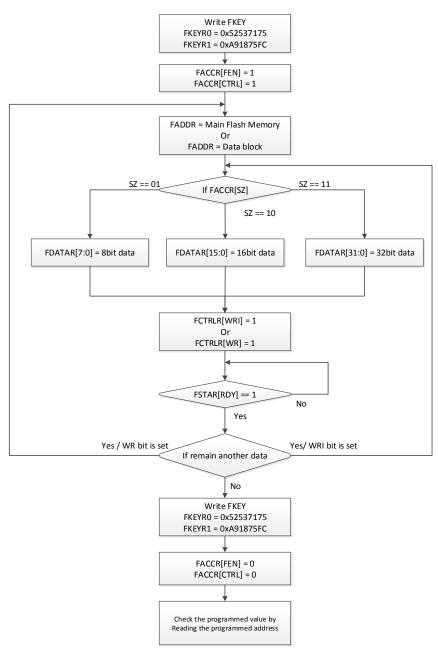

## 9.2.4 Flash program operation

The main Flash memory can be programmed word, half word, or 1 byte at a time by SZ bit of FACCR. The program operation is started when the CPU writes a data into a main Flash memory address with the WRI or WR bit of FCTRLR register set.

The main Flash memory programming sequence in standard mode is as below:

Figure 9. main Flash memory programming sequence

1. Check that no main Flash memory operation is ongoing by checking the RDY bit in the FSTATR register.

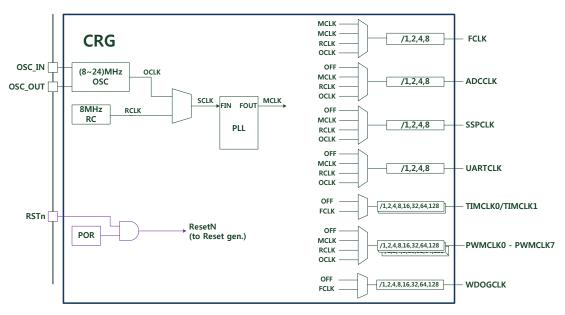

# 10 Clock Reset generator (CRG)

### 10.1 Introduction

CRG is clock reset generator block for W7500P System. It provides every clock/reset for all other block include CPU and peripherals. CRG includes PLL and POR.

## 10.2 Features

#### 10.2.1Reset

- Three types of reset external reset, Power reset, system reset

- External reset is generated by low level on the RSTn pin (external reset)

- Power reset is generated by Power-on reset (POR)

- Power on reset is generated by POR

- System reset is generated when one of the following events occurs

- Watchdog event

- After remapping

- Software reset (SYSRESETREQ bit in Cortex-M0. Refer to the Cortex-M0 technical reference manual for more detail)

- Power reset sets all registers to their reset values.

- System reset sets all registers to their reset values except the CRG block registers and remap register to protect remap value

# 10.2.2Clock

Two clock sources can be used to drive the system clock.

- External oscillator clock (8MHz ~ 24MHz) (OCLK)

- Internal 8MHz RC oscillator clock (RCLK)

One additional clock source

• 32.768KHz low speed external crystal which derives the real time clock.

There is a PLL

One PLL is integrated

- Input clock range is from 8MHz to 24MHz

- Frequency can be generated by M/N/OD registers. (refer register description)

- Bypass option enabled

There are many generated clocks for independent operating with system clock

- System clock (FCLK)

- ADC clock (ADCCLK)

- SSP0, SSP1 clock (SSPCLK)

- UART0, UART1 clock (UARTCLK)

- Two Timer clocks (TIMCLK0, TIMCLK1)

- 8ea PWM clocks (PWMCLK0 PWMCLK7)

- Real time clock (RTCCLK)

- WDOG clock (WDOGCLK)

- Random number generator clock (RNGCLK)

RNGCLK have only one source (pll output) and no prescaler

Some of the generated clocks turn off automatically when CPU enters sleep mode.

ADCCLK, RNGCLK

Generate two Hardware TCPIP Clocks (MII\_RXC, MII\_TXC) are from external PADs.

Hardware TCPIP Clocks can be gated by register control.

All clocks generated from CRG can be monitored.

# 10.3 Functional description

Figure 10 shows the CRG block diagram.

# 10.3.1External Oscillator Clock

External oscillator clock (OCLK) can be generated from two possible clock source

- External crystal/ceramic resonator (8 to 24MHz external oscillator)

- User external clock

Table 7 shows the two clock sources of external oscillator clock

Table 7 External oscillator clock sources

| External clock | Crystal/ |

|----------------|----------|

|----------------|----------|

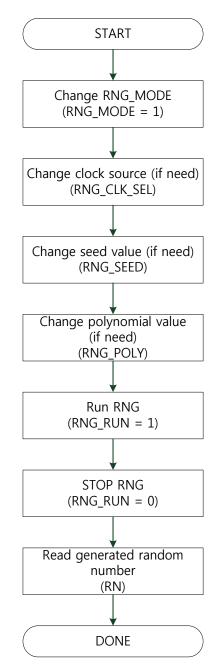

# 11.3.1 Operation RNG

Figure 12 shows the flowchart of RNG operation.

A random number is automatically generated after powering on reset,

Follow the procedure below to manually generate a random number.

- 1. Change MODE to start/stop by register.

- 2. Change clock source / seed value / polynomial value if need.

- 3. Run and Stop the RNG.

- 4. Read Random value.

Figure 12. Flow chart of RNG operation

| PB_06 | 15 | DUP       | GPIOB_6  |           |      |

|-------|----|-----------|----------|-----------|------|

| PC_00 | 53 | U_CTS1    | GPIOC_0  | PWM0/CAP0 |      |

| PC_01 | 54 | U_RTS1    | GPIOC_1  |           |      |

| PC_02 | 55 | U_TXD1    | GPIOC_2  | PWM2/CAP2 |      |

| PC_03 | 56 | U_RXD1    | GPIOC_3  |           |      |

| PC_04 | 57 | SCL1      | GPIOC_4  | PWM4/CAP4 |      |

| PC_05 | 58 | SDA1      | GPIOC_5  | PWM5/CAP5 |      |

| PC_06 | 11 | GPIOC_6   | GPIOC_6  | U_TXD2    |      |

| PC_08 | 1  | PWM0/CAP0 | GPIOC_8  | SCL0      | AIN7 |

| PC_09 | 2  | PWM1/CAP1 | GPIOC_9  | SDA0      | AIN6 |

| PC_10 | 3  | U_TXD2    | GPIOC_10 | PWM2/CAP2 | AIN5 |

| PC_11 | 4  | U_RXD2    | GPIOC_11 | PWM3/CAP3 | AIN4 |

| PC_12 | 5  | AIN3      | GPIOC_12 | SSELO     | AIN3 |

| PC_13 | 6  | AIN2      | GPIOC_13 | SCLK0     | AIN2 |

| PC_14 | 7  | AIN1      | GPIOC_14 | MISOO     | AIN1 |

| PC_15 | 8  | AINO      | GPIOC_15 | MOSIO     | AINO |

# 13 External Interrupt (EXTI)

## 13.1 Introduction

Each functional pads are connected to the external interrupt(EXTINT) source.

# 13.2 Features

- All functional pads can be used as an external interrupt source regardless of any set of pad function.

- External Interrupt controller has the following functions and can be controlled by registers.

- Interrupt mask (enable or disable, default : disable)

- Interrupt polarity (rising or falling, default : rising)

# 13.3 Functional description

All pads are connected to the control register individually. (External interrupt mask register and External Interrupt polarity register)

External interrupt working as following expression:

- Each pad interrupt = Interrupt mask & (Interrupt polarity ^ Pad input)

- EXTINT = any Each pad interrupt

Figure 13 shows the External Interrupt diagram.

In this mode, the controller can be configured to use either the primary or the alternate channel control data structure. After the channel is enabled and the controller receives a request for this channel, the flow for the auto-request cycle is as below:

- 1. The controller performs  $2^{R}$  transfers. If the number of transfers remaining is zero the flow continues at step 3.

- 2. The controller arbitrates if there are any transfers remaining after 2<sup>R</sup> transfers. If the current channel c has the highest priority, the cycle continues at step 1.

The controller sets dma\_done[c] signal for this channel HIGH for one system clock cycle. This indicates to the host processor that the DMA cycle is complete.

#### 16.3.3.4 Ping-pong cycle

In this mode, the controller performs a DMA cycle using one of the data structures and then performs a DMA cycle using the other data structure. The controller continues to switch between primary and alternate structures until it reads a data structure that is invalid, until the user reprograms the cycle\_type to basic, or until the host processor disables the channel.

In ping-pong mode, the user can program or reprogram one of the two channel data structures (primary or alternate) while using the other channel data structure for the active transfer. When a transfer is done, the next transfer can be started immediately using the prepared channel data structure - provided that a higher priority channel does not require servicing. If the user does not reprogram the channel control data structure not in use for a transfer, the cycle type remains invalid (which is the value at the end of the last transfer using that structure), and the ping-pong cycle completes.

The ping-pong cycle can be used for transfers to or from peripherals or for memory- to-memory transfers.

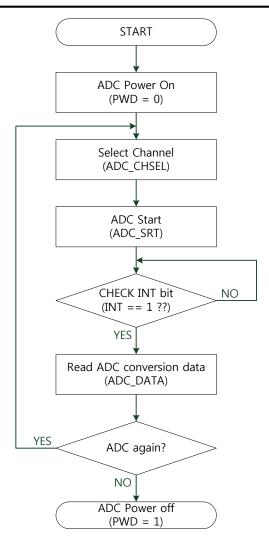

Figure 23. The ADC operation flowchart with non-interrupt

# 19.3 Functional description

## 19.3.1 Clock and clock enable

The dual timers contain PCLK and TIMERCLK clock inputs. PCLK is the main APB system clock and is used by the register interface. TIMERCLK is the input to the prescale units and the decrementing counters. PCLK and TIMERCLK are synchronous.

The dual timers consist two programmable 32-bit Free-Running Counters(FRC) which operate independently. The two timers operate from one TIMERCLK but Each FRC is controlled independently by individual clock enable.

### 19.3.2 Timer size

Users can select FRC as 16-bit or 32-bit using the control register.

### 19.3.3 Prescaler

The timer has a prescaler that can divide down the enabled clock rate by 1, 16 or 256.

### 19.3.4 Repetition mode

There are two repetition mode: one-shot and wrapping mode. Wrapping mode has two modes: free-running and periodic mode.

#### One-shot mode

The counter generates an interrupt once. When the counter reaches 0, it halts until users reprogram it. Users can do this as below:

- Clear the one-shot count bit in the control register, in which case the count proceeds according to the selection of wrapping mode(free-running or periodic mode).

- Write a new value to the Load Value register.

#### Wrapping mode

#### Free-running mode

The counter wraps after reaching its zero value, and continues to count down from the maximum value. This is the default mode.

#### Periodic mode

Figure 45. I2C Bus Configuration

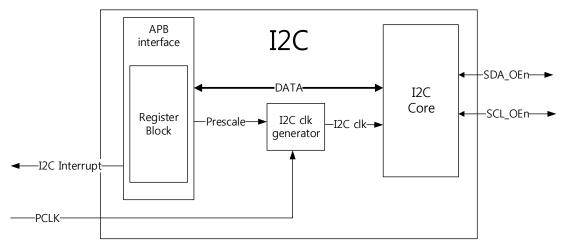

Figure 46 shows the I2C block diagram.

In addition to receiving and transmitting data, this interface converts it from serial to parallel format and vice versa. The interrupt is enabled or disabled by software. The interface is connected to the  $I^2C$  bus by a data pin (SDA) and by a Clock pin (SCL). It can be connected with a standard (up to 100 KHz)  $I^2C$  bus.

Figure 46. I2C block diagram

SDA is the bi- directions serial data line and SCL is the bi-directions serial clock line. The bus is considered idle when both lines are high. Every transaction on the  $I^2C$  bus is nine bits long, consisting of eight data bits and a single acknowledge bit and data must be transferred MSB first.

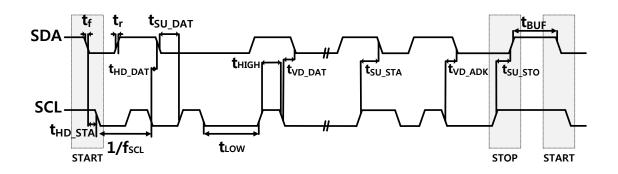

## 21.3.1 Data validity

The data on the SDA line must be stable during the HIGH period of the SCL. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW (Figure 47). One clock pulse is generated for each data bit transferred.

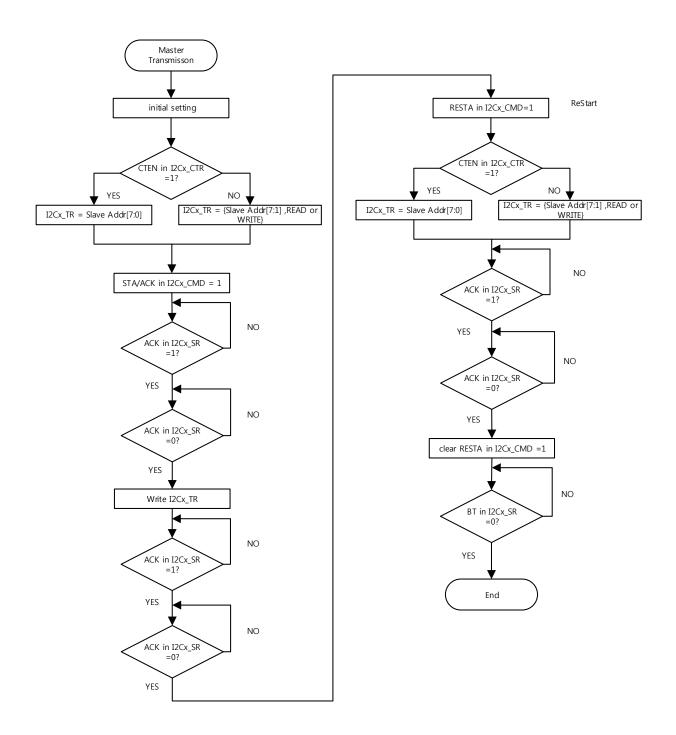

Figure 55 shows the operation of repeated START.

The repeated START operates for data read operation execution.

The operation sequences are Slave address, send data, repeated START, and send data.

Figure 55. Master Transmit with Repeated START

### 22.3.2 Data transmission

Data transmitted is stored in a 32-byte FIFOs. Transmit data is written into the transmit FIFO for transmission. If UART is enabled, it causes a data frame to start transmitting with parameters indicated in the UARTxLCR\_H.

Data continues to transmit until there is no data left in the transmit FIFO. The BUSY bit of UARTxFR is '1' as soon as data is written to the transmit FIFO, which means the FIFO is not empty, and remains as '1' while data is being transmitted.

### 22.3.3 Data receive

Received data is stored in the 32-byte FIFOs. When a start bit has been received, it begins running and data is sampled on the eighth cycle of that counter in UART mode. A valid stop bit is confirmed if UARTRXD is '1'. When a full word is received, the data is stored in the receive FIFO. Error bit is stored in bit[10:8] of UARTxCR and overrun is stored in bit[11] of UARTxCR.

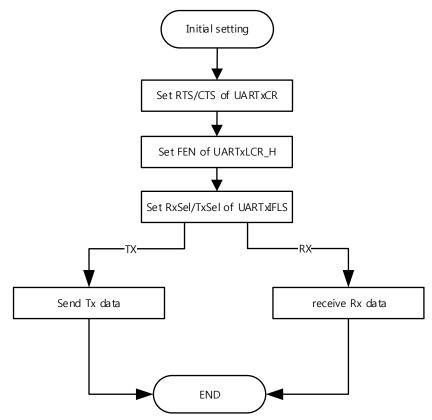

Figure 61. Transmit and Receive data flow chart

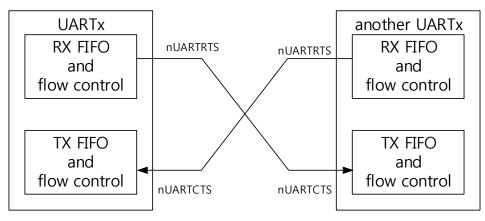

## 22.3.4 Hardware flow control

Figure 62. Hardware flow control description

The RTS flow control is enabled by setting the RTSen of UARTxCR. If RTS is enabled, the data flow is controlled as follows.

When the receiver FIFO level reaches the programmed trigger level, nUARTRTS(pin) is asserted(to a low value). nUARTRTS is reasserted(to a low level) once the receiver FIFO has reached the previous trigger level. The reasserted of nUARTRTS signals to the sending UART to continue transmitting data.

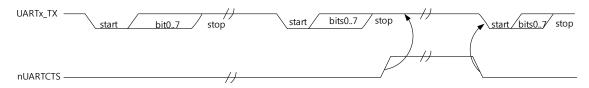

The CTS flow control is enabled, the transmitter can only transmit data when nUARTCTS is asserted. When nUARTCTR is re-asserted(to a low) the transmitter sends the next byte. To stop the transmitter from sending the following byte, nUARTCTS must be released before the middle of the last stop bit that is currently being sent.

Figure 63. CTS Functional Timing

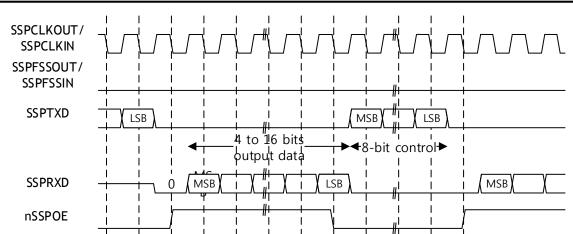

## 23.3.8 Enable PrimeCell SSP operation

You can either prime the transmit FIFO, by writing up to eight 16-bit values when the PrimeCell SSP is disabled, or permit the transmit FIFO service request to interrupt the CPU. Once enabled, transmission or reception of data begins on the transmit, SSPTXD, and receive, SSPRXD, pins.

## 23.3.9 Clock ratios

There is a constraint on the ratio of the frequencies of PCLK to SSPCLK. The frequency of SSPCLK must be less or equal to that of PCLK. This ensures that control signals from the SSPCLK domain to the PCLK domain are guaranteed to get synchronized before one frame duration: FSSPCLK <= FPCLK.

In the slave mode of operation, the SSPCLKIN signal from the external master is doublesynchronized and then delayed to detect an edge. It takes three SSPCLKs to detect an edge on SSPCLKIN. SSPTXD has less setup time to the falling edge of SSPCLKIN on which the master is sampling the line.

The setup and hold times on SSPRXD, with reference to SSPCLKIN, must be more conservative to ensure that it is at the right value when the actual sampling occurs within the SSPMS. To ensure correct device operation, SSPCLK must be at least 12 times faster than the maximum expected frequency of SSPCLKIN.

The frequency selected for SSPCLK must accommodate the desired range of bit clock rates. The ratio of minimum SSPCLK frequency to SSPCLKOUT maximum frequency in the case of the slave mode is 12, and for the master mode, it is two.

To generate a maximum bit rate of 1.8432Mbps in the master mode, the frequency of SSPCLK must be at least 3.6864MHz. With an SSPCLK frequency of 3.6864MHz, the SSPCPSR register must be programmed with a value of 2, and the SCR[7:0] field in the SSPCR0 register must be programmed with a value of 0.

To work with a maximum bit rate of 1.8432Mbps in the slave mode, the frequency of SSPCLK must be at least 22.12MHz. With an SSPCLK frequency of 22.12MHz, the SSPCPSR register can be programmed with a value of 12 and the SCR[7:0] field in the SSPCRO register can be programmed with a value of 0. Similarly, the ratio of SSPCLK maximum frequency to SSPCLKOUT minimum frequency is 254 x 256.

The minimum frequency of SSPCLK is calculated by the following equations, both of which must be satisfied:

FSSPCLK(min) => 2 x FSSPCLKOUT(max), for master mode

Figure 76. National Semiconductor Microwire frame format, continuous transfers

## 23.3.16 Master and Slave configurations

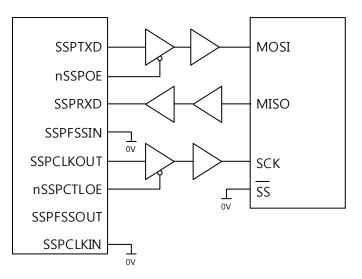

Figure 77 shows how a PrimeCell SSP (PL022) configured as master, interfaces to a Motorola SPI slave. The SPI Slave Select (SS) signal is permanently tied LOW and configures it as a slave. Similar to the above operation, the master can broadcast to the slave through the master PrimeCell SSP SSPTXD line. In response, the slave drives its SPI MISO port onto the SSPRXD line of the master.

Figure 77. PrimeCell SSP master coupled to an SPI slave

Figure 78 shows a Motorola SPI configured as a master and interfaced to an instance of a PrimeCell SSP (PL022) configured as a slave. In this case, the slave Select Signal (SS) is permanently tied HIGH to configure it as a master. The master can broadcast to the slave through the master SPI MOSI line. In response, the slave drives its nSSPOE signal LOW. This enables its SSPTXD data onto the MISO line of the master.

| t <sub>vd_dat</sub> | Data valid time                          |     | 3.5 |     | 1.0 | us |

|---------------------|------------------------------------------|-----|-----|-----|-----|----|

| t <sub>su_dat</sub> | Data setup time                          | 200 |     | 90  |     | ns |

| t <sub>VD_ACK</sub> | Data valid acknowledge time              |     | 3.5 |     | 1.0 | us |

| t <sub>HD_STA</sub> | Hold time START condition                | 3.8 |     | 0.5 |     | us |

| t <sub>su_sta</sub> | Set-up time for a repeat START condition | 4.5 |     | 0.5 |     | us |

| t <sub>su_sto</sub> | Set-up time for STOP condition           | 3.8 |     | 0.5 |     | us |

Figure 83. I2C bus AC waveform

# 25.8 SSP Interface Characteristics

Table 26 shows the SSP characteristics of W7500P.

| Symbol             | Parameter                        | Conditions                 | Min | Max | Unit |

|--------------------|----------------------------------|----------------------------|-----|-----|------|

| f                  | SSD clock froquency              | Master mode                |     | 20  | MHz  |

| $f_{SCL}$          | SSP clock frequency              | Slave mode                 |     | 20  | MHz  |

| t <sub>r_SCK</sub> | SSP clock rising and fall time   | Capacitive load : C = 25pF |     | 8   | ns   |

| t <sub>su_m</sub>  | Data input satur time            | Master mode                | 5   |     | ns   |

| t <sub>su_s</sub>  | Data input setup time            | Slave mode                 | 6   |     | ns   |

| t <sub>H_M</sub>   | Data input hold time             | Master mode                | 5   |     | ns   |

| t <sub>H_s</sub>   | Data input hold time             | Slave mode                 | 6   |     | ns   |

| t <sub>v_M</sub>   | Data output valid time           | Master mode                |     | 20  | ns   |

| tv_s               | Data output valid time           | Slave mode                 |     | 5   | ns   |

| t <sub>H_M</sub>   | Data output hold time            | Master mode                | 13  |     |      |

| t <sub>H_s</sub>   | Data output hold time            | Slave mode                 | 3   |     |      |

| DuCy               | SPI slave input clock duty cycle | Slave mode                 | 45  | 55  | %    |

Table 26 SSP characteristics

# Document History Information

| Version    | Date      | Descriptions                                                                                                                                                                                                                                    |  |

|------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Ver. 1.0.0 | 07SEP2015 | Initial Release                                                                                                                                                                                                                                 |  |

| Ver. 1.0.1 | 18NOV2015 | Corrected Package diagram error                                                                                                                                                                                                                 |  |

| Ver. 1.0.2 | 08JAN2016 | <ol> <li>Bit rate in SPI interface changed 'up to 20MHz and higher' to 'up<br/>to 20MHz'.</li> <li>Bit rate generation example changed in 23.3.11 Programming the<br/>SSPCR1 Control Register.</li> </ol>                                       |  |

| Ver. 1.0.3 | 05FEB2016 | Modified the problem with none mention of 2 <sup>nd</sup> Function on PB_06 in Table 28 functional description table                                                                                                                            |  |

| Ver. 1.0.4 | 08MAR2016 | <ol> <li>In 2.2.2Memory map, GPIO0,1,2,3 changed to GPIOA,B,C,D</li> <li>In Table 1 W7500P interrupt assignments, GPIO0,1,2,3 changed to GPIOA,B,C,D</li> <li>In Table 8 functional description table, GPIO1,2,3 changed to GPIOA,B,C</li></ol> |  |

| Ver. 1.0.5 | 18JUL2017 | 1. In Table 7 External oscillator clock sources, switching External clock Schematic with Crystal/Ceramic resonators Schematic.                                                                                                                  |  |

| Ver. 1.0.6 | 19JUL2017 | 1. Modified $T_A$ , $T_J$ temperature range in Table 16 General operating conditions.                                                                                                                                                           |  |