# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 48                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                            |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | -                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f321bar6t6 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# FLASH PROGRAM MEMORY (Cont'd)

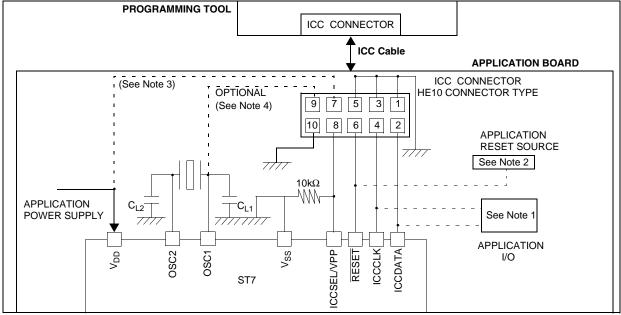

# 4.4 ICC Interface

ICC needs a minimum of 4 and up to 6 pins to be connected to the programming tool (see Figure 7). These pins are:

- RESET: device reset

- V<sub>SS</sub>: device power supply ground

# Figure 7. Typical ICC Interface

- ICCCLK: ICC output serial clock pin

- ICCDATA: ICC input/output serial data pin

- ICCSEL/V<sub>PP</sub>: programming voltage

- OSC1(or OSCIN): main clock input for external source (optional)

- V<sub>DD</sub>: application board power supply (optional, see Figure 7, Note 3)

## Notes:

1. If the ICCCLK or ICCDATA pins are only used as outputs in the application, no signal isolation is necessary. As soon as the Programming Tool is plugged to the board, even if an ICC session is not in progress, the ICCCLK and ICCDATA pins are not available for the application. If they are used as inputs by the application, isolation such as a serial resistor has to implemented in case another device forces the signal. Refer to the Programming Tool documentation for recommended resistor values.

2. During the IC<u>C</u> session, the programming tool must control the RESET pin. This can lead to conflicts between the programming tool and the application reset circuit if it drives more than 5mA at high level (push pull output or pull-up resistor<1K). A schottky diode can be used to isolate the application RESET circuit in this case. When using a classical RC network with R>1K or a reset management IC with open drain output and pull-up resistor>1K, no additional components are needed. In all cases the user must ensure that no external reset is generated by the application during the ICC session.

3. The use of Pin 7 of the ICC connector depends on the Programming Tool architecture. This pin must be connected when using most ST Programming Tools (it is used to monitor the application power supply). Please refer to the Programming Tool manual.

4. Pin 9 has to be connected to the OSC1 or OS-CIN pin of the ST7 when the clock is not available in the application or if the selected clock option is not programmed in the option byte. ST7 devices with multi-oscillator capability need to have OSC2 grounded in this case.

57

# CENTRAL PROCESSING UNIT (Cont'd)

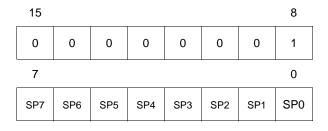

# Stack Pointer (SP)

# Read/Write

**47/**

Reset Value: 01 FFh

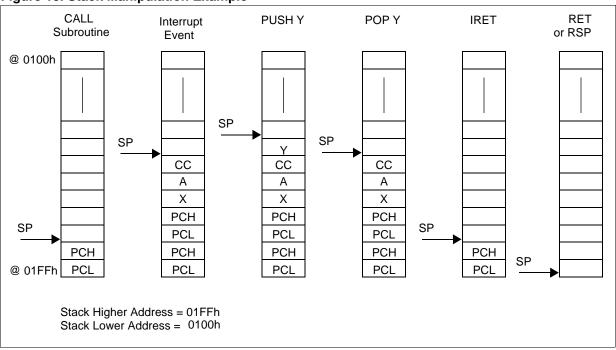

The Stack Pointer is a 16-bit register which is always pointing to the next free location in the stack. It is then decremented after data has been pushed onto the stack and incremented before data is popped from the stack (see Figure 2).

Since the stack is 256 bytes deep, the 8 most significant bits are forced by hardware. Following an MCU Reset, or after a Reset Stack Pointer instruction (RSP), the Stack Pointer contains its reset value (the SP7 to SP0 bits are set) which is the stack higher address.

# Figure 10. Stack Manipulation Example

The least significant byte of the Stack Pointer (called S) can be directly accessed by a LD instruction.

**Note:** When the lower limit is exceeded, the Stack Pointer wraps around to the stack upper limit, without indicating the stack overflow. The previously stored information is then overwritten and therefore lost. The stack also wraps in case of an underflow.

The stack is used to save the return address during a subroutine call and the CPU context during an interrupt. The user may also directly manipulate the stack by means of the PUSH and POP instructions. In the case of an interrupt, the PCL is stored at the first location pointed to by the SP. Then the other registers are stored in the next locations as shown in Figure 2.

- When an interrupt is received, the SP is decremented and the context is pushed on the stack.

- On return from interrupt, the SP is incremented and the context is popped from the stack.

A subroutine call occupies two locations and an interrupt five locations in the stack area.

## 6.4 SYSTEM INTEGRITY MANAGEMENT (SI)

The System Integrity Management block contains the Low Voltage Detector (LVD), Auxiliary Voltage Detector (AVD) functions. It is managed by the SICSR register.

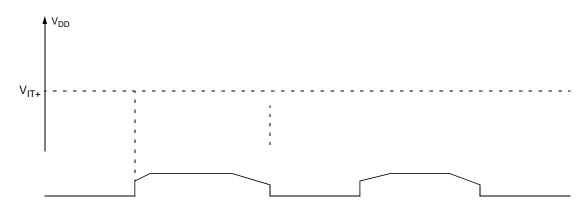

# 6.4.1 Low Voltage Detector (LVD)

The Low Voltage Detector function (LVD) generates a static reset when the  $V_{DD}$  supply voltage is below a  $V_{IT}$  reference value. This means that it secures the power-up as well as the power-down keeping the ST7 in reset.

The V<sub>IT</sub> reference value for a voltage drop is lower than the V<sub>IT</sub> reference value for power-on in order to avoid a parasitic reset when the MCU starts running and sinks current on the supply (hysteresis).

The LVD Reset circuitry generates a reset when  $V_{DD}$  is below:

- $V_{IT+}$  when  $V_{DD}$  is rising

- $-V_{IT}$  when  $V_{DD}$  is falling

- The LVD function is illustrated in Figure 16.

The voltage threshold can be configured by option byte to be low, medium or high.

Provided the minimum  $V_{DD}$  value (guaranteed for the oscillator frequency) is above  $V_{IT-}$ , the MCU can only be in two modes:

## Figure 16. Low Voltage Detector vs Reset

- under full software control

- in static safe reset

In these conditions, secure operation is always ensured for the application without the need for external reset hardware.

During a Low Voltage Detector Reset, the RESET pin is held low, thus permitting the MCU to reset other devices.

#### Notes:

The LVD allows the device to be used without any external RESET circuitry.

If the medium or low thresholds are selected, the detection may occur outside the specified operating voltage range. Below 3.8V, device operation is not guaranteed.

The LVD is an optional function which can be selected by option byte.

It is recommended to make sure that the  $V_{DD}$  supply voltage rises monotonously when the device is exiting from Reset, to ensure the application functions properly.

# INTERRUPTS (Cont'd)

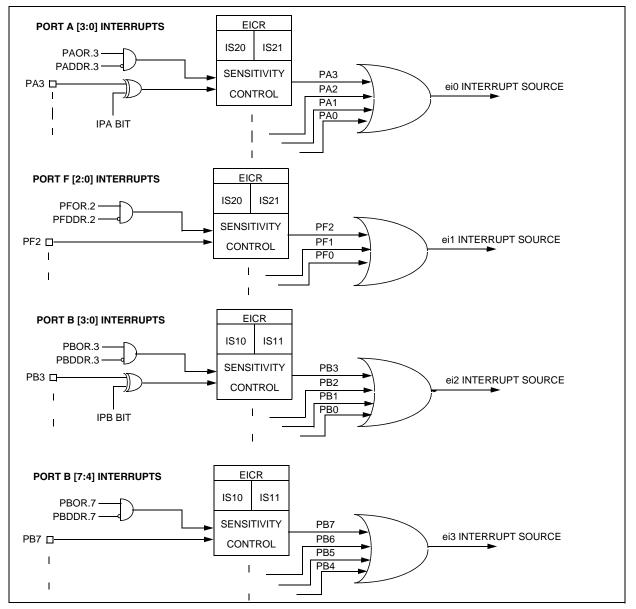

# Figure 23. External Interrupt Control bits

<u>ل</u>حک

38/187

I/O PORTS (Cont'd) Figure 31. I/O Port General Block Diagram

Table 10. I/O Port Mode Options

Legend : NI - not implemented Off - implemented not activated

# I/O PORTS (Cont'd)

# Table 13. I/O Port Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label                        | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|-------------------|------------------------------------------|-----|---|---|---|---|---|---|-----|

|                   | Reset Value<br>of all I/O port registers |     | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

| 0000h             | PADR                                     |     |   |   |   |   |   |   |     |

| 0001h             | PADDR                                    | MSB |   |   |   |   |   |   | LSB |

| 0002h             | PAOR                                     |     |   |   |   |   |   |   |     |

| 0003h             | PBDR                                     |     |   |   |   |   |   |   |     |

| 0004h             | PBDDR                                    | MSB |   |   |   |   |   |   | LSB |

| 0005h             | PBOR                                     |     |   |   |   |   |   |   |     |

| 0006h             | PCDR                                     | MSB |   |   |   |   |   |   | LSB |

| 0007h             | PCDDR                                    |     |   |   |   |   |   |   |     |

| 0008h             | PCOR                                     |     |   |   |   |   |   |   |     |

| 0009h             | PDDR                                     |     |   |   |   |   |   |   |     |

| 000Ah             | PDDDR                                    | MSB |   |   |   |   |   |   | LSB |

| 000Bh             | PDOR                                     |     |   |   |   |   |   |   |     |

| 000Ch             | PEDR                                     |     |   |   |   |   |   |   |     |

| 000Dh             | PEDDR                                    | MSB |   |   |   |   |   |   | LSB |

| 000Eh             | PEOR                                     |     |   |   |   |   |   |   |     |

| 000Fh             | PFDR                                     |     |   |   |   |   |   |   |     |

| 0010h             | PFDDR                                    | MSB |   |   |   |   |   |   | LSB |

| 0011h             | PFOR                                     |     |   |   |   |   |   |   |     |

# **Related Documentation**

AN 970: SPI Communication between ST7 and EEPROM

AN1045: S/W implementation of I2C bus master AN1048: Software LCD driver

57

# 16-BIT TIMER (Cont'd) CONTROL/STATUS REGISTER (CSR)

Read/Write (bits 7:3 read only)

Reset Value: xxxx x0xx (xxh)

| 7    |      |     |      |      |      |   | 0 |

|------|------|-----|------|------|------|---|---|

| ICF1 | OCF1 | TOF | ICF2 | OCF2 | TIMD | 0 | 0 |

## Bit 7 = ICF1 Input Capture Flag 1.

0: No input capture (reset value).

1: An input capture has occurred on the ICAP1 pin or the counter has reached the OC2R value in PWM mode. To clear this bit, first read the SR register, then read or write the low byte of the IC1R (IC1LR) register.

## Bit 6 = OCF1 Output Compare Flag 1.

0: No match (reset value).

1: The content of the free running counter has matched the content of the OC1R register. To clear this bit, first read the SR register, then read or write the low byte of the OC1R (OC1LR) register.

#### Bit 5 = **TOF** *Timer Overflow Flag.*

0: No timer overflow (reset value).

1: The free running counter rolled over from FFFFh to 0000h. To clear this bit, first read the SR register, then read or write the low byte of the CR (CLR) register. **Note:** Reading or writing the ACLR register does not clear TOF.

#### Bit 4 = ICF2 Input Capture Flag 2.

- 0: No input capture (reset value).

- 1: An input capture has occurred on the ICAP2 pin. To clear this bit, first read the SR register, then read or write the low byte of the IC2R (IC2LR) register.

## Bit 3 = **OCF2** Output Compare Flag 2.

- 0: No match (reset value).

- 1: The content of the free running counter has matched the content of the OC2R register. To clear this bit, first read the SR register, then read or write the low byte of the OC2R (OC2LR) register.

### Bit 2 = **TIMD** *Timer disable.*

This bit is set and cleared by software. When set, it freezes the timer prescaler and counter and disabled the output functions (OCMP1 and OCMP2 pins) to reduce power consumption. Access to the timer registers is still available, allowing the timer configuration to be changed, or the counter reset, while it is disabled.

0: Timer enabled

1: Timer prescaler, counter and outputs disabled

Bits 1:0 = Reserved, must be kept cleared.

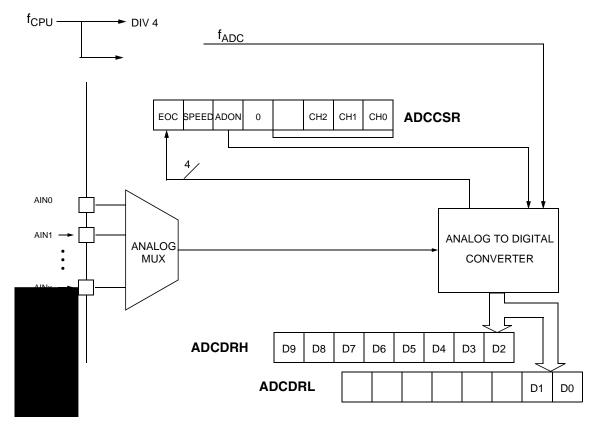

# 10.8 10-BIT A/D CONVERTER (ADC)

## **10.8.1 Introduction**

The on-chip Analog to Digital Converter (ADC) peripheral is a 10-bit, successive approximation converter with internal sample and hold circuitry. This peripheral has up to 16 multiplexed analog input channels (refer to device pin out description) that allow the peripheral to convert the analog voltage levels from up to 16 different sources.

The result of the conversion is stored in a 10-bit Data Register. The A/D converter is controlled through a Control/Status Register.

# Figure 69. ADC Block Diagram

## 10.8.2 Main Features

- 10-bit conversion

- Up to 16 channels with multiplexed input

- Linear successive approximation

- Data register (DR) which contains the results

- Conversion complete status flag

- On/off bit (to reduce consumption)

The block diagram is shown in Figure 69.

Ĺ**Ţ**